JP5132330B2 - 不揮発性半導体記憶装置およびその製造方法 - Google Patents

不揮発性半導体記憶装置およびその製造方法 Download PDFInfo

- Publication number

- JP5132330B2 JP5132330B2 JP2008008301A JP2008008301A JP5132330B2 JP 5132330 B2 JP5132330 B2 JP 5132330B2 JP 2008008301 A JP2008008301 A JP 2008008301A JP 2008008301 A JP2008008301 A JP 2008008301A JP 5132330 B2 JP5132330 B2 JP 5132330B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- film

- silicon nitride

- high dielectric

- silicon oxide

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 33

- 238000004519 manufacturing process Methods 0.000 title claims description 18

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 82

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 82

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 82

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 82

- 238000003860 storage Methods 0.000 claims description 41

- 239000000758 substrate Substances 0.000 claims description 31

- 238000000034 method Methods 0.000 claims description 25

- 229910052723 transition metal Inorganic materials 0.000 claims description 6

- 239000010410 layer Substances 0.000 description 97

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 21

- 238000002955 isolation Methods 0.000 description 21

- 229910052710 silicon Inorganic materials 0.000 description 21

- 239000010703 silicon Substances 0.000 description 21

- 230000005684 electric field Effects 0.000 description 18

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 8

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 8

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 229910052735 hafnium Inorganic materials 0.000 description 6

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 6

- 239000011777 magnesium Substances 0.000 description 6

- 229920006395 saturated elastomer Polymers 0.000 description 6

- 239000002344 surface layer Substances 0.000 description 6

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 5

- 238000000231 atomic layer deposition Methods 0.000 description 5

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 5

- 230000002093 peripheral effect Effects 0.000 description 5

- 238000001020 plasma etching Methods 0.000 description 5

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 238000005121 nitriding Methods 0.000 description 4

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 3

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 239000011248 coating agent Substances 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- -1 hafnium or zirconium Chemical class 0.000 description 3

- 239000011229 interlayer Substances 0.000 description 3

- 229910052749 magnesium Inorganic materials 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- 150000003624 transition metals Chemical class 0.000 description 3

- 230000005641 tunneling Effects 0.000 description 3

- 229910052727 yttrium Inorganic materials 0.000 description 3

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 229910052797 bismuth Inorganic materials 0.000 description 2

- JCXGWMGPZLAOME-UHFFFAOYSA-N bismuth atom Chemical compound [Bi] JCXGWMGPZLAOME-UHFFFAOYSA-N 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- MROCJMGDEKINLD-UHFFFAOYSA-N dichlorosilane Chemical compound Cl[SiH2]Cl MROCJMGDEKINLD-UHFFFAOYSA-N 0.000 description 2

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 229910052746 lanthanum Inorganic materials 0.000 description 2

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 2

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 2

- 239000000395 magnesium oxide Substances 0.000 description 2

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 239000001272 nitrous oxide Substances 0.000 description 2

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 2

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 2

- 229920001709 polysilazane Polymers 0.000 description 2

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 229910052712 strontium Inorganic materials 0.000 description 2

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910000314 transition metal oxide Inorganic materials 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- 229910052726 zirconium Inorganic materials 0.000 description 2

- 229910001928 zirconium oxide Inorganic materials 0.000 description 2

- 208000032368 Device malfunction Diseases 0.000 description 1

- 229910052688 Gadolinium Inorganic materials 0.000 description 1

- 229910003855 HfAlO Inorganic materials 0.000 description 1

- 229910004129 HfSiO Inorganic materials 0.000 description 1

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910052772 Samarium Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- 229910007875 ZrAlO Inorganic materials 0.000 description 1

- 229910006501 ZrSiO Inorganic materials 0.000 description 1

- LPQOADBMXVRBNX-UHFFFAOYSA-N ac1ldcw0 Chemical compound Cl.C1CN(C)CCN1C1=C(F)C=C2C(=O)C(C(O)=O)=CN3CCSC1=C32 LPQOADBMXVRBNX-UHFFFAOYSA-N 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000011529 conductive interlayer Substances 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000010893 electron trap Methods 0.000 description 1

- UIWYJDYFSGRHKR-UHFFFAOYSA-N gadolinium atom Chemical compound [Gd] UIWYJDYFSGRHKR-UHFFFAOYSA-N 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- QPJSUIGXIBEQAC-UHFFFAOYSA-N n-(2,4-dichloro-5-propan-2-yloxyphenyl)acetamide Chemical compound CC(C)OC1=CC(NC(C)=O)=C(Cl)C=C1Cl QPJSUIGXIBEQAC-UHFFFAOYSA-N 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 239000007800 oxidant agent Substances 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- GFQYVLUOOAAOGM-UHFFFAOYSA-N zirconium(iv) silicate Chemical compound [Zr+4].[O-][Si]([O-])([O-])[O-] GFQYVLUOOAAOGM-UHFFFAOYSA-N 0.000 description 1

Images

Landscapes

- Formation Of Insulating Films (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Description

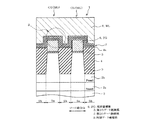

図7に示すように、p型の単結晶のシリコン基板2の表層にNウェル2aおよびPウェル2bを順に形成し、シリコン基板2上にゲート絶縁膜5(絶縁膜)を1〜15[nm]範囲の所定膜厚で形成する。次に、図8に示すように、ゲート絶縁膜5上に非晶質シリコンを化学気相成長法により10〜200[nm]範囲の所定膜厚で堆積する。この非晶質シリコンは後の熱処理によって多結晶化することで多結晶シリコンに変成され導電層6(浮遊ゲート電極FG)として構成される。次に、図9に示すように、化学気相成長法によってシリコン窒化膜9を50〜200[nm]範囲の所定膜厚で堆積し、次に、化学気相成長法によってシリコン酸化膜10をハードマスクとして50〜400[nm]範囲の所定膜厚で堆積する。

高誘電体絶縁膜7abが非遷移金属元素(Al)の酸化膜により形成されているため、高誘電体絶縁膜7bにトラップされた電荷の再放出を防ぐことができ閾値変動を抑制させることができる。

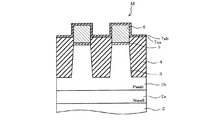

(第2の実施形態)

図20は、本発明の第2の実施形態を示すもので、前述実施形態と異なるところは、ゲート間絶縁膜の積層構造にある。前述実施形態と同一部分については同一符号を付して説明を省略し、以下、異なる部分についてのみ説明する。

本発明は、上記実施形態にのみ限定されるものではなく、次のように変形または拡張できる。

浮遊ゲート電極FG、ゲート間絶縁膜7、制御ゲート電極CGの積層構造を備えた不揮発性半導体記憶装置1に適用したが、その他のNOR型の不揮発性半導体記憶装置などにも適用できる。また、浮遊ゲート電極に代えて電荷トラップ層としてシリコン窒化膜を適用した電荷トラップ型のセル構造(MONOS、SONOSと称される)を具備した不揮発性半導体記憶装置においても同様に適用できる。

Claims (5)

- 半導体基板と、

前記半導体基板上に形成された第1のゲート絶縁膜と、

前記第1のゲート絶縁膜上に形成された電荷蓄積層と、

前記電荷蓄積層上に形成された第2のゲート絶縁膜と、

前記第2のゲート絶縁膜上に形成された制御ゲート電極層とを備え、

前記第2のゲート絶縁膜は、前記電荷蓄積層と前記制御ゲート電極層との間において、シリコン酸化膜と、シリコン窒化膜の比誘電率よりも高い比誘電率を有する第1の高誘電体絶縁膜と、シリコン窒化膜の比誘電率よりも高い比誘電率を有する第2の高誘電体絶縁膜とを備え、前記第1および第2の高誘電体絶縁膜が前記シリコン酸化膜を挟んだ層構造を備えると共に前記電荷蓄積層と前記層構造との間に下層シリコン窒化膜を備えることを特徴とする不揮発性半導体記憶装置。 - 半導体基板と、

前記半導体基板上に形成された第1のゲート絶縁膜と、

前記第1のゲート絶縁膜上に形成された電荷蓄積層と、

前記電荷蓄積層上に形成された第2のゲート絶縁膜と、

前記第2のゲート絶縁膜上に形成された制御ゲート電極層とを備え、

前記第2のゲート絶縁膜は、前記電荷蓄積層と前記制御ゲート電極層との間に前記電荷蓄積層側から前記制御ゲート電極層側にかけて、第1のシリコン窒化膜、第1のシリコン酸化膜、比誘電率がシリコン窒化膜の比誘電率よりも高い比誘電率を有する第1の高誘電体絶縁膜、第2のシリコン酸化膜、第2のシリコン窒化膜の積層構造を備えると共に、第1のシリコン窒化膜および第1のシリコン酸化膜間、または、第2のシリコン窒化膜および第2のシリコン酸化膜間の少なくとも何れか一方に比誘電率がシリコン窒化膜の比誘電率よりも高い比誘電率を有する第2の高誘電体絶縁膜を備えたことを特徴とする不揮発性半導体記憶装置。 - 半導体基板と、

前記半導体基板上に形成された第1のゲート絶縁膜と、

前記第1のゲート絶縁膜上に形成された電荷蓄積層と、

前記電荷蓄積層上に形成された第2のゲート絶縁膜と、

前記第2のゲート絶縁膜上に形成された制御ゲート電極層とを備え、

前記第2のゲート絶縁膜は、前記電荷蓄積層と前記制御ゲート電極層との間において、第1ないし第3のシリコン酸化膜の3層シリコン酸化膜構造を備えると共に、比誘電率がシリコン窒化膜の比誘電率よりも高い比誘電率を有する第1の高誘電体絶縁膜と、比誘電率がシリコン窒化膜の比誘電率よりも高い比誘電率を有する第2の高誘電体絶縁膜とを備え、前記第1の高誘電体絶縁膜が前記3層シリコン酸化膜構造間に介在する2層のうちの何れか一方に形成されていると共に前記第2の高誘電体絶縁膜が前記3層シリコン酸化膜構造間に介在する2層のうちの他方に形成されていることを特徴とする不揮発性半導体記憶装置。 - 前記第1の高誘電体絶縁膜は遷移金属元素の酸化膜を含んでいることを特徴とする請求項1ないし3の何れかに記載の不揮発性半導体記憶装置。

- 半導体基板上に第1のゲート絶縁膜を形成する工程と、

前記第1のゲート絶縁膜上に電荷蓄積層を形成する工程と、

前記電荷蓄積層上に第1のシリコン窒化膜を形成する工程と、

前記第1のシリコン窒化膜上に第1のシリコン酸化膜を形成する工程と、

前記第1のシリコン酸化膜上に比誘電率がシリコン窒化膜の比誘電率よりも高い比誘電率を有する第1の高誘電体絶縁膜を形成する工程と、

前記第1の高誘電体絶縁膜上に第2のシリコン酸化膜を形成する工程と、

前記第2のシリコン酸化膜上に比誘電率がシリコン窒化膜の比誘電率よりも高い比誘電率を有する第2の高誘電体絶縁膜を形成する工程と、

前記第2の高誘電体絶縁膜上に第2のシリコン窒化膜を形成する工程と、

前記第2のシリコン窒化膜上に制御ゲート電極層を形成する工程とを備えたことを特徴とする不揮発性半導体記憶装置の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008008301A JP5132330B2 (ja) | 2008-01-17 | 2008-01-17 | 不揮発性半導体記憶装置およびその製造方法 |

| US12/333,983 US8008707B2 (en) | 2007-12-14 | 2008-12-12 | Nonvolatile semiconductor memory device provided with charge storage layer in memory cell |

| US13/207,149 US8742487B2 (en) | 2007-12-14 | 2011-08-10 | Nonvolatile semiconductor memory device provided with charge storage layer in memory cell |

| US14/273,162 US9142685B2 (en) | 2007-12-14 | 2014-05-08 | Nonvolatile semiconductor memory device provided with charge storage layer in memory cell |

| US14/697,121 US9450108B2 (en) | 2007-12-14 | 2015-04-27 | Nonvolatile semiconductor memory device provided with charge storage layer in memory cell |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008008301A JP5132330B2 (ja) | 2008-01-17 | 2008-01-17 | 不揮発性半導体記憶装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009170719A JP2009170719A (ja) | 2009-07-30 |

| JP2009170719A5 JP2009170719A5 (ja) | 2010-04-08 |

| JP5132330B2 true JP5132330B2 (ja) | 2013-01-30 |

Family

ID=40971562

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008008301A Active JP5132330B2 (ja) | 2007-12-14 | 2008-01-17 | 不揮発性半導体記憶装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5132330B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013197191A (ja) | 2012-03-16 | 2013-09-30 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP5865214B2 (ja) | 2012-09-06 | 2016-02-17 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US9224874B2 (en) | 2014-01-10 | 2015-12-29 | Kabushiki Kaisha Toshiba | Semiconductor storage device |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4851740B2 (ja) * | 2005-06-30 | 2012-01-11 | 株式会社東芝 | 半導体装置およびその製造方法 |

| KR100648860B1 (ko) * | 2005-09-08 | 2006-11-24 | 주식회사 하이닉스반도체 | 유전막 및 그 형성방법과, 상기 유전막을 구비한 반도체메모리 소자 및 그 제조방법 |

-

2008

- 2008-01-17 JP JP2008008301A patent/JP5132330B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009170719A (ja) | 2009-07-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9450108B2 (en) | Nonvolatile semiconductor memory device provided with charge storage layer in memory cell | |

| KR101038131B1 (ko) | 불휘발성 반도체 메모리 | |

| JP5361328B2 (ja) | 不揮発性半導体記憶装置の製造方法 | |

| US20050285219A1 (en) | Nonvolatile semiconductor memory and method of fabricating the same | |

| KR101218447B1 (ko) | 반도체 기억 장치 | |

| US8212303B2 (en) | Nonvolatile semiconductor memory device | |

| KR101139556B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US7049189B2 (en) | Method of fabricating non-volatile memory cell adapted for integration of devices and for multiple read/write operations | |

| JP2009252774A (ja) | 半導体記憶装置およびその製造方法 | |

| JP2019197772A (ja) | 半導体装置およびその製造方法 | |

| JP2012114199A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2009054942A (ja) | 不揮発性半導体記憶装置 | |

| JP2000286349A (ja) | 半導体装置およびその製造方法 | |

| JP5132330B2 (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| US7205189B2 (en) | Method of manufacturing a dual bit flash memory | |

| JP2019117913A (ja) | 半導体装置およびその製造方法 | |

| JP2003282748A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| KR100620217B1 (ko) | 비휘발성 메모리 소자의 제조 방법 | |

| JP2020013850A (ja) | 半導体装置およびその製造方法 | |

| JP2009147135A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| JP2022079032A (ja) | 半導体装置 | |

| JP2006332098A (ja) | 半導体装置およびその製造方法 | |

| JP2010027967A (ja) | 不揮発性半導体記憶装置の製造方法 | |

| KR100771553B1 (ko) | 전하트랩층을 갖는 매몰형 불휘발성 메모리소자 및 그제조방법 | |

| JP2010109185A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100217 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100217 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120622 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120626 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120827 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121009 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121106 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151116 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5132330 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151116 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |