以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

(実施の形態1)

本実施の形態では、異なる膜厚を有するマスクを用いて形成される微小構造体の作製方法について説明する。本実施の形態において、フォトリソグラフィー法には、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用い、マスクを加工する。

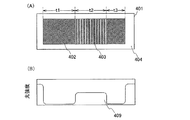

図1(A)に示すように絶縁表面を有する基板(絶縁基板と記す)100を用意する。なお図1(B)には、A−Bにおける断面図を示す。

絶縁基板100には、ガラス基板、石英基板、プラスチック基板等を適用することができる。例えば、プラスチック基板に微小構造体を形成することにより、柔軟性が高く、薄型な微小構造体を有する装置を形成することができる。またガラス基板を研磨等により薄くすることによって、薄型な装置を形成することもできる。さらに本発明の微小構造体は、金属等の導電性基板や、シリコン等の半導体性基板上に絶縁性を有する層を形成した基板に形成することも可能である。

絶縁基板100上に犠牲層101を形成する。なお犠牲層とは、後の工程で選択的に除去される層を指す。そのため、犠牲層は除去されればよく、導電層であっても、絶縁層であってもよい。このような犠牲層を除去することによって空間が生じる。すなわち、所定の形状の構造物を空間に形成することができる。犠牲層101は、チタン(Ti)、アルミニウム(Al)、モリブデン(Mo)、タングステン(W)等の金属を有する材料により形成することができ、シリコンを有する半導体層(シリコン層とも記す)、シリコンの酸化物(シリコン酸化物)、又はシリコンの窒化物(シリコン窒化物)を有する材料によっても形成することができる。また犠牲層101は、上記の金属と、シリコンとの化合物である金属化合物を用いて形成してもよい。さらに犠牲層101は、単層構造であっても、積層構造であってもよい。積層構造の場合、上記材料から選ばれた材料を積層すればよい。

犠牲層101は、スパッタリング法やCVD法等を用いて形成することができる。そして、犠牲層101の加工には、フォトリソグラフィー法を用いてレジストマスクを形成し、ドライエッチング法により行うことができる。またインクジェット法を代表とする液滴吐出法により形成することもできる。液滴吐手法を用いる場合、上記した金属が混在された溶媒を滴下することで犠牲層101を選択的に形成することができる。そのため、犠牲層101のフォトリソグラフィー工程やパターニング工程を不要とすることができる。その結果、レジスト材料の無駄や工程時間を省くことができる。

犠牲層101はその膜厚が薄すぎれば、エッチング剤が拡散せず、犠牲層101がエッチングされない、またはエッチング後に構造層が座屈(微小構造体が下面に付着する)するといった現象が生じる。一方、犠牲層を除去すると生じる空間を介して微小構造体を静電駆動させる場合、犠牲層101が厚すぎると、空間の距離が大きくなり、微小構造体を駆動しにくくなる。従って、微小構造体を静電駆動によるスイッチング素子として用いる場合、犠牲層101の膜厚は、0.5μmから4μmが好ましい。勿論、犠牲層101の材料を考慮する必要がある。犠牲層101の膜厚は、空間の高さとなりえる。

本実施の形態では、犠牲層101にシリコン層を用い、CVD法により形成する。その後、フォトリソグラフィー法を用いてマスクを形成し、当該マスクを用いて犠牲層101をエッチングする。本実施の形態では、矩形状に犠牲層101をエッチングする。

次に、図2(A)に示すように犠牲層101上に構造層102をスパッタリング法、CVD法等を用いて形成する。構造層102は、シリコン層から形成することができる。シリコン層の材料には、シリコン、ゲルマニウムを0.01〜4.5atomic%程度に有するシリコンゲルマニウムがある。シリコン層は、非晶質状態又は結晶状態のものを用いることができる。また構造層102はシリコン酸化物、又はシリコン窒化物を用いて形成することもでき、チタン(Ti)、アルミニウム(Al)、モリブデン(Mo)、タングステン(W)等の金属材料を用いることができる。また構造層102は、上記の金属と、シリコンとの化合物である金属化合物を用いて形成してもよい。さらに構造層102は、単層構造であっても、積層構造であってもよい。積層構造の場合、上記材料から選ばれた各材料を積層すればよい。

シリコン層から形成された構造層102に導電性が必要な場合は、燐や砒素、硼素等の不純物元素を添加することも可能である。このような不純物元素を添加して、不純物領域を形成してもよい。不純物領域は、フォトリソグラフィー法によりレジストマスクを形成し、選択的に不純物元素を添加して形成することができる。不純物元素を添加する方法は、イオンドープ法またはイオン注入法で行うことができる。このような導電性を有する微小構造体は、静電力(静電引力とも記す)で制御すると好ましく、カンチレバー型のスイッチに適する。勿論、微小構造体を電磁力により制御してもよい。

不純物領域を形成した後、不純物元素を活性化するために加熱処理を行ってもよい。

なお犠牲層101と構造層102とは、上記した材料に限定されるものではなく、犠牲層101を選択的に除去することができる材料の組み合わせであればよい。そのため、同一材料であっても、結晶状態等によって、特定のエッチング剤に選択的に除去される材料と、除去されない材料との組み合わせであってもよい。

このように構造層をシリコン層等からなる薄膜によって形成することにより、ウエハを用いて形成する場合と比較して、非常に薄く形成することができる。またこのような構造層は、絶縁基板上に形成することができるため、生産コストを削減することができる。

次に、図2(A)に示すように、構造層102上にマスク103を形成する。なお図2(B)には、A−Bにおける断面図を示す。

マスク103は、感光剤を含む市販のレジスト材料を用いてもよく、ポジ型レジスト又はネガ型レジストを用いることができる。代表的なポジ型レジストは、ノボラック樹脂と感光剤であるナフトキノンジアジド化合物であり、代表的なネガ型レジストであるベース樹脂、ジフェニルシランジオール及び酸発生剤等がある。その他、エポキシ樹脂、アクリル樹脂、フェノール樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いることができる。またマスク103は、ベンゾシクロブテン、パリレン、フッ化アリーレンエーテル、透過性を有するポリイミド等の有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いて液滴吐出法で形成することもできる。

そして、マスク103を露光、現像し、所定の形状となるように加工する。本実施の形態では、マスク103を犠牲層101の大部分を覆うような形状とする。さらに図2(B)に示すように、マスク103の膜厚が異なっており、本実施の形態では第1の膜厚(d1)と、第2の膜厚(d2)とを有し、第2の膜厚は第1の膜厚より薄くなっている(d2<d1)。

マスク103を形成するために、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置した露光用マスクを用いる。露光用マスクとして、フォトマスク又はレチクルが挙げられる。このような露光用マスクについて図6から図8を用いて説明する。なお図6から図8において、第1の膜厚(d1)領域のマスクを形成するための遮光部の幅をt1、t3とし、第2の膜厚(d2)領域のマスクを形成するための補助パターンが設けられた部分の幅をt2と示す。

図6(A)に、露光装置の解像限界以下のライン及びスペースを有するスリット部を有する回折格子パターン部403、遮光部402、透光部404を備えた露光用マスク401の上面図の一部を示す。回折格子パターン部403とは、スリット、ドット等のパターンが少なくとも1つ以上配置されたパターンである。スリット、ドット等のパターンを複数配置する場合は、周期的に配置されていてもよいし、非周期的に配置されてもよい。解像度限界以下の微細パターンを用いることによって、実質的な露光量を変調することが可能であり、露光されるマスクの膜厚を調節することが可能である。

回折格子パターン部403のスリットの方向は、遮光部402の長軸方向と平行でも、図7に示すように遮光部402の長軸方向と垂直でも構わない。なお、このフォトリソグラフィー工程で使用されるマスクとしてレジストを適用する場合、ネガ型レジストが適用困難である為、ポジ型レジストを前提にしている。

露光用マスク401に光を照射した場合、遮光部402の光強度はゼロであり、透光部404の光強度は100%となる。一方、露光装置の解像限界以下のラインおよびスペースからなる回折格子パターン部403の光強度は、10〜70%の範囲で調整可能となる。このような光強度の例を図6(B)の光強度分布409に示す。回折格子パターン部403の光強度の調整は、スリットのピッチ及びスリット幅の調整により実現している。

また、補助パターンの具体例として、図8(A)に、露光の光強度を低減する機能を有する半透膜からなる半透部407を備え、図6、図7と同様に遮光部402、透光部404を有する露光用マスク415の上面図の一部を示す。半透膜としては、MoSiN、MoSi、MoSiO、MoSiON、CrSiなどのシリサイドを用いることができる。半透部407を備えた露光用マスクを用いた露光法は、ハーフトーン露光法とも呼ばれる。

このような露光用マスク415に光を照射した場合、遮光部402の光強度はゼロ、透光部404の光強度は100%であり、半透膜からなる半透部407の光強度は、10〜70%の範囲で調整可能となっている。すなわち半透膜と遮光部とにわたり、光強度を連続的に変化させたり、多段階的に変化させることができる。露光用マスクの光強度の一例を、図8(B)の光強度分布410に示す。

露光用マスク401、415を用いて露光すると、第1の膜厚(d1)と、第2の膜厚(d2)とを有し、第2の膜厚は第1の膜厚より薄くなるマスク103を得ることができる。

このようなマスク103を用いて、構造層102をエッチングする。本実施の形態では、構造層102の一辺のみが、犠牲層101の端面を超えて設けられ、且つ他辺は犠牲層101の端面より短くなり、その幅は上方から見ると犠牲層101の幅よりも狭くなるように、矩形状に加工する。すなわち、図2(B)に示す断面図でみると、構造層102及びマスク103は、犠牲層101による段差を有している。

その後、図3に示すようにマスク103を用いて構造層102を加工する。加工にはウェットエッチング法やドライエッチング法を適用することができる。このとき、マスク103で覆われていない構造層102と、マスク103の表面とが除去されていく。マスク103は、第2の膜厚(d2)が薄いため、第1の膜厚(d1)の領域より先に除去され、第2の膜厚のマスク103下の構造層102は除去される。その結果、構造層102はマスク103を除去したり再度形成することなく、一回のエッチング工程によって、第3の膜厚(d3)及び第4の膜厚(d4)を有するように加工することができる。言い換えると、構造層102のうち第3の膜厚を有する部分は、第1の膜厚を有するマスク103下に形成され、第4の膜厚を有する部分は、第2の膜厚を有するマスク103下に形成される。本実施の形態では、構造層102において、第4の膜厚が第3の膜厚より薄くなる(d4<d3)。

また本発明の微小構造体をスイッチング素子として用いる場合、構造層の可動部の長さは、第4の膜厚を有する構造層102の膜厚の30倍から50倍となると好ましい。このとき、微小構造体のバネ定数を考慮するとよい。また第3の膜厚を有する構造層102の膜厚は、密度を考慮してその膜厚を決定する。第3の膜厚を有する構造層が低密度の場合、膜厚を厚くすることにより、下方の電極との接触を高めることができる。

次に図4に示すように、マスク103を除去する。マスク103の除去には、ウェットエッチング法やドライエッチング法を適用することができる。例えば、2−アミノエタノール、グライコールエーテルを主成分とするナガセケムテックス社製「ナガセレジストストリップN−300」剥離液や、o−ジクロルベンゼン、フェノール、アルキルベンゼンスルホン酸を主成分とする東京応化工業社製「剥離液710」等の剥離液を適用することができる。

そして、図5に示すように、犠牲層101を除去する。犠牲層の除去には、ウェットエッチング法又はドライエッチング法を適用することができる。

例えば、犠牲層101にタングステン(W)を用いる場合、28%のアンモニアと31%の過酸化水素水を1:2で混合した溶液に20分程度漬けることで、除去することができる。犠牲層101に二酸化シリコン(SiO2)を用いる場合は、フッ酸49%水溶液1に対してフッ化アンモニウムを7の割合で混合したバッファードフッ酸を用いて、除去することができる。犠牲層101にシリコンを有する層を用いる場合は、リン酸、KOH、NaOH、CsOH等のアルカリ金属元素の水酸化物を用いて除去することができる。その他犠牲層の材料によって、NH4OH、ヒドラジン、EPD(エチレンジアミン、ピロカテコール、水の混合物)、TMAH、IPA、NMD3溶液等を用いて、除去することができる。また、三フッ化塩素(ClF3)、三フッ化窒素(NF3)、三フッ化臭素(BrF3)、フッ化水素(HF)等のフッ化ハロゲンを用いてシリコンを有する層を除去することもできる。

ウェットエッチング後の乾燥に際しては、毛管現象による微小構造体の座屈を防ぐため、粘性の低い有機溶媒(例えばシクロヘキサン)を用いてリンスを行う、若しくは低温低圧の条件で乾燥させる、またはこの両者を組み合わせた処理を行うとよい。

また、犠牲層101は、大気圧など高圧の条件において、O2、F2、XeF2を用いてドライエッチング法を用いて除去することができる。上記した毛管現象による微小構造体の座屈を防ぐため、微小構造体表面に撥水性を持たせるプラズマ処理を行うとよい。

このように犠牲層101を除去すると、空間105が生じる。空間105によって、構造層102が上下や左右に可動することができる。構造層102が可動する先端の下部電極との接触により、スイッチとして動作することができる。このような形状を有する微小構造体をカンチレバー型微小構造体と呼ぶ。カンチレバー型微小構造体をスイッチに適用すると、低損失、低電力動作を行うことができる。

またマスク103の除去と、犠牲層101の除去を同一工程で行うこともできる。この場合、マスク103と、犠牲層101は同一材料、又は同一エッチング剤によって除去できる材料から形成するとよい。

このようにして本発明は、シリコン層を代表とする薄膜によって、絶縁基板上にカンチレバー型微小構造体を作製することができる。本発明のカンチレバー型微小構造体はスイッチに適用でき、このようなスイッチはシリコンウェハからなるスイッチと比較して、薄型化でき、安価に作製することができる。

また以下の実施の形態で示すが、本発明のカンチレバー型微小構造体は半導体素子と同一絶縁基板上に形成することができる。その結果、カンチレバー型微小構造体と半導体素子との接続不良を低減でき、量産性を高めることができる。

本実施の形態で示したカンチレバー型の微小構造体は、スイッチ以外にAFMの針、加速度センサ(Gセンサ)、又は角速度センサとして用いることもできる。

(実施の形態2)

本発明において構造層や犠牲層に適用するシリコン層には、結晶状態を有するもの、非晶質状態を有するもの等を用いることができる。そこで本実施の形態では、犠牲層に結晶性シリコン層を用いる場合を説明する。

まず、図13(A)に示すように、犠牲層の被形成面である絶縁基板100上に、非晶質シリコン層161を形成する。非晶質シリコン層161は、SH4、Ar等の原料ガスを用い、CVD法により作製することができる。非晶質シリコン層161の膜厚は、犠牲層の膜厚であり、空間の高さとなる。

そして非晶質シリコン層を加熱処理することによって結晶化された結晶性シリコン層を得る。加熱処理には、レーザ照射、加熱炉、若しくはランプ光から発する光の照射(以下、ランプアニールと記す)、又はこれらを組み合わせて用いることができる。

レーザ照射を用いる場合、連続発振型のレーザビーム(以下、CWレーザビームと記す)やパルス発振型のレーザビーム(以下、パルスレーザビームと記す)を用いることができる。レーザビームとしては、Arレーザ、Krレーザ、エキシマレーザ、YAGレーザ、Y2O3レーザ、YVO4レーザ、YLFレーザ、YAlO3レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイヤレーザ、銅蒸気レーザまたは金蒸気レーザのうち一種または複数種から発振されるものを用いることができる。このようなレーザビームの基本波、及び当該基本波の第2高調波から第4高調波のレーザビームを照射することで、大粒径の結晶を得ることができる。例えば、Nd:YVO4レーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いることができる。このときレーザビームのエネルギー密度は0.01〜100MW/cm2程度(好ましくは0.1〜10MW/cm2)が必要である。そして、走査速度を10〜2000cm/sec程度として照射する。

なお基本波のCWレーザビームと高調波のCWレーザビームとを照射するようにしてもよいし、基本波のCWレーザビームと高調波のパルスレーザビームとを照射するようにしてもよい。このように複数のレーザビームを照射することにより、エネルギーを補うことができる。

パルスレーザビームであって、シリコン層がレーザ光によって溶融してから固化するまでに、次のパルスのレーザ光を照射できるような発振周波数でレーザを発振させるレーザビームを用いることもできる。このような周波数でレーザビームを発振させることで、走査方向に向かって連続的に成長した結晶粒を得ることができる。具体的なレーザビームの発振周波数は10MHz以上であって、通常用いられている数十Hz〜数百Hzの周波数帯よりも著しく高い周波数帯を使用する。

その他の加熱処理として加熱炉を用いる場合には、非晶質シリコン層を400〜550℃で2〜20時間かけて加熱する。このとき、徐々に高温となるように温度を400〜550℃の範囲で多段階に設定するとよい。最初の400℃程度の低温加熱工程により、非晶質シリコン層の水素等が出てくるため、結晶化(上記レーザを用いた結晶化を含む)の際の膜荒れを低減することができる。

さらに、結晶化を促進させる金属を用いて結晶化すると加熱温度を低下させることができる。例えばニッケル(Ni)を非晶質シリコン層上に形成した後加熱すると、加熱温度が低下する。このような金属としては、鉄(Fe)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、白金(Pt)、銅(Cu)、銀(Au)等がある。

さらに加熱処理に加えて、上記のようなレーザを用いて照射を行って結晶性シリコン層を形成してもよい。

本実施の形態では、図13(B)に示すように、非晶質シリコン層161上に、ニッケルを有する溶液を塗布し、その後加熱炉を用いて結晶化を行う。加熱温度は、500度〜550度とする。

そして、図13(C)に示すように、金属を用いて結晶化されたシリコン層(多結晶シリコン層)163を得ることができる。

その後、図13(D)に示すように、多結晶シリコン層163を加工し、所定の形状を有する犠牲層101とすることができる。フォトリソグラフィー法によりマスクを形成し、当該マスクを用いてエッチングすることにより、多結晶シリコン層を加工することができる。

その後、図13(E)に示すように、実施の形態1と同様にしてカンチレバー型微小構造体を作製することができる。

以上、金属を用いて結晶化された多結晶シリコンを犠牲層101に適用する場合を説明したが、当該多結晶シリコン層は、構造層102に適用してもよい。このような金属を用いて結晶化された多結晶シリコンは、金属を用いた結晶化により結晶粒界が連続している多結晶シリコンを作ることができる。結晶粒界が連続している多結晶シリコンは、金属を用いない結晶化によって得られる多結晶シリコンと異なり、結晶粒界で共有結合が途切れることが無い。そのため、結晶粒界が欠陥となって起こる応力集中が起こらず、結果として金属を用いずに形成された多結晶シリコンに比べて破壊応力が高くなる。このような多結晶シリコンの結晶構造は、単結晶を用いた場合と近く、金属を用いない結晶化によって作製される多結晶シリコンに比べて靭性の高い多結晶シリコンを得ることができる。このような多結晶シリコンは、可動する構造層102に好適である。

結晶粒界が連続している多結晶シリコン層は、電子の移動度が大きいため、構造層102を静電力で制御する場合に好適である。さらに、結晶化を助長させる金属を多結晶シリコン層中に残存させることにより、導電性を持たせることもできる。このような導電性を有する多結晶シリコン層は、構造層102を静電力で制御する微小電気機械式装置に好適である。勿論、微小構造体を電磁力により制御する場合の構造層102に、金属を用いて結晶化された多結晶シリコン層を適用してもよい。

また金属にニッケルを用いる場合、シリコン層では、ニッケルの濃度によってニッケルシリサイドが形成される。ニッケルシリサイドのようなシリコン合金は強度が高い。そのため、結晶化のための金属を用いてシリサイド化させることができ、さらに硬く、導電性の高い構造層102を作製することができる。

このようなシリサイドは、ニッケル以外にタングステン、チタン、モリブデン、タンタル、コバルト、白金によっても形成することができる。それぞれ、タングステンシリサイド層、チタンシリサイド層、モリブデンシリサイド層、タンタルシリサイド層、コバルトシリサイド層、白金シリサイド層となる。このうち、コバルトや白金は、結晶化の加熱温度を低下させるための金属として用いることができる。

構造層102は積層構造をとることができ、ニッケルシリサイドを有する層(ニッケルシリサイド層)と、多結晶シリコン層とを積層させてもよい。このような積層構造により、導電性に優れ、しなやかな構造層102を得ることができる。また構造層102に、非晶質シリコン層とニッケルシリサイド層とを積層することで、導電性に優れつつ、硬くすることができる。

上記のように、金属を用いて結晶化を行う場合、金属を用いずに行う結晶化に比べて低温で結晶化することができる。そのため、微小構造体を形成する基板に使用できる材料の幅が広がる。例えば、シリコン層を加熱のみで結晶化させる場合、1000℃程度の温度で1時間程度の加熱を行う必要があり、熱に被弱なガラス基板を用いることができない。しかしながら、本実施の形態のように金属を用いて結晶化することによって、ゆがみ点の低いガラス基板等を用いることが可能になる。

本実施の形態は、上記実施の形態と自由に組み合わせることができる。

(実施の形態3)

本発明の微小構造体を静電力で可動させる場合、構造層下に共通電極や制御電極として使用する下部電極を形成する。そこで本実施の形態では、下部電極を有するカンチレバー型の微小構造体について説明する。

図12に示すように、構造層102の下方であって、空間105内に、下部電極150として機能する導電層を形成する。下部電極150は共通電極や制御電極等として使用することができる。下部電極150は、タングステン等の金属や導電性を有する物質を材料として、スパッタリング法等により形成することができ必要に応じて所定の形状にエッチングする。

本実施の形態は、上記実施の形態と自由に組み合わせることができる。

(実施の形態4)

本実施の形態では、本発明の微小構造体を適用できるカンチレバーの種類について説明する。

図15(A)に示すように、構造層501の下方に第1の電極502、第2の電極503が設けられている。第1の電極502は制御用として機能し、第2の電極503はコンタクト用として機能する。制御用として機能する第1の電極502は、構造層501を選択するか否かの選択信号が入力される。選択信号が流れると、構造層501と第1の電極502間には電位差が生じ、これによる静電気によって、構造層501が下降する。すると構造層501の先端部がコンタクト用として機能する第2の電極503に接触し、電流が流れる。

制御用として機能する電極やコンタクト用として機能する電極は複数設けてもよい。例えば、図15(B)に示すように、2つの制御用として機能する第1の電極502、504を設けてもよい。制御用の電極502、504と構造層501とに発生する静電気によって、構造層501を上下させることができる。そのため制御用の電極を複数設けることによって、構造層501が大きく、動作しがたいときであっても、構造層501の動作を正確に制御することができる。また制御用の電極の面積を大きくすることによっても、動作を正確に制御することができる。同様にコンタクト用の電極においても、複数設けたり、面積を大きくしてもよい。コンタクト抵抗が低くなり、正確なコンタクトをとることができる。

また制御用やコンタクト用の電極上方の微小構造体は、その他の領域の微小構造体より厚膜化して設ける。その結果、構造層501の重さがますため、特に構造層501の下降動作が制御しやすくなる。その結果、正確なコンタクトをとることができる。

このようにして、構造層501を選択し、カンチレバー型のスイッチとして動作させることができる。

図15(C)には、カンチレバー型とは異なり、ブリッジ型のスイッチを示す。ブリッジ型のスイッチにおいて、構造層501は、両端が固定されており、その他の構成は図15(B)と同様である。このようなブリッジ型の構造層501も、本発明の異なる膜厚を有するマスクを用いて形成することができる。

このような本発明のスイッチにおいて、電極と接する構造層501には、接触抵抗を低くするため、導電性の高い膜を設けてもよい。併せて電極側に、導電性の高い膜を設けてもよい。このような膜は、接触抵抗を低くするだけでなく、微小構造体や電極の摩耗を低減することができる。

図16(A)には、微小構造体を有するスイッチの上面図を示す。構造層501の下方に切断された配線507が設けられており、構造層501と配線507とは重なるように配置している。構造層501は、カンチレバー型やブリッジ型を適用することができる。

図16(A)で示したスイッチが選択されると、配線507が導通し、電流や信号を流すことができる。このように、スイッチとして機能することができる。このようなスイッチは、シリーズ(Series)型スイッチとなる。

図16(B)には、図16(A)とは異なるスイッチの上面図を示す。配線509及び配線510が並列に設けられており、それらからT字状に接続領域に設けられている。接続領域では、配線509、510の上方に構造層501が配置されている。構造層501がオフの状態では、配線509の一端である点Aから他端であるGND1へ電流が流れている。構造層501がオフの状態では、同様に配線510の一端である点BからGND2へ電流が流れている。このような形態において、構造層501が選択されオンとなると、点Aから点Bへ信号が流れる。このようなスイッチは、シャント(Shunt)型スイッチとなる。

以上、カンチレバー型スイッチがオンとなると、電流が流れる、つまり信号を伝える形態を示したが、オンとなると信号を伝えない形態でもよい。

(実施の形態5)

微小構造体は上下や左右の動作、さらには回転動作を行うため、空気抵抗を受けやすい。そこで本実施の形態では、空気抵抗を減らした微小構造体の形態について説明する。

図18(A)は構造層501の上面図を示す。構造層501において、可動部領域の幅(d6)は錘が設けられている領域(以下、錘領域と記す)の幅(d7)よりも小さく(d6<d7)設けられている。可動領域の幅を錘領域の幅より小さくすることによって、可動部の動作をスムーズに行うことができる。

このとき、上下動作等による可動部の劣化を考慮する。例えば、可動部領域の微小構造体の膜厚を制御して、動作による可動部の劣化を防止することができる。

図18(B)には、図18(A)と異なり、可動部領域において、錘領域との境界をテーパー形状とする微小構造体の上面図を示す。境界をテーパー形状とすることにより、可動部の動作をよりスムーズに行うことができる。

図18(C)には、図18(B)の微小構造体に加えて、可動部領域において、微小構造体に開口部801を設ける。開口部801は単数であっても、複数であってもよい。また開口部が単数の場合、開口部の直径を大きくし、開口部が複数の場合、開口部の直径はさほど大きくせずともよい。開口部801によって、特に微小構造体が上下動作を行うときの空気抵抗を低減することができる。

このような開口部を有する微小構造体は、本発明の異なる膜厚を有するマスクを用いて形成することができる。

このような微小構造体の形態は、上記実施の形態と自由に組み合わせることができる。

(実施の形態6)

微小構造体を有するスイッチは、多数の端子へ出力することができる。本実施の形態では、多端子出力を可能とするスイッチの形態について説明する。

図19には、一つの入力端子(IN)に対して、3つの出力端子(OUT1〜3)を有し、微小構造体1〜3によって、いずれの出力端子へ信号を出力するか制御するスイッチを示す。例えば、微小構造体1が選択されると、INからOUT1へ信号が出力される。また微小構造体1及び2が選択されると、INからOUT1及び2へ信号が出力される。また微小構造体1〜3は、本発明の異なる膜厚を有するマスクを用いて形成される。

本実施の形態では3つの出力端子を有する場合を説明したが、本発明はこれに限定されない。本発明の微小構造体を有するスイッチは、2つの出力端子や4つ以上の出力端子を有しても良い。

(実施の形態7)

本実施の形態では、上記の微小構造体と、微小構造体を制御するための半導体素子を同一表面上に形成する方法について説明する。本実施の形態では、半導体素子として半導体膜上方にゲート電極が設けられたトップゲート型の薄膜トランジスタを用いる場合について説明する。

図10(A)に示すように、絶縁基板100上に、下地層201を形成する。絶縁基板100は、実施の形態1と同様なものを適用することができる。下地層201はシリコンを有する絶縁層を用いることができる。シリコンを有する絶縁層としてシリコン酸化物またはシリコン窒化物が挙げられ、代表的には酸化シリコン、窒化シリコン、または酸化窒化シリコン等がある。下地層201は、このような材料を用いて単層構造または積層構造とすることができる。

本実施の形態では、下地層201として2層構造を用いる場合を説明する。下地層201の一層目として、膜厚10nm以上200nm以下(好ましくは50nm以上100nm以下)の酸化窒化シリコン層を形成する。当該酸化窒化シリコン層は、プラズマCVD法を用い、SiH4、NH3、N2O及びH2を反応ガスとして形成することができる。次いで下地層201のニ層目として、膜厚50nm以上200nm以下(好ましくは100nm以上150nm以下)の酸化窒化シリコン層を形成する。当該酸化窒化シリコン層は、プラズマCVD法を用い、SiH4及びN2Oを反応ガスとして形成することができる。

下地層201上に、半導体層を形成する。半導体層にはシリコン層を適用することができる。多結晶シリコン層の作製方法は、実施の形態2を参照することができる。本実施の形態では、非晶質状態のシリコン層を形成し、金属を用いて結晶化した多結晶シリコン層を作製する。

このような多結晶シリコン層は、移動度が高く半導体素子においても好適である。

その後、半導体素子を形成する第1の領域251、微小構造体を形成する第2の領域252において、多結晶シリコン層を加工し、所定の形状を有するシリコン層202、204を形成する。第1の領域251では、半導体素子の活性層となるように加工する。なお活性層とは、チャネル形成領域、ソース領域及びドレイン領域を有する。また第2の領域252では、上記実施の形態で示したように矩形状となるように加工する。

図10(B)に示すように、第1の領域251のみにゲート絶縁層として機能する絶縁層206を形成する。絶縁層206にはシリコン酸化物またはシリコン窒化物を用いることができ、代表的には酸化シリコン、窒化シリコン、または酸化窒化シリコン等がある。第1の領域251に選択的に絶縁層206を形成するため、第2の領域252はマスク205で覆っておく。マスク205は、感光剤を含む市販のレジスト材料を用いてもよく、ポジ型レジスト又はネガ型レジストを用いることができる。代表的なポジ型レジストは、ノボラック樹脂と感光剤であるナフトキノンジアジド化合物であり、代表的なネガ型レジストであるベース樹脂、ジフェニルシランジオール及び酸発生剤等がある。その他、エポキシ樹脂、アクリル樹脂、フェノール樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いることができる。またマスク205は、ベンゾシクロブテン、パリレン、フッ化アリーレンエーテル、透過性を有するポリイミド等の有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いて液滴吐出法で形成することもできる。その他、第1の領域251及び第2の領域252にわたって絶縁層206を形成し、その後第2の領域252の絶縁層206を除去してもよい。

第1の領域251のみに絶縁層206を形成する場合を説明したが、第2の領域252に絶縁層206を形成してもよい。但し、犠牲層204となるシリコン層を除去できるようにする。

図10(C)に示すように、マスク205を除去した後、第1の領域251及び第2の領域252にわたってゲート電極として機能する導電層208を形成する。導電層208は、アルミニウム(Al)、チタン(Ti)、モリブデン(Mo)、タンタル(Ta)、タングステン(W)もしくはシリコン(Si)の元素からなる膜又はこれらの元素を有する合金膜を用いることができる。導電層208は、単層構造又は積層構造とすることができ、積層構造として窒化タンタルとタングステンの積層構造を適用することができる。導電層208は、スパッタリング法やCVD法により作製することができる。

図11(A)に示すように、第1の領域251及び第2の領域252における導電層208上にマスク210を形成する。マスク210は、フォトリソグラフィー法によって形成することができる。フォトリソグラフィー法には、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いる。回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置した領域は、光の透過率が低下する。その結果、第1の膜厚(d1)と、d1より薄い第2の膜厚(d2)を有するマスク210を形成することができる。光の透過率が低下した領域が、マスクの第2の膜厚(d2)の領域となる。なお、第1の領域251におけるマスク210は、d1が内側、d2が外側となるようにする。第2の領域252におけるマスク210は、d2が内側、d1が外側となるようにする。このようにマスクの膜厚において、どの領域を薄くするかは、加工されるパターンによって決定することができる。その後、ウェットエッチング法又はドライエッチング法を用いて、導電層208を加工する。

図11(B)に示すように、エッチングを開始すると、マスク210で覆われていない導電層208及びマスク210の表面が徐々に除去される。マスク210においては、第2の膜厚(d2)の領域が先に除去され、導電層208が露出されてくる。その結果、図11(C)に示すように、第1の領域251においては導電層208の端部にテーパ(点線領域)が形成され、第2の領域252においては導電層208の中心部に凹部(点線領域)が形成される。テーパーを形成するには、外側に向かって光の透過率を徐々に低くするため、回折パターンの幅を狭くした補助パターンを有するフォトマスクまたはレチクルを用いてマスク210を露光、現像するとよい。

図11(D)に示すように、マスク210を除去し、膜厚の異なる導電層208を形成することができる。すなわちマスク210により、一エッチング工程で膜厚の異なる導電層を加工することができる。勿論、導電層以外であっても、本発明のマスクを用いて加工してもよい。

そして、第1の領域251のシリコン層においてテーパーを有する導電層208を用いて、不純物元素を添加する。n型を付与する不純物元素としてリン(P)を用いて半導体素子253を形成し、p型を付与する不純物元素としてボロン(B)を用いて半導体素子254を形成することができる。なお半導体素子として、薄膜トランジスタ(TFT)を用いる。テーパーを有する導電層208を用いて不純物元素を添加すると、高濃度不純物領域213、216、テーパーの下方に低濃度不純物領域214、215を形成することができる。

また不純物領域の表面にシリサイドを形成してもよい。シリサイドを形成することによって、ソースドレイン間抵抗を下げることができる。ソースドレイン間抵抗が下がることにより、移動度の向上が期待される。

図11(E)に示すように、第1の領域251において導電層208、絶縁層206、シリコン層202を覆うように層間膜として機能する絶縁層218を形成する。絶縁層218は単層構造又は積層構造とすることができ、絶縁性を有する無機材料や、有機材料等により形成することができる。無機材料は、酸化シリコン、窒化シリコンを用いることができる。有機材料はポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト又はベンゾシクロブテン、シロキサン、ポリシラザンを用いることができる。なお、シロキサンとは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。ポリシラザンは、シリコン(Si)と窒素(N)の結合を有するポリマー材料を出発原料として形成される。無機材料を用いると不純物元素の侵入を防止することができ、有機材料を用いると平坦性を高めることができる。

そして、不純物領域に接続された配線219を形成する。配線219はソース領域に接続される場合ソース配線と呼び、ドレイン領域に接続される場合ドレイン配線と呼ぶ。配線219は、アルミニウム(Al)、チタン(Ti)、モリブデン(Mo)、タンタル(Ta)、タングステン(W)もしくはシリコン(Si)の元素からなる膜又はこれらの元素を有する合金膜を用いることができる。配線219は、単層構造又は積層構造を用いることができ、例えば第1層にタングステン膜、窒化タングステン膜等を用い、第2層にアルミニウムとシリコンの合金(Al−Si)膜、アルミニウムとチタンの合金(Al−Ti)膜を用い、第3層に窒化チタン膜、チタン膜等を順次積層した構造を適用することができる。配線219は、CVD法やスパッタリング法を用いて作製することができる。

配線219は、カンチレバー型微小構造体と接続することができる。具体的には、配線219は構造層たる導電層208と接続することができる。

図11(F)に示すように、犠牲層204となるシリコン層を除去する。犠牲層の除去には、ウェットエッチング法又はドライエッチング法を適用することができる。詳細は、上記実施の形態を参照することができる。

その後必要に応じて、パッケージを行うことができる。例えば、第1の領域215には水分や不純物元素の侵入を防ぐため、シリコン窒化物やシリコン酸化物を有する保護膜を形成することができる。

このようにして、カンチレバー型微小構造体と、当該微小構造体を制御するための半導体素子を同一表面上に形成することができる。

本発明のカンチレバー型微小構造体は絶縁基板上に形成される半導体素子と一体形成することができるため、カンチレバー型微小構造体と半導体素子との接続不良を低減でき、量産性を高めることができる。

本実施の形態で示したカンチレバー型微小構造体は、スイッチ以外にAFMの針、Gセンサ/角速度センサとして用いることもできる。

本実施の形態は、上記実施の形態と自由に組み合わせることができる。

(実施の形態8)

本実施の形態では、微小構造体を封止する構造について説明する。

図17(A)に示すように、図11(D)までと同様に、第1の領域251において絶縁基板100上に半導体素子253、254を形成し、第2の領域252において絶縁基板100上に犠牲層204、構造層209を形成する。

図17(B)に示すように、第1の領域251には絶縁層218を形成し、第2の領域252には絶縁層231を形成する。絶縁層231は、絶縁層218と同様な材料、方法によって作製することができるが、特定のエッチング剤に対してエッチング比率の異なる材料を用いる。絶縁層231のみを選択的に除去するからである。次に、第1の領域251及び第2の領域252に渡って、不純物領域に接続された配線219を形成する。このようにして犠牲層204及び構造層209の上方には、絶縁層231及び配線219が形成される。このとき、構造層209と、半導体素子253、254とは電気的に接続することができる。例えば、配線219と同一材料により、構造層209と、半導体素子253、254とを電気的に接続する。

そして第2の領域252において、配線219に開口部230を形成する。開口部230は、ウェットエッチング法又はドライエッチング法を用いて形成することができる。このとき、配線219を選択的に除去することができるエッチング剤を使用する。

図17(C)に示すように、開口部230からエッチング剤を導入し、絶縁層231を除去する。絶縁層231の除去には、ウェットエッチング法又はドライエッチング法を用いることができる。

このとき、第1の領域251において、絶縁層218や配線219がエッチング剤に曝されることを防止するため、マスク234を設けるとよい。マスク234は、マスク103と同様の材料、方法によって形成することができる。

そして図17(D)に示すように、犠牲層204を除去する。犠牲層204を除去することによって、空間236が生じる。犠牲層204の除去には、ウェットエッチング法又はドライエッチング法を用いることができる。

絶縁層231と、犠牲層204は同一の工程で除去してもよい。例えば、絶縁層231と犠牲層204とを同一エッチング剤に反応する材料から形成することによって、同一の工程で除去することができる。同一工程で除去することにより、時間の短縮、コストの削減を図ることができる。

図17(E)に示すように、保護膜237を形成する。保護膜237は、絶縁層218と同一な材料、方法によって作製することができる。保護膜237は、開口部230内に入り込むように形成されうるが、開口部230の直径を小さくすることにより、空間233、236にまで入り込む恐れはない。空間233、236内を不活性ガスで充填するため、不活性ガス雰囲気内において保護膜237を形成する。不活性ガスとして、窒素ガスがある。

このようにして微小構造体及び半導体素子を一体形成し、さらに封止することができる。封止された微小構造体及び半導体素子は、機械的強度を高めることができ、持ち運びが簡便なものとなる。また封止された微小構造体及び半導体素子は、別の装置に実装する場合、取り扱いが簡便なものとなる。

本実施の形態は、上記実施の形態と自由に組み合わせることができる。

(実施の形態9)

上記実施の形態では、同一絶縁基板上に半導体素子と微小構造体を同時に形成する作製方法を説明したが、半導体素子と微小構造体とを積層させてもよい。そこで本実施の形態では、半導体素子の上方に微小構造体を積層する場合の作製方法について説明する。

図20(A)に示すように、図11(E)の第1の領域251と同様に、絶縁基板100上に半導体素子253、254を形成する。そして図17(C)と同様に、絶縁層218を覆うように絶縁層235を形成する。

図20(B)に示すように、絶縁層235にコンタクトホールを形成し、配線219と接続される電極240を形成する。電極240の材料、方法は、配線219と同様である。電極240は、微小構造体の制御用の電極として使用することができる。

図20(C)に示すように、電極240を覆うように犠牲層241を形成する。犠牲層241は、犠牲層101と同様な材料、方法によって作製することができる。

図20(D)に示すように、犠牲層241の少なくとも一部を覆うように微小構造体242を形成する。微小構造体242は、構造層209と同様な材料、方法によって作製することができる。

図20(E)に示すように、犠牲層241を除去する。犠牲層の除去には、ウェットエッチング法又はドライエッチング法を適用することができる。犠牲層241を除去する結果、空間243が生じる。

このようにして、半導体素子と、微小構造体とを積層させることができる。

本実施の形態は、上記実施の形態と自由に組み合わせることができる。

(実施の形態10)

本実施の形態では、半導体素子に半導体膜下方にゲート電極が設けられたボトムゲート型の薄膜トランジスタを用い、当該半導体素子と微小構造体とを同一表面上に形成する方法について説明する。

上記実施の形態と同様に絶縁基板100を用意し、導電層を形成する。導電層を所定の形状に加工して、第1の領域251にはゲート電極、第2の領域252には犠牲層を形成する。

そして、ゲート電極及び犠牲層を覆うように、シリコン層を形成する。シリコン層を所定の形状に加工して、第1の領域251には半導体層、第2の領域252には構造層を形成する。シリコン層は、上記実施の形態と同様に形成することができ、導電性を付与したい場合には、シリサイド化、又は不純物添加を行えばよい。上記実施の形態と同様に、構造層は、その一辺のみが、犠牲層の端面を超えて設けられ、且つ他辺は犠牲層の端面より短くなり、その幅は上方から見ると犠牲層の幅よりも狭くなるように、矩形状に加工する。

その後、第1の領域251において、不純物元素を有する半導体層、ソース配線及びドレイン配線を形成し、必要に応じてシリコン酸化物やシリコン窒化物による保護膜を形成する。ソース配線やドレイン配線は、上記実施の形態と同様に形成することができる。このとき第2の領域252は、マスクで覆っておく。

第2の領域252のマスクを除去し、犠牲層を除去する。このとき選択的に犠牲層を除去するため、第1の領域251にマスクを設ける又は保護膜で覆っている場合、そのマスク又は保護膜には犠牲層と選択比がとれる材料を使用する。

このようにしてボトムゲート型と微小構造体とを同一表面上に形成することができる。

また犠牲層と構造層の材料は、それぞれ導電層とシリコン層に限定されるものではない。例えば、ゲート電極となる導電層を用いて下部電極を形成し、シリコン層を用いて犠牲層を形成し、ソース配線及びドレイン配線となる導電層を用いて構造層を形成してもよい。

導電層を用いて構造層を形成するため、カンチレバー型スイッチに適用する場合に好適である。

(実施の形態11)

本実施の形態では、プラスチック基板等の樹脂基板へカンチレバー型微小構造体及び半導体素子を転置する形態を説明する。

図14(A)に示すように、上記実施の形態と同様に、絶縁層218まで形成する。そして第2の領域252では、マスク212を設けた状態とする。そして、絶縁基板100を剥離する。剥離する手段としては、剥離層を絶縁基板100と下地層201との間に設けておき、剥離層を物理的又は化学的に除去する方法がある。

物理的に除去するためには、剥離層の結晶状態を制御することによって絶縁基板100との密着強度を弱め、力を加えて絶縁基板100を剥離する。このような剥離層には酸化タングステン、酸化モリブデンを用いることができ、加熱処理によって結晶状態を制御することができる。

化学的に除去するためには、剥離層に貫通する開口部を形成し、エッチング剤を導入して剥離層を除去して絶縁基板100を剥離する。このような剥離層にはシリコン層又はタングステン層を用いることができ、エッチング剤には三フッ化塩素(ClF3)、三フッ化窒素(NF3)、三フッ化臭素(BrF3)、フッ化水素(HF)等のフッ化ハロゲンを用いることができる。

勿論、物理的手段と、化学的手段とを組み合わせて適用してもよい。

図14(B)に示すように、接着層255を用いて、プラスチック基板等の樹脂基板256を下地層201に貼り合わせる。接着層255には、紫外線硬化樹脂、熱硬化樹脂等を用いることができる。

図14(C)に示すように、上記実施の形態と同様にマスク212を除去し、配線219を形成し、犠牲層204となるシリコン層を除去する。

このようにして、樹脂基板へ転置されたカンチレバー型微小構造体及び半導体素子を形成することができる。樹脂基板に転置することにより、さらなる軽量化、薄型化を達成することができる。

本実施の形態は、上記実施の形態と自由に組み合わせることができる。

(実施の形態12)

従来、ミリメートル単位以下といった微小なものを扱う場合、まず、微小な対象物の構造を拡大し、人間やコンピュータがその情報を得て情報処理および動作の決定を行い、そして、その動作を縮小して微小な対象物に伝えるというプロセスを必要としていた。

しかし、本発明のカンチレバー型微小構造体は、人間やコンピュータが上位概念的な命令を伝えるだけで、微小なものを扱うことが可能になる。すなわち、人間やコンピュータが目的を決定して命令を伝えると、カンチレバー型微小構造体はセンサ等を用いて対象物の情報を得て情報処理を行い、行動を取ることができる。なお対象物が微小なものであると仮定したが、これは例えば、対象物自体はメートル単位の大きさを有するが、その対象物から発せられる微小な信号(例えば、光や圧力の微小な変化)等も含まれる。

本発明のカンチレバー型微小構造体は、マイクロマシンの分野に属するものであり、マイクロメートルからミリメートル単位の大きさを有することができる。ある機械装置の部品として組み込まれるために作製される場合は、組み立て時に扱いやすいよう、カンチレバー型微小構造体はメートル単位の大きさを有する場合もある。

本実施の形態では、上記したようなカンチレバー型微小構造体の構成例についてブロック図を用いて説明する。

図9に、カンチレバー型微小構造体を有する微小電気機械式装置の概念図を示す。本発明の微小電気機械式装置11は、半導体素子を有する電気回路部12、および微小構造体を有する構造体部13を有する。電気回路部12は、微小構造体を制御する制御回路14や、外部の制御装置10と通信を行うインターフェース15等を有する。構造体部13は、微小構造体により、センサ16やアクチュエータ17、スイッチ等を有する。アクチュエータとは、信号(主に電気信号)を物理量に変換する構成要素を意味する。

電気回路部12は、構造体部13が得た情報を処理するための中央演算処理装置等を有することも可能である。

外部の制御装置10は、微小電気機械式装置11を制御する信号を送信する、微小電気機械式装置11が得た情報を受信する、または微小電気機械式装置11に駆動電力を供給する等の動作を行う。

本発明はカンチレバー型微小構造体内部に、半導体素子を有し微小構造体を制御する電気回路、および微小構造体を有することを特徴とし、その他の構成等は図9に限定されることはない。

(実施の形態13)

本実施の形態では、微小構造体を有するスイッチを適用するデバイスについて説明する。本発明のスイッチと、伝導路とを組み合わせて、移相器を形成することができる。移相器は、携帯電話器に実装することができる。

また本発明のカンチレバー型の微小構造体を用いて共振器を作製することもできる。図21には、共振器の回路図を示す。共振器は、コイル:Lとコンデンサ:Cと抵抗:Rとが直列に接続され、その間には容量素子Cs1が設けられている。コイル:L及び抵抗:Rの両端にも容量素子Cs2が設けられている。

本発明のスイッチは、このような位相器や共振器に適用することができる。