JP5113609B2 - 表示装置及びその製造方法 - Google Patents

表示装置及びその製造方法 Download PDFInfo

- Publication number

- JP5113609B2 JP5113609B2 JP2008114683A JP2008114683A JP5113609B2 JP 5113609 B2 JP5113609 B2 JP 5113609B2 JP 2008114683 A JP2008114683 A JP 2008114683A JP 2008114683 A JP2008114683 A JP 2008114683A JP 5113609 B2 JP5113609 B2 JP 5113609B2

- Authority

- JP

- Japan

- Prior art keywords

- signal line

- video signal

- opening

- display device

- line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/441—Interconnections, e.g. scanning lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

Landscapes

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

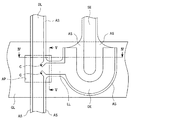

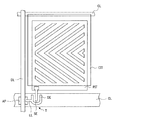

本発明の実施形態に係る表示装置は液晶表示装置であって、走査信号線、映像信号線、薄膜トランジスタ、画素電極、及びコモン電極が形成されたTFT基板と、当該TFT基板と対向し、カラーフィルタが設けられたフィルタ基板と、両基板に挟まれた領域に封入された液晶材料と、を含んで構成される。TFT基板及びフィルタ基板は、いずれもガラス基板などである。

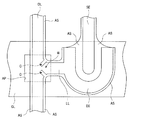

第2実施形態に係る表示装置も第1実施形態と同様の構成(図2〜図5参照)を有し、第2実施形態におけるTFT基板TSの製造方法も第1実施形態と同様の製造方法(図6参照)であるため、ここでは説明を省略する。

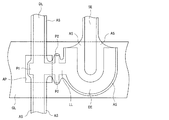

第3実施形態に係る表示装置も第1実施形態と同様の構成(図2〜図5参照)を有し、第3実施形態におけるTFT基板TSの製造方法も第1実施形態と同様の製造方法(図6参照)であるため、ここでは説明を省略する。

第4実施形態に係る表示装置も第1実施形態と同様の構成(図2〜図5参照)を有し、第4実施形態におけるTFT基板TSの製造方法も第1実施形態と同様の製造方法(図6参照)であるため、ここでは説明を省略する。

第5実施形態に係る表示装置も第1実施形態と同様の構成(図2〜図5参照)を有し、第5実施形態におけるTFT基板TSの製造方法も第1実施形態と同様の製造方法(図6参照)であるため、ここでは説明を省略する。

Claims (12)

- 基板上に順次積層された走査信号線、絶縁膜、半導体層及び導電体層を備える表示装置であって、

前記導電体層は、前記走査信号線と前記絶縁膜を介して交差する映像信号線と、薄膜トランジスタのドレイン電極及びソース電極と、前記映像信号線と前記ドレイン電極又は前記ソース電極のいずれか一方とを接続する接続線と、を含んで形成され、

前記半導体層は、少なくとも、前記絶縁膜の、前記映像信号線及び前記接続線が形成される領域より広がった領域を覆うように形成され、

前記走査信号線には、開口部が、前記映像信号線の一部と重なるように形成され、

前記接続線は、前記開口部上において前記映像信号線と接続され、かつ、前記開口部外に延伸して前記ドレイン電極又は前記ソース電極のいずれか一方と接続され、

前記映像信号線又は/及び前記接続線には、前記開口部に対応する領域又はその近傍において、切欠部、突起部又は拡幅部が形成されている、

ことを特徴とする表示装置。 - 前記映像信号線と前記接続線との接続箇所に前記切欠部が形成されていることを特徴とする請求項1に記載の表示装置。

- 前記映像信号線の、前記接続線が接続される側とは反対側に前記突起部が形成されていることを特徴とする請求項1に記載の表示装置。

- 前記接続線の、前記開口部に対応する領域外であって、かつ、前記開口部の近傍に前記突起部が形成されていることを特徴とする請求項1に記載の表示装置。

- 前記映像信号線と前記接続線との接続箇所に前記突起部が形成されていることを特徴とする請求項1に記載の表示装置。

- 前記接続線には、前記映像信号線との接続端から所定距離以内の領域において、前記映像信号線に近づくにつれて幅が徐々に広くなる前記拡幅部が形成されていることを特徴とする請求項1に記載の表示装置。

- 基板上に、走査信号線と、絶縁膜と、半導体層を構成する半導体材料と、導電体層を構成する導電体材料と、が順次積層されてなる積層構造上にパターン形成されたレジスト材をマスクとして前記導電体材料をエッチングすることによって、前記走査信号線と前記絶縁膜を介して交差する映像信号線と、薄膜トランジスタのドレイン電極及びソース電極と、前記映像信号線と前記ドレイン電極又は前記ソース電極のいずれか一方とを接続する接続線と、を含んだ前記導電体層を形成する工程と、

前記導電体層が形成された後、前記導電体層上に残っている前記レジスト材を融解し、該融解された前記レジスト材をマスクとして前記半導体材料をエッチングすることによって、前記半導体層を形成する工程と、

を含み、

前記走査信号線には、開口部が、前記映像信号線の一部と重なるように形成され、

前記接続線は、前記開口部上において前記映像信号線と接続され、かつ、前記開口部外に延伸して前記ドレイン電極又は前記ソース電極のいずれか一方と接続され、

前記レジスト材は、前記レジスト材を融解した場合の、前記開口部における前記レジスト材の広がりを制御するための切欠部、突起部又は拡幅部を前記映像信号線又は/及び前記接続線が備えるようにパターン形成される、

ことを特徴とする表示装置の製造方法。 - 前記映像信号線と前記接続線との接続箇所に前記切欠部が形成されるように、前記レジスト材がパターン形成されることを特徴とする請求項7に記載の表示装置の製造方法。

- 前記映像信号線の、前記接続線が接続される側とは反対側に前記突起部が形成されるように、前記レジスト材がパターン形成されることを特徴とする請求項7に記載の表示装置の製造方法。

- 前記接続線の、前記開口部に対応する領域外であって、かつ、前記開口部の近傍に前記突起部が形成されるように、前記レジスト材がパターン形成されることを特徴とする請求項7に記載の表示装置の製造方法。

- 前記映像信号線と前記接続線との接続箇所に前記突起部が形成されるように、前記レジスト材がパターン形成されることを特徴とする請求項7に記載の表示装置の製造方法。

- 前記接続線の、前記映像信号線との接続端から所定距離以内の領域において、前記映像信号線に近づくにつれて幅が徐々に広くなる前記拡幅部が形成されるように、前記レジスト材がパターン形成されることを特徴とする請求項7に記載の表示装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008114683A JP5113609B2 (ja) | 2008-04-24 | 2008-04-24 | 表示装置及びその製造方法 |

| US12/429,244 US8059077B2 (en) | 2008-04-24 | 2009-04-24 | Display device and manufacturing method of display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008114683A JP5113609B2 (ja) | 2008-04-24 | 2008-04-24 | 表示装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009265348A JP2009265348A (ja) | 2009-11-12 |

| JP2009265348A5 JP2009265348A5 (ja) | 2010-08-19 |

| JP5113609B2 true JP5113609B2 (ja) | 2013-01-09 |

Family

ID=41379156

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008114683A Active JP5113609B2 (ja) | 2008-04-24 | 2008-04-24 | 表示装置及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8059077B2 (ja) |

| JP (1) | JP5113609B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9568794B2 (en) | 2010-12-20 | 2017-02-14 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| CN103137558B (zh) * | 2013-02-06 | 2016-10-05 | 京东方科技集团股份有限公司 | 一种tn型阵列基板及其制作方法、显示装置 |

| JP6278633B2 (ja) * | 2013-07-26 | 2018-02-14 | 三菱電機株式会社 | 薄膜トランジスタアレイ基板およびその製造方法、並びに、液晶表示装置およびその製造方法 |

| US10539839B2 (en) | 2015-02-12 | 2020-01-21 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| CN105405852B (zh) * | 2016-01-05 | 2019-04-23 | 京东方科技集团股份有限公司 | 阵列基板及其制造方法、显示装置 |

| CN109473449A (zh) * | 2018-11-07 | 2019-03-15 | 惠科股份有限公司 | 跨线结构及其制作方法、显示面板 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2762820B2 (ja) * | 1992-02-21 | 1998-06-04 | 株式会社日立製作所 | 薄膜トランジスタマトリクス及びそれを用いた液晶表示装置 |

| JPH08146462A (ja) * | 1994-11-18 | 1996-06-07 | Hitachi Ltd | 液晶表示装置及びその製造方法 |

| JPH09258244A (ja) | 1996-03-22 | 1997-10-03 | Hitachi Ltd | 液晶表示装置 |

| JPH10221704A (ja) * | 1997-02-07 | 1998-08-21 | Sharp Corp | 反射型液晶表示装置およびその製造方法 |

| JP3335567B2 (ja) * | 1997-10-17 | 2002-10-21 | シャープ株式会社 | アクティブマトリクス型液晶表示装置およびその欠陥修正方法 |

| JP4211250B2 (ja) * | 2000-10-12 | 2009-01-21 | セイコーエプソン株式会社 | トランジスタ及びそれを備える表示装置 |

| JP4410951B2 (ja) * | 2001-02-27 | 2010-02-10 | Nec液晶テクノロジー株式会社 | パターン形成方法および液晶表示装置の製造方法 |

| US7858415B2 (en) * | 2005-04-28 | 2010-12-28 | Sharp Kabushiki Kaisha | Production methods of pattern thin film, semiconductor element, and circuit substrate, and resist material, semiconductor element, and circuit substrate |

| US7330235B2 (en) * | 2005-11-08 | 2008-02-12 | Chunghwa Picture Tubes, Ltd. | Liquid crystal display panel having spacers wedged in three-layered conductive lines and manufacturing method thereof |

-

2008

- 2008-04-24 JP JP2008114683A patent/JP5113609B2/ja active Active

-

2009

- 2009-04-24 US US12/429,244 patent/US8059077B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009265348A (ja) | 2009-11-12 |

| US8059077B2 (en) | 2011-11-15 |

| US20090295696A1 (en) | 2009-12-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101294237B1 (ko) | 프린지 필드 스위칭 모드 액정표시장치용 어레이 기판 및 이의 제조방법 | |

| KR20080107821A (ko) | 프린지 필드 스위칭 모드 액정표시장치용 어레이 기판 및이의 제조 방법 | |

| CN102096251A (zh) | 有源矩阵基板及具备该有源矩阵基板的液晶显示装置 | |

| JP4693781B2 (ja) | アクティブマトリクス基板及び表示装置 | |

| KR101634635B1 (ko) | 표시 장치 | |

| JP5113609B2 (ja) | 表示装置及びその製造方法 | |

| JP2010079075A (ja) | 透過型液晶表示装置 | |

| JP4644179B2 (ja) | 液晶表示装置用アレイ基板及びその製造方法 | |

| KR20140122623A (ko) | 박막 트랜지스터 표시판 및 그 제조 방법 | |

| US8309959B2 (en) | Display device having opening portion with different widths | |

| JP2009093176A (ja) | 液晶表示装置 | |

| KR20140053667A (ko) | 박막 트랜지스터 표시판 및 그 제조 방법 | |

| JP2010074030A (ja) | 薄膜トランジスタおよび電気光学装置 | |

| KR20110072042A (ko) | 액정 표시 장치 및 이의 제조 방법 | |

| CN110176429B (zh) | 一种阵列基板的制作方法及阵列基板、显示面板 | |

| TW201523103A (zh) | 液晶顯示器及其製造方法 | |

| KR101875937B1 (ko) | 액정표시장치 | |

| KR20120015162A (ko) | 액정표시장치 및 그 제조방법 | |

| JP6234232B2 (ja) | 液晶表示パネルおよびそのリペア方法 | |

| JP5081461B2 (ja) | 表示装置の製造方法 | |

| JP2009271105A (ja) | 液晶表示装置の製造方法 | |

| KR20090073709A (ko) | 씨오티 구조 횡전계형 액정표시장치용 어레이 기판의 제조방법 | |

| JP2008089646A (ja) | 表示装置 | |

| JP2004333673A (ja) | 表示装置 | |

| JP2008170987A (ja) | 面内スイッチング型液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100706 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100706 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120907 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120918 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121012 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151019 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5113609 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |