JP5094232B2 - 半導体装置を内包する用紙およびその作製方法 - Google Patents

半導体装置を内包する用紙およびその作製方法 Download PDFInfo

- Publication number

- JP5094232B2 JP5094232B2 JP2007164594A JP2007164594A JP5094232B2 JP 5094232 B2 JP5094232 B2 JP 5094232B2 JP 2007164594 A JP2007164594 A JP 2007164594A JP 2007164594 A JP2007164594 A JP 2007164594A JP 5094232 B2 JP5094232 B2 JP 5094232B2

- Authority

- JP

- Japan

- Prior art keywords

- paper

- layer

- semiconductor device

- film

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 206

- 238000000034 method Methods 0.000 title description 82

- 238000004519 manufacturing process Methods 0.000 title description 33

- 238000007789 sealing Methods 0.000 claims description 59

- 239000000463 material Substances 0.000 claims description 44

- 239000010409 thin film Substances 0.000 claims description 10

- 239000004020 conductor Substances 0.000 claims description 5

- 239000010410 layer Substances 0.000 description 253

- 239000010408 film Substances 0.000 description 197

- 239000000758 substrate Substances 0.000 description 62

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 48

- 229910052710 silicon Inorganic materials 0.000 description 48

- 239000010703 silicon Substances 0.000 description 48

- 239000007789 gas Substances 0.000 description 38

- 230000008569 process Effects 0.000 description 32

- 239000012535 impurity Substances 0.000 description 30

- 229910052721 tungsten Inorganic materials 0.000 description 20

- 238000012545 processing Methods 0.000 description 19

- 229920005989 resin Polymers 0.000 description 19

- 239000011347 resin Substances 0.000 description 19

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 19

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 18

- 239000010937 tungsten Substances 0.000 description 18

- 239000004642 Polyimide Substances 0.000 description 17

- 230000006870 function Effects 0.000 description 17

- 229920001721 polyimide Polymers 0.000 description 17

- 238000004544 sputter deposition Methods 0.000 description 17

- 230000005540 biological transmission Effects 0.000 description 16

- 230000015572 biosynthetic process Effects 0.000 description 16

- 229910021417 amorphous silicon Inorganic materials 0.000 description 15

- 229910021419 crystalline silicon Inorganic materials 0.000 description 14

- 229910052814 silicon oxide Inorganic materials 0.000 description 14

- 239000010936 titanium Substances 0.000 description 14

- 239000003990 capacitor Substances 0.000 description 13

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 13

- 239000011521 glass Substances 0.000 description 12

- 229910052751 metal Inorganic materials 0.000 description 12

- 239000002184 metal Substances 0.000 description 12

- 238000000206 photolithography Methods 0.000 description 12

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 11

- 238000002425 crystallisation Methods 0.000 description 11

- 229910052739 hydrogen Inorganic materials 0.000 description 11

- 239000001257 hydrogen Substances 0.000 description 11

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 11

- 230000008025 crystallization Effects 0.000 description 10

- 230000001678 irradiating effect Effects 0.000 description 10

- 238000005229 chemical vapour deposition Methods 0.000 description 9

- 238000005530 etching Methods 0.000 description 9

- 238000005247 gettering Methods 0.000 description 9

- 238000007726 management method Methods 0.000 description 9

- 229910052760 oxygen Inorganic materials 0.000 description 9

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 8

- 239000010949 copper Substances 0.000 description 8

- 229910052581 Si3N4 Inorganic materials 0.000 description 7

- 239000000853 adhesive Substances 0.000 description 7

- 230000001070 adhesive effect Effects 0.000 description 7

- 239000012790 adhesive layer Substances 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 7

- 229910052732 germanium Inorganic materials 0.000 description 7

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 7

- 238000010438 heat treatment Methods 0.000 description 7

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 7

- 229910052719 titanium Inorganic materials 0.000 description 7

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 6

- 239000011651 chromium Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 239000003822 epoxy resin Substances 0.000 description 6

- 239000001301 oxygen Substances 0.000 description 6

- 229920000647 polyepoxide Polymers 0.000 description 6

- 230000004888 barrier function Effects 0.000 description 5

- 238000004891 communication Methods 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 238000012937 correction Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 150000002500 ions Chemical class 0.000 description 5

- 230000010355 oscillation Effects 0.000 description 5

- 238000003825 pressing Methods 0.000 description 5

- 239000002994 raw material Substances 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 4

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 4

- 229920002472 Starch Polymers 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 239000013078 crystal Substances 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- 230000003647 oxidation Effects 0.000 description 4

- 238000007254 oxidation reaction Methods 0.000 description 4

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 4

- 239000002356 single layer Substances 0.000 description 4

- 239000000243 solution Substances 0.000 description 4

- 235000019698 starch Nutrition 0.000 description 4

- 239000008107 starch Substances 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical group [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 3

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 3

- 229910000831 Steel Inorganic materials 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 125000004429 atom Chemical group 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 229910052799 carbon Inorganic materials 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- 238000005520 cutting process Methods 0.000 description 3

- 230000006378 damage Effects 0.000 description 3

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 3

- 238000000605 extraction Methods 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- -1 halogen fluoride Chemical class 0.000 description 3

- 239000011229 interlayer Substances 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 238000002360 preparation method Methods 0.000 description 3

- 239000010948 rhodium Substances 0.000 description 3

- 229910000077 silane Inorganic materials 0.000 description 3

- 239000010959 steel Substances 0.000 description 3

- 229920001187 thermosetting polymer Polymers 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 230000027455 binding Effects 0.000 description 2

- 238000004364 calculation method Methods 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 2

- 238000007865 diluting Methods 0.000 description 2

- 239000002019 doping agent Substances 0.000 description 2

- 229910000078 germane Inorganic materials 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 230000001771 impaired effect Effects 0.000 description 2

- 238000007641 inkjet printing Methods 0.000 description 2

- 229910052741 iridium Inorganic materials 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- 238000000608 laser ablation Methods 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 230000009149 molecular binding Effects 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- 229910052762 osmium Inorganic materials 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 238000007639 printing Methods 0.000 description 2

- 229910052703 rhodium Inorganic materials 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- 238000007650 screen-printing Methods 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 125000001424 substituent group Chemical group 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 230000003313 weakening effect Effects 0.000 description 2

- 229910052724 xenon Inorganic materials 0.000 description 2

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 2

- QTBSBXVTEAMEQO-UHFFFAOYSA-M Acetate Chemical compound CC([O-])=O QTBSBXVTEAMEQO-UHFFFAOYSA-M 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 1

- 229920000875 Dissolving pulp Polymers 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- 229910019142 PO4 Inorganic materials 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004743 Polypropylene Substances 0.000 description 1

- 239000004793 Polystyrene Substances 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910004283 SiO 4 Inorganic materials 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910052775 Thulium Inorganic materials 0.000 description 1

- XTXRWKRVRITETP-UHFFFAOYSA-N Vinyl acetate Chemical compound CC(=O)OC=C XTXRWKRVRITETP-UHFFFAOYSA-N 0.000 description 1

- 229910052769 Ytterbium Inorganic materials 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- 235000013405 beer Nutrition 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000003575 carbonaceous material Substances 0.000 description 1

- 125000002091 cationic group Chemical group 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 230000000052 comparative effect Effects 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 238000003851 corona treatment Methods 0.000 description 1

- 125000004122 cyclic group Chemical group 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 125000001153 fluoro group Chemical group F* 0.000 description 1

- 229910052839 forsterite Inorganic materials 0.000 description 1

- 230000005484 gravity Effects 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000009616 inductively coupled plasma Methods 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 239000005001 laminate film Substances 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- HCWCAKKEBCNQJP-UHFFFAOYSA-N magnesium orthosilicate Chemical compound [Mg+2].[Mg+2].[O-][Si]([O-])([O-])[O-] HCWCAKKEBCNQJP-UHFFFAOYSA-N 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 1

- 229910052753 mercury Inorganic materials 0.000 description 1

- 150000002736 metal compounds Chemical class 0.000 description 1

- 229910001507 metal halide Inorganic materials 0.000 description 1

- 150000005309 metal halides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- QKCGXXHCELUCKW-UHFFFAOYSA-N n-[4-[4-(dinaphthalen-2-ylamino)phenyl]phenyl]-n-naphthalen-2-ylnaphthalen-2-amine Chemical compound C1=CC=CC2=CC(N(C=3C=CC(=CC=3)C=3C=CC(=CC=3)N(C=3C=C4C=CC=CC4=CC=3)C=3C=C4C=CC=CC4=CC=3)C3=CC4=CC=CC=C4C=C3)=CC=C21 QKCGXXHCELUCKW-UHFFFAOYSA-N 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 239000012299 nitrogen atmosphere Substances 0.000 description 1

- 125000000962 organic group Chemical group 0.000 description 1

- SYQBFIAQOQZEGI-UHFFFAOYSA-N osmium atom Chemical compound [Os] SYQBFIAQOQZEGI-UHFFFAOYSA-N 0.000 description 1

- NBIIXXVUZAFLBC-UHFFFAOYSA-K phosphate Chemical compound [O-]P([O-])([O-])=O NBIIXXVUZAFLBC-UHFFFAOYSA-K 0.000 description 1

- 239000010452 phosphate Substances 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229920003023 plastic Polymers 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920002401 polyacrylamide Polymers 0.000 description 1

- 229920002239 polyacrylonitrile Polymers 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920001155 polypropylene Polymers 0.000 description 1

- 229920002223 polystyrene Polymers 0.000 description 1

- 239000004800 polyvinyl chloride Substances 0.000 description 1

- 229920000915 polyvinyl chloride Polymers 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 239000012744 reinforcing agent Substances 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 239000010979 ruby Substances 0.000 description 1

- 229910001750 ruby Inorganic materials 0.000 description 1

- 239000012266 salt solution Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000007779 soft material Substances 0.000 description 1

- 238000007711 solidification Methods 0.000 description 1

- 230000008023 solidification Effects 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229920003002 synthetic resin Polymers 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- 229920002803 thermoplastic polyurethane Polymers 0.000 description 1

- 229920005992 thermoplastic resin Polymers 0.000 description 1

- FQFKTKUFHWNTBN-UHFFFAOYSA-N trifluoro-$l^{3}-bromane Chemical compound FBr(F)F FQFKTKUFHWNTBN-UHFFFAOYSA-N 0.000 description 1

- JOHWNGGYGAVMGU-UHFFFAOYSA-N trifluorochlorine Chemical compound FCl(F)F JOHWNGGYGAVMGU-UHFFFAOYSA-N 0.000 description 1

- 229920006163 vinyl copolymer Polymers 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Landscapes

- Recrystallisation Techniques (AREA)

- Paper (AREA)

- Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Description

まず、半導体装置を抄き込んだ紙の構成について説明する。本明細書では、半導体装置として、無線で通信を行う手段を有し、RFIDの機能を備えた半導体装置を例に取り説明する。

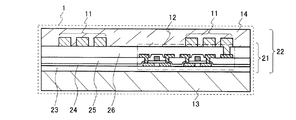

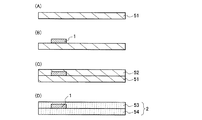

図2〜図5を用いて、半導体装置1の構成および作製方法を説明する。図2は、半導体装置1の模式的な断面図であり、図3は、半導体装置1の外観構造を説明する図である。図4および図5は、半導体装置1の作製方法を示す断面図である。

素子層21を作製するための基板31を用意する。基板31は、基板31には、薄膜トランジスタを製造するためときに必要な剛性と、プロセス温度に耐えうる耐熱性を備えた基板を選択する。例えば、基板31として、ガラス基板、石英基板、シリコン基板、金属基板、ステンレス基板を用いることができる。

次に、図8に示す断面図を用いて、半導体装置1を紙に抄き込む方法を説明する。本実施形態の紙は、多層紙として形成され、紙層と紙層の間に半導体装置1が抄き込まれる。

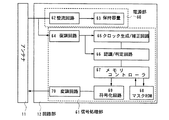

次に、半導体装置1の回路構成例について説明する。図9に、半導体装置1のブロック回路図を示す。

半導体装置1の別の回路構成例について説明する。ここでは、半導体装置1に暗号処理機能を備えた半導体装置1の回路構成例を示す。図10は、半導体装置1のブロック回路図である。

本発明の半導体装置を抄き込んだ紙はあらゆる紙媒体に使用できる。特に、本発明の紙は、紙からRFタグを取り出そうとすると、紙にその痕跡が残るという特徴をいかして、偽造防止が要求されるあらゆる紙媒体に使用することができる。例えば、紙幣、戸籍謄本、住民票、パスポート、免許証、身分証、会員証、鑑定書、診察券、定期券、手形、小切手、貨物引換証、船貨証券、倉庫証券、株券、債券、商品券、チケット、抵当証券などである。

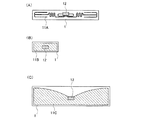

下層の紙層、上層の紙層共に坪量が28g/m2になるように湿紙125、126を用意した。下層の湿紙125の上面に酢酸エステル化澱粉を散布した後、下層の湿紙125の上面に厚さ50μmの半導体装置1を置き、上層の湿紙126を下層の湿紙125と重ねた。重ねた湿紙125と湿紙126をプレス機のステージ(スチール製)128にのせた。湿紙126の上面に濾紙127を置いた状態で、プレス機のステージ128とプレス板(スチール製)129で湿紙125と湿紙126を挟み、プレスした(図12(A)参照)。プレス時間は2分、圧力は20.6kPaとした。プレスされた湿紙125、126を乾燥機で100℃の温度で100秒間乾燥させて、紙層130と紙層131でなる多層紙132を作製した(図12(B)参照)。

紙の坪量を30g/m2とし、半導体装置1の厚さを26μmとした。他は、紙Aと同様の条件で紙132を抄いた。紙Bも、紙Aと同様に、濾紙127を置かなかった紙層130の表面は半導体装置1の凹凸は現れていなく、平坦であり、他方の紙層131の表面は半導体装置1の凹凸が指先で若干感じられる程度の高い平滑性の面に形成された。

紙Cは比較例であり、半導体装置1の厚さが135μmである他は、紙Aと同じ条件で紙を形成した。紙Cは、半導体装置1を含まない部分の厚さt1が100μmであり、半導体装置1を含む部分の厚さt2が210μmであり、厚さt2とt1の差分は110μmである。紙Cの場合は、紙層130、131の各々の厚さ(約50μm)よりも厚い半導体装置1を抄き込んだため、半導体装置1の厚さと同程度のでっぱりが生じたが、濾紙127を置かなかった紙層130の表面は半導体装置1による凹凸は現れていなかった。

2 紙

11 アンテナ

11A、11B、11C アンテナ

12 回路部

13 可撓性基材

14 封止層

21 素子層

22 積層体

23〜26 絶縁膜

31 基板

32 剥離層

33 半導体膜

34 第1の導電層

35 不純物領域

36 チャネル形成領域

37 第2の導電層

40 開口部

41 支持基材

51、52 湿紙

53 紙層

54 紙層

60 電源部

61 信号処理部

62 整流回路

63 保持容量

64 復調回路

65 クロック生成/補正回路

66 認識/判定回路

67 メモリコントローラ

68 マスクROM

69 符号化回路

70 変調回路

76 CPUインターフェース

77 制御レジスタ

78 コード抽出回路

79 符号化回路

80 演算回路

81 アナログ部

82 CPU

83 ROM

83a 秘密鍵

84 RAM

85 コントローラ

88 共振回路

89 電源回路

90 リセット回路

91 クロック生成回路

92 復調回路

93 変調回路

94 電源管理回路

96 受信信号

96a 暗号文データ

97 送信信号

97a 復号文データ

98 受信データ

99 送信データ

111 無記名債券

112 証書類

113 ラベル台紙

114 ラベル

115 ボックス

116 タグ

117 書籍

125、126 湿紙

127 濾紙

128 ステージ

129 プレス板

130、131 紙層

132 多層紙

301 半導体装置

311 アンテナ

312 回路部

313 可撓性基材

313a 接着層

313b 基材フィルム

314 封止層

321 素子層

322 積層体

400 ガラス基板

401 酸化窒化シリコン膜

402 タングステン膜

403 酸化シリコン膜

404 酸化窒化シリコン膜

405 酸化窒化シリコン膜

406 結晶性シリコン膜

407〜409 半導体層

407a、407b p型高濃度不純物領域

407c チャネル形成領域

408a、408b n型高濃度不純物領域

408c チャネル形成領域

408e、408d n型低濃度不純物領域

409a、409b n型高濃度不純物領域

409c チャネル形成領域

409e、409d n型低濃度不純物領域

410 酸化窒化シリコン膜

412 n型不純物領域

413〜415 第1導電層

416〜419 n型低濃度不純物領域

423〜425 絶縁層

426 酸化窒化シリコン膜

427 酸化窒化シリコン膜

428〜433 第2導電層

435 ポリイミド

436 導電層

437 ポリイミド

439 開口部

440 UV剥離テープ

Claims (4)

- 半導体装置が内包された用紙であって、

前記半導体装置は、封止層と、素子層と、可撓性の基材とを有し、

前記素子層は、薄膜トランジスタを有する回路と、前記回路に電気的に接続されたアンテナとを有し、

前記素子層は、前記封止層と、前記可撓性の基材とに挟まれており、

前記アンテナは、導体表面に凹凸を有し、

前記凹凸は、前記アンテナの導体表面と重なる領域において、外光が乱反射するように設けられることを特徴とする半導体装置を内包する用紙。 - 半導体装置が内包された用紙であって、

前記半導体装置は、第1の紙層と第2の紙層の間に挟まれ、封止層と、素子層と、可撓性の基材とを有し、

前記素子層は、薄膜トランジスタを有する回路と、前記回路に電気的に接続されたアンテナとを有し、

前記素子層は、前記封止層と、前記可撓性の基材とに挟まれており、

前記アンテナは、導体表面に凹凸を有し、

前記凹凸は、前記アンテナの導体表面と重なる領域において、外光が乱反射するように設けられることを特徴とする半導体装置を内包する用紙。 - 請求項2において、

前記半導体装置の厚さは、前記第1の紙層の厚さ又は前記第2の紙層の厚さより薄いことを特徴とする半導体装置を内包する用紙。 - 請求項1乃至3のいずれか一項において、

前記半導体装置が内包された用紙の少なくとも一方の表面は、平坦性を有していることを特徴とする半導体装置を内包する用紙。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007164594A JP5094232B2 (ja) | 2006-06-26 | 2007-06-22 | 半導体装置を内包する用紙およびその作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006175678 | 2006-06-26 | ||

| JP2006175678 | 2006-06-26 | ||

| JP2007164594A JP5094232B2 (ja) | 2006-06-26 | 2007-06-22 | 半導体装置を内包する用紙およびその作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008033907A JP2008033907A (ja) | 2008-02-14 |

| JP2008033907A5 JP2008033907A5 (ja) | 2010-05-27 |

| JP5094232B2 true JP5094232B2 (ja) | 2012-12-12 |

Family

ID=39123201

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007164594A Expired - Fee Related JP5094232B2 (ja) | 2006-06-26 | 2007-06-22 | 半導体装置を内包する用紙およびその作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5094232B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101925772B1 (ko) * | 2008-07-10 | 2018-12-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 발광 장치 및 전자 기기 |

| JP5586920B2 (ja) * | 2008-11-20 | 2014-09-10 | 株式会社半導体エネルギー研究所 | フレキシブル半導体装置の作製方法 |

| WO2011021248A1 (ja) * | 2009-08-20 | 2011-02-24 | 国立大学法人東京大学 | 半導体基板、半導体層の製造方法、半導体基板の製造方法、半導体素子、発光素子、表示パネル、電子素子、太陽電池素子及び電子機器 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2634482B2 (ja) * | 1990-06-12 | 1997-07-23 | 三田工業株式会社 | 画像形成装置のクリーニング方法 |

| JP3925101B2 (ja) * | 2001-04-19 | 2007-06-06 | 特種製紙株式会社 | 偽造防止用シート状物の製造方法 |

| JP5041681B2 (ja) * | 2004-06-29 | 2012-10-03 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4749062B2 (ja) * | 2004-07-16 | 2011-08-17 | 株式会社半導体エネルギー研究所 | 薄膜集積回路を封止する装置及びicチップの作製方法 |

| JP4563122B2 (ja) * | 2004-09-14 | 2010-10-13 | 株式会社中戸研究所 | バリア性積層フィルム及びその製造方法 |

| JP5072210B2 (ja) * | 2004-10-05 | 2012-11-14 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4799130B2 (ja) * | 2004-11-09 | 2011-10-26 | 株式会社半導体エネルギー研究所 | Icチップおよびicチップの作製方法 |

| JP4811561B2 (ja) * | 2005-04-19 | 2011-11-09 | 大日本印刷株式会社 | 無効化可能非接触icタグ |

-

2007

- 2007-06-22 JP JP2007164594A patent/JP5094232B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008033907A (ja) | 2008-02-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2038818B1 (en) | Paper including semiconductor device and manufacturing method thereof | |

| JP2022069697A (ja) | 半導体装置 | |

| JP5094149B2 (ja) | 感圧紙、及び感圧紙を用いた筆跡記録システム | |

| CN101088158B (zh) | 半导体装置 | |

| US7906847B2 (en) | Semiconductor device | |

| US20060270175A1 (en) | Method for manufacturing antenna and method for manufacturing semiconductor device | |

| CN101189625A (zh) | 半导体器件及其制造方法以及天线的制造方法 | |

| TW200903665A (en) | Method for manufacturing semiconductor device | |

| KR101241066B1 (ko) | 반도체 장치 제조 방법 | |

| JP5094232B2 (ja) | 半導体装置を内包する用紙およびその作製方法 | |

| JP5089033B2 (ja) | 半導体装置の作製方法 | |

| JP5030470B2 (ja) | 半導体装置の作製方法 | |

| JP4908936B2 (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100409 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100409 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120417 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120612 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120703 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120821 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120911 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120918 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150928 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150928 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |