JP5014591B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP5014591B2 JP5014591B2 JP2005150304A JP2005150304A JP5014591B2 JP 5014591 B2 JP5014591 B2 JP 5014591B2 JP 2005150304 A JP2005150304 A JP 2005150304A JP 2005150304 A JP2005150304 A JP 2005150304A JP 5014591 B2 JP5014591 B2 JP 5014591B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- region

- semiconductor device

- gate electrode

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Description

なお、本発明に関連する公知文献としては、例えば特開2004−221554号公報(特許文献1)、及び特開2001−168219号公報(特許文献2)がある。

しかしながら、このようなデータの書き込み/消去においては、以下に示す問題が生じる。

〈特許文献1〉

上記特許文献1には、消去時に書き込みと同様にチャネル電流を流すことで、ホットエレクトロンとホットホールの注入位置をほぼ同じにできる旨の記載がある。しかしながら、この場合、消去動作に1〜10uA/bit程度の電流が必要であり、(a)共通ワード線内を分割して消去するか、(b)電源容量を増強するか、が必要である。(a)の場合は消去時間の増加が懸念され、(b)の場合は回路面積の増加が必要である。

(1)電荷蓄積層の一部の誘電率を変える方法では、形成時に基板側の絶縁膜に欠陥が発生するため、信頼性が著しく低下する恐れがある。

(2)チャネル形成領域に段差を形成する方法では、同文献の第6実施形態及び第7実施形態(段落番号

本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかになるであろう。

前記半導体基板は、第1の面と、前記第1の面から深さ方向に向かって前記第1の面よりも低い第2の面とを有し、

前記不揮発性記憶素子は、前記第1の面上に第1の絶縁膜を介在して設けられたコントロールゲート電極と、

前記第1の絶縁膜とは異なる膜からなる第2の絶縁膜、及び前記第2の絶縁膜上に設けられた電荷蓄積膜を含む積層膜と、

前記コントロールゲート電極と隣り合って前記第2の面上に前記積層膜を介在して設けられたメモリゲート電極と、

前記コントロールゲート電極に整合して前記半導体基板に設けられた第1の半導体領域と、

前記メモリゲート電極に整合して前記半導体基板に設けられた第2の半導体領域と、を有する。

(a)半導体基板の第1の面上に第1の絶縁膜を介在してコントロールゲート電極を形成する工程と、

(b)前記(a)工程の後、前記半導体基板をエッチングして前記第1の面から深さ方向に前記第1の面よりも低い第2の面を形成する工程と、

(c)前記(b)工程の後、前記第2の面上に、前記第2の面側から順次積層された第2の絶縁膜及び電荷蓄積膜を含む積層膜を形成する工程と、

(d)前記(c)工程の後、前記第2の面上に前記積層膜を介在してメモリゲート電極を形成する工程と、を有する。

本発明によれば、不揮発性記憶素子において、オフリーク電流の増大を招くことなく、書き換え耐性及びデータ保持特性の向上、並びに動作電圧の低電圧化を図ることができる。

本発明の実施例を説明する前に、実施例における用語の意味を説明すると次の通りである。

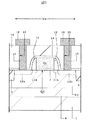

図1は、半導体装置の概略構成を示す模式的断面図である。

図2は、図1の一部(低耐圧MISFETの部分)を拡大した模式的断面図である。

図3は、図1の一部(高耐圧MISFETの部分)を拡大した模式的断面図である。

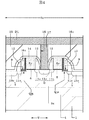

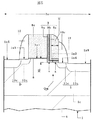

図4は、図1の一部(不揮発性記憶素子の部分)を拡大した模式的断面図である。

図5は、図4を簡略化して拡大した模式的断面図である。

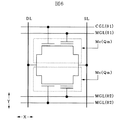

図6は、図4の不揮発性記憶素子の等価回路図である。

図7乃至図24は、半導体装置の製造工程を示す模式的断面図である。

なお、図12は、図11の一部を拡大した模式的断面図である。

まず、例えば比抵抗が10[Ωcm]程度のp型単結晶シリコンからなるシリコン基板(基板1)を準備し、その後、基板1の主面に、活性領域(2a,2b,2c)を区画するための素子分離領域3を形成する(図7参照)。素子分離領域3は、例えば周知のSTI技術で形成する。STI技術による素子分離領域3は、まず、基板1の主面に浅溝(例えば深さが300nm程度の溝)を形成し、その後、前記浅溝の内部を埋め込むようにして基板1の主面上に例えば酸化シリコン膜からなる絶縁膜をCVD法で形成し、その後、前記浅溝の内部に前記絶縁膜が選択的に残るように基板1上の前記絶縁膜をCMP法で除去することによって形成される。

Claims (16)

- 半導体基板に形成された不揮発性記憶素子を有する半導体装置であって、

前記半導体基板は、第1の面と、前記第1の面から深さ方向に向かって前記第1の面よりも低い第2の面とを有し、

前記不揮発性記憶素子は、

前記第1の面上に第1の絶縁膜を介在して設けられたコントロールゲート電極と、

前記第1の絶縁膜とは異なる膜からなる第2の絶縁膜、及び前記第2の絶縁膜上に設けられた電荷蓄積膜を含む積層膜と、

前記コントロールゲート電極と隣り合って前記第2の面上に前記積層膜を介在して設けられたメモリゲート電極と、

前記コントロールゲート電極に整合して前記半導体基板に設けられた第1の半導体領域と、

前記メモリゲート電極に整合して前記半導体基板に設けられた第2の半導体領域と、を有し、

前記第1の半導体領域は、前記コントロールゲート電極に整合して形成され、かつ、前記第1の面及び前記第1の面から深さ方向に向かって前記第1の面よりも低い第3の面に亘って設けられ、

前記第2の半導体領域は、前記メモリゲート電極に整合して形成され、かつ、前記第2の面及び前記第2の面から深さ方向に向かって前記第2の面よりも低い第4の面に亘って設けられ、

前記第2の面は、前記半導体基板の深さ方向に向かって前記第3の面よりも低い位置に形成され、

前記不揮発性記憶素子のデータ書き込みは、前記半導体基板側から前記電荷蓄積膜中にホットエレクトロンを注入させることによって行われ、

前記不揮発性記憶素子のデータ消去は、前記半導体基板側から前記電荷蓄積膜中にホットホールを注入させることによって行われ、

前記ホットエレクトロンは、主に前記コントロールゲート電極に近い前記電荷蓄積膜中に注入され、

前記ホットホールは、主に前記第2半導体領域に近い前記電荷蓄積膜中に注入されることを特徴とする半導体装置。 - 請求項1に記載の半導体装置において、

前記第1及び第2の絶縁膜は、夫々の膜厚が異なっていることを特徴とする半導体装置。 - 請求項1に記載の半導体装置において、

前記第2の絶縁膜は、前記第1の絶縁膜よりも膜厚が厚いことを特徴とする半導体装置。 - 請求項1に記載の半導体装置において、

前記第2の絶縁膜は、前記第1の面と前記第2の面との段差部における壁面を覆うようにして、前記第2の面から前記コントロールゲート電極の側面に亘って形成されていることを特徴とする半導体装置。 - 請求項1に記載の半導体装置において、

前記積層膜は、前記第1の面と前記第2の面との段差部における壁面を覆うようにして、前記第2の面から前記コントロールゲート電極の側面に亘って形成され、

前記コントロールゲート電極と前記メモリゲート電極は、前記積層膜によって電気的に分離されていることを特徴とする半導体装置。 - 請求項1に記載の半導体装置において、

前記第2の面と前記第1の面との高低差は、10〜30[nm]の範囲内であることを特徴とする半導体装置。 - 請求項1に記載の半導体装置において、

前記第1の半導体領域はドレイン領域であり、前記第2の半導体領域はソース領域であることを特徴とする半導体装置。 - 請求項1に記載の半導体装置において、

前記第1及び第2の絶縁膜は酸化膜であり、前記電荷蓄積膜は窒化膜であることを特徴とする半導体装置。 - 請求項1に記載の半導体装置において、

前記積層膜は、前記電荷蓄積膜上に形成された第3の絶縁膜を含み、

前記第1乃至第3の絶縁膜は酸化膜であり、前記電荷蓄積膜は窒化膜であることを特徴とする半導体装置。 - 不揮発性記憶素子を有する半導体装置の製造方法であって、

(a)半導体基板の第1の面上に第1の絶縁膜を介在し、一方の側壁面側に第1の領域を有し、かつ、他方の側壁側に第2の領域を有するコントロールゲート電極を形成する工程と、

(b)前記(a)工程の後、前記半導体基板上に、前記コントロールゲート電極の前記第2の領域を覆い、かつ、前記第1の領域上に開口部を有するパターンからなるマスクを形成する工程と、

(c)前記(b)工程の後、前記マスクが形成された状態で、前記半導体基板をエッチングすることにより、前記第1の面から深さ方向に前記第1の面よりも低い第2の面を形成する工程と、

(d)前記(c)工程の後、前記第2の面上に、前記第2の面側から順次積層された第2の絶縁膜及び電荷蓄積膜を含む積層膜を形成する工程と、

(e)前記(d)工程の後、前記第2の面上に前記積層膜を介在してメモリゲート電極を形成する工程と、

(f)前記(e)工程の後、熱酸化処理を施して前記半導体基板に犠牲酸化膜を形成する工程と、

(g)前記(f)工程の後、前記犠牲酸化膜で覆われた前記半導体基板に不純物をイオン注入して、前記コントロールゲート電極に整合した第1の半導体領域と、前記メモリゲート電極に整合した第2の半導体領域とを形成する工程と、

(h)前記(g)工程の後、前記犠牲酸化膜を洗浄にて除去する工程と、を有し、

前記(h)工程における洗浄により前記犠牲酸化膜が除去されることにより、前記第1の面から深さ方向に向かって前記第1の面よりも低い第3の面、及び、前記第2の面から深さ方向に向かって前記第2の面よりも低い第4の面が形成され、

前記第1の半導体領域は、前記第1の面及び前記第3の面に亘って設けられ、

前記第2の半導体領域は、前記第2の面及び前記第4の面に亘って設けられ、

前記第2の面は、前記半導体基板の深さ方向に向かって前記第3の面よりも低い位置に形成され、

前記不揮発性記憶素子のデータ書き込みは、前記半導体基板側から前記電荷蓄積膜中にホットエレクトロンを注入させることによって行われ、

前記不揮発性記憶素子のデータ消去は、前記半導体基板側から前記電荷蓄積膜中にホットホールを注入させることによって行われ、

前記ホットエレクトロンは、主に前記コントロールゲート電極に近い前記電荷蓄積膜中に注入され、

前記ホットホールは、主に前記第2半導体領域に近い前記電荷蓄積膜中に注入されることを特徴とする半導体装置の製造方法。 - 請求項10に記載の半導体装置の製造方法において、

前記第2の面は、前記コントロールゲート電極に整合して形成されることを特徴とする半導体装置の製造方法。 - 請求項10に記載の半導体装置の製造方法において、

前記半導体基板のエッチングは、ドライエッチングであることを特徴とする半導体装置の製造方法。 - 請求項10に記載の半導体装置の製造方法において、

前記半導体基板のエッチングは、前記第1の面と前記第2の面との高低差が10〜30[nm]の範囲内になるように行うことを特徴とする半導体装置の製造方法。 - 請求項10に記載の半導体装置の製造方法において、

前記第2の絶縁膜は、前記第1の絶縁膜よりも厚さが厚いことを特徴とする半導体装置の製造方法。 - 請求項10に記載の半導体装置の製造方法において、

前記積層膜は、前記第1の面と前記第2の面との段差部の壁面を覆うようにして前記第2の面から前記コントロールゲート電極の側面に亘って形成され、

前記メモリゲート電極は、前記コントロールゲート電極の隣に前記積層膜を介在して形成されることを特徴とする半導体装置の製造方法。 - 請求項10に記載の半導体装置の製造方法において、

前記第1の半導体領域はドレイン領域であり、前記第2の半導体領域はソース領域であることを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005150304A JP5014591B2 (ja) | 2005-05-24 | 2005-05-24 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005150304A JP5014591B2 (ja) | 2005-05-24 | 2005-05-24 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006332143A JP2006332143A (ja) | 2006-12-07 |

| JP5014591B2 true JP5014591B2 (ja) | 2012-08-29 |

Family

ID=37553554

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005150304A Expired - Fee Related JP5014591B2 (ja) | 2005-05-24 | 2005-05-24 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5014591B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6450624B2 (ja) * | 2015-03-30 | 2019-01-09 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP6275920B2 (ja) | 2015-03-30 | 2018-02-07 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP6557095B2 (ja) * | 2015-08-26 | 2019-08-07 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP6594198B2 (ja) * | 2015-12-28 | 2019-10-23 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4547749B2 (ja) * | 1999-09-29 | 2010-09-22 | ソニー株式会社 | 不揮発性半導体記憶装置 |

| JP2003110015A (ja) * | 2001-09-28 | 2003-04-11 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

| JP4601287B2 (ja) * | 2002-12-26 | 2010-12-22 | ルネサスエレクトロニクス株式会社 | 不揮発性半導体記憶装置 |

| JP2004303918A (ja) * | 2003-03-31 | 2004-10-28 | Renesas Technology Corp | 半導体装置の製造方法および半導体装置 |

-

2005

- 2005-05-24 JP JP2005150304A patent/JP5014591B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006332143A (ja) | 2006-12-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8344444B2 (en) | Semiconductor device having a nonvolatile memory cell with a cap insulating film formed over a selection gate electrode | |

| JP5191633B2 (ja) | 半導体装置およびその製造方法 | |

| JP5007017B2 (ja) | 半導体装置の製造方法 | |

| JP4620334B2 (ja) | 半導体記憶装置、半導体装置及びそれらを備える携帯電子機器、並びにicカード | |

| US10600799B2 (en) | Memory device and low breakdown voltage transistor | |

| US20040245564A1 (en) | Semiconductor storage device, semiconductor device and their manufacturing methods, and portable electronic equipment, and IC card | |

| JP5538828B2 (ja) | 半導体装置およびその製造方法 | |

| CN105226064B (zh) | 半导体器件及其制造方法 | |

| US9214350B2 (en) | Semiconductor device having a capacitive element | |

| US7595237B2 (en) | Non-volatile memory cell with a hybrid access transistor | |

| CN109994542B (zh) | 半导体器件及其制造方法 | |

| US10325899B2 (en) | Semiconductor device including transistors formed in regions of semiconductor substrate and operation method of the same | |

| US11342430B2 (en) | Semiconductor device | |

| JP4405489B2 (ja) | 不揮発性半導体メモリ | |

| US7715242B2 (en) | Erasing method of non-volatile memory | |

| TW200816397A (en) | Flash memory device with single-poly structure and method for manufacturing the same | |

| JP2009010281A (ja) | 半導体装置およびその製造方法 | |

| JP5014591B2 (ja) | 半導体装置及びその製造方法 | |

| US9831093B2 (en) | Semiconductor device and manufacturing method thereof | |

| US11264473B2 (en) | Method for manufacturing semiconductor device | |

| JP5351274B2 (ja) | 不揮発性半導体記憶装置 | |

| JP2004342881A (ja) | 半導体記憶装置および半導体装置およびicカードおよび携帯電子機器および半導体記憶装置の製造方法 | |

| JP2004349304A (ja) | 半導体記憶装置、半導体装置及びそれらの製造方法、並びに携帯電子機器、並びにicカード | |

| JP2010093154A (ja) | 不揮発性半導体記憶装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080409 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100412 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100511 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111115 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120113 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120306 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120605 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120606 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150615 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |