JP4890276B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4890276B2 JP4890276B2 JP2007009139A JP2007009139A JP4890276B2 JP 4890276 B2 JP4890276 B2 JP 4890276B2 JP 2007009139 A JP2007009139 A JP 2007009139A JP 2007009139 A JP2007009139 A JP 2007009139A JP 4890276 B2 JP4890276 B2 JP 4890276B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- region

- signal line

- electrically connected

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 37

- 239000000758 substrate Substances 0.000 claims description 45

- 238000007740 vapor deposition Methods 0.000 claims description 45

- 238000012360 testing method Methods 0.000 claims description 35

- 238000000034 method Methods 0.000 claims description 11

- 239000003566 sealing material Substances 0.000 claims description 7

- 238000005259 measurement Methods 0.000 description 52

- 239000003990 capacitor Substances 0.000 description 41

- 239000010408 film Substances 0.000 description 24

- 238000005401 electroluminescence Methods 0.000 description 22

- 238000007789 sealing Methods 0.000 description 17

- 238000000151 deposition Methods 0.000 description 9

- 239000011159 matrix material Substances 0.000 description 9

- 238000005019 vapor deposition process Methods 0.000 description 9

- 239000012535 impurity Substances 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 7

- 230000008021 deposition Effects 0.000 description 7

- 230000003071 parasitic effect Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- 230000005856 abnormality Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 238000007689 inspection Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 238000005192 partition Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 239000002041 carbon nanotube Substances 0.000 description 1

- 229910021393 carbon nanotube Inorganic materials 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

Images

Landscapes

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Electroluminescent Light Sources (AREA)

- Thin Film Transistor (AREA)

Description

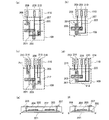

本実施形態では、半導体装置をアクティブ型ELパネルに適用した例について説明する。図1に本実施形態のELパネルを正面から見た図を示す。

アクティブマトリクス型ELパネルには、画素がマトリクス状に配置されている。図5を用いてアクティブマトリクス型ELパネルの画素回路を説明する。画素回路は、データ信号線501、ゲート信号線502、電源線503、2つのTFT504、505、電荷保持用のコンデンサ506でなる。

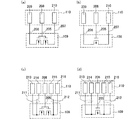

本実施形態では、実施形態2と同様、ダミー画素をTEGに用いたアクティブマトリクス型ELパネルの例を示す。図7を用いて本実施形態を説明する。

本実施形態では、実施形態2と同様、ダミー画素をTEGに用いたアクティブマトリクス型ELパネルの例を示す。図8を用いて本実施形態を説明する。

本実施形態ではTEG109を蒸着領域101の複数箇所に設け、蒸着領域101の位置によるTEGの電気的特性の分布を把握できるようにする。

101 蒸着領域

102 画素領域

103 封止領域

105 基板

106 データ信号線駆動回路

107 ゲート信号線駆動回路

108 端子部

109 TEG

110 測定用端子部

201 半導体層

202 ゲート絶縁膜

203 ゲート電極

204 絶縁層

205 配線

206 配線

207 配線

208 測定用端子

209 測定用端子

210 測定用端子

211 配線

212 配線

213 測定用端子

214 配線

215 測定用端子

401 半導体層

402 ゲート絶縁膜

403 ゲート電極

404 絶縁層

405 配線

406 配線

407 測定用端子

408 測定用端子

501 データ信号線

502 ゲート信号線

503 電源線

504 TFT

505 TFT

506 コンデンサ

507 発光素子

511 画素

513 画素

601 データ信号線

602 ゲート信号線

603 電源線

604 TFT

605 TFT

606 コンデンサ

701 データ信号線

702 ゲート信号線

703 電源線

704 TFT

705 TFT

706 コンデンサ

708 スイッチ

711 データ信号線

712 ゲート信号線

713 電源線

714 TFT

715 TFT

716 コンデンサ

717 発光素子

801 データ信号線

802 ゲート信号線

803 電源線

804 TFT

805 TFT

806 コンデンサ

807 バッファ

808 端子

901 TEG

902 TEG

903 TEG

904 TEG

9101 本体

9102 表示部

9201 本体

9202 表示部

9301 本体

9302 表示部

9401 本体

9402 表示部

9501 本体

9502 表示部

9701 表示部

9702 表示部

Claims (8)

- 第1の領域と、前記第1の領域内に設けられた第2の領域とが規定された基板と、

前記第2の領域に設けられ、第1のトランジスタ、第2のトランジスタ、ゲート信号線、データ信号線及び電源線を有する第1の回路と、前記第1の回路に電気的に接続された発光素子とを有する画素と、

前記第2の領域の外側の前記第1の領域に設けられ、前記第2の領域の前記第1のトランジスタ及び前記第2のトランジスタを検査するためのテストエレメントグループと、を有し、

前記テストエレメントグループは、第3のトランジスタ、第4のトランジスタ、ゲート信号線、データ信号線及び電源線を有する第2の回路を有し、

前記第1のトランジスタは、ゲートが前記ゲート信号線に電気的に接続され、ソース又はドレインの一方は前記データ信号線に電気的に接続され、他方は前記第2のトランジスタのゲートに電気的に接続され、前記第2のトランジスタのソース又はドレインの一方は前記電源線に電気的に接続され、他方は前記発光素子に電気的に接続され、

前記第3のトランジスタは、ゲートが前記ゲート信号線に電気的に接続され、ソース又はドレインの一方は前記データ信号線に電気的に接続され、他方は前記第4のトランジスタのゲートに電気的に接続され、前記第4のトランジスタのソース又はドレインの一方は前記電源線に電気的に接続され、

前記第2の回路の前記ゲート信号線の電位は一定であり、

前記第1の領域は、蒸着法により膜が設けられた蒸着領域であることを特徴とする半導体装置。 - 第1の領域と、前記第1の領域内に設けられた第2の領域とが規定された基板と、

前記第2の領域に設けられ、第1のトランジスタ、第2のトランジスタ、ゲート信号線、データ信号線及び電源線を有する第1の回路と、前記第1の回路に電気的に接続された発光素子とを有する画素と、

前記第2の領域の外側の前記第1の領域に設けられ、前記第2の領域の前記第1のトランジスタ及び前記第2のトランジスタを検査するためのテストエレメントグループと、を有し、

前記テストエレメントグループは、第3のトランジスタ、第4のトランジスタ、ゲート信号線、データ信号線及び電源線を有する第2の回路を有し、

前記第1のトランジスタは、ゲートが前記ゲート信号線に電気的に接続され、ソース又はドレインの一方は前記データ信号線に電気的に接続され、他方は前記第2のトランジスタのゲートに電気的に接続され、前記第2のトランジスタのソース又はドレインの一方は前記電源線に電気的に接続され、他方は前記発光素子に電気的に接続され、

前記第3のトランジスタは、ゲートが前記ゲート信号線に電気的に接続され、ソース又はドレインの一方は前記データ信号線に電気的に接続され、他方は前記第4のトランジスタのゲートに電気的に接続され、前記第4のトランジスタのソース又はドレインの一方は前記電源線に電気的に接続され、

前記第2の回路の前記ゲート信号線の電位は、バッファを用いることにより一定であり、

前記第1の領域は、蒸着法により膜が設けられた蒸着領域であることを特徴とする半導体装置。 - 第1の領域と、前記第1の領域内に設けられた第2の領域とが規定された基板と、

前記第2の領域に設けられ、第1のトランジスタ、第2のトランジスタ、ゲート信号線、データ信号線及び電源線を有する第1の回路と、前記第1の回路に電気的に接続された発光素子とを有する画素と、

前記第2の領域の外側の前記第1の領域の四隅に設けられ、前記第2の領域の前記第1のトランジスタ及び前記第2のトランジスタを検査するためのテストエレメントグループと、を有し、

前記テストエレメントグループは、第3のトランジスタ、第4のトランジスタ、ゲート信号線、データ信号線及び電源線を有する第2の回路を有し、

前記第1のトランジスタは、ゲートが前記ゲート信号線に電気的に接続され、ソース又はドレインの一方は前記データ信号線に電気的に接続され、他方は前記第2のトランジスタのゲートに電気的に接続され、前記第2のトランジスタのソース又はドレインの一方は前記電源線に電気的に接続され、他方は前記発光素子に電気的に接続され、

前記第3のトランジスタは、ゲートが前記ゲート信号線に電気的に接続され、ソース又はドレインの一方は前記データ信号線に電気的に接続され、他方は前記第4のトランジスタのゲートに電気的に接続され、前記第4のトランジスタのソース又はドレインの一方は前記電源線に電気的に接続され、

前記第1の領域は、蒸着法により膜が設けられた蒸着領域であることを特徴とする半導体装置。 - 第1の領域と、前記第1の領域内に設けられた第2の領域とが規定された基板と、

前記第2の領域に設けられ、第1のトランジスタ、第2のトランジスタ、ゲート信号線、データ信号線及び電源線を有する第1の回路と、前記第1の回路に電気的に接続された発光素子とを有する画素と、

前記第2の領域の外側の前記第1の領域の四隅に設けられ、前記第2の領域の前記第1のトランジスタ及び前記第2のトランジスタを検査するためのテストエレメントグループと、を有し、

前記テストエレメントグループは、第3のトランジスタ、第4のトランジスタ、ゲート信号線、データ信号線及び電源線を有する第2の回路を有し、

前記第1のトランジスタは、ゲートが前記ゲート信号線に電気的に接続され、ソース又はドレインの一方は前記データ信号線に電気的に接続され、他方は前記第2のトランジスタのゲートに電気的に接続され、前記第2のトランジスタのソース又はドレインの一方は前記電源線に電気的に接続され、他方は前記発光素子に電気的に接続され、

前記第3のトランジスタは、ゲートが前記ゲート信号線に電気的に接続され、ソース又はドレインの一方は前記データ信号線に電気的に接続され、他方は前記第4のトランジスタのゲートに電気的に接続され、前記第4のトランジスタのソース又はドレインの一方は前記電源線に電気的に接続され、

前記第2の回路の前記ゲート信号線の電位は一定であり、

前記第1の領域は、蒸着法により膜が設けられた蒸着領域であることを特徴とする半導体装置。 - 第1の領域と、前記第1の領域内に設けられた第2の領域とが規定された基板と、

前記第2の領域に設けられ、第1のトランジスタ、第2のトランジスタ、ゲート信号線、データ信号線及び電源線を有する第1の回路と、前記第1の回路に電気的に接続された発光素子とを有する画素と、

前記第2の領域の外側の前記第1の領域に設けられ、前記第2の領域の前記第1のトランジスタ及び前記第2のトランジスタを検査するためのテストエレメントグループと、

前記第1の領域の外側に設けられた少なくとも1つの端子と、を有し、

前記テストエレメントグループは、第3のトランジスタ、第4のトランジスタ、ゲート信号線、データ信号線及び電源線を有する第2の回路を有し、

前記第1のトランジスタは、ゲートが前記ゲート信号線に電気的に接続され、ソース又はドレインの一方は前記データ信号線に電気的に接続され、他方は前記第2のトランジスタのゲートに電気的に接続され、前記第2のトランジスタのソース又はドレインの一方は前記電源線に電気的に接続され、他方は前記発光素子に電気的に接続され、

第3のトランジスタ又は第4のトランジスタの少なくとも一方が前記端子に電気的に接続され、

前記第2の回路の前記ゲート信号線の電位は一定であり、

前記第1の領域は、蒸着法により膜が設けられた蒸着領域であることを特徴とする半導体装置。 - さらに他の基板を有し、

前記基板に対向するように前記他の基板がシール材により固定されて、前記第1の領域が封止されており、

前記端子は、前記基板、前記他の基板及び前記シール材により封止された領域の外側に設けられていることを特徴とする請求項5に記載の半導体装置。 - さらに3つの端子を有し、

前記第3のトランジスタ又は前記第4のトランジスタの少なくとも一方が前記3つの端子に電気的に接続されていることを特徴とする請求項1乃至請求項4のいずれか1項に記載の半導体装置。 - さらに2つの端子を有し、

前記第3のトランジスタ又は前記第4のトランジスタのソース及びドレインが、それぞれ前記2つの端子に電気的に接続されていることを特徴とする請求項1乃至請求項4のいずれか1項に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007009139A JP4890276B2 (ja) | 2006-01-31 | 2007-01-18 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006022074 | 2006-01-31 | ||

| JP2006022074 | 2006-01-31 | ||

| JP2007009139A JP4890276B2 (ja) | 2006-01-31 | 2007-01-18 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007235106A JP2007235106A (ja) | 2007-09-13 |

| JP2007235106A5 JP2007235106A5 (ja) | 2010-03-04 |

| JP4890276B2 true JP4890276B2 (ja) | 2012-03-07 |

Family

ID=38555332

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007009139A Expired - Fee Related JP4890276B2 (ja) | 2006-01-31 | 2007-01-18 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4890276B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10676637B2 (en) | 2014-07-25 | 2020-06-09 | Dsm Ip Assets B.V. | Matt powder coatings |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009282285A (ja) * | 2008-05-22 | 2009-12-03 | Mitsubishi Electric Corp | 画像表示装置、およびその実装検査方法 |

| JP5862204B2 (ja) * | 2011-10-31 | 2016-02-16 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| CN103426369B (zh) * | 2013-08-27 | 2015-11-11 | 京东方科技集团股份有限公司 | 显示屏 |

| US12016208B2 (en) * | 2018-09-28 | 2024-06-18 | Sharp Kabushiki Kaisha | Display device and method of manufacturing display device |

| JP6818837B2 (ja) * | 2018-11-07 | 2021-01-20 | キヤノン株式会社 | 表示装置、撮像装置、照明装置、移動体および電子機器 |

| CN112997236B (zh) * | 2018-11-16 | 2023-01-10 | 夏普株式会社 | 显示装置 |

| CN110649045B (zh) * | 2019-10-31 | 2022-08-26 | 京东方科技集团股份有限公司 | 有机发光显示面板及显示装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11167123A (ja) * | 1997-09-30 | 1999-06-22 | Sanyo Electric Co Ltd | 表示装置 |

| JP4003471B2 (ja) * | 2002-02-12 | 2007-11-07 | セイコーエプソン株式会社 | 電気光学装置、電子機器、および電気光学装置の製造方法 |

| JP4369112B2 (ja) * | 2002-12-09 | 2009-11-18 | 株式会社半導体エネルギー研究所 | 半導体装置及び電子機器 |

| JP4026618B2 (ja) * | 2004-05-20 | 2007-12-26 | セイコーエプソン株式会社 | 電気光学装置、その検査方法および電子機器 |

| JPWO2006016662A1 (ja) * | 2004-08-11 | 2008-05-01 | 三洋電機株式会社 | 半導体素子マトリクスアレイ、その製造方法及び表示パネル |

-

2007

- 2007-01-18 JP JP2007009139A patent/JP4890276B2/ja not_active Expired - Fee Related

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10676637B2 (en) | 2014-07-25 | 2020-06-09 | Dsm Ip Assets B.V. | Matt powder coatings |

| US10703930B2 (en) | 2014-07-25 | 2020-07-07 | Dsm Ip Assets B.V. | Matt powder coatings |

| US11046865B2 (en) | 2014-07-25 | 2021-06-29 | Dsm Ip Assets B.V. | Matt powder coatings |

| US11479690B2 (en) | 2014-07-25 | 2022-10-25 | Covestro (Netherlands) B.V. | Matt powder coatings |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007235106A (ja) | 2007-09-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7947979B2 (en) | Semiconductor device | |

| JP4890276B2 (ja) | 半導体装置 | |

| US11302760B2 (en) | Array substrate and fabrication method thereof, and display device | |

| US7265572B2 (en) | Image display device and method of testing the same | |

| US10585514B2 (en) | Pixel circuit, display panel and driving method thereof | |

| US9564478B2 (en) | Liquid crystal displays with oxide-based thin-film transistors | |

| US8018403B2 (en) | Display device | |

| KR20180057764A (ko) | 표시 장치 | |

| TW201630180A (zh) | 具有矽及半導電性氧化物薄膜電晶體之顯示器 | |

| US10622429B2 (en) | Micro display device and display integrated circuit | |

| JP2014149429A (ja) | 液晶表示装置および液晶表示装置の製造方法 | |

| US20220115280A1 (en) | Display panel and display apparatus | |

| JP2010262302A (ja) | 半導体装置の検査方法 | |

| CN110827730A (zh) | 一种检测ltpsamoled显示基板像素区晶体管特性的电路与方法 | |

| US20140062520A1 (en) | Display device and mother substrate | |

| US7053649B1 (en) | Image display device and method of testing the same | |

| KR20160001584A (ko) | 플렉서블 유기발광 표시패널 및 그 제조방법 | |

| KR102684692B1 (ko) | 표시 패널 및 표시 패널의 검사 방법 | |

| CN107437401A (zh) | 像素驱动电路以及具有像素驱动电路的显示装置 | |

| CN112466916B (zh) | 显示面板的屏内传感器件结构及显示装置 | |

| JP2008083529A (ja) | アクティブマトリクス基板、アクティブマトリクス基板の検査方法および電気光学装置 | |

| JP4369112B2 (ja) | 半導体装置及び電子機器 | |

| US20240215422A1 (en) | Display panel and test method thereof, display apparatus | |

| CN110796976B (zh) | 一种阵列基板的检测方法及检测系统 | |

| KR100649247B1 (ko) | 발광 표시 장치, 발광 표시 패널 및 그 데이터 구동장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100118 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100118 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110826 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111004 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111124 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111213 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111214 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4890276 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141222 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141222 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |