JP4870876B2 - 不揮発性半導体メモリ装置の消去方法 - Google Patents

不揮発性半導体メモリ装置の消去方法 Download PDFInfo

- Publication number

- JP4870876B2 JP4870876B2 JP2001081448A JP2001081448A JP4870876B2 JP 4870876 B2 JP4870876 B2 JP 4870876B2 JP 2001081448 A JP2001081448 A JP 2001081448A JP 2001081448 A JP2001081448 A JP 2001081448A JP 4870876 B2 JP4870876 B2 JP 4870876B2

- Authority

- JP

- Japan

- Prior art keywords

- threshold voltage

- erase

- memory cell

- erased

- erasing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3468—Prevention of overerasure or overprogramming, e.g. by verifying whilst erasing or writing

- G11C16/3477—Circuits or methods to prevent overerasing of nonvolatile memory cells, e.g. by detecting onset or cessation of current flow in cells and using the detector output to terminate erasing

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/14—Circuits for erasing electrically, e.g. erase voltage switching circuits

- G11C16/16—Circuits for erasing electrically, e.g. erase voltage switching circuits for erasing blocks, e.g. arrays, words, groups

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3404—Convergence or correction of memory cell threshold voltages; Repair or recovery of overerased or overprogrammed cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3404—Convergence or correction of memory cell threshold voltages; Repair or recovery of overerased or overprogrammed cells

- G11C16/3409—Circuits or methods to recover overerased nonvolatile memory cells detected during erase verification, usually by means of a "soft" programming step

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3468—Prevention of overerasure or overprogramming, e.g. by verifying whilst erasing or writing

Landscapes

- Read Only Memory (AREA)

Description

【発明の属する技術分野】

本発明は不揮発性半導体メモリ装置に関し、さらには消去されたセルのしきい値電圧の分布を最小化できる不揮発性半導体メモリ装置の消去方法に関する。

【0002】

【従来の技術】

不揮発性半導体メモリ装置として幅広く使用されるフラッシュメモリ装置は、行と列のマトリックスに配列された複数のメモリセルを含む。フラッシュメモリ装置はメモリセルの全てのアレイを同時に消去する。さらに、フラッシュメモリ装置はアレイ内の1つ又はそれより多いメモリセルの内容を電気的にプログラムしたりリードしたりする。

【0003】

フラッシュメモリ装置のメモリセルは、一般的に、行と列に配列された浮遊ゲートトランジスタ(floating gate transistors)を利用する。図1に示すように、各浮遊ゲートトランジスタ10はソース14、ドレイン16、浮遊ゲート22、制御ゲート26を含む。浮遊ゲート22は、図1を参照すると、P型半導体基板又はバルク12内に形成されたチャンネル領域18と重なり、薄いトンネル酸化膜20を通じてチャンネル領域18の両側に位置したソース14及びドレイン16のエッジ部分と重なる。制御ゲート26は浮遊ゲート22の上部に位置し、O-N-O(Oxide-Nitride-Oxide)のような中間絶縁膜24によって浮遊ゲート22から絶縁される。同一の行を占有する浮遊ゲートトランジスタの制御ゲートは複数のワードラインのうち1つに共通に連結される。同一の列を占有する浮遊ゲートトランジスタのドレイン領域は複数のビットラインのうち1つに共通に連結される。浮遊ゲートトランジスタのソース領域は共通ソースラインに連結される。

【0004】

周知のように、任意に選択されたメモリセルは、チャンネル領域と浮遊ゲートの間のホットエレクトロン注入(hot electron injection)によってプログラムされる。浮遊ゲートへのホットエレクトロン注入は、ソース及び基板は接地電圧に維持され、制御ゲートに高電圧(例えば約10V)が印加され、ホットエレクトロンを誘導するための電圧(例えば5V〜6V)がドレインに印加される。プログラムされた後、選択されたメモリセルのしきい値電圧は電子の蓄積によって増加される。プログラムされたメモリセルからデータをリードするためには、約1Vの電圧がドレインに印加され、電源電圧(又は5.5V)が制御ゲートに印加され、ソースは接地電圧に維持される。プログラムされたメモリセルの増加されたしきい値電圧はリード動作の間、ゲート電圧の遮断電位として作用するので、図2に示されたように、プログラムされたメモリセルは6V〜8Vの間に存在するしきい値電圧を有するオフセル(off-cell)に判別される。

【0005】

メモリセルの消去は、F-Nトンネル(Fowler-Nordheim tunneling)効果によってなされる。 F-Nトンネル効果は、制御ゲートに−8Vのマイナス電圧を印加し、基板(又はバルク)に約8V〜10Vの電圧を印加することによってなされる。この時、ドレイン及びソースは高インピーダンス状態(又はフローティング状態)に維持される。このような電圧バイアス条件によって誘導される制御ゲート及び基板の間の強電界は、浮遊ゲートの電子をバルクに移動させる。消去されたメモリセルは、以前に比べて、低しきい値電圧を有し、図2に示されたように、1V〜3Vの間に存在するしきい値電圧を有するオンセル(on-cell)に判別される。

【0006】

表1はプログラム、消去及びリードの時に使用された電圧レベルを示す。

【表1】

【0007】

メモリセルの消去動作が実施されると、図2で陰影処理された部分に示されたように、消去されたメモリセルのうち、特定電圧(消去状態に対応するしきい値電圧分布の最下限)以下のしきい値電圧を有するメモリセルが存在する。消去されたメモリセルのしきい値電圧が特定電圧(消去状態に対応するしきい値電圧分布の最下限)以下に低まる原因は、セクタ内に存在するメモリセルの消去速度が異なるためである。メモリセルの消去速度が異なる場合、消去されたメモリセルのしきい値電圧の分布が相対的に広まる。これは、又、消去されたメモリセルのしきい値電圧が特定電圧(消去状態に対応するしきい値電圧分布の最下限)以下に低まるようにする。即ち、消去状態に対応するしきい値電圧分布の幅は消去速度と関係がある。

【0008】

一般的に、消去速度は浮遊ゲート及び制御ゲートの間に存在する中間絶縁膜(ONO)のキャパシタンス(Cono)及びトンネル酸化膜(Ctunnel)のカップリング比(R)によって決定され得る。

【0009】

R=Cono /Cono+Ctunnel 数学式1

ここで、Conoは浮遊ゲート形状及び絶縁膜(ONO)厚さの関数であり、Ctunnelはトンネル酸化膜の厚さ及びアクティブ幅(active width)(又はチャンネル幅)の関数である。Ctunnelの変化がConoの変化よりずっと大きいので、数学式から分かるように、均一なしきい値電圧分布を得るためには、均一なトンネル酸化膜厚さ及び均一なアクティブ幅を確保するのが重要である。しかし、メモリセルのアクティブ幅は実際製造工程でウェハ又はチップ内で不均一な分布を有し、これはメモリセルの消去速度が異なるようにする。メモリセルが過度に消去されるのを防止するためには、アクティブ幅の分布を減少させなければならない(又は、チップ又はウェハ内で均一にしなければならない)。不幸にも、現製造工程を考慮する時、アクティブ幅の分布を減らすのは限界に至った。

【0010】

アクティブ幅の分布を減らすことの対案として、消去状態に対応するしきい値電圧分布の最下限より高しきい値電圧を有するように、消去リペア動作によって、異なる消去速度を有するメモリセルのうち、過度に消去されたメモリセルを治癒する方法が提案されてきた。このような消去リペア動作はポスト-プログラム(post-program) と呼ばれる。このような消去リペア動作は、従来技術の消去アルゴリズムを示す図3に示されたように、プリ-プログラム(pre-program)のすぐ後に実施されるメイン消去動作に続き実施される。プリ-プログラム(pre-programming)、メイン消去(main erasing)、ポスト-プログラム(post-programming)は消去サイクルを構成する。

【0011】

プリ-プログラム動作は、次に続くメイン消去の時に過度に消去されるメモリセルの発生を防止するために、前述の正常なプログラム動作と同一のバイアス条件(表1参照)を利用して実施される。図4を参照すると、プリ-プログラム動作が開始されると、所定のメモリセルがプログラム状態であるかを判別するためのプログラム検証動作が実施される(S10)。プログラム検証動作の結果、選択されたメモリセルの状態がプログラム状態ではないと、選択されたメモリセルがプログラム状態になるまでプログラム動作が反復的に実施される。もし、選択されたメモリセルの状態がプログラム状態であると、最後のメモリセルが選択される時まで段階(S10〜S16)が反復的に実施される。プリ-プログラム動作の結果、プログラムされたメモリセルのしきい値電圧は、図3に示されたように、約6V又はそれより高いレベル(即ち、オフ-セルのしきい値電圧)に移動される。

【0012】

続いて、セクタの全てのメモリセルがオン-セルの状態になるようにメイン消去動作が実施される。メイン消去動作が開始されると、図5に示されたように、前述の電圧バイアス条件下で、セクタ内の全てのメモリセルが同時に消去される(S20)。消去動作の後、消去されたメモリセルが消去状態であるかを判別するための消去検証動作が実施される(S22)。消去検証動作の結果、選択されたメモリセルの状態が消去状態ではないと、セクタ内の全てのメモリセルが消去状態になる時まで前述の過程(S20、S22)が反復的に実施される。たとえプリ-プログラム動作が実施されても、消去速度の差によって、メイン消去動作の後に過度に消去されたメモリセル(又は、目標しきい値電圧の最下限以下のしきい値電圧を有するメモリセル)が存在するので、ポスト-プログラム動作が実施される。

【0013】

ポスト-プログラム動作を実施するためには、過度に消去されたメモリセルのソース及び基板は接地され、制御ゲートはプログラム電圧(例えば、10V)より低電圧(例えば、3V)に連結され、ドレインは約5V〜6Vに連結される。このような電圧バイアス条件の結果、プリ-プログラム動作より少量のマイナス電荷が浮遊ゲートに蓄積される。ポスト-プログラム動作は、図4に示されたように、プリ-プログラム動作と同一の手順によって実施される。

【0014】

前述の消去方法を使用することによって、過度に消去されたメモリセルは大抵治癒され得る。しかし、メモリセルが過度に治癒されるのを根本的に解決できない。これはメイン消去過程の消去検証動作が一番高いしきい値電圧を有するメモリセルに基づいて実施されるためである。言い換えれば、全てのメモリセルのしきい値電圧が消去状態に対応するしきい値電圧分布の最上限まで下がるように消去動作を反復的に実施する。このような反復的な消去過程で、消去速度が速い(又はカップリング比(R)が大きい)メモリセルは、消去速度が遅い(又はカップリング比(R)が小さい)メモリセルに比べて、相対的に速く消去される。

【0015】

消去速度の差が大きいほど、消去状態に対応するしきい値電圧分布はより広まる。従って、相対的に速い消去速度のメモリセルは特定電圧(消去状態に対応するしきい値電圧分布の最下限)又は0Vより低電圧を有し、その結果、ポスト-プログラム動作が実施される時、リードフェイル及びドレインターンオンの問題が発生する。

【0016】

任意に消去されたメモリセルのしきい値電圧が消去状態に対応するしきい値電圧分布内に存在するかを判別するプログラム動作が実施される場合、もし、メモリセルが連結されたビットラインに関したメモリセルのうち少なくとも1つが消去されたメモリセルのしきい値電圧、特に、0V又はそれより低い電圧を有すると、そのようなメモリセルの列に連結されたメモリセルは、プログラム状態に関係なくいつもオン-セルに判別される。これを“リードフェイル”と呼ぶ。

【0017】

ポスト-プログラムの時に選択されたメモリセルのドレイン(又はビットライン)に例えば5V〜6Vの電圧が印加される時、選択されたメモリセルの列に連結された非選択のメモリセル即ち浮遊ゲートトランジスタの浮遊ゲート電圧(Vf=Rd×Vd)がドレインカップリング比(Rd=Cdrain/Cono+Ctunnel)によって増加する。もし、増加した浮遊ゲート電圧(Vf)が非選択のメモリセルのしきい値電圧(Vfg)より高いと、ワードライン電圧が印加されないにもかかわらず、非選択のメモリセルは導通される。従って、ポスト-プログラム動作が不可能であったり、長い間、ポスト-プログラム動作が実施されなければならない。これを“プログラムフェイル”又は“ドレインターンオン現象”と呼ぶ。従って、ドレインターンオン現象は消去状態に対応するしきい値電圧分布の最下限を決定する重要な要因になる。以降、ドレインターンオン現象を誘導するしきい値電圧を有するメモリセルを“過消去されたメモリセル”と呼ぶ。

【0018】

【発明が解決しようとする課題】

結果的に、メモリセルのしきい値電圧が特定電圧以下に低まる現象を防止できないので、従来技術による消去アルゴリズム(プリ-プログラム、メイン消去及びポスト-プログラムでなされる)は根本的にリードフェイル又はドレインターンオンの問題を有する。従って、メモリセルのしきい値電圧が特定電圧以下に低まる現象を根本的に防止できる新たな概念の消去方法が要求される。

【0019】

本発明は、消去されたメモリセルのしきい値電圧の分布を精密に制御できる不揮発性半導体メモリ装置の消去方法を提供することを目的とする。

【0020】

本発明は、メモリセルの消去速度を均一に調節できる不揮発性半導体メモリ装置の消去方法を提供することを目的とする。

【0021】

本発明は、総消去時間を縮め得る不揮発性半導体メモリ装置の消去方法を提供することを目的とする。

【0022】

【課題を解決するための手段】

本発明の特徴によると、各々が消去状態とプログラム状態のうち1つを有する少なくとも2つのメモリセルを消去する方法が提供される。消去方法としては、まず、少なくとも2つのメモリセルが全部プログラム状態であるかが判別される。メモリセルが全部プログラム状態である時、メモリセルが同時に消去される。その次に、消去されたメモリセルのうち相対的に速い消去速度を有するメモリセルが検出される。相対的に速い消去速度を有するメモリセルの消去時間が、相対的に遅い消去速度を有するメモリセルの消去時間より縮まるように、検出されたメモリセルをプログラムした後、消去されたメモリセル及びプログラムされたメモリセルが同時に消去される。

【0023】

本発明の他の特徴によると、行と列に配列された電気的に消去及びプログラム可能なセルトランジスタを有するセクタを備え、各セルトランジスタはプログラム状態に対応する第1しきい値電圧分布及び消去状態に対応する第2しきい値電圧分布のうちいずれか1つの分布内に存在するしきい値電圧を有する不揮発性半導体メモリ装置を消去する方法が提供される。消去方法は、セクタの全てのセルトランジスタが第1しきい値電圧分布の最下限より高しきい値電圧を有するかを判別する段階と、もしそうなら、セクタの全てのセルトランジスタを同時に消去する段階と、消去されたセルトランジスタのうち、第2しきい値電圧分布の最上限と第1しきい値電圧分布の最下限の間に存在する検出電圧レベルより低しきい値電圧を有するセルトランジスタを検出する段階と、検出電圧レベルより高しきい値電圧を有するように、検出されたセルトランジスタを個別的にプログラムする段階と、セクタの全てのセルトランジスタを同時に消去する段階とを含む。

【0024】

このような方法によると、相対的に遅い消去速度を有するメモリセルの消去時間に比べて、相対的に速い消去速度を有するメモリセルの消去時間が縮まり得る。

【0025】

【発明の実施の形態】

以下、本発明の望ましい実施形態を添付した図面を参照して詳細に説明する。

不揮発性半導体メモリ装置としてのNOR型フラッシュメモリ装置は浮遊ゲートトランジスタでなされたメモリセルのセクタを有し、セクタ内の全てのメモリセルは同時に消去される。前述のように、現製造工程技術の限界によって、チップ又はウェハ内でメモりセルに対する均一なカップリング比(R)を得にくい。従って、セクタ内のメモリセルが相違した消去速度を有し、消去されたメモリセルのしきい値電圧が広く分布されるのは当然である。図11に示されたように、相違した消去速度を有する2つのメモリセルA、Bが例えば1msecの間に消去される場合、相対的に速い消去速度(又は相対的に大きいカップリング比)を有するメモリセルAは、相対的に遅い消去速度(又は相対的に少ないカップリング比)を有するメモリセルBのしきい値電圧より低しきい値電圧を有する。即ち、2つのメモリセルA、Bの速度の差が大きいほど、2つのメモリセルA、Bのしきい値電圧の差が大きくなる。

【0026】

図11に示されたように、相対的に速い消去速度を有するメモリセルAの消去時間が約1/3乃至1/2に縮まる場合、メモリセルAのしきい値電圧は、相対的に遅い消去速度を有するメモリセルBが総消去時間(例えば1msec)の間に消去された時のメモリセルBのしきい値電圧と同一になる。即ち、相対的に遅い消去速度を有するメモリセルBのしきい値電圧をそのままに維持した状態で、相対的に速い消去速度を有するメモリセルAのしきい値電圧を縮まった消去時間に対応する電圧以上に増加させることによって、メモリセルA、Bは、消去された後、同一又は類似したしきい値電圧を有するようになる。これは消去時間を調節することによって、均一なしきい値電圧分布を得ることができることを意味する。このような理論的な背景に基づいた本発明による消去方法が、以降、詳細に説明される。

【0027】

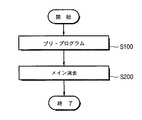

図6は、本発明による消去方法を示す概略的なフローチャートであり、図7は、図6に図示された改善されたメイン消去動作を示すフローチャートである。

【0028】

図6を参照すると、本発明による消去アルゴリズム又は消去モードはプリ-プログラム段階S100とメイン消去段階S200でなされる。プリ-プログラム動作は、次に続くメイン消去の時、過消去されたセルの発生を防止するために、正常なプログラム動作と同一のバイアス条件(表1参照)を利用して実施される。プリ-プログラム動作が開始されると、所定のメモリセルがプログラム状態であるかを判別するためのプログラム検証動作が実施される。プログラム検証動作の結果、選択されたメモリセルの状態がプログラム状態ではないと、選択されたメモリセルがプログラム状態になる時まで、プログラム動作が反復的に実施される。もし、選択されたメモリセルの状態がプログラム状態であると、最後のメモリセルが選択される時まで、前記の過程が反復的に実施される。プリ-プログラム動作の結果、プログラムされたメモリセルのしきい値電圧は、図9(A)及び図10(A)に示されたように、約6V又はそれより高いレベル(即ちオフ-セルのしきい値電圧)に移動される。即ち、本発明によるプリ-プログラム動作は従来技術のプリ-プログラム動作と同一の過程(図4参照)を通じて実施される。

【0029】

プリ-プログラム動作が完了された後、本発明による改善された

メイン消去動作が実施される。本発明の改善されたメイン消去動作は、第1消去段階、プログラム段階(以降、“中間プログラム(middle program)”と呼ぶ)、そして、第2消去段階でなされる。前述のように、第1消去段階の後、中間プログラム動作を実施することによって、相対的に速い消去速度を有するメモリセルの消去時間が、相対的に遅い消去速度を有するメモリセルの消去時間に比べて相対的に縮まり、その結果、セクタ内の消去されたメモリセルのしきい値電圧の分布が均一になる(又は精密になる)。これは消去されたメモリセルのしきい値電圧が消去状態に対応するしきい値電圧分布の最下限(例えば1V)以下に低まるのを防止できることを意味する。従って、リードフェイル及びプログラムフェイル(又はドレインタン-オン現象)を根本的に防止することによって、別途のポスト-プログラム動作が要求されない。

【0030】

図7は、図6に示されたメイン消去動作の手順を示すフローチャートである。図7を参照すると、メイン消去動作が開始されると、まず、前述の電圧バイアス条件(表1参照)下で、セクタ内の全てのメモリセルが同時に消去される(S210)。この消去動作の後、消去されたメモリセルのしきい値電圧が検出電圧レベル(例えば4V)以下であるかを判別するための消去検証動作が実施される(S220)。この消去検証動作の結果、検出電圧レベル以下のしきい値電圧を有するメモリセルが存在しない場合、段階S210、S220は反復的に実施される。第1消去段階を実施した後、得られたしきい値電圧分布が図9(B)及び図10(B)に示されている。

【0031】

ここで、検出電圧レベルはメモリセルのうち消去速度が相対的に速いメモリセルを探すための基準電圧レベルを意味する。消去動作が実施された後、しきい値電圧分布の最下限の辺りに位置したメモリセルは、しきい値電圧分布の最上限の辺りに位置したメモリセルに比べて相対的に速い消去速度を有する。同一のバイアス条件下で、検出電圧レベル以下のしきい値電圧を有するメモリセルは“相対的に速い消去速度を有するメモリセル”として定義され得る。検出電圧レベルがメモリ装置によって違う値に決定されるのは当業者には周知である。

【0032】

もし、検出電圧レベル以下のしきい値電圧を有するメモリセルが発見されると、次の段階S230で、中間プログラム動作が実施される。中間プログラム動作の間、検出電圧レベル以下のしきい値電圧を有するメモリセルが判別され、判別されたメモリセルが検出電圧レベル以上のしきい値電圧を有するようにプログラムされる。より詳細な説明は次のようである。

【0033】

図8(A)に示されたように、中間プログラムが開始されると、選択されたメモリセルが検出電圧レベル(例えば4V)以上のしきい値電圧を有するかを判別する(S231)。即ち、選択されたメモリセルが相対的に遅い消去速度を有するかが判別される。もしそれなら、選択されたメモリセルが最後のメモリセルであるかが判別される(S223)。選択されたメモリセルが最後のメモリセルである場合、中間プログラム動作は終了される。これに対して、選択されたメモリセルが最後のメモリセルではない場合、手順は次のメモリセルを選択した後、プログラム検証段階S231に進行する。段階S231で、選択されたメモリセルが検出電圧レベル(例えば4V)以下のしきい値電圧を有する場合、このようなメモリセルは相対的に速い消去速度を有する。即ち、このようなメモリセルは過度に消去される可能性が高い。次の段階S232で、検出電圧レベル以下のしきい値電圧を有するメモリセルは検出電圧レベルより高しきい値電圧を有するようにプログラムされる。その後、手順は前述の段階S233に進む。

【0034】

このような過程を順次的に実施することによって、検出電圧レベル以下のしきい値電圧を有するメモリセル(又は、相対的に速い消去速度を有するメモリセル)は、検出電圧レベル以上のしきい値電圧を有するようにプログラムされる。従って、中間プログラムに従うプログラム電圧バイアス条件は、メモリセルのしきい値電圧が検出電圧レベル以上に増加されるように設定される。中間プログラムを実施することに必要なプログラム電圧(例えばワードライン電圧)は、従来技術に使用されたポスト-プログラムを実施することに必要なプログラム電圧より高く設定されるのは当業者には周知である。ここで、中間プログラム過程でプログラムされるメモリセルの目標しきい値電圧は、図9(C)及び図10(C)に示されたように、各メモリ装置によって相違した値に設定され得る。これは次のような理論的な背景に基づく。

【0035】

図12に示されたように、相違したしきい値電圧(例えば5V〜12V)を有するメモリセルが、所定時間(例えば100μs)の間に消去された場合、メモリセルのしきい値電圧はプログラムされたしきい値電圧に関係なく、同一又は類似した電圧レベルに到達する。即ち、中間プログラム動作に従ってプログラムされるメモリセルの目標しきい値電圧は、各メモリ装置によって相違した値に設定され得る。たとえプログラムされるメモリセルの目標しきい値電圧が相違した値に設定されても、相違した消去速度を有するメモリセルは、所定時間の間に消去動作を実施することによって、同一又は類似した電圧レベルに到達するようになる。これはプログラムS232の後、プログラム検証動作が不要であることを意味する。もし、必要であると、図8(B)に示されたように、プログラム段階S232’の後、図8(A)とは違ってプログラム検証動作S231’に進行する。

【0036】

図7に示されたように、前述の中間プログラム動作が終了された後、第2消去動作が実施される。第2消去動作が開始されると、前述のバイアス条件(表1参照)下で、セクタ内の全てのメモリセルが同時に消去される(S240)。セクタ内には、第1消去動作に従って消去されたメモリセルと中間プログラム動作に従ってプログラムされたメモリセルが含まれる。消去動作の後、消去されたメモリセルのしきい値電圧が消去状態に対応するしきい値電圧分布の最上限(例えば3V)以下であるかを判別するための消去検証動作が実施される(S250)。この消去検証動作の結果、消去状態に対応するしきい値電圧分布の最上限より高しきい値電圧を有するメモリセルが存在する場合、段階S240、S250が反復的に実施される。もし、全てのメモリセルのしきい値電圧が消去状態に対応するしきい値電圧分布の最上限以下の場合、メイン消去動作又は消去モードは終了される。第2消去段階の後、得られるしきい値電圧分布が図9(D)及び図10(D)に示されている。

【0037】

本発明の消去方法によると、過消去されたメモリセルの治癒のためのポスト-プログラム動作は実施されない。これは、中間プログラム動作に従って消去速度が速いメモリセルを消去の間にプログラムすることによって、低消去速度のメモリセルと高消去速度のメモリセルが、メイン消去動作の後、ほぼ同一又は類似したしきい値電圧レベルを有するためである。もし、必要であると、従来技術と同一の方法によってポスト-プログラム動作が選択的に実施される。

【0038】

本発明の消去アルゴリズムは様々に変形され得るのは当業者には周知である。例えば、消去状態に対応するしきい値電圧分布をさらに均一に調節するために、メイン消去過程が、消去段階、第1検出電圧レベルを有する第1中間プログラム段階、消去段階、第1検出電圧レベルより低い第2検出電圧レベルを有する第2中間プログラム段階、そして、消去段階で構成され得る。

【0039】

【発明の効果】

前述の消去アルゴリズムを利用して、セクタ消去を行うことによって、次のような様々な効果を得ることができる。

【0040】

一番目は、過消去される可能性が高い又は消去速度が速いメモリセルを消去の間にプログラムすることによって、セクタ内の全てのメモリセルのしきい値電圧が均一に分布される。即ち、図13に示されたように、消去速度が速いメモリセルのしきい値電圧が消去速度が遅いメモリセルのしきい値電圧に近く分布されるので、過度に消去されるメモリセル(消去速度が速いメモリセルを意味する)によって発生されるプログラムフェイル又はドレインターン-オン現象及びリードフェイルを防止できる。

【0041】

二番目は、消去の間に中間プログラムが実施されることによって、ポスト-プログラム及びポスト-プログラム検証過程が不要であるので、プリ-プログラム、メイン消去及びポスト-プログラムでなされた従来の消去モードに比べて、本発明による消去モードを実施するのに必要な総消去時間は縮まる。即ち、中間プログラムの過程にプログラム検証過程が不要であるので、プログラム検証動作を実施するのに必要な時間は縮まる。のみならず、中間プログラム動作を実施するのに必要なプログラム電圧(例えばワードライン電圧)がポスト-プログラム動作を実施するのに必要なプログラム電圧より高いので、プログラムするのに必要な時間は縮まる。

【0042】

三番目は、ドレインターン-オンの問題が根本的に発生しないので、浮遊ゲートとドレインの間のオーバラップを増やすことができるので、プログラム速度を向上させ得る。より詳細に説明すると、次のようである。オーバラップ領域の増加によってドレインカップリング比(Rd=Cdrain/Cono+Ctunnel)が増加されると、浮遊ゲート電圧(Vf)が増加されたドレインカップリング比に比例して増加される。しかし、中間プログラムを含むメイン消去動作を実施することに従って、消去状態に対応するしきい値電圧分布の最下限(例えば1V)が正確に制御されるので、浮遊ゲートとドレインの間のオーバーラップ領域が増加され得る。ホットエレクトロン注入方式を利用したプログラム方式で、浮遊ゲートとドレインの間のオーバラップ領域が増加されると、プログラム速度も速くなる。結果的に、プログラム速度の向上はプリ-プログラム速度及び中間プログラム速度を増加させ、その結果、本発明による消去モードに必要な総消去時間は縮まる。

【0043】

四番目は、中間プログラムを含む消去アルゴリズムを採用することによって、しきい値電圧分布を均一に管理できるので、本発明の消去アルゴリズムはマルチ-レベル又はマルチ-ビット半導体で、非常に有用である。即ち、しきい値電圧分布が均一に管理されることによって、全般的なしきい値電圧分布が減少される。

これは、各動作モードに必要な電圧が低まるのを意味する。

【図面の簡単な説明】

【図1】一般的なフラッシュメモリセルの構造を示す断面図である。

【図2】一般的なプログラムされた及び消去されたセルのしきい値電圧分布を示す図である。

【図3】従来技術による消去アルゴリズムを示すフローチャートである。

【図4】図3に示されたプリ-プログラム及びポスト-プログラム動作を説明するためのフローチャートである。

【図5】図3に示された消去動作を説明するためのフローチャートである。

【図6】本発明による概略的な消去アルゴリズムを示すフローチャートである。

【図7】図6に示された改善されたメイン消去動作を説明するためのフローチャートである。

【図8】図7に示された中間プログラム動作を説明するためのフローチャートである。

【図9】本発明の消去アルゴリズムによって消去された、そして、プログラムされたセルのしきい値電圧分布の変化を示す図である。

【図10】本発明の消去アルゴリズムによって消去された、そして、プログラムされたセルのしきい値電圧分布の変化を示す図である。

【図11】相違した消去速度を有するメモリセルを消去する時、しきい値電圧対消去時間を示す図である。

【図12】相違した消去速度を有するメモリセルを消去する時、消去時間に対するしきい値電圧の変化を示す図である。

【図13】本発明及び従来技術の消去アルゴリズムによって消去されたセルのしきい値電圧分布を示す図である。

Claims (4)

- 行と列に配列された電気的に消去及びプログラム可能なセルトランジスタを有するセクタを備え、前記各セルトランジスタはプログラム状態に対応する第1しきい値電圧分布及び消去状態に対応する第2しきい値電圧分布のうちいずれか1つの分布内に存在するしきい値電圧を有する不揮発性半導体メモリ装置を消去する方法において、

前記セクタの全てのセルトランジスタが前記第1しきい値電圧分布の最下限より高いしきい値電圧を有するかを判別する段階と、

もしそうなら、前記第2しきい値電圧分布の最上限と前記第1しきい値電圧分布の最下限との間に存在する検出電圧レベルより低いしきい値電圧レベルを有するセルトランジスタが検出される時まで、前記セクタの全てのセルトランジスタを同時に消去して、相対的に速い消去動作を有するセルトランジスタを検出する段階と、

前記検出電圧レベルより高いしきい値電圧を有するように、前記検出されたセルトランジスタを個別的にプログラムする段階と、

前記セクタの全てのセルトランジスタを同時に消去する段階とを含むことを特徴とする不揮発性半導体メモリ装置の消去方法。 - 前記セルトランジスタが前記第2しきい値電圧分布の最上限より低いしきい値電圧を有するかを判別する段階と、

前記セルトランジスタのうち少なくとも1つが前記第2しきい値電圧分布の最上限より高いしきい値電圧を有する時、前記セルトランジスタが前記第2しきい値電圧分布の最上限より低いしきい値電圧を有する時まで、前記消去及び判別段階を反復的に実施する段階とを含むことを特徴とする請求項1に記載の不揮発性半導体メモリ装置の消去方法。 - 前記セルトランジスタが前記第2しきい値電圧分布の最上限より低いしきい値電圧を有する時、前記セルトランジスタが過消去されたかを判別する段階と、

前記消去されたセルトランジスタのうち少なくとも1つが過消去された時、この過消去されたセルトランジスタをプログラムする段階とを含むことを特徴とする請求項2に記載の不揮発性半導体メモリ装置の消去方法。 - 前記検出されたセルトランジスタを個別的にプログラムする段階は、前記プログラムされたセルトランジスタが前記検出電圧レベルより高いしきい値電圧を有するかを判別する段階を含み、前記検出されたセルトランジスタが前記検出電圧レベルより高いしきい値電圧を有する時までプログラム及び判別動作を反復的に実施することを特徴とする請求項1に記載の不揮発性半導体メモリ装置の消去方法。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR20000021646 | 2000-04-24 | ||

| KR10-2000-0076373A KR100428784B1 (ko) | 2000-04-24 | 2000-12-14 | 소거된 셀들의 문턱 전압 분포를 최소화할 수 있는불휘발성 반도체 메모리 장치의 소거 방법 |

| KR2000P-76373 | 2000-12-14 | ||

| KR2000P-21646 | 2000-12-14 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001307492A JP2001307492A (ja) | 2001-11-02 |

| JP4870876B2 true JP4870876B2 (ja) | 2012-02-08 |

Family

ID=26637905

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001081448A Expired - Fee Related JP4870876B2 (ja) | 2000-04-24 | 2001-03-21 | 不揮発性半導体メモリ装置の消去方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6507522B2 (ja) |

| JP (1) | JP4870876B2 (ja) |

| TW (1) | TW512350B (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7061810B2 (en) * | 2001-10-09 | 2006-06-13 | Micron Technology, Inc. | Erasing flash memory without pre-programming the flash memory before erasing |

| KR100456596B1 (ko) * | 2002-05-08 | 2004-11-09 | 삼성전자주식회사 | 부유트랩형 비휘발성 기억소자의 소거 방법 |

| KR100463954B1 (ko) * | 2002-05-17 | 2004-12-30 | 주식회사 하이닉스반도체 | 플래시 메모리 장치 및 그 소거 방법 |

| US6876582B2 (en) * | 2002-05-24 | 2005-04-05 | Hynix Semiconductor, Inc. | Flash memory cell erase scheme using both source and channel regions |

| JP4028301B2 (ja) * | 2002-06-11 | 2007-12-26 | 富士通株式会社 | 不揮発性半導体記憶装置及びその消去方法 |

| KR20040008526A (ko) * | 2002-07-18 | 2004-01-31 | 주식회사 하이닉스반도체 | 플래시 메모리 셀의 소거 방법 |

| US6925011B2 (en) * | 2002-12-26 | 2005-08-02 | Micron Technology, Inc. | Programming flash memories |

| US7251158B2 (en) | 2004-06-10 | 2007-07-31 | Spansion Llc | Erase algorithm for multi-level bit flash memory |

| US7079424B1 (en) * | 2004-09-22 | 2006-07-18 | Spansion L.L.C. | Methods and systems for reducing erase times in flash memory devices |

| US7200043B2 (en) * | 2005-05-31 | 2007-04-03 | Elite Semiconductor Memory Technology, Inc. | Nonvolatile memory using a two-step cell verification process |

| KR100749736B1 (ko) * | 2005-06-13 | 2007-08-16 | 삼성전자주식회사 | 플래시 메모리 장치 및 그것의 소거 방법 |

| JP4904780B2 (ja) * | 2005-11-07 | 2012-03-28 | 富士通セミコンダクター株式会社 | 不揮発性半導体記憶装置 |

| US7859904B1 (en) * | 2007-09-20 | 2010-12-28 | Cypress Semiconductor Corporation | Three cycle memory programming |

| US7643349B2 (en) * | 2007-10-18 | 2010-01-05 | Macronix International Co., Ltd. | Efficient erase algorithm for SONOS-type NAND flash |

| US7796443B2 (en) * | 2008-06-12 | 2010-09-14 | Fs Semiconductor Corp., Ltd. | Method of erasing a flash EEPROM memory |

| KR20120030818A (ko) | 2010-09-20 | 2012-03-29 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 그것의 소거 방법 |

| US9496044B2 (en) | 2013-08-15 | 2016-11-15 | Renesas Electronics Corporation | Semiconductor device |

| KR102358463B1 (ko) * | 2014-10-20 | 2022-02-07 | 삼성전자주식회사 | 불휘발성 메모리 장치의 동작 방법 |

| US9679652B2 (en) * | 2015-05-04 | 2017-06-13 | Phison Electronics Corp. | Threshold based multi-level cell programming for reliability improvement |

| US10916310B2 (en) | 2019-05-10 | 2021-02-09 | Macronix International Co., Ltd. | Memory system, memory controller, and memory control method |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE69033438T2 (de) * | 1989-04-13 | 2000-07-06 | Sandisk Corp., Santa Clara | Austausch von fehlerhaften Speicherzellen einer EEprommatritze |

| JP2982676B2 (ja) * | 1995-12-08 | 1999-11-29 | 日本電気株式会社 | 不揮発性半導体記憶装置の過消去救済方法 |

| KR100257854B1 (ko) * | 1997-12-10 | 2000-06-01 | 김영환 | 플래쉬 메모리의 소거 방법 |

| US6049486A (en) * | 1999-01-04 | 2000-04-11 | Taiwan Semiconductor Manufacturing Company | Triple mode erase scheme for improving flash EEPROM cell threshold voltage (VT) cycling closure effect |

-

2001

- 2001-03-21 JP JP2001081448A patent/JP4870876B2/ja not_active Expired - Fee Related

- 2001-04-24 TW TW090109788A patent/TW512350B/zh not_active IP Right Cessation

- 2001-04-24 US US09/841,917 patent/US6507522B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US20010043492A1 (en) | 2001-11-22 |

| TW512350B (en) | 2002-12-01 |

| JP2001307492A (ja) | 2001-11-02 |

| US6507522B2 (en) | 2003-01-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4870876B2 (ja) | 不揮発性半導体メモリ装置の消去方法 | |

| US6252803B1 (en) | Automatic program disturb with intelligent soft programming for flash cells | |

| US6777292B2 (en) | Set of three level concurrent word line bias conditions for a NOR type flash memory array | |

| US7408804B2 (en) | Systems for soft programming non-volatile memory utilizing individual verification and additional soft programming of subsets of memory cells | |

| KR100761091B1 (ko) | 소프트 프로그래밍이 vt 분포의 폭을 좁힐 수 있게 하는 게이트 램핑 기술 | |

| US6363013B1 (en) | Auto-stopped page soft-programming method with voltage limited component | |

| EP1306855A2 (en) | Method for erasing a memory cell | |

| KR100960352B1 (ko) | 선 소거 단계를 이용하여 플래시 메모리를 소거하는 방법 | |

| KR100308192B1 (ko) | 플래시 메모리 셀들의 과소거를 방지할 수 있는 플래시 메모리장치 및 그것의 소거 방법 | |

| JP2004524643A (ja) | フラッシュメモリアレイ内のコアセルのソフトプログラム及びソフトプログラム検証 | |

| WO2003088260A1 (en) | Algorithm dynamic reference programming | |

| US6442071B2 (en) | Non-volatile semiconductor memory device with improved erase algorithm | |

| US7277329B2 (en) | Erase method to reduce erase time and to prevent over-erase | |

| US6452840B1 (en) | Feedback method to optimize electric field during channel erase of flash memory devices | |

| US6285588B1 (en) | Erase scheme to tighten the threshold voltage distribution of EEPROM flash memory cells | |

| EP2102868B1 (en) | Method and system of low voltage programming of non-volatile memory cells | |

| KR100428784B1 (ko) | 소거된 셀들의 문턱 전압 분포를 최소화할 수 있는불휘발성 반도체 메모리 장치의 소거 방법 | |

| US6416556B1 (en) | Structure and method of operating an array of non-volatile memory cells with source-side programming | |

| US6198664B1 (en) | APDE scheme for flash memory application | |

| US7020021B1 (en) | Ramped soft programming for control of erase voltage distributions in flash memory devices | |

| US6178117B1 (en) | Background correction for charge gain and loss | |

| US7599228B1 (en) | Flash memory device having increased over-erase correction efficiency and robustness against device variations | |

| KR100655281B1 (ko) | 플래시 메모리 셀들의 과소거를 방지할 수 있는 플래시메모리 장치 및 그것의 소거 방법 | |

| KR100368861B1 (ko) | 불 휘발성 반도체 메모리의 과소거 구제 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080311 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100916 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101005 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101224 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110524 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110920 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20110928 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111025 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111118 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4870876 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141125 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |