JP4865122B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4865122B2 JP4865122B2 JP2000202985A JP2000202985A JP4865122B2 JP 4865122 B2 JP4865122 B2 JP 4865122B2 JP 2000202985 A JP2000202985 A JP 2000202985A JP 2000202985 A JP2000202985 A JP 2000202985A JP 4865122 B2 JP4865122 B2 JP 4865122B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- silicon

- silicon film

- semiconductor film

- heat treatment

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本発明は結晶構造を有する半導体膜で活性領域を形成した半導体装置及びその作製方法に関する。特に、本発明は当該半導体膜でチャネル形成領域を形成する薄膜トランジスタ及びその作製方法に好適に用いることができる。尚、本明細書において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、半導体集積回路、電気光学装置、及び半導体集積回路や電気光学装置を搭載した電子機器は半導体装置の範疇に含まれるものとする。

【0002】

【従来の技術】

ガラスや石英などの基板上に結晶構造を有する半導体膜(以下、結晶質半導体膜という)を用いて薄膜トランジスタ(以下、TFTと記す)を作製する技術が開発されている。TFTはフラットパネルディスプレイの分野において、高精細な画像表示を実現する手段として、又は、画素部と当該画素部の駆動に必要な集積回路を同一基板上に形成したモノシリック型ディスプレイを実現することを可能としている。

【0003】

SOI技術(Silicon on Insulator technology)以外で結晶質半導体膜を形成するには、気相成長法(CVD法)により基板上に直接結晶質半導体膜を形成する方法や、非晶質半導体膜を加熱処理、或いはレーザー光の照射により結晶化させる方法が知られている。しかし、TFTにおいては、良好な電気的特性が得られることから後者の方法が積極的に用いられている。

【0004】

ガラスまたは石英などの基板上の非晶質半導体膜を加熱処理やレーザー光の照射により結晶化した結晶質半導体膜は多結晶構造となる。通常の場合、結晶化は非晶質半導体膜と基板との界面に自然に発生する結晶核が基となり結晶化が進むことが判明している。多結晶構造における個々の結晶粒は任意な結晶面が析出しているが、下地に酸化シリコンがある場合には、その界面エネルギーが最小となる(111)面の結晶が析出する確率が高くなる。

【0005】

ところで、TFTに必要な半導体膜の厚さは10〜100nm程度である。この膜厚の範囲では、格子の不整合により、異種材料である下地の影響を無視することができず、高品質の結晶質半導体膜をガラスや石英などの基板上に形成することが困難となる。また、自然に発生する結晶核を当てにする結晶化方法では、結晶方位を制御することは困難であり、また相互に干渉しあう為、個々の結晶粒の大粒径化を望むことはできない。

【0006】

結晶質シリコン膜を形成する他の手法として、非晶質シリコン膜にシリコンの結晶化を助長する元素を導入し、従来よりも低い温度の加熱処理で結晶質シリコン膜を作製する技術が開示されている。例えば、特開平7−130652号公報、特開平8−78329号公報では、非晶質シリコン膜にニッケルなどの金属元素を導入し、550℃、4時間の熱処理により結晶質シリコン膜を得ることができる。

【0007】

この場合には、自然核が発生するより低い温度で導入した元素のシリサイド化物が形成され、当該シリサイドを基にした結晶成長が起こっている。例えば、ニッケルを用いて形成されるニッケルシリサイド(NiSix(0.4≦x≦2.5))は特定の配向性を持たないが、非晶質シリコン膜の厚さを10〜100nmとすると基板表面に対し平行な方向しか殆ど成長することが許されなくなる。この場合、NiSixと結晶シリコンの(111)面とが接する界面エネルギーが最も小さいので、結晶質シリコン膜の表面と平行な面は(110)面となり、この格子面が優先的に配向する。しかし、結晶成長方向が基板表面に対し平行な方向に柱状に成長する場合には、その柱状結晶を軸とした回転方向には自由度が存在するため、必ずしも(110)面が配向するとは限らないため、その他の格子面も析出していた。

【0008】

【発明が解決しようとする課題】

配向率が低い場合、異なる方位の結晶がぶつかる結晶粒界で、格子の連続性を保持することが殆ど不可能となり、不対結合手が多く形成されることが容易に推定される。粒界にできる不対結合手は再結合中心または捕獲中心となり、キャリア(電子・ホール)の輸送特性を低下させている。その結果、キャリアが再結合で消滅したり欠陥にトラップされたりするため、このような結晶質半導体膜を用いてTFTを作製しても高い電界効果移動度を有するTFTを期待することができない。

【0009】

また、結晶粒の位置を意図的に制御することは殆ど不可能であり、結晶粒界はランダムに存在するため、TFTのチャネル形成領域を特定の結晶方位をもつ結晶粒で形成することができない。そのために結晶格子の連続性が低下して、結晶粒界では欠陥が形成される。結果として、TFTの特性をばらつかせる要因となり、様々な悪影響をもたらすことになる。例えば、電界効果移動度が低下して、TFTを高速で動作させることができなくなる。また、しきい値電圧の変動は低電圧駆動を不可能として、消費電力の増加をもたらすことになる。

【0010】

本発明はこのような問題点を解決する手段を提供することを目的とし、非晶質半導体膜を加熱処理とレーザー光または紫外線、赤外線などの強光の照射により結晶化して得られる結晶質半導体膜の配向率を高め、そのような結晶質半導体膜で活性領域を形成した半導体装置及びその作製方法を提供することを目的とする。

【0011】

【課題を解決するための手段】

本発明は、{101}面の配向率の高い結晶質半導体膜を得る技術であり、当該結晶質半導体膜は、シリコンに対するゲルマニウムの組成比が0.1原子%以上10原子%以下であり、窒素及び炭素の濃度が5×1018/cm3未満であり、酸素の濃度が1×1019/cm3未満である非晶質半導体膜を加熱処理とレーザー光またはそれと同等な強光を照射して、非晶質半導体膜を溶融させずに結晶化した半導体膜であることを特徴としている。

【0012】

そして、本発明の結晶質半導体膜の配向率は、反射電子線回折パターン法で検出される{101}格子面の結晶質半導体膜の表面となす角が10度以内である割合が20%以上であり、かつ、{001}格子面の結晶質半導体膜の表面となす角が10度以内である割合が3%以下であり、かつ、{111}格子面の結晶質半導体膜の表面となす角が10度以内である割合が5%以下であることを特徴としている。{101}格子面の結晶質半導体膜の表面となす角が5度以内である割合がについて見れば5%以上となる。

【0013】

上記本発明の結晶質半導体膜の作製方法は、シリコンに対するゲルマニウムの組成比が0.1原子%以上10原子%以下であり、窒素及び炭素の濃度が5×1018/cm3未満であり、酸素の濃度が1×1019/cm3未満である非晶質半導体膜を形成する第1の工程と、非晶質半導体膜に当該非晶質半導体膜の結晶化を助長する元素を添加して加熱処理を行い結晶構造を有する半導体膜を形成する第2の工程と、結晶構造を有する半導体膜にレーザー光またはそれと同等な強光を照射して、溶融させることなくアニールを行う第3の工程とを有することを特徴としている。

【0014】

また、他の方法は、シリコンに対するゲルマニウムの組成比が0.1原子%以上10原子%以下であり、窒素及び炭素の濃度が5×1018/cm3未満であり、酸素の濃度が1×1019/cm3未満である非晶質半導体膜を形成する第1の工程と、非晶質半導体膜に当該非晶質半導体膜の結晶化を助長する元素を添加して第1の加熱処理を行い結晶構造を有する半導体膜を形成する第2の工程と、結晶構造を有する半導体膜にレーザー光またはそれと同等な強光を照射して、溶融させることなくアニールを行う第3の工程と、結晶構造を有する半導体膜の上層に水素を含有する窒化シリコン膜または酸化窒化シリコン膜を形成する第4の工程と、第4の工程の後に、第2の加熱処理と第3の加熱処理を行う第5の工程とを有していることを特徴としている。

【0015】

非晶質半導体膜の結晶化を助長する元素は、Fe、Co、Ni、Ru、Rh、Pd、Os、Ir、Pt、Cu、Auから選ばれた一種または複数種であり、非晶質半導体膜の厚さは10nm〜100nmの厚さで形成する。

【0016】

【発明の実施の形態】

本発明において、TFTのチャネル形成領域に用いる半導体膜は、{101}格子面の配向率が高いシリコンとゲルマニウムから成る結晶質半導体膜であることに特徴を有している。このような結晶質半導体膜を得る典型的な一実施形態は、シリコン原子及びゲルマニウム原子の水素化物またはフッ化物または塩化物によるガスを用い、プラズマCVD法または減圧CVD法により非晶質半導体膜を形成し、その表面に該非晶質半導体膜の結晶化を助長する元素を導入し、当該元素を利用して加熱処理とレーザー光または紫外線、赤外線などの強光の照射により結晶化して結晶質半導体膜を形成する。

【0017】

このような結晶質半導体膜を形成するための基板は、アルミナホウケイ酸ガラスやバリウムホウケイ酸ガラスなどの無アルカリガラス基板が適している。代表的にはコーニング社の#7059ガラス基板や#1737ガラス基板を用いる。その他に石英基板やサファイア基板を用いても良い。或いは、シリコン、ゲルマニウム、ガリウム・砒素などの半導体基板の表面に絶縁膜を形成し、これを基板としても良い。

【0018】

また、基板として上記ガラス基板を用いる場合には、非晶質半導体膜とガラス基板との間に窒化シリコン、酸化シリコン、または酸化窒化シリコンなどでブロッキング層を形成する。こうして、ガラス基板中に含まれるアルカリ金属元素などの不純物元素が半導体膜中に拡散することを防ぐ。例えば、プラズマCVD法でSiH4、NH3、N2を反応ガスとして用い、窒化シリコン膜を形成する。または、SiH4、N2O、NH3を反応ガスとして用い、酸化窒化シリコン膜を形成する。ブロッキング層の厚さは20〜200nmで形成する。

【0019】

このような基板上に上記非晶質半導体膜を形成する。プラズマCVD法または減圧CVD法、その他適宣の方法により行う。プラズマCVD法を適用する場合には、SiH4とGeH4とから成る反応ガス、或いは、SiH4とH2で希釈したGeH4とから成る反応ガスを加えて反応室に導入し、1〜200MHzの高周波放電により分解し基板上に非晶質半導体膜を堆積させる。反応ガスは、SiH4の代わりにSi2H6またはSiF4を、GeH4の代わりにGeF4を採用しても良い。減圧CVD法を用いる場合にも同様な反応ガスを適用することが可能であり、好ましくはHeで反応ガスを希釈して、400〜500℃の温度で基板上に非晶質半導体膜を堆積する。いずれにしても、本発明で用いる上記ガスは、堆積される非晶質半導体膜に取り込まれる酸素、窒素、炭素などの不純物元素の濃度を低減するために高純度に精製されたものを用いる。堆積する非晶質半導体膜の厚さは10〜100nmの範囲とする。

【0020】

本発明に用いる非晶質半導体膜は、シリコンとゲルマニウムとから成り、シリコンに対するゲルマニウムの含有量は0.1原子%以上、10原子%未満とする。このような非晶質半導体膜は、代表的な反応ガスとして用いられるSiH4とGeH4の混合比を調節することで、ゲルマニウムの含有量を所定の範囲内とすることができる。また、非晶質半導体中に含まれる異種元素として、窒素及び炭素の濃度は5×1018/cm3未満、酸素の濃度は1×1019/cm3未満とする。結晶化の過程においてこれらの不純物は、主に結晶粒の粒界に析出し、粒界のポテンシャル障壁が高くなりキャリアーの移動度が低下する等の不具合が生じてしまう。

【0021】

ここで、本明細書ではこれらの異種元素の濃度は、二次イオン質量分析法(SIMS)により検出される濃度を言うものであり、当該膜中における濃度の最低値を指している。

【0022】

上記のように形成した非晶質半導体膜に、該非晶質半導体膜の結晶化を助長する元素を導入する。そのような元素としては、鉄(Fe)、ニッケル(Ni)、コバルト(Co)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスニウム(Os)、イリジウム(Ir)、白金(Pt)、銅(Cu)、金(Au)から選ばれた一種または複数種の元素を用いる。これらの元素は、本明細書に記載する何れの発明においても非晶質半導体膜の結晶化を助長する元素として使用することができる。上記いずれの元素を用いても同質、同様の効果を得ることができるが、代表的にはニッケルを用いる。

【0023】

当該元素を導入する箇所は、非晶質半導体膜の全面、或いは非晶質半導体膜の膜面における適宣箇所のスリット状の面または点状の面などとする。前者の場合には、当該非晶質半導体膜の基板側に位置する面または基板側とは反対の面のいずれであっても良い。後者の場合には、好ましくは非晶質半導体膜上に絶縁膜が形成され、その絶縁膜に設けられた開孔を利用して元素を導入することができる。開孔の大きさに特に限定はないが、その幅は10〜40μmとすることができる。また、その長手方向の長さは任意に決めれば良く、数十μm〜数十cmの範囲とすることができる。

【0024】

当該元素を導入する方法は、当該元素を非晶質半導体膜の表面又は内部に存在させる手法であれば特に限定はなく、例えば、スパッタ法、蒸着法、プラズマ処理法(含むプラズマCVD法)、吸着法、金属塩の溶液を塗布する方法などを使用することができる。プラズマ処理法は、不活性ガスによるグロー放電雰囲気において、陰極からスパッタされる当該元素を利用する。また、金属塩の溶液を塗布する方法は簡易であり、当該元素の濃度調整が容易である点で有用である。

【0025】

金属塩としては各種塩を用いることが可能であり、溶媒としては水、アルコール類、アルデヒド類、エーテル類その他の有機溶媒、または水とこれらの有機溶媒の混合物を用いることができる。また、それらの金属塩が完全に溶解した溶液とは限らず、金属塩の一部または全部が懸濁状態で存在する溶液であっても良い。いずれの方法を採用するにしても、当該元素は非晶質半導体膜の表面又は内部に分散させて導入する。

【0026】

上記何れかの方法で当該元素を導入した後、当該元素を利用して非晶質半導体膜の結晶化を行う。結晶化は加熱処理、レーザー光または紫外線、赤外線などの強光の照射によって行う(以下、本明細書では一括してレーザー処理と標記する)。加熱処理のみでも{101}に優先的に配向する結晶質シリコン膜を得ることができるが、好ましくは、加熱処理を行いその後レーザー光などの強光の照射を行う方法を適用する。加熱処理後のレーザー処理は、結晶粒内に残される結晶欠陥を修復することができ、作製される結晶の品質を向上させる目的に対して有効な処置となる。

【0027】

加熱処理は450〜1000℃の範囲で行うことが可能であるが、温度の上限は使用する基板の耐熱温度が一つの上限として考慮される。例えば、石英基板を用いる場合には1000℃の熱処理にも耐えるが、ガラス基板の場合にはその歪み点以下が上限温度の一つの根拠となる。例えば、歪み点667℃のガラス基板に対しては、660℃程度が上限となり、好ましくは600℃以下とするのが良い。必要とされる時間は加熱温度や、その後の処理条件(例えばレーザー光を照射する処理の有無など)により若干異なるが、好適には550〜600℃にて4〜24時間の加熱処理を行う。また、その後レーザー処理を行う場合には、500〜550℃にて4〜8時間の熱処理を行う。以上の加熱処理は空気中や水素雰囲気中でも良いが、好適には窒素或いは不活性ガス雰囲気中にて行う。

【0028】

また、レーザー処理は、波長400nm以下のエキシマレーザーや、YAGまたはYVO4レーザーの第2高調波(波長532nm)〜第4高調波(波長266nm)を光源として用いて行う。これらのレーザー光は光学系にて線状またはスポッ状に集光し、そのエネルギー密度を100〜300mJ/cm2として照射し、上記のように集光したレーザービームを基板の所定の領域に渡って走査させ処理を行う。その他、レーザーの代わりに、ハロゲンランプ、キセノンランプ、水銀ランプ、メタルハライドランプなどを光源としても良い。

【0029】

以上のような工程により、本発明における{101}面の配向率が高い結晶質半導体膜が得られるモデルは、概略以下のように推測することができる。それについて図24を参照しながら説明する。

【0030】

基板2401上に形成された非晶質半導体膜2402に導入されたシリコンの結晶化を助長する元素は、脱水素処理中に速やかに非晶質半導体2402中に拡散する。そして、当該元素とシリコンが反応してシリサイド2403が形成され、これが結晶核となりその後の結晶成長に寄与する。例えば、代表的な元素としてニッケルを用いた場合、NiSixが形成される。しかし、NiSix中にはゲルマニウムが殆ど固溶しないため、非晶質半導体2402中のNiSixは、ゲルマニウムを周囲に排除しつつ移動する。

【0031】

NiSixは特定の配向性を持たないが、非晶質半導体膜の厚さを10〜100nmとすると基板表面に対し平行な方向しか殆ど成長することが許されなくなる。この場合、NiSixと結晶シリコンの(111)面とが接する界面エネルギーが最も小さいので、結晶質シリコン膜の表面と平行な面は(110)面となり、この格子面が優先的に配向する。結晶成長方向が基板表面に対し平行な方向に、しかも柱状に成長する場合には、その柱状結晶を軸とした回転方向には自由度が存在するため、必ずしも(110)面が配向するとは限らないため、その他の格子面も析出することになる。

【0032】

NiSixから見ると、周囲の非晶質半導体のみに原子半径の大きいゲルマニウムが存在しているため、大きな歪み(引っ張り応力)が発生していることが予想される。この歪みエネルギーにより、核生成の臨界半径を大きくする方向に働く。さらに、この歪み(引っ張り応力)は、NiSixによる核の結晶方位に制限を与え、特定の結晶面(具体的には、{101}面)の配向率を高める作用があると推測される。

【0033】

NiSixの構造はホタル石型構造であり、ダイアモンド型構造のシリコン格子間にニッケル原子を配置した構造となっている。NiSixからニッケル原子が無くなるとシリコンの結晶構造が残ることになる。数々の実験の結果から、ニッケル原子は非晶質シリコン側に移動していくことが判明しており、この理由は非晶質シリコン中の固溶度の方が結晶シリコン中のそれよりも高いためであると考えられる。従って、恰もニッケルが非晶質シリコン中を移動しながら結晶シリコン膜2404を形成するというモデルを立案することができる。

【0034】

本発明は、結晶質半導体膜の{101}面の配向を高めるために、シリコンとゲルマニウムから成る非晶質半導体膜にシリコンの結晶化を助長する元素を添加して、加熱処理とレーザー処理を行って結晶化させる。

【0035】

ところで、非晶質半導体膜、具体的には非晶質シリコン膜に0.1〜10原子%のゲルマニウムを含有させると結晶核の発生密度が低下することが、本発明者により見いだされている。図13は結晶核の隣接間距離について、GeH4の添加量依存性について調べた結果であり、縦軸はその累積度数を示している。成膜条件として、SiH4と水素で10%に希釈したGeH4の合計流量は100SCCM一定としたものである。

【0036】

図13(A)はシリコンの結晶化を助長する元素として、酢酸ニッケル塩が3ppmの水溶液を用いた結果であり、図13(B)は1ppmの結果を示している。GeH4の添加量の増加は、非晶質シリコン中に含まれるゲルマニウム濃度がそれに伴って増えることを意味する。図13(A)、(B)の結果は、いずれもGeH4の添加量が多い方が結晶核の隣接間距離が長くなることを示している。図14はこの結果を基に、GeH4の添加量に対する結晶核の密度を示している。GeH4の量が増加するに従い、結晶核密度が低下している傾向が示されている。

【0037】

核生成理論の立場からは、体積Vの核が母相中に現れる際のエネルギー変化ΔGは次式で与えられる。

【0038】

【数1】

【0039】

ここで、ΔGvは単位体積当たりの自由エネルギー変化(負)であり、右辺第1項は核生成の駆動力となる。一方、Eは単位体積当たりの歪みエネルギーであり、γsは単位体積当たりの界面エネルギー(Sは析出した核の表面積)であり、第2項、第3項は核の析出を妨害する方向に働く。これら二つの項があるため、ある臨界半径r0以下の核はエネルギー的に不安定(ΔGがrと共に増加する)であり、一時的に現れたとしても消滅してしまう。即ち、r0を超えた核のみが安定化することを示している。このことは上記考察において、非晶質シリコン膜中にゲルマニウムが存在することにより核生成の臨界半径を大きくする方向に働くことを裏付けている。

【0040】

次に上述の本発明に基づいて作製される結晶質半導体膜について、その作製条件の一例を示す。表1はプラズマCVD法で作製する非晶質半導体膜の作製条件である。反応ガスはSiH4と水素で10%に希釈されたGeH4を用いる。これらの反応ガスは、形成される非晶質半導体膜に含まれる酸素、窒素、炭素の不純物濃度を低減させるために、SiH4の純度は99.9999%以上のものを、またGeH4は窒素、炭化水素化合物が1ppm以下、CO2が2ppm以下の高純度品を用いている。第1の非晶質半導体膜において、シリコンに対するゲルマニウムの含有量を変化させるために、合計流量が一定になるようにして、SiH4とH2で10%に希釈したGeH4のガス流量の混合比を変化させている。共通条件としては、高周波電力が0.35W/cm2(27MHz)であり、繰り返し周波数10kHz(デューティ比30%)のパルス放電に変調して平行平板型のプラズマCVD装置の陰極に給電する。その他、共通条件として反応圧力33.25Pa、基板温度300℃、電極間隔35mmとする。

【0041】

【表1】

【0042】

図9はプラズマCVD装置の一例であり、共通室1120は、ロード・アンロード(L/UL)室1110、1115、反応室(1)〜反応室(3)111〜113、予備室114とゲート弁1122〜1127を介して連結されている。基板は、ロード・アンロード(L/UL)室1110、1115のカセット1128、1129に装填され、共通室1120の搬送手段1121により各反応室または予備室に搬送される。予備室114では主に基板の予備加熱のみを行い、反応室(1)では窒化シリコン膜や酸化シリコン膜などの絶縁膜の形成、反応室(2)では非晶質半導体膜の成膜の形成を行い、反応室(3)ではシリコンの結晶化を助長する元素をプラズマ処理により添加するように分離されている。このプラズマ処理は、不活性ガスのグロー放電により、ニッケルなどの上記結晶化を助長する元素で形成された陰極からスパッタされる元素を非晶質半導体膜に付着させる処理である。このような構成のプラズマCVD装置を用いれば、基板に密接して形成するブロッキング層から非晶質半導体膜、及び非晶質半導体膜の結晶化を助長する元素の添加までを、大気に曝すことなく連続して形成することができる。

【0043】

図10はこのようなプラズマCVD装置の一つの反応室の構成を詳細に説明するものであり、非晶質半導体膜を形成する反応室の一例を示している。反応室501は、高周波電源505が接続する陰極(カソード)502、陽極(アノード)503が設けられた平行平板型である。陰極502はシャワー板となっていて、ガス供給手段506からの反応ガスは、このシャワー板を通して反応室中に供給される。陽極503にはシーズヒーターなどによる加熱手段が設けられ、基板515が設置されている。ガス供給系の詳細は割愛するが、SiH4やGeH4などが充填されたシリンダー514、ガスの流量を制御するマスフローコントローラー512、ストップバルブ513などから構成されている。排気手段507は、ゲートバルブ508、自動圧力制御弁509、ターボ分子ポンプ(または複合分子ポンプ)510、ドライポンプ511から成っている。ターボ分子ポンプ(または複合分子ポンプ)510、ドライポンプ511は潤滑油を使用しないもので、油の拡散による反応室内の汚染を完全に無くしている。排気速度は、反応室の容積13Lの反応室に対し、一段目に排気速度300L/秒のターボ分子ポンプ、二段目に排気速度40m3/hrのドライポンプを設け、排気系側から有機物の蒸気が逆拡散してくるのを防ぐと共に、反応室の到達真空度を高め、非晶質半導体膜の形成時に不純物元素が膜中に取り込まれることを極力防いでいる。

【0044】

こうしてプラズマCVD法で作製される非晶質半導体膜に含まれる窒素、炭素、酸素のそれぞれの含有量は、二次イオン質量分析法(SIMS)によって測定されている。図11にそのデータを示す。測定に用いた試料は、シリコン基板上にSiH4のみ(SJ0)、水素で10%に希釈したGeH4を5SCCM添加した条件(SJ1)、同10SCCM添加した条件(SJ2)の順に積層したものであるが、いずれの成膜条件においても窒素、炭素の含有量は5×1018/cm3未満、酸素の含有量は1×1019/cm3未満である。

【0045】

絶縁表面上に形成する非晶質半導体膜は10〜100nmの厚さで形成する。非晶質半導体膜にはシリコンに対して原子半径の大きなゲルマニウムを含有し、結晶核の生成密度を小さくすることができる。図12はこうして得られた非晶質半導体膜のゲルマニウム濃度をSIMSにより測定した結果を示す。シリコンに対してゲルマニウムの含有量は、SJ1で1.5原子%、SJ2では3.5原子%、SJ3では11.0原子%の濃度で含まれている。SiH4に対するGeH4の流量比から換算すると、シリコンに対してゲルマニウムは3〜4倍の割合で膜中に取り込まれている。これは、SiH4に対しGeH4の方がグロー放電にて分解するエネルギーが小さいためである。

【0046】

非晶質半導体膜の結晶化は、シリコンの結晶化を助長する元素としてニッケルを用い、500〜600℃の加熱処理、または加熱処理とレーザー処理を行う。代表的な処理条件として、窒素雰囲気中550℃にて4時間の加熱処理及びレーザー処理を行う方法がある。ニッケルは酢酸ニッケルを10ppmの濃度で含有する水溶液を用い、スピナーで塗布する。また、レーザー処理はXeClエキシマレーザー(波長308nm)を用い、照射エネルギー密度50〜200mJ/cm2、重ね合わせ率95〜98%で照射する。レーザー処理は半導体膜が溶融しない条件とし、レーザー光を用いた加熱処理により、未結晶化部分の結晶化や、結晶粒内の欠陥を補修するために行う。

【0047】

図15は結晶質半導体膜のゲルマニウム濃度の分布を示し、図15(A)はレーザー処理無し、図15(B)はレーザー処理有り(471mJ/cm2)、図15(C)はレーザー処理有り(521mJ/cm2)後の状態を示している。いずれにしても、レーザー処理後のものは、ゲルマニウム濃度が膜の表面側で高くなっている。これは、レーザー光の照射により半導体膜が溶融し、ゲルマニウムが偏析したためである。

【0048】

偏析現象は、融液中の不純物濃度と、その融液から成長した結晶中の不純物濃度が異なることで認識される。これは、2元系相図において、液相線と固相線が分離していることに対応する。この場合、固化の過程で融液から結晶内に入りにくい不純物は固化後に結晶表面近傍に偏析する。偏析の度合いを表す界面偏析係数は以下の式で定義される。

【0049】

【数2】

【0050】

通常の引き上げ法や浮融耐帯法などの場合、固液界面の移動速度は1〜5mm/minである。一方、パルスレーザー光の照射後における固液界面の移動速度(固相成長速度)は、1〜10m/secである。従ってパルスレーザー光の照射後におこる固化は、通常の引き上げ法や浮融耐帯法などの場合と比較してその速度が104〜105倍となる。固液界面の移動速度が速いほど、融液中原子が拡散するのに十分な時間がなく、原子配列が液相状態のままで凍結することになる。通常の引き上げ法や浮融耐帯法などの場合、k*=k0(k:平衡偏析係数または平衡分配係数)になるが、成長界面で非平衡度が大きいほどk*はk0よりずれてくる。このような界面偏析係数k*の求め方およびk*の固化速度依存性については、"高速結晶成長−半導体のレーザーアニーリング−:千川純一、佐藤史郎、応用物理 第54巻 第6号(1985)" で詳しく述べられている。

【0051】

図16はパルスレーザー光を照射した結晶質半導体膜中のゲルマニウム濃度の分布を一方向凝固(Normal freezing)の式でフィッティングすることによって、固液界面偏析係数を求めたものである。偏析係数が1の場合には、偏析しないことになるが、シリコン中のゲルマニウムの平衡偏析係数は0.33であることが知られている。図15のデータからパルスレーザー光を照射して溶融−固化させた場合には、偏析係数は0.6が求められている。

【0052】

本発明者が試作したTFTにおいて、結晶質半導体膜の表面にゲルマニウムが偏析した状態の試料では良好な特性を得ることができなかった。その理由は種々あると推測されるが、化学量論的組成のずれから生じる欠陥というよりは、むしろ10〜100ナノ秒のパルスレーザー光の照射により瞬間的に起こった溶融−固化の過程において、融点の低いゲルマニウムが特定の領域に偏析して、かつ、欠陥を生成したためであると推測することができる。

【0053】

結晶質シリコン膜で実績のあるように、本来このような欠陥は水素化処理により終端して不活性化させることができるが、ゲルマニウムの場合には水素の離脱開始温度がシリコンの場合より100℃近く低く、よって水素により欠陥を補償する水素化処理が困難である。

【0054】

プラズマにより生成された水素を用いるプラズマ水素化は有効な手段として採用することができる。それ以外の手法として、効果的な水素化の方法は、プラズマCVD法で200〜300℃、好ましくは250℃にて窒化シリコン膜または酸化窒化シリコン膜を形成し、その後410℃の加熱処理で窒化シリコン膜中の水素を放出させ、250〜350℃の温度で0.1〜1時間保持する加熱処理を行い、このように2段階に温度を変化させて水素化を行う方法である。

【0055】

こうして{101}面に対して高い配向性を示す結晶質半導体膜は、非晶質半導体膜においてゲルマニウムの濃度を0.1〜10原子%の範囲で添加し、当該膜中に含まれる酸素を1×1019/cm3未満に、窒素、炭素の元素の濃度を5×1018/cm3未満とし、膜厚を10〜100nmの範囲として、基板表面と平行な方向の成長が支配的となるようにして、シリコンの結晶化を助長する元素を添加してた後、溶融させることなく加熱処理とレーザー処理を行って結晶化させることで得ることができる。

【0056】

本発明の結晶質半導体膜はこれらの相乗効果により初めて得られるものであり、このような{101}面の配向率の高い結晶質半導体膜はTFTのチャネル形成領域、光起電力素子の光電変換層など素子の特性を決定付けるチャネル形成領域に好適に用いることができる。

【0057】

結晶の配向率に関して言えば、複数の結晶粒が集合している結晶質半導体において、各結晶粒の結晶方位及びその分布は反射電子回折パターン(EBSP:Electron Backscatter diffraction Pattern)により詳細に求めることができる。EBSPは走査型電子顕微鏡(SEM:Scanning Electron Microscopy)に専用の検出器を設け、一次電子の後方散乱から結晶方位を分析する手法である(以下、この手法を便宜上EBSP法と呼ぶ)。EPSPを用いた結晶半導体膜の評価は、"Microtexture Analysis of Location Controlled Large Si Grain Formed by Exciter-Laser Crystallization Method: R. Ishihara and P. F. A. Alkemade, AMLCD'99 Digest of Technical Papers 1999 Tokyo Japan, pp99-102"に紹介されている。

【0058】

この測定方法は、結晶構造を持った試料に電子線が入射すると、後方にも非弾性散乱が起こり、その中には試料中でブラッグ回折による結晶方位に特有の線状パターン(一般に菊地像と呼ばれる)も合わせて観察される。EBSP法は検出器スクリーンに映った菊地像を解析することにより試料の結晶方位を求めている。試料の電子線の当たる位置を移動させつつ方位解析を繰り返す(マッピング測定)ことで、面状の試料について結晶方位または配向の情報を得ることができる。入射電子線の太さは、走査型電子顕微鏡の電子銃のタイプにより異なるが、ショットキー電界放射型の場合、10〜20nmの非常に細い電子線が照射される。マッピング測定では、測定点数が多いほど、また測定領域が広いほど、結晶配向のより平均化した情報を得ることができる。実際には、100×100μm2の領域で、10000点(1μm間隔)〜4000点(0.5μm間隔)の程度の測定を行っている。

【0059】

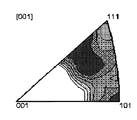

マッピング測定により各結晶粒の結晶方位がすべて求まると、膜に対する結晶配向の状態を統計的に表示できる。図23(A)にEBSP法により求められる逆極点図の例を示す。逆極点図は多結晶体の優先配向を表示する際によく用いられるもので、試料のある特定の面(ここでは膜表面)が、どの格子面に一致しているかを集合的に表示したものである。

【0060】

図23(A)の扇形状の枠は一般に標準三角形と呼ばれるもので、この中に立方晶系における全ての指数が含まれている。またこの図中における長さは、結晶方位における角度に対応している。たとえば{001}と{101}の間は45度、{101}と{111}の間は35.26度、{111}と{001}の間は54.74度である。また、白抜きの点線は{101}からのずれ角5度及び10度の範囲を示している。

【0061】

図23(A)は、マッピングにおける全測定点(この例では11655点)を標準三角形内にプロットしたものである。{101}付近で点の密度が濃くなっていることがわかる。図23(B)は、このような点の集中度を等高線表示したものである。ここで数値は各結晶粒が完全に無秩序な配向だと仮定した場合、すなわち標準三角形内に点を偏りなく分布させた場合に対する倍率を示しており無次元数である。

【0062】

このように特定の指数(ここでは{101})に優先配向している事がわかった場合、その指数近傍にどの程度の結晶粒が集まっているか、その割合を数値化することで、優先配向の度合いをよりイメージしやすくなる。例えば図23(A)に例示した逆極点図において{101}からのずれ角5度及び10度の範囲(図中に白点線で示す)に存在する点数の全体に対する割合を配向率として次式により求めて示すことができる。

【0063】

【数3】

【0064】

この割合は、次のように説明することもできる。図23(A)のように{101}付近に分布が集中している場合、実際の膜においては各結晶粒の<101>方位は基板に概略垂直であるが、その周りにやや揺らぎを持って並んでいることが予想される。この揺らぎの角に許容値を5度、10度と設け、それより小さいものの割合を数値で示してゆく。以上に説明したように許容ずれ角を5度及び10度と定め、それを満たす結晶粒の割合を表示してゆくことにより配向率を求めることができる。

【0065】

図21は石英基板上にプラズマCVD法で作製した54nmの非晶質シリコン膜を600℃にて20時間の加熱処理により結晶化して得られた結晶質シリコン膜の逆極点図を示している。この試料では{111}面に強く配向していることがわかる。また、非晶質シリコン膜にニッケルを添加して550℃にて4時間の熱処理により得られた結晶質半導体膜の逆極点図を図22に示すが、この場合は{101}面の配向率が12%であり、その他に{001}と{111}の中間にある{311}面に配向している。

【0066】

図17は表1におけるSJ2の条件で作製した非晶質シリコン膜を用い、添加する酢酸ニッケルを含有する水溶液のニッケル濃度を0.1〜30ppmの範囲で変化させて作製した結晶質半導体膜の逆極点図を示している。結晶化は、580℃にて4時間の加熱処理を行ったものである。結晶の配向率は{101}に強く配向して、その他に{001}と{111}の中間にある{311}面に配向している傾向が見られる。{101}の配向率はニッケルの濃度依存性が見られ、低濃度になるに従い配向率が高くなっている。表2は図17の逆極点図より、{101}配向率のニッケル水溶液濃度をまとめた結果である。図18は{101}配向率のニッケル濃度依存性を示すグラフであり、GeH4の添加量が5SCCMと10SCCMである場合を示している。配向率は#SGN10の場合にニッケル濃度と強い相関を示し、0.1ppmのニッケル水溶液濃度において61%の配向率が得られている。この結果を表2に示す。また、参照データとして示す図22は、GeH4を添加しないSJ0の条件で作製した結晶質半導体膜の逆極点図であり、{101}の配向率は12%である。

【0067】

【表2】

【0068】

表3は逆極点図を基にして、各種試料について{101}、{001}、{111}、{113}の配向率を、各格子面が膜表面となす角度が5度以内、及び10度以内の範囲にある割合を求めた結果を示している。表3においてHPSはニッケルなどを用いないで結晶化させた結晶質半導体膜の配向率であり、{113}と{111}の配向率が高く、それぞれ18%(10度以内)、12%(10度以内)となっている。また、SJ0は{101}と{113}の配向率が高くなっている。{113}は対称性の立場から等価な格子面の数が他と比較して最も多く、ランダムに配向する多結晶体では発生する確率がその分高くなる。

【0069】

【表3】

【0070】

一方、ゲルマニウムを添加したSJ1〜3においても、試料内の比較において傾向が見られ、膜中に含有するゲルマニウム濃度により結晶の配向が変化することを示している。SJ1、2で特に注目される傾向は、他の格子面に対して{101}格子面の配向が強く、SJ2ではずれ角10度以内が31%、5度以内でも14%となっている。また、SJ1ではずれ角10度以内が20%、5度以内で6%となっている。このような{101}格子面に対する高い配向率はゲルマニウムを添加しない他の試料では達成されない新規な効果が得られている。

【0071】

しかし、SJ3において、膜中に含有するゲルマニウムの含有量が11原子%に増加すると{101}格子面の配向率は低下してしまうことが示されている。また、SJ1において1.5原子%に低下すると配向率が20%低下している。従って、この結果が意味するところは、{101}の配向率を高めるためには非晶質シリコン膜中に含有させるゲルマニウムの濃度には適した範囲があり、その濃度範囲は0.1原子%から10原子%、好ましくは1〜5原子%程度であることがわかる。

【0072】

勿論、このような{101}格子面に対して高い配向性を示す結晶質半導体膜は、添加するゲルマニウムの濃度を0.1〜10原子%の範囲で添加するだけでなく、膜中に含まれる酸素、窒素、炭素の元素の濃度を1×1019/cm3未満にすること、及び膜厚を20〜100nmの範囲として、基板表面と平行な方向の成長が支配的となるようにすることの相乗効果により達成される。

【0073】

さらに、このような結晶質半導体膜の構造をX線回折から評価した。X線回折法では、回折角2θをスキャンしながら回折強度の測定を行う。このとき強度がピークとなった2θの測定からブラッグの式(2d sinθ=λ、λはX線の波長)格子面間隔dを求めることができる。ここで2θスキャンを遅くしてピーク位置を精密に求めると、格子に加わっている歪についての情報も得ることができる。

【0074】

測定は、表3のSJ0で示される結晶質シリコン膜、及びゲルマニウムを含む結晶質シリコン膜について測定を行い、d値を比較した。両者とも石英基板を使用した。膜厚は54nm、酢酸ニッケルの添加量10ppmの水溶液、結晶化500℃にて1時間と580℃にて8時間の加熱処理で作製したものである。測定は膜に平行な格子面のほか、図19示すように試料にあおり角を持たせることにより、膜から60度の角を持った格子面についても行った。この様子を模式的に図20に示す。また、2θの大きい回折を用いたほうが測定精度は向上する。この2つの試料で配向の違いにより測定できる回折が異なっていたが、それぞれについて予備測定により2θの最も大きい回折を調べ、それらについて本測定を行った。本測定に用いた回折は、ゲルマニウムを含む結晶質シリコン膜(試料A)では(440)、結晶質シリコン膜(試料B)では(220)である。

【0075】

あおり角を持たせた場合、2θの値には装置のX線光学系に特有の系統的なずれが生じる。このずれはわずかであるが、今回のような精密な測定ではその影響が無視できなくなるため、あらかじめ標準試料(無配向のタングステン粉末)を用いてあおり角0度、60度で2θ値の測定を行い、そのときのずれ量を用いて補正を行った。標準試料の測定結果を表4に示す。ここでは多結晶試料の本測定における指数と2θが近い回折を選んでいる。即ち、試料Aでは(440)回折(2θ=106度付近)を測定したので、タングステンの(310)回折(2θ=100。628度)で補正を行った。一方、試料Bでは(220)回折(2θ=47度付近)を測定したので、タングステンの(110)回折(2θ=40.2444度)で補正を行った。

【0076】

【表4】

【0077】

試料Aと試料Bの測定結果を表5に示す。あおり角Psiで比較すると、どちらの試料も0度に比べ60度の場合のほうがd値は大きく、従って格子が膜に水平方向に伸びた歪を有していることがわかる。格子定数aに換算して試料間の比較を行うと、試料Aでは両者の差は0.00164nmであるのに対して、試料Bでは0.00272nmと、より大きい値になっている。従って非晶質半導体膜の形成時にゲルマニウムを含ませておくことにより、結晶化後の膜の歪を緩和させることができるということができる。

【0078】

【表5】

【0079】

このような{110}格子面の配向率の高い結晶質半導体膜はTFTのチャネル形成領域、光起電力素子の光電変換層など素子の特性を決定付けるチャネル形成領域に好適に用いることができる。

【0080】

【実施例】

[実施例1]

図1で説明する結晶質半導体膜の作製方法は、ゲルマニウムを含む非晶シリコン膜の全面にシリコンの結晶化を助長する金属元素を添加して結晶化を行う方法である。まず、図1(A)において、基板101はコーニング社の#1773ガラス基板に代表されるガラス基板を用いる。基板101の表面には、ブロッキング層102としてプラズマCVD法でSiH4とN2Oを用い酸化窒化シリコン膜を100nmの厚さに形成する。ブロッキング層102はガラス基板に含まれるアルカリ金属がこの上層に形成する半導体膜中に拡散しないために設ける。

【0081】

シリコンとゲルマニウムから成る非晶質半導体膜103はプラズマCVD法により作製し、SiH4とH2で10%に希釈されたGeH4ガスを反応室に導入し、グロー放電分解して基板101上に堆積させる。その詳細な条件は表1に従うが、ここで採用される条件はSJ1またはSJ2の条件、或いはその中間的な条件である。このシリコンとゲルマニウムから成る非晶質半導体膜103の厚さは50nmの厚さで形成する。シリコンとゲルマニウムから成る非晶質半導体膜103の酸素、窒素、炭素などの不純物を極力低減するために、SiH4は純度99.9999%以上のものを、GeH4は純度99.99%以上のガスを用いる。また、プラズマCVD装置の仕様としては、反応室の容積13Lの反応室に対し、一段目に排気速度300L/秒の複合分子ポンプ、二段目に排気速度40m3/hrのドライポンプを設け、排気系側から有機物の蒸気が逆拡散してくるのを防ぐと共に、反応室の到達真空度を高め、非晶質半導体膜の形成時に不純物元素が膜中に取り込まれることを極力防いでいる。

【0082】

そして図1(B)で示すように、重量換算で10ppmのニッケルを含む酢酸ニッケル塩溶液をスピナーで塗布してニッケル含有層104を形成する。この場合、当該溶液の馴染みをよくするために、シリコンとゲルマニウムから成る非晶質半導体膜103の表面処理として、オゾン含有水溶液で極薄い酸化膜を形成し、その酸化膜をフッ酸と過酸化水素水の混合液でエッチングして清浄な表面を形成した後、再度オゾン含有水溶液で処理して極薄い酸化膜を形成しておく。シリコンの表面は本来疎水性なので、このように酸化膜を形成しておくことにより酢酸ニッケル塩溶液を均一に塗布することができる。

【0083】

次に、500℃にて1時間の加熱処理を行い、シリコンとゲルマニウムから成る非晶質半導体膜中の水素を放出させる。そして、550℃にて4時間に加熱処理を行い結晶化を行う。こうして、図1(C)に示す結晶質半導体膜105が形成される。

【0084】

図25は加熱処理の途中で抜き取った試料の電子顕微鏡写真であり、結晶化の過程でNiSixが非晶質半導体中を移動し、その後に結晶質半導体が形成されている様子を示している。

【0085】

また、図25に示す*1〜*6の点においてエネルギー分散型X線分光分析(EDX:Energy Dispersion X-ray Spectroscopy)で組成を調べた。その結果を表6に示す。非晶質半導体(*1)にはシリコンとゲルマニウムの存在が確認され、また、NiSixの前後の非晶質半導体(*2、*4)においてはシリコンとゲルマニウムの他にニッケルの存在が確認されている。しかし、NiSix中(*3)にはシリコンとニッケルのみでゲルマニウムが存在していない。NiSixの後ろの結晶質半導体(*5)においては、シリコンとゲルマニウムのみが観測され、結晶質半導体と非晶質半導体の境界領域(*6)においても同様な組成となっている。この結果は、上述の結晶化のモデルを裏付けている。

【0086】

【表6】

【0087】

さらに結晶化率(膜の全体積における結晶成分の割合)を高め、結晶粒内に残される欠陥を補修するために、結晶質半導体膜205に対してレーザー光206を照射するレーザー処理を行う。レーザーは波長308nmにて30Hzで発振するエキシマレーザー光を用いる。当該レーザー光は光学系にて100〜300mJ/cm2に集光し、90〜95%のオーバーラップ率をもって半導体膜を溶融させることなくレーザー処理を行う。こうして図1(D)に示すシリコンとゲルマニウムから成る結晶質半導体膜107を得ることができる。

【0088】

[実施例2]

非晶質半導体膜の結晶化を助長する元素を選択的に形成する方法を図2を用いて説明する。図2(A)において、基板120は前述のガラス基板または石英基板を採用する。ガラス基板を用いる場合には、実施例1と同様にブロッキング層を設ける。

【0089】

シリコンとゲルマニウムから成る非晶質半導体121は、は実施例1と同様にプラズマCVD法で形成しても良いし、イオン注入法またはイオンドープ法によりゲルマニウムを導入しても良い。また、減圧CVD法で、Si2H6とGeH4を450〜500℃の温度で分解して形成する方法も採用可能である。

【0090】

シリコンとゲルマニウムから成る非晶質半導体121上に150nmの厚さの酸化シリコン膜122を形成する。酸化シリコン膜の作製方法は限定されないが、例えば、オルトケイ酸テトラエチル(Tetraethyl Ortho Silicate:TEOS)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させ形成する。

【0091】

次に、酸化シリコン膜122に開孔部123を形成し、重量換算で10ppmのニッケルを含む酢酸ニッケル塩溶液を塗布する。これにより、ニッケル含有層124が形成され、ニッケル含有層124は開孔部123の底部のみでゲルマニウムを含む非晶質シリコン膜121と接触する。

【0092】

図2(B)で示す結晶化は、加熱処理の温度500〜650℃で4〜24時間、例えば570℃にて14時間の熱処理を行う。この場合、結晶化はニッケルが接した非晶質シリコン膜の部分が最初に結晶化し、そこから基板の表面と平行な方向に結晶化が進行する。こうして形成された結晶質シリコン膜125は棒状または針状の結晶が集合して成り、その各々の結晶は巨視的に見ればある特定の方向性をもって成長している。その後、酸化シリコン膜222を除去すれば結晶質シリコン膜225を得ることができる(図2(C))。

【0093】

[実施例3]

実施例1、2で説明する方法に従い作製される結晶質シリコン膜には結晶化において利用したニッケルに代表される元素が残存している。それは膜中において一様に分布していないにしろ、平均的な濃度とすれば、1×1019/cm3を越える濃度で残存している。勿論、このような状態でもTFTをはじめ各種半導体装置のチャネル形成領域に用いることが可能であるが、より好ましくは、ゲッタリングにより当該元素を除去することが望ましい。

【0094】

本実施例はゲッタリング方法の一例を図3を用いて説明する。図3(A)において、基板130は実施例1のガラス基板、或いは石英基板が採用される。ガラス基板を用いる場合には、実施例1と同様にブロッキング層を設ける。また、結晶質半導体膜131は実施例1または2のいずれの方法で作製されたものであっても同様に適用される。結晶質半導体膜131の表面には、マスク用の酸化シリコン膜132が150nmの厚さに形成され、開孔部133が設けられ結晶質半導体膜が露出した領域が設けられている。実施例2に従う場合には、図2(A)で示す酸化シリコン膜122をそのまま利用可能であり、図2(B)の工程の後からそのまま本実施例の工程に移行することもできる。そして、イオンドープ法によりリンを添加して、1×1019〜1×1022/cm3の濃度のリン添加領域135を形成する。

【0095】

そして、図3(B)に示すように、窒素雰囲気中で550〜800℃、5〜24時間、例えば600℃にて12時間の熱処理を行うと、リン添加領域135がゲッタリングサイトとして働き、結晶質シリコン膜131に残存していた触媒元素はリン添加領域135に偏析させることができる。

【0096】

その後、図3(C)で示すようにマスク用の酸化シリコン膜132と、リンが添加領域135とをエッチングして除去することにより、結晶化の工程で使用した金属元素の濃度が1×1017/cm3未満にまで低減された結晶質半導体膜136を得ることができる。

【0097】

[実施例4]

次に、このようなシリコンとゲルマニウムを成分とする結晶質半導体膜を用いて、TFTを作製する例を示す。図5は本実施例の作製工程を説明する図である。

【0098】

図5(A)において、基板210上にシリコンとゲルマニウムを成分とする結晶質半導体膜212を形成するが、この結晶質半導体膜212は、上記実施例1〜3で示す工程により作製される何れかのものが採用される。TFTを作製するに当たっては、素子分離のため所定の大きさにエッチングし、島状に分割しておく。基板210がガラス基板である場合には、ブロッキング層211を設ける。

【0099】

絶縁膜213はTFTにおいてゲート絶縁膜として利用されるものであり30〜200nmの厚さで形成する。この絶縁膜213はプラズマCVD法によりSiH4とN2Oとから作製される酸化窒化シリコン膜、或いはTEOSとN2Oとから作製される酸化窒化シリコン膜などで形成する。本実施例では前者を選択し、70nmの厚さに形成する。

【0100】

絶縁膜213上には、タンタル、タングステン、チタン、アルミニウム、モリブデンから選ばれた一種または複数種の元素を成分とする導電性材料でゲート電極214を形成する。

【0101】

次に、図5(B)で示すように、TFTのソース及びドレイン領域を形成する一導電型の不純物領域216を形成する。この不純物領域216はイオンドープ法により形成し、nチャネル型TFTであればリン、砒素に代表される周期律表第15族の元素、pチャネル型TFTであればボロンに代表される周期律表第13族の元素を添加する。

【0102】

その後、プラズマCVD法により作製される窒化シリコン膜、酸化窒化シリコン膜により第1の層間絶縁膜217を形成する。第1の層間絶縁膜217はプラズマCVD法で200〜300℃の基板温度で形成し、その後、窒素雰囲気中350〜450℃、好ましくは410℃の温度で加熱処理を行う。この温度で第1の層間絶縁膜中の水素を放出させ、その後250〜350℃にて0.1〜1時間程度保持する加熱処理を行い、結晶質半導体膜の水素化を行う。このような二段階の加熱処理により結晶質半導体膜の水素化を行うことで、特に350℃以上の温度では水素化しにくいゲルマニウムのダングリングボンド(未結合種)を水素化し、補償することができる。さらに、ソース及びドレイン電極218を形成しTFTを得ることができる。

【0103】

尚、ここではTFTをシングルゲートの構造で示したが、勿論、複数のゲート電極を設けたマルチゲート構造を採用することもできる。

【0104】

本発明で得られるシリコンとゲルマニウムを成分とする結晶質半導体膜は、{101}の配向率が高く、形成されるチャネル形成領域はゲート絶縁膜との界面特性が良好である。また、結晶粒界及び結晶粒内の欠陥密度が低く、高い電界効果移動度を得ることができる。ここでは、TFTをシングルドレインの構造で説明したが、低濃度ドレイン(LDD)構造や、LDDがゲート電極とオーバーラップした構造のTFTを形成することもできる。本発明で作製されるTFTは、アクティブマトリクス型の液晶表示装置やEL表示装置を作製するためのTFTとて、また従来の半導体基板にて作製されるLSIに代わる薄膜集積回路を実現するTFTとして用いることができる。

【0105】

[実施例5]

図4は本発明の結晶質半導体膜を用いて作製される逆スタガ型のTFTの断面図である。逆スタガ型TFTは、ガラスまたは石英などの基板201上にゲート電極260、261が形成されており、シリコンゲルマニウムを成分とする結晶質半導体膜263、264は、ゲート絶縁膜262上に形成されている。結晶質半導体膜263、264は実施例1〜3の方法により作製されるいずれの結晶質半導体膜であっても適用可能である。

【0106】

nチャネル型TFT280は結晶質半導体膜263を用いて作製され、チャネル形成領域273とn型不純物(ドナー)をドーピングして作製されるLDD領域274及びソースまたはドレイン領域275が形成されている。pチャネル型TFT281は結晶質半導体膜264を用いて作製され、チャネル形成領域276とp型不純物(アクセプタ)をドーピングして作製されるソースまたはドレイン領域277が形成されている。

【0107】

チャネル形成領域273、276上にはチャネル保護膜265、266が形成され、第1の層間絶縁膜267、第2の層間絶縁膜268を介してソースまたはドレイン電極269〜272が形成されている。水素化処理は、第1の層間絶縁膜267を窒化シリコン膜または酸化窒化シリコン膜で形成し、その後、窒素雰囲気中350〜450℃、好ましくは410℃の温度で加熱処理を行う。この温度で第1の層間絶縁膜中の水素を放出させ、その後250〜350℃にて0.1〜1時間程度保持する加熱処理を行い、結晶質半導体膜の水素化を行うことができる。

【0108】

このような逆スタガ型のTFTを用いても、アクティブマトリクス型の液晶表示装置やEL表示装置の駆動回路を形成することができる。それ以外にも、このようなnチャネル型TFTまたはpチャネル型TFTは、画素部を形成するトランジスタに応用することができる。尚、ここではTFTをシングルゲートの構造で示したが、勿論、複数のゲート電極を設けたマルチゲート構造を採用することもできる。このようなTFTは、従来の半導体基板にて作製されるLSIに代わる薄膜集積回路を実現するTFTとして用いることができる。

【0109】

[実施例6]

本実施例は、nチャネル型TFTとpチャネル型TFTとを相補的に組み合わせたCMOS型のTFTを作製する一例について図6を用いて説明する。図6(A)において、基板301上にゲルマニウムを含有する結晶質シリコン膜を形成する。ゲルマニウムを含有する結晶質シリコン膜は実施例1〜3で示す方法により作製されるいずれのものを適用しても良い。TFTを作製するに当たっては、素子分離のため所定の大きさにエッチングし、島状に分割して半導体層331〜333を形成する。基板301がガラス基板である場合には、ブロッキング層302を設ける。

【0110】

ブロッキング層302としてプラズマCVD法でSiH4とN2Oを用い酸化窒化シリコン膜を50〜200nmの厚さに形成する。その他の形態として、プラズマCVD法でSiH4とNH3とN2Oから作製される酸化窒化シリコン膜を50nm、SiH4とN2Oから作製される酸化窒化シリコン膜を100nm積層させた2層構造や、或いは、窒化シリコン膜とTEOS(Tetraethyl Ortho Silicate)を用いて作製される酸化シリコン膜を積層させた2層構造としても良い。

【0111】

ブロッキング層302及びその上に形成する非晶質半導体膜はいずれもプラズマCVD法で形成することが可能であり、これらの層を連続して、シングルチャンバー方式のCVD装置において同一反応室中で、或いは、マルチチャンバー方式のCVD装置において各反応室間を移動させながら連続して形成することができる。いずれにしても、大気解放せずに成膜することでブロッキング層と非晶質半導体膜の界面を清浄にしておくことができる。

【0112】

絶縁膜334はゲート絶縁膜として利用するものであり、プラズマCVD法またはスパッタ法を用い、膜厚を40〜150nmの厚さで形成する。本実施例では、70nmの厚さで酸化窒化シリコン膜を用いて形成する。特に、SiH4とN2OにO2を添加させて作製する酸化窒化シリコン膜は膜中の固定電荷密度を低減させることが可能となり、ゲート絶縁膜として好ましい材料である。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく、酸化シリコン膜や酸化タンタル膜などの絶縁膜を単層または積層構造として用いても良い。

【0113】

そして、絶縁膜334上にゲート電極を形成するための第1導電膜335と第2導電膜336とを形成する。本実施例では、第1導電膜335を窒化タンタルまたはチタンで50〜100nmの厚さに形成し、第2導電膜336をタングステンで100〜300nmの厚さに形成する。これらの材料は、窒素雰囲気中における400〜600℃の熱処理でも安定であり、抵抗率が著しく増大することがない。

【0114】

次に図6(B)に示すように、レジストによるマスク337を形成し、ゲート電極を形成するための第1のエッチング処理を行う。エッチング方法に限定はないが、好適にはICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いる。エッチング用ガスにCF4とCl2を混合し、0.5〜2Pa、好ましくは1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した場合にはタングステン膜、窒化タンタル膜及びチタン膜の場合でも、それぞれ同程度の速度でエッチングすることができる。

【0115】

上記エッチング条件では、レジストによるマスクの形状と、基板側に印加するバイアス電圧の効果により端部をテーパー形状とすることができる。テーパー部の角度は15〜45°となるようにする。また、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させると良い。W膜に対する酸化窒化シリコン膜の選択比は2〜4(代表的には3)であるので、オーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50nm程度エッチングされる。こうして、第1のエッチング処理により第1導電膜と第2導電膜から成る第1形状の導電層338〜340(第1の導電層338a〜340aと第2導電層338b〜340b)を形成する。341はゲート絶縁膜であり、第1の形状の導電層で覆われない領域は20〜50nm程度エッチングされ薄くなる。

【0116】

さらに図6(C)に示すように第2のエッチング処理を行う。エッチングはICPエッチング法を用い、エッチングガスにCF4とCl2とO2を混合して、1Paの圧力でコイル型の電極に500WのRF電力(13.56MHz)を供給してプラズマを生成する。基板側(試料ステージ)には50WのRF(13.56MHz)電力を投入し、第1のエッチング処理に比べ低い自己バイアス電圧を印加する。このような条件によりタングステン膜を異方性エッチングし、第1の導電層である窒化タンタル膜またはチタン膜を残存させるようにする。こうして、第2形状の導電層342〜344(第1の導電膜342a〜344aと第2の導電膜342b〜344b)を形成する。345はゲート絶縁膜であり、第2の形状の導電層342〜344で覆われない領域はさらに20〜50nm程度エッチングされて膜厚が薄くなる。

【0117】

そして、第1のドーピング処理を行う。本ドーピング処理では、nチャネル型TFTのLDD領域を形成するためにn型の不純物(ドナー)をドーピングする。その方法はイオンドープ法若しくはイオン注入法で行う。例えば、イオンドープ法を用い、加速電圧を70〜120keVとし、1×1013/cm2のドーズ量で行い、第1の不純物領域を形成する。ドーピングは、第2の導電膜342b〜344bを不純物元素に対するマスクとして用い、第1の導電膜342a〜344aの下側の領域に不純物元素が添加されるようにドーピングする。こうして、第1の導電膜342a〜344aと一部が重なる第1の不純物領域346〜348が形成される。第1の不純物領域は1×1017〜1×1019/cm3の範囲の濃度で形成する。

【0118】

次に、図6(D)に示すように、レジストでマスク349〜351を形成し、第2のドーピング処理を行いう。第2のドーピング処理は、nチャネル型TFTのソースまたはドレイン領域を形成するためにn型の不純物(ドナー)をドーピングする。イオンドープ法の条件はドーズ量を1×1013〜5×1014/cm2として行う。n型の不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いる。レジストでマスク349〜351は個々にその形状を最適化することが可能であり、第2形状の導電層の外側まで覆う形状のものとして、先に形成した第1の不純物領域と重なるようにすることでLDD領域を形成することができる。こうして、第2の不純物領域352〜354を形成する。第2の不純物領域725〜729おけるリン(P)濃度は1×1020〜1×1021/cm3の範囲となるようにする。

【0119】

そして、図6(E)に示すように、レジストによるマスク355を形成し、pチャネル型TFTを形成する島状半導体層331にp型の不純物(アクセプタ)をドーピングする。典型的にはボロン(B)を用いる。第3の不純物領域356、357の不純物濃度は2×1020〜2×1021/cm3となるようにし、含有するリン濃度の1.5〜3倍のボロンを添加して導電型を反転させる。

【0120】

以上までの工程でそれぞれの島状半導体層に不純物領域が形成される。第2形状の導電層342〜344はゲート電極となる。その後、図6(F)に示すように、窒化シリコン膜または酸化窒化シリコン膜から成る保護絶縁膜358をプラズマCVD法で形成する。そして導電型の制御を目的としてそれぞれの島状半導体層に添加された不純物元素を活性化する工程を行う。活性化はファーネスアニール炉を用いる熱アニール法で行うことが好ましい。その他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することもできる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には400〜600℃で行うものであり、本実施例では500℃で4時間の熱処理を行う。

【0121】

さらに、窒化シリコン膜359を形成し、350〜450℃、好ましくは410℃の加熱処理を行う。この温度で第1の層間絶縁膜中の水素を放出させ、その後250〜350℃にて0.1〜1時間程度保持する加熱処理を行い、結晶質半導体膜の水素化を行う。このような二段階の加熱処理により結晶質半導体膜の水素化を行うことで、特に350℃以上の温度では水素化しにくいゲルマニウムのダングリングボンド(未結合種)を水素化し、補償することができる。

【0122】

層間絶縁膜360は、ポリイミド、アクリルなどの有機絶縁物材料で形成し表面を平坦化する。勿論、プラズマCVD法でTEOS(Tetraethyl Ortho Silicate)を用いて形成される酸化シリコン膜を適用しても良いが、平坦性を高める観点からは前記有機物材料を用いることが望ましい。

【0123】

次いで、コンタクトホールを形成し、アルミニウム(Al)、チタン(Ti)、タンタル(Ta)などを用いて、ソースまたはドレイン配線361〜366を形成する。

【0124】

pチャネル型TFT370にはチャネル形成領域363、ソース領域またはドレイン領域として機能する第3の不純物領域356、357を有している。nチャネル型TFT371はチャネル形成領域368、第2形状の導電層343から成るゲート電極と重なる第1不純物領域362とソース領域またはドレイン領域として機能する第1不純物領域353を有している。nチャネル型TFT372はチャネル形成領域369、第2形状の導電層344から成るゲート電極と重なる第1不純物領域348a、ゲート電極の外側に形成される第1不純物領域348b、ソース領域またはドレイン領域として機能する第1不純物領域353を有している。第1不純物領域362、348aはゲート電極とオーバーラップするLDD領域であり、ドレイン端に形成される高電界領域を緩和してホットキャリア効果によるTFTに劣化を防ぐ上で効果がある。第1不純物領域348bはLDD領域であり、本実施例で示す工程では、オフ電流値を低減するために最適な寸法を設定することができる。

【0125】

以上の工程で、nチャネル型TFTとpチャネル型TFTとを相補的に組み合わせたCMOS型のTFTを得ることができる。本実施例で示す工程は、各TFTに要求される特性を考慮してLDDを設計し、同一基板内において作り分けることができる。このようなCMOS型のTFTは、アクティブマトリクス型の液晶表示装置やEL表示装置の駆動回路を形成することを可能とする。それ以外にも、このようなnチャネル型TFTまたはpチャネル型TFTは、画素部を形成するトランジスタに応用することができる。さらに、従来の半導体基板にて作製されるLSIに代わる薄膜集積回路を実現するTFTとして用いることができる。尚、ここではTFTをシングルゲートの構造で示したが、勿論、複数のゲート電極を設けたマルチゲート構造を採用することもできる。

【0126】

また、CMOS回路を組み合わせることで基本論理回路を構成した、さらに複雑なロジック回路(信号分割回路、D/Aコンバータ、オペアンプ、γ補正回路など)をも構成することができ、さらにはメモリやマイクロプロセッサをも形成することが可能である。

【0127】

[実施例7]

本実施例は、画素部と駆動回路が同一基板上に形成されたモノシリック型の液晶表示装置の構成例を図7、8を用いて説明する。画素部におけるスイッチング用のTFTと駆動回路のnチャネル型及びpチャネル型のTFTは、いずれも本発明のゲルマニウムを含む結晶質シリコン膜を用いて活性領域を形成している。ゲルマニウムを含有する結晶質シリコン膜は実施例1〜3で示す方法により作製されるいずれのものを適用することができる。

【0128】

図7において、基板401は、好適にはバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板などを用いる。その他に石英基板を用いても良い。ガラス基板を用いる場合にはブロッキング層402が形成される。

【0129】

画素部445におけるスイッチング用の画素TFT442と駆動回路444のnチャネル型TFT441及びpチャネル型TFT440の構造に限定はないが、本実施例では実施例6により作製されるTFTを用いて説明する。勿論、実施例4または実施例5のTFTを採用することも可能である。

【0130】

駆動回路444には配線408、417及びソースまたはドレイン配線418〜421が形成されている。また、画素部445においては、画素電極424、ゲート配線423、接続電極422、ソース配線409が形成されている。

【0131】

駆動回路444のpチャネル型TFT440には、半導体層403にチャネル形成領域426、ソース領域またはドレイン領域として機能する第3不純物領域427を有している。このpチャネル型TFT453は実施例6のpチャネル型TFT370と同様にして作製することができる。

【0132】

nチャネル型TFT441には、半導体層404にチャネル形成領域428、第2形状の導電層411から成るゲート電極と重なる第1不純物領域429とソース領域またはドレイン領域として機能する第2不純物領域430を有している。このnチャネル型TFT441は実施例6のnチャネル型TFT371と同様にして作製することができる。

【0133】

画素部のnチャネル型TFT442には、半導体層405にチャネル形成領域431、ゲート電極を形成する第2形状の導電層412と重なる第1不純物領域432a(GOLD領域)、ゲート電極の外側に形成される第1不純物領域432b(LDD領域)とソース領域またはドレイン領域として機能する第2不純物領域433、434、435を有している。このnチャネル型TFT442は実施例6のnチャネル型TFT372と同様にして作製することができる。また、保持容量443の一方の電極として機能する半導体層406は第6不純物領域437、第5不純物領域438と不純物が添加されない領域436が形成されている。

【0134】

画素部445においては、接続電極422によりソース配線409は、画素TFT442のソースまたはドレイン領域433と電気的な接続が形成される。また、ゲート配線423は、ゲート電極として機能する第3形状の導電層412と電気的な接続が形成される。また、画素電極424は、画素TFT442のソースまたはドレイン領域435及び保持容量443の一方の電極である半導体層406の不純物領域438と接続している。

【0135】

図7における画素部445の断面図は、図8で示すA−A'線に対応したものである。ゲート電極として機能する第3形状の導電層412は隣接する画素の保持容量の一方の電極を兼ね、画素電極452と接続する半導体層453と重なる部分で容量を形成している。また、ソース配線407と画素電極424及び隣接する画素電極451との配置関係は、画素電極424、451の端部をソース配線407上に設け、重なり部を形成することにより、迷光を遮り遮光性を高めている。

【0136】

[実施例8]

本実施例では実施例7で作製した各TFTから、アクティブマトリクス型の液晶表示装置を作製する一例を示す。図26では透過型の液晶表示装置を作製するために、画素部445の層間絶縁膜上に透明導電膜で形成した画素電極601が形成されている。画素電極は画素のnチャネル型TFT442に接続する補助電極609、及び保持容量443の補助電極610と接続されている。これらの補助電極とゲート線608、接続電極607、駆動回路444の各TFTのソースまたはドレイン配線603〜606、配線602は、フォトレジストまたは感光性ポリイミドまたは感光性アクリルなどからなる有機樹脂611〜619をマスクとして、その下層に形成されている導電膜をエッチングして形成されている。

【0137】

有機樹脂611〜619は、配線を形成するための導電膜上に当該有機樹脂材料を全面に塗布し、光露光プロセスにより図27に示すようにパターン形成されている。その後、オフセット印刷により5〜20mPa・の粘度のポリイミド樹脂層を形成し、200℃にて焼成して配向膜を形成している。オフセット印刷により塗布したポリイミド樹脂は、焼成の段階で有機樹脂611〜619とその下層の配線または電極の段差部にうまく回り込み、その端部を覆うことができる。

その後、液晶を配向させるためラビングを行う。

【0138】

対向側の基板621には透明導電膜で形成する対向電極622と配向膜623を形成し、画素部445及び駆動回路444が形成されている基板と対向基板621とをシール材624で貼り合わせる。シール材624にはフィラー(図示せず)が混入されていて、このフィラーとスペーサ(図示せず)によって均一な間隔を持って貼り合わされている。その後、両基板の間に液晶625を注入する。液晶材料には公知の液晶材料を用いれば良い。例えば、TN液晶の他に、電場に対して透過率が連続的に変化する電気光学応答性を示す、無しきい値反強誘電性混合液晶を用いることもできる。この無しきい値反強誘電性混合液晶には、V字型の電気光学応答特性を示すものもある。このようにして図27に示すアクティブマトリクス型の液晶表示装置が完成する。

【0139】

[実施例9]

本実施例は、上記実施例4〜6で得られるTFTを用いてEL(エレクトロルミネセンス)表示装置を作製する一例を図27を用いて説明する。

【0140】

同一の絶縁体上に画素部とそれを駆動する駆動回路を有した発光装置の例(但し封止前の状態)を図27に示す。なお、駆動回路には基本単位となるCMOS回路を示し、画素部には一つの画素を示す。このCMOS回路は実施例6に従えば得ることができる。

【0141】

図27において、基板700は絶縁体であり、その上にはnチャネル型TFT701、pチャネル型TFT702、pチャネル型TFTからなるスイッチングTFT703およびnチャネル型TFTからなる電流制御TFT704が形成されている。これらのTFTのチャネル形成領域は、本発明に基づき作製される結晶質半導体膜で形成され、その具体的な作製方法は実施例1〜3に示されている。

【0142】

nチャネル型TFT701およびpチャネル型TFT702は実施例6を参照すれば良いので省略する。また、スイッチングTFT703はソース領域およびドレイン領域の間に二つのチャネル形成領域を有した構造(ダブルゲート構造)となっている。なお、本実施例はダブルゲート構造に限定されることなく、チャネル形成領域が一つ形成されるシングルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。

【0143】

また、電流制御TFT704のドレイン領域705の上には第2層間絶縁膜707が設けられる前に、第1層間絶縁膜706にコンタクトホールが設けられている。これは第2層間絶縁膜707にコンタクトホールを形成する際に、エッチング工程を簡単にするためである。第2層間絶縁膜707にはドレイン領域705に到達するようにコンタクトホールが形成され、ドレイン領域705に接続された画素電極708が設けられている。画素電極708はEL素子の陰極として機能する電極であり、周期表の1族もしくは2族に属する元素を含む導電膜を用いて形成されている。本実施例では、リチウムとアルミニウムとの化合物からなる導電膜を用いる。

【0144】

次に、713は画素電極708の端部を覆うように設けられた絶縁膜であり、本明細書中ではバンクと呼ぶ。バンク713は珪素を含む絶縁膜もしくは樹脂膜で形成すれば良い。樹脂膜を用いる場合、樹脂膜の比抵抗が1×106〜1×1012Ωm(好ましくは1×108〜1×1010Ωm)となるようにカーボン粒子もしくは金属粒子を添加すると、成膜時の絶縁破壊を抑えることができる。

【0145】

また、EL素子709は画素電極(陰極)708、EL層711および陽極712からなる。陽極712は、仕事関数の大きい導電膜、代表的には酸化物導電膜が用いられる。酸化物導電膜としては、酸化インジウム、酸化スズ、酸化亜鉛もしくはそれらの化合物を用いれば良い。なお、本明細書中では発光層に対して正孔注入層、正孔輸送層、正孔阻止層、電子輸送層、電子注入層もしくは電子阻止層を組み合わせた積層体をEL層と定義する。

【0146】

尚、ここでは図示しないが陽極712を形成した後、EL素子709を完全に覆うようにしてパッシベーション膜を設けることは有効である。パッシベーション膜としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いる。

【0147】

[実施例10]

本発明の半導体装置は、各種多様の電子機器の表示装置や各種集積回路、或いは、従来の集積回路に代わる回路用途に応用することができる。このような半導体装置には、携帯情報端末(電子手帳、モバイルコンピュータ、携帯電話等)、ビデオカメラ、スチルカメラ、パーソナルコンピュータ、テレビ、プロジェクター等が挙げられる。それらの一例を図28〜図30に示す。

【0148】

図28(A)は携帯電話であり、表示用パネル2701、操作用パネル2702、接続部2703から成り、表示用パネル2701には液晶表示装置またはEL表示装置に代表される表示装置2704、音声出力部2705、アンテナ2709などが設けられている。操作パネル2702には操作キー2706、電源スイッチ2702、音声入力部27058などが設けられている。本発明は表示装置2904及びそれに付随する半導体集積回路を形成することができる。

【0149】

図28(B)はビデオカメラであり、本体9101、液晶表示装置またはEL表示装置に代表される表示装置9102、音声入力部9103、操作スイッチ9104、バッテリー9105、受像部9106から成っている。本発明は表示装置9102及びそれに付随する半導体集積回路に適用することができる。

【0150】

図28(C)はモバイルコンピュータ或いは携帯型情報端末であり、本体9201、カメラ部9202、受像部9203、操作スイッチ9204、液晶表示装置またはEL表示装置に代表される表示装置9205で構成されている。本発明は半導体装置は表示装置9205及びそれに付随する半導体集積回路に適用することができる。

【0151】

図28(D)はテレビ受像器であり、本体9401、スピーカ9402、液晶表示装置またはEL表示装置に代表される表示装置9403、受信装置9404、増幅装置9405等で構成される。本発明は表示装置9403及びそれに付随する半導体集積回路に適用することができる。

【0152】

図28(E)は携帯書籍であり、本体9501、液晶表示装置またはEL表示装置に代表される表示装置9502、9503、記憶媒体9504、操作スイッチ9505、アンテナ9506から構成されており、ミニディスク(MD)やDVDに記憶されたデータや、アンテナで受信したデータを表示するものである。本発明は表示装置9502、9503や、記憶媒体9504及びそれに付随する半導体集積回路に適用することができる。

【0153】

図29(A)はパーソナルコンピュータであり、本体9601、画像入力部9602、液晶表示装置またはEL表示装置に代表される表示装置9603、キーボード9604で構成される。本発明は表示装置9601や、内蔵する各種集積回路に適用することができる。

【0154】

図29(B)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体9701、液晶表示装置またはEL表示装置に代表される表示装置9702、スピーカ部9703、記録媒体9704、操作スイッチ9705で構成される。なお、この装置は記録媒体としてDVD(Digtial Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示装置9702や、内蔵する各種集積回路に適用することができる。

【0155】

図29(C)はデジタルカメラであり、本体9801、液晶表示装置またはEL表示装置に代表される表示装置9802、接眼部9803、操作スイッチ9804、受像部(図示しない)で構成される。本発明は表示装置9802や、内蔵する各種集積回路に適用することができる。

【0156】

図30(A)はフロント型プロジェクターであり、投射装置3601、スクリーン3602で構成される。本発明は投射装置3601やその他の信号制御回路に適用することができる。

【0157】

図30(B)はリア型プロジェクターであり、本体3701、投射装置3702、ミラー3703、スクリーン3704で構成される。本発明は投射装置3702やその他の信号制御回路に適用することができる。

【0158】

尚、図30(C)は、図30(A)及び図30(B)中における投射装置3601、3702の構造の一例を示した図である。投射装置3601、3702は、光源光学系3801、ミラー3802、3804〜3806、ダイクロイックミラー3803、プリズム3807、液晶表示装置3808、位相差板3809、投射光学系3810で構成される。投射光学系3810は、投射レンズを含む光学系で構成される。本実施例は三板式の例を示したが、特に限定されず、例えば単板式であってもよい。また、図30(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。

【0159】

また、図30(D)は、図30(C)中における光源光学系3801の構造の一例を示した図である。本実施例では、光源光学系3801は、リフレクター3811、光源3812、レンズアレイ3813、3814、偏光変換素子3815、集光レンズ3816で構成される。なお、図30(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

【0160】

ここでは図示しなかったが、本発明はその他にもナビゲーションシステムをはじめ冷蔵庫、洗濯機、電子レンジ、固定電話機、ファクシミリなどに組み込む表示装置としても適用することも可能である。このように本発明の適用範囲はきわめて広く、さまざまな製品に適用することができる。

【0161】

【発明の効果】

以上のとおり、本発明の結晶質半導体膜を用いて半導体装置の活性領域を形成することができる。特に、薄膜トランジスタのチャネル形成領域を形成するのに適している。このような結晶質半導体膜を用いたTFTは、アクティブマトリクス型の液晶表示装置やEL表示装置を作製するためのTFTとて、また従来の半導体基板にて作製されるLSIに代わる薄膜集積回路を実現するTFTとして用いることができる。

【図面の簡単な説明】

【図1】 本発明の結晶質半導体膜の作製方法を説明する図。

【図2】 本発明の結晶質半導体膜の作製方法を説明する図。

【図3】 本発明の結晶質半導体膜の作製方法を説明する図。

【図4】 本発明の結晶質半導体膜を用いた逆スタガ型のTFTの構造を説明する断面図。

【図5】 本発明の結晶質半導体膜を用いてTFTを作製する工程を説明する図。

【図6】 本発明の結晶質半導体膜を用いてCMOS構造のTFTを作製する工程を説明する図。

【図7】 本発明の結晶質半導体膜を用いた表示装置の構造を説明する断面図。

【図8】 画素部における画素構造の上面図。

【図9】 本発明に用いるプラズマCVD装置の構成を示す図。

【図10】 本発明に用いるプラズマCVD装置の反応室の構成を示す図。

【図11】 SIMSにより測定されたSiH4、GeH4、H2ガスより作製された試料のC、N、O濃度を示すグラフ。

【図12】 SIMSにより測定された結晶質半導体膜中のGe濃度分布を示すグラフ。

【図13】 結晶核の隣接間距離を示す累積度数グラフ。

【図14】 GeH4の流量と結晶核発生密度との関係を示すグラフ。

【図15】 パルスレーザー光を照射した結晶質半導体膜中におけるゲルマニウムの分布をSIMSにより求めたグラフ。

【図16】 結晶質半導体膜中のゲルマニウム濃度の分布を一方向凝固(Normal freezing)の式でフィッティングすることによって固液界面偏析係数を求めた図。

【図17】 EBSP法により求められる本発明の結晶質半導体膜の逆極点図。

【図18】 Ni水溶液濃度と{101}配向率の関係を示すグラフ。

【図19】 X線回折測定と試料あおり角を説明する図。

【図20】 試料あおり角と、回折に寄与する格子面を説明する図。

【図21】 石英基板上にプラズマCVD法で作製した54nmの非晶質シリコン膜を600℃にて20時間の加熱処理により結晶化して得られた結晶質シリコン膜の逆極点図。

【図22】 非晶質シリコン膜にニッケルを添加して550℃にて4時間の熱処理により得られた結晶質半導体膜の逆極点図。

【図23】 EBSP法で得られる逆極点図の一例(模式図)。

【図24】 NiSixを核とした結晶化のモデルを説明する図。

【図25】 NiSixを核とした結晶化の様子を示す電子顕微鏡写真。

【図26】 本発明の結晶質半導体膜を用いた液晶表示装置の構造を説明する断面図。

【図27】 本発明の結晶質半導体膜を用いたEL表示装置の構造を説明する断面図。

【図28】 半導体装置の一例を示す図。

【図29】 半導体装置の一例を示す図。

【図30】 プロジェクターの一例を示す図。

Claims (3)

- シリコンに対するゲルマニウムの組成比が0.1原子%以上10原子%以下であり、窒素及び炭素の濃度が5×1018/cm3未満であり、酸素の濃度が1×1019/cm3未満である非晶質シリコン膜を10nm乃至100nmの膜厚で形成し、

前記非晶質シリコン膜にニッケルを、酢酸ニッケルを含有する水溶液のニッケル濃度を1〜30ppmで添加して450℃以上660℃以下で加熱処理を行って結晶構造を有するシリコン膜を形成し、

前記結晶構造を有するシリコン膜に50mJ/cm2以上300mJ/cm2以下で10〜100ナノ秒のパルスレーザ光を照射し、

前記結晶構造を有するシリコン膜上に水素を含有する窒化シリコン膜または酸化窒化シリコン膜を形成し、

窒素雰囲気中で350〜450℃の加熱処理と、その後の250〜350℃で0.1〜1時間保持する加熱処理との二段階の加熱処理によりシリコン膜の水素化を行うことを特徴とする半導体装置の作製方法。 - シリコンに対するゲルマニウムの組成比が0.1原子%以上10原子%以下であり、窒素及び炭素の濃度が5×1018/cm3未満であり、酸素の濃度が1×1019/cm3未満である非晶質シリコン膜を10nm乃至100nmの膜厚で形成し、

前記非晶質シリコン膜にニッケルを、酢酸ニッケルを含有する水溶液のニッケル濃度を1〜30ppmで添加して450℃以上660℃以下で加熱処理を行って結晶構造を有するシリコン膜を形成し、

前記結晶構造を有するシリコン膜に50mJ/cm2以上300mJ/cm2以下で10〜100ナノ秒のパルスレーザ光を照射し、

前記結晶構造を有するシリコン膜上に水素を含有する窒化シリコン膜または酸化窒化シリコン膜を形成し、

窒素雰囲気中で350〜450℃の加熱処理と、その後の250〜350℃で0.1〜1時間保持する加熱処理との二段階の加熱処理によりシリコン膜の水素化を行い、

反射電子線回折パターン法で検出される{101}格子面の前記結晶構造を有するシリコン膜の表面となす角が10度以内である割合が20%以上であり、かつ、{001}格子面の前記結晶構造を有するシリコン膜の表面となす角が10度以内である割合が3%以下であり、かつ、{111}格子面の前記結晶構造を有するシリコン膜の表面となす角が10度以内である割合が5%以下の結晶構造を有する半導体膜を形成することを特徴とする半導体装置の作製方法。 - シリコンに対するゲルマニウムの組成比が0.1原子%以上10原子%以下であり、窒素及び炭素の濃度が5×1018/cm3未満であり、酸素の濃度が1×1019/cm3未満である非晶質シリコン膜を10nm乃至100nmの膜厚で形成し、

前記非晶質シリコン膜にニッケルを、酢酸ニッケルを含有する水溶液のニッケル濃度を1〜30ppmで添加して450℃以上660℃以下で加熱処理を行って結晶構造を有するシリコン膜を形成し、

前記結晶構造を有するシリコン膜に50mJ/cm2以上300mJ/cm2以下で10〜100ナノ秒のパルスレーザ光を照射し、

前記結晶構造を有するシリコン膜上に水素を含有する窒化シリコン膜または酸化窒化シリコン膜を形成し、

窒素雰囲気中で350〜450℃の加熱処理と、その後の250〜350℃で0.1〜1時間保持する加熱処理との二段階の加熱処理によりシリコン膜の水素化を行い、

反射電子線回折パターン法で検出される{101}格子面の前記結晶構造を有するシリコン膜の表面となす角が5度以内である割合が5%以上であり、かつ、{001}格子面の前記結晶構造を有するシリコン膜の表面となす角が10度以内である割合が3%以下であり、かつ、{111}格子面の前記結晶構造を有するシリコン膜の表面となす角が10度以内である割合が5%以下の結晶構造を有する半導体膜を形成することを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000202985A JP4865122B2 (ja) | 2000-07-04 | 2000-07-04 | 半導体装置の作製方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000202985A JP4865122B2 (ja) | 2000-07-04 | 2000-07-04 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002025905A JP2002025905A (ja) | 2002-01-25 |

| JP2002025905A5 JP2002025905A5 (ja) | 2007-10-11 |

| JP4865122B2 true JP4865122B2 (ja) | 2012-02-01 |

Family

ID=18700439

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000202985A Expired - Fee Related JP4865122B2 (ja) | 2000-07-04 | 2000-07-04 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4865122B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4674937B2 (ja) * | 2000-08-02 | 2011-04-20 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP3961310B2 (ja) | 2002-02-21 | 2007-08-22 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR100843345B1 (ko) * | 2007-09-06 | 2008-07-03 | 고삼석 | 교량용 신축이음부의 시공방법 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3514891B2 (ja) * | 1994-10-07 | 2004-03-31 | 株式会社半導体エネルギー研究所 | 半導体装置およびその作製方法 |

| JP2000114173A (ja) * | 1998-08-07 | 2000-04-21 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| JP2002083974A (ja) * | 2000-06-19 | 2002-03-22 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

-

2000

- 2000-07-04 JP JP2000202985A patent/JP4865122B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002025905A (ja) | 2002-01-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4827325B2 (ja) | 半導体装置の作製方法 | |

| US7307282B2 (en) | Thin film transistors and semiconductor device | |

| JP5072157B2 (ja) | 半導体装置の作製方法 | |

| US6828587B2 (en) | Semiconductor device | |

| US7368335B2 (en) | Semiconductor device and method of manufacturing the same | |

| US8067278B2 (en) | Semiconductor device and method for manufacturing the same | |

| US7534670B2 (en) | Semiconductor device and manufacturing method of the same | |

| US7122450B2 (en) | Process for manufacturing a semiconductor device | |

| JP2002252174A (ja) | 半導体薄膜の形成方法、半導体装置及び電気光学装置の製造方法、これらの方法の実施に使用する装置、並びに半導体装置及び電気光学装置 | |

| JP3999138B2 (ja) | 半導体装置の製造方法、表示装置の製造方法、および電子機器の製造方法 | |

| JP4869504B2 (ja) | 半導体装置の作製方法 | |

| JP4974425B2 (ja) | 半導体装置の作製方法 | |

| JP4865122B2 (ja) | 半導体装置の作製方法 | |

| JP4993822B2 (ja) | 半導体装置の作製方法 | |

| JP4646460B2 (ja) | 半導体装置の作製方法 | |

| JP4216003B2 (ja) | 半導体装置の作製方法 | |

| JP4674937B2 (ja) | 半導体装置の作製方法 | |

| JP4827324B2 (ja) | 半導体装置の作製方法 | |

| JP4837871B2 (ja) | 半導体装置の作製方法 | |

| JPH11284199A (ja) | 半導体装置およびその作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070703 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070823 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100708 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100720 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100726 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100825 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110802 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110909 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111004 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111014 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111108 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111110 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141118 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141118 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |