JP4838502B2 - 画像表示装置とその製造方法 - Google Patents

画像表示装置とその製造方法 Download PDFInfo

- Publication number

- JP4838502B2 JP4838502B2 JP2004221606A JP2004221606A JP4838502B2 JP 4838502 B2 JP4838502 B2 JP 4838502B2 JP 2004221606 A JP2004221606 A JP 2004221606A JP 2004221606 A JP2004221606 A JP 2004221606A JP 4838502 B2 JP4838502 B2 JP 4838502B2

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- potential

- common electrode

- control

- display element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 14

- 239000003990 capacitor Substances 0.000 claims description 20

- 230000006866 deterioration Effects 0.000 claims description 9

- 238000000034 method Methods 0.000 claims description 9

- 230000001747 exhibiting effect Effects 0.000 claims description 4

- 230000003247 decreasing effect Effects 0.000 claims 1

- 239000000463 material Substances 0.000 description 11

- 239000003086 colorant Substances 0.000 description 7

- 238000010586 diagram Methods 0.000 description 4

- 238000005401 electroluminescence Methods 0.000 description 4

- 239000011368 organic material Substances 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 239000007787 solid Substances 0.000 description 3

- 101100214494 Solanum lycopersicum TFT4 gene Proteins 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 239000002346 layers by function Substances 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000012044 organic layer Substances 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

- G09G3/3241—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/028—Generation of voltages supplied to electrode drivers in a matrix display other than LCD

Description

表示部と電圧源とを含む画像表示装置であって、

前記表示部が表示素子と画素回路とを有し、

前記画素回路が、

前記表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該表示素子に駆動電流を供給するためのPチャネル型駆動トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記駆動トランジスタの前記制御電極の電位を設定するための制御トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を保持するためのコンデンサと、

を備え、

前記表示素子の他方の端子は第2の共通電極に接続されており、

前記電圧源は、前記Pチャネル型駆動トランジスタの前記制御電極に設定された電位に基づいて前記表示素子を発光させて測定した輝度変動を、前記制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げるための又は前記第2の共通電極の電位を上げるための調整回路を備えることを特徴とする画像表示装置である。

カラー表示部と電圧源とを含む画像表示装置であって、

前記カラー表示部が、第1の色を呈する第1の表示素子と、第2の色を呈する第2の表示素子と、第1の画素回路と、第2の画素回路と、を有し、

前記第1の画素回路が、

前記第1の表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該第1の表示素子に駆動電流を供給するための第1のPチャネル型駆動トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第1の制御トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第1のコンデンサと、を備え、

前記第2の画素回路が、

前記第2の表示素子の一方の端子に接続される第1主電極と、第2の共通電極に接続される第2主電極と、制御電極と、を有する、該第2の表示素子に駆動電流を供給するための第2のPチャネル型駆動トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第2の制御トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第2の共通電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第2のコンデンサと、を備え、

前記第1の表示素子の他方の端子は第3の共通電極、前記第2の表示素子の他方の端子は第4の共通電極に接続されており、

前記電圧源は、前記Pチャネル型駆動トランジスタの前記制御電極に設定された電位に基づいて前記表示素子を発光させて測定した輝度変動を、少なくとも前記第1の制御トランジスタがオフ状態におけるリーク電流又は前記第2の制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位又は前記第2の共通電極の電位を下げるための若しくは前記第3の共通電極の電位又は前記第4の共通電極の電位を上げるための調整回路を備えることを特徴とする画像表示装置である。

表示部が表示素子と画素回路と調整回路とを有し、

前記画素回路が、

前記表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該表示素子に駆動電流を供給するためのPチャネル型駆動トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を設定するための制御トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を保持するためのコンデンサと、

を備え、

前記表示素子の他方の端子は第2の共通電極に接続されており、

前記調整回路によって前記第1の共通電極又は前記第2の共通電極の電位の調整が可能である画像表示装置の製造方法であって、

(i)表示部を用意するステップと、

(ii)前記第1の共通電極と前記第2の共通電極との間に電圧を印加するステップと、

(iii)前記表示部の発光輝度の変動を測定するステップと、

(iv)測定した前記発光輝度の変動を、前記制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げる又は前記第2の共通電極の電位を上げるように、前記調整回路を調整するステップと、

を含むことを特徴とする画像表示装置の製造方法である。

カラー表示部が、第1の色を呈する第1の表示素子と、第2の色を呈する第2の表示素子と、第1の画素回路と、第2の画素回路と、第1の調整回路と、第2の調整回路と、を有し、

前記第1の画素回路が、

前記第1の表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該第1の表示素子に駆動電流を供給するための第1のPチャネル型駆動トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第1の制御トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第1のコンデンサと、を備え、

前記第2の画素回路が、

前記第2の表示素子の一方の端子に接続される第1主電極と、第2の共通電極に接続される第2主電極と、制御電極と、を有する、該第2の表示素子に駆動電流を供給するための第2のPチャネル型駆動トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第2の制御トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第2の共通電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第2のコンデンサと、を備え、

前記第1の表示素子の他方の端子は第3の共通電極、前記第2の表示素子の他方の端子は第4の共通電極に接続され、

前記第1の調整回路は、前記第1の共通電極又は前記第3の共通電極の電位の調整が可能であり、

前記第2の調整回路は、前記第2の共通電極又は前記第4の共通電極の電位の調整が可能である画像表示装置の製造方法であって、

(i)カラー表示部を用意するステップと、

(ii)前記第1の共通電極と前記第3の共通電極との間又は前記第2の共通電極と前記第4の共通電極との間に電圧を印加するステップと、

(iii)前記表示部の発光輝度の変動を測定するステップと、

(iv)測定した前記発光輝度の変動を、少なくとも前記第1の制御トランジスタがオフ状態におけるリーク電流又は前記第2の制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げるように又は前記第3の共通電極の電位を上げるように前記第1の調整回路を調整する若しくは前記第2の共通電極の電位を下げるように又は前記第4の共通電極の電位を上げるように前記第2の調整回路を調整するステップと、

を含むことを特徴とする画像表示装置の製造方法である。

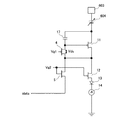

図1は、本発明の画像形成装置の実施形態のひとつの画素回路と電位源である電源装置及び電位源であるグランド部及び調整回路であるDC−DCコンバータの接続の状態を略等価的に示した図である。

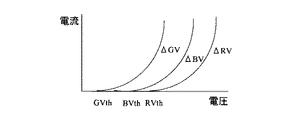

実施の形態1では、駆動用トランジスタの主電極のうちの表示素子が接続される主電極ではない主電極に供給する電位を調整回路で調整した構成を示したが、本実施形態では、表示素子に対して駆動用トランジスタが接続される側とは反対側に供給する電位を調整回路で調整する構成を採用している。具体的には図6では調整回路を第1の共通電極608に供給する電位を調整するように配置しているが、本実施形態では調整回路を第2の共通電極609に供給する電位を調整するように配置する。具体的には調整回路を第2の電位源となるグランド部と各画素回路の表示素子が共通に接続される共通電極との間に設けている。

上記実施の形態1、2では第1の共通電極は異なる色に対応する表示素子を有する画素回路が共通に接続されるものであった。

図9に、本実施形態の画像形成装置の構成を概略的に示す。図中、上記実施形態1〜3と共通する部分は同じ符号を付与している。

13 OEL

14 電流計

15 電源

17 コンデンサ

19 可変電圧電源

36 表示制御部

37 コントローラ

38 映像信号変換メモリ

601 走査回路

602 変調回路

603 電源装置

604 DC−DCコンバータ

605 表示部

606 走査信号配線

607 変調信号配線

608,609 共通電極

701〜703 DC−DCコンバータ

704〜706,901〜903 共通電極

904〜906 DC−DCコンバータ

1001 ラッチ

1002 Hシフトレジスタ

1003 Vシフトレジスタ

Claims (6)

- 表示部と電圧源とを含む画像表示装置であって、

前記表示部が表示素子と画素回路とを有し、

前記画素回路が、

前記表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該表示素子に駆動電流を供給するためのPチャネル型駆動トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記駆動トランジスタの前記制御電極の電位を設定するための制御トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を保持するためのコンデンサと、

を備え、

前記表示素子の他方の端子は第2の共通電極に接続されており、

前記電圧源は、前記Pチャネル型駆動トランジスタの前記制御電極に設定された電位に基づいて前記表示素子を発光させて測定した輝度変動を、前記制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げるための又は前記第2の共通電極の電位を上げるための調整回路を備えることを特徴とする画像表示装置。 - カラー表示部と電圧源とを含む画像表示装置であって、

前記カラー表示部が、第1の色を呈する第1の表示素子と、第2の色を呈する第2の表示素子と、第1の画素回路と、第2の画素回路と、を有し、

前記第1の画素回路が、

前記第1の表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該第1の表示素子に駆動電流を供給するための第1のPチャネル型駆動トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第1の制御トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第1のコンデンサと、を備え、

前記第2の画素回路が、

前記第2の表示素子の一方の端子に接続される第1主電極と、第2の共通電極に接続される第2主電極と、制御電極と、を有する、該第2の表示素子に駆動電流を供給するための第2のPチャネル型駆動トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第2の制御トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第2の共通電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第2のコンデンサと、を備え、

前記第1の表示素子の他方の端子は第3の共通電極、前記第2の表示素子の他方の端子は第4の共通電極に接続されており、

前記電圧源は、前記Pチャネル型駆動トランジスタの前記制御電極に設定された電位に基づいて前記表示素子を発光させて測定した輝度変動を、少なくとも前記第1の制御トランジスタがオフ状態におけるリーク電流又は前記第2の制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位又は前記第2の共通電極の電位を下げるための若しくは前記第3の共通電極の電位又は前記第4の共通電極の電位を上げるための調整回路を備えることを特徴とする画像表示装置。 - 表示部が表示素子と画素回路と調整回路とを有し、

前記画素回路が、

前記表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該表示素子に駆動電流を供給するためのPチャネル型駆動トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を設定するための制御トランジスタと、

前記Pチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記Pチャネル型駆動トランジスタの前記制御電極の電位を保持するためのコンデンサと、

を備え、

前記表示素子の他方の端子は第2の共通電極に接続されており、

前記調整回路によって前記第1の共通電極又は前記第2の共通電極の電位の調整が可能である画像表示装置の製造方法であって、

(i)表示部を用意するステップと、

(ii)前記第1の共通電極と前記第2の共通電極との間に電圧を印加するステップと、

(iii)前記表示部の発光輝度の変動を測定するステップと、

(iv)測定した前記発光輝度の変動を、前記制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げる又は前記第2の共通電極の電位を上げるように、前記調整回路を調整するステップと、

を含むことを特徴とする画像表示装置の製造方法。 - 前記(iv)のステップは、表示素子の劣化による電圧上昇を加味することを特徴とする請求項3に記載の画像表示装置の製造方法。

- カラー表示部が、第1の色を呈する第1の表示素子と、第2の色を呈する第2の表示素子と、第1の画素回路と、第2の画素回路と、第1の調整回路と、第2の調整回路と、を有し、

前記第1の画素回路が、

前記第1の表示素子の一方の端子に接続される第1主電極と、第1の共通電極に接続される第2主電極と、制御電極と、を有する、該第1の表示素子に駆動電流を供給するための第1のPチャネル型駆動トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第1の制御トランジスタと、

前記第1のPチャネル型駆動トランジスタの前記制御電極と前記第1の共通電極との間に設けられ、前記第1のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第1のコンデンサと、を備え、

前記第2の画素回路が、

前記第2の表示素子の一方の端子に接続される第1主電極と、第2の共通電極に接続される第2主電極と、制御電極と、を有する、該第2の表示素子に駆動電流を供給するための第2のPチャネル型駆動トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第1主電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を設定するための第2の制御トランジスタと、

前記第2のPチャネル型駆動トランジスタの前記制御電極と前記第2の共通電極との間に設けられ、前記第2のPチャネル型駆動トランジスタの前記制御電極の電位を保持するための第2のコンデンサと、を備え、

前記第1の表示素子の他方の端子は第3の共通電極、前記第2の表示素子の他方の端子は第4の共通電極に接続され、

前記第1の調整回路は、前記第1の共通電極又は前記第3の共通電極の電位の調整が可能であり、

前記第2の調整回路は、前記第2の共通電極又は前記第4の共通電極の電位の調整が可能である画像表示装置の製造方法であって、

(i)カラー表示部を用意するステップと、

(ii)前記第1の共通電極と前記第3の共通電極との間又は前記第2の共通電極と前記第4の共通電極との間に電圧を印加するステップと、

(iii)前記表示部の発光輝度の変動を測定するステップと、

(iv)測定した前記発光輝度の変動を、少なくとも前記第1の制御トランジスタがオフ状態におけるリーク電流又は前記第2の制御トランジスタがオフ状態におけるリーク電流を抑制することで抑制すべく、前記第1の共通電極の電位を下げるように又は前記第3の共通電極の電位を上げるように前記第1の調整回路を調整する若しくは前記第2の共通電極の電位を下げるように又は前記第4の共通電極の電位を上げるように前記第2の調整回路を調整するステップと、

を含むことを特徴とする画像表示装置の製造方法。 - 前記(iv)のステップは、前記第1の表示素子又は前記第2の表示素子の劣化による電圧上昇を加味することを特徴とする請求項5に記載の画像表示装置の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004221606A JP4838502B2 (ja) | 2003-08-07 | 2004-07-29 | 画像表示装置とその製造方法 |

| US10/909,388 US7119367B2 (en) | 2003-08-07 | 2004-08-03 | Display apparatus |

| US11/503,966 US7537946B2 (en) | 2003-08-07 | 2006-08-15 | Display apparatus |

| US12/425,459 US7812349B2 (en) | 2003-08-07 | 2009-04-17 | Display apparatus |

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003288401 | 2003-08-07 | ||

| JP2003288401 | 2003-08-07 | ||

| JP2003288520 | 2003-08-07 | ||

| JP2003288520 | 2003-08-07 | ||

| JP2004221606A JP4838502B2 (ja) | 2003-08-07 | 2004-07-29 | 画像表示装置とその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005070761A JP2005070761A (ja) | 2005-03-17 |

| JP2005070761A5 JP2005070761A5 (ja) | 2006-08-10 |

| JP4838502B2 true JP4838502B2 (ja) | 2011-12-14 |

Family

ID=34279535

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004221606A Expired - Fee Related JP4838502B2 (ja) | 2003-08-07 | 2004-07-29 | 画像表示装置とその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US7119367B2 (ja) |

| JP (1) | JP4838502B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4838502B2 (ja) * | 2003-08-07 | 2011-12-14 | キヤノン株式会社 | 画像表示装置とその製造方法 |

| TWI252446B (en) * | 2004-08-05 | 2006-04-01 | Chunghwa Picture Tubes Ltd | Active matrix organic electro-luminescent display panel and fabrication method thereof |

| US7811146B2 (en) * | 2004-09-24 | 2010-10-12 | Chunghwa Picture Tubes, Ltd. | Fabrication method of active matrix organic electro-luminescent display panel |

| JP4769569B2 (ja) * | 2005-01-06 | 2011-09-07 | キヤノン株式会社 | 画像形成装置の製造方法 |

| KR100729060B1 (ko) * | 2005-03-31 | 2007-06-14 | 삼성에스디아이 주식회사 | 발광 표시장치 및 그의 구동방법 |

| KR101219036B1 (ko) * | 2005-05-02 | 2013-01-07 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| KR100635511B1 (ko) * | 2005-09-30 | 2006-10-17 | 삼성에스디아이 주식회사 | 유기 전계발광 표시장치 |

| JP2009037083A (ja) * | 2007-08-03 | 2009-02-19 | Sony Corp | El表示パネル、配線駆動装置及び電子機器 |

| EP2308047A1 (en) * | 2008-06-27 | 2011-04-13 | GVBB Holdings S.A.R.L | Editing device and editing method |

| KR102217614B1 (ko) * | 2014-10-23 | 2021-02-22 | 삼성디스플레이 주식회사 | 표시 장치 및 이를 포함하는 전자기기 |

| CN104392690B (zh) * | 2014-10-28 | 2017-04-19 | 中国电子科技集团公司第五十五研究所 | 应用于具有公共阳极的amoled像素单元电路 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS63280300A (ja) | 1987-05-13 | 1988-11-17 | 小糸工業株式会社 | 情報表示装置 |

| US5990629A (en) | 1997-01-28 | 1999-11-23 | Casio Computer Co., Ltd. | Electroluminescent display device and a driving method thereof |

| JPH10232649A (ja) | 1997-02-21 | 1998-09-02 | Casio Comput Co Ltd | 電界発光表示装置およびその駆動方法 |

| JP3887826B2 (ja) | 1997-03-12 | 2007-02-28 | セイコーエプソン株式会社 | 表示装置及び電子機器 |

| EP0978114A4 (en) * | 1997-04-23 | 2003-03-19 | Sarnoff Corp | PIXEL STRUCTURE WITH LIGHT EMITTING DIODE AND ACTIVE MATRIX AND METHOD |

| US6229506B1 (en) | 1997-04-23 | 2001-05-08 | Sarnoff Corporation | Active matrix light emitting diode pixel structure and concomitant method |

| JP2001056667A (ja) | 1999-08-18 | 2001-02-27 | Tdk Corp | 画像表示装置 |

| JP4145495B2 (ja) * | 2000-01-11 | 2008-09-03 | 株式会社半導体エネルギー研究所 | 表示装置、コンピュータ、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置、ゲーム機器、携帯情報端末、及び画像再生装置 |

| JP2002023666A (ja) | 2000-07-10 | 2002-01-23 | Matsushita Electric Ind Co Ltd | 電光表示装置 |

| JP2002032058A (ja) * | 2000-07-18 | 2002-01-31 | Nec Corp | 表示装置 |

| JP2002215095A (ja) | 2001-01-22 | 2002-07-31 | Pioneer Electronic Corp | 発光ディスプレイの画素駆動回路 |

| JP2002304156A (ja) * | 2001-01-29 | 2002-10-18 | Semiconductor Energy Lab Co Ltd | 発光装置 |

| JP2003202837A (ja) * | 2001-12-28 | 2003-07-18 | Pioneer Electronic Corp | 表示パネルの駆動装置及び駆動方法 |

| US7274363B2 (en) | 2001-12-28 | 2007-09-25 | Pioneer Corporation | Panel display driving device and driving method |

| JP2003280583A (ja) * | 2002-03-26 | 2003-10-02 | Sanyo Electric Co Ltd | 有機el表示装置 |

| JP4838502B2 (ja) * | 2003-08-07 | 2011-12-14 | キヤノン株式会社 | 画像表示装置とその製造方法 |

-

2004

- 2004-07-29 JP JP2004221606A patent/JP4838502B2/ja not_active Expired - Fee Related

- 2004-08-03 US US10/909,388 patent/US7119367B2/en not_active Expired - Fee Related

-

2006

- 2006-08-15 US US11/503,966 patent/US7537946B2/en not_active Expired - Fee Related

-

2009

- 2009-04-17 US US12/425,459 patent/US7812349B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005070761A (ja) | 2005-03-17 |

| US7812349B2 (en) | 2010-10-12 |

| US20050059185A1 (en) | 2005-03-17 |

| US7537946B2 (en) | 2009-05-26 |

| US20060275938A1 (en) | 2006-12-07 |

| US20090203157A1 (en) | 2009-08-13 |

| US7119367B2 (en) | 2006-10-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7537946B2 (en) | Display apparatus | |

| EP2388764B1 (en) | Method and System for Programming and Driving Active Matrix Light Emitting Device Pixel | |

| JP3854161B2 (ja) | 表示装置 | |

| US8736525B2 (en) | Display device using capacitor coupled light emission control transistors for mobility correction | |

| JP4501429B2 (ja) | 画素回路及び表示装置 | |

| US7609234B2 (en) | Pixel circuit and driving method for active matrix organic light-emitting diodes, and display using the same | |

| JP5455307B2 (ja) | 画像表示装置およびその駆動方法 | |

| JP5157467B2 (ja) | 自発光型表示装置およびその駆動方法 | |

| EP2345023B1 (en) | Display device with compensation for variations in pixel transistors mobility | |

| JP2012230392A (ja) | ディスプレイ装置および光変調器用制御回路 | |

| JP2006293370A (ja) | アクティブマトリックス型ディスプレイ及び駆動方法 | |

| JP2005164894A (ja) | 画素回路及び表示装置とこれらの駆動方法 | |

| JP4831392B2 (ja) | 画素回路及び表示装置 | |

| JP2010008522A (ja) | 表示装置 | |

| JP5646925B2 (ja) | 画像表示装置およびその駆動方法 | |

| JP4501059B2 (ja) | 画素回路及び表示装置 | |

| JP2007272224A (ja) | 表示素子の駆動回路及び画像表示装置 | |

| JP5789585B2 (ja) | 表示装置および電子機器 | |

| US20090184900A1 (en) | Image display device and display device control method | |

| JP2006030336A (ja) | 画像表示装置及びその駆動方法と走査線駆動回路 | |

| JP2006038964A (ja) | 画素回路及び表示装置とこれらの駆動方法 | |

| JP2010008520A (ja) | 表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060626 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060626 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100223 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100423 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101019 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110517 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110713 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110927 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110930 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141007 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141007 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |