JP4758780B2 - 半導体装置の製造方法及び半導体装置の実装装置 - Google Patents

半導体装置の製造方法及び半導体装置の実装装置 Download PDFInfo

- Publication number

- JP4758780B2 JP4758780B2 JP2006019285A JP2006019285A JP4758780B2 JP 4758780 B2 JP4758780 B2 JP 4758780B2 JP 2006019285 A JP2006019285 A JP 2006019285A JP 2006019285 A JP2006019285 A JP 2006019285A JP 4758780 B2 JP4758780 B2 JP 4758780B2

- Authority

- JP

- Japan

- Prior art keywords

- elements

- substrate

- semiconductor device

- air suction

- vacuum

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/7525—Means for applying energy, e.g. heating means

- H01L2224/753—Means for applying energy, e.g. heating means by means of pressure

- H01L2224/75301—Bonding head

- H01L2224/75302—Shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/7565—Means for transporting the components to be connected

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/7598—Apparatus for connecting with bump connectors or layer connectors specially adapted for batch processes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01019—Potassium [K]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12041—LED

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/1615—Shape

- H01L2924/16195—Flat cap [not enclosing an internal cavity]

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Supply And Installment Of Electrical Components (AREA)

- Wire Bonding (AREA)

Description

また、本発明は、前記コレットが上昇することにより前記粘着テープを上方に押圧して前記粘着テープ上の一の当該素子を前記空気吸引孔に押し付け、前記コレットが下降することにより前記粘着テープの巻き取りテンションの作用により一の当該素子の下面から前記粘着テープが剥がされることを特徴とする。

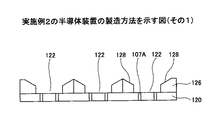

上記の陽極接合が行われると、シリコン基板120を構成するSiと、ガラス板140中の酸素とが結合し、接合力が良好で安定した接合が行われる。また、陽極接合では、樹脂材料を用いた接合と異なり、発光素子124が封止される凹部122の内部空間を汚染するようなガス、不純物などが殆ど発生することがない。

20,120 基板

30 配線パターン

40,124 発光素子

60 半導体装置の実装装置

70,170 真空吸着部

72,172 空気吸引孔

76 電磁式三方弁

78 真空発生装置

80 制御部

122 凹部

126 壁部

128 傾斜面

140 ガラス板

Claims (7)

- 基板に複数の素子を実装する半導体装置の製造方法において、

前記基板の各素子取付位置に対応する所定間隔で配された複数の空気吸引孔が形成された真空吸着部に対して前記複数の素子が貼着された粘着テープを水平移動させて前記複数の素子を前記複数の空気吸引孔に対向させる位置に移動させる工程と、

前記複数の空気吸引孔から空気を吸引して前記真空吸着部に前記複数の素子を所定間隔で吸着させる工程と、

前記複数の空気吸引孔から空気を吸引して前記真空吸着部に前記複数の素子を所定間隔で吸着させる際、前記粘着テープの前記素子が粘着されている側の反対側から一の当該素子を前記真空吸着部に押圧するコレットを前記空気吸引孔と対向する位置へ移動させて一の当該素子を前記空気吸引孔に押圧する工程と、

前記真空吸着部に吸着された前記素子を前記粘着テープから離間させる工程と、

前記真空吸着部に吸着された前記複数の素子を前記基板上の所定位置に載置する工程と、

前記複数の素子を前記基板の複数の所定位置に載置して前記真空吸着部による前記複数の素子に対する吸着を解除する工程と、

前記複数の素子の端子を前記基板の配線パターンに同時に接合する工程と、

を有することを特徴とする半導体装置の製造方法。 - 前記コレットが上昇することにより前記粘着テープを上方に押圧して前記粘着テープ上の一の当該素子を前記空気吸引孔に押し付け、前記コレットが下降することにより前記粘着テープの巻き取りテンションの作用により一の当該素子の下面から前記粘着テープが剥がされることを特徴とする請求項1に記載の半導体装置の製造方法。

- 前記基板に前記素子を囲む複数の壁部を形成する工程をさらに有することを特徴とする請求項1または2の何れかに記載の半導体装置の製造方法。

- 前記複数の壁部の上端を透過性のカバーにより封止する工程をさらに有することを特徴とする請求項3に記載の半導体装置の製造方法。

- 前記壁部は、前記素子の上方に向けて広がるように傾斜された傾斜面を有することを特徴とする請求項3または4の何れかに記載の半導体装置の製造方法。

- 前記壁部は、前記素子から発光された光を反射させる反射面を有することを特徴とする請求項3乃至5の何れかに記載の半導体装置の製造方法。

- 基板に複数の素子を実装する半導体装置の実装装置において、

前記基板の各素子取付位置に対応する所定間隔で配された複数の空気吸引孔により前記複数の素子を吸着する真空吸着部と、

前記複数の素子が貼着された粘着テープを水平移動させて前記複数の素子を前記真空吸着部の複数の空気吸引孔に対向させる位置に移動させる素子供給ラインと、

前記空気吸引孔と対向する位置へ移動され、前記粘着テープの前記素子が粘着されている側の反対側から一の当該素子を前記真空吸着部に押圧し、一の当該素子を前記空気吸引孔に押圧するコレットと、

前記複数の空気吸引孔より空気を吸引する真空発生装置と、

前記真空発生装置と前記複数の空気吸引孔との間に配された切替弁と、

前記コレットを上昇させて前記粘着テープを押圧して一の当該素子を前記空気吸引孔に押し付けると共に、前記複数の素子を前記基板上の所定位置に搬送するまで前記切替弁を前記真空発生装置と前記複数の空気吸引孔とを連通して前記複数の素子を吸着し、前記コレットを下降させて前記真空吸着部に吸着された前記複数の素子から前記粘着テープを離間させ、前記複数の素子を前記基板上の所定位置に載置した後、前記切替弁を切替えて前記複数の素子に対する吸着を解除する制御部と、

を有することを特徴とする半導体装置の実装装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006019285A JP4758780B2 (ja) | 2006-01-27 | 2006-01-27 | 半導体装置の製造方法及び半導体装置の実装装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006019285A JP4758780B2 (ja) | 2006-01-27 | 2006-01-27 | 半導体装置の製造方法及び半導体装置の実装装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007201259A JP2007201259A (ja) | 2007-08-09 |

| JP2007201259A5 JP2007201259A5 (ja) | 2008-12-04 |

| JP4758780B2 true JP4758780B2 (ja) | 2011-08-31 |

Family

ID=38455519

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006019285A Active JP4758780B2 (ja) | 2006-01-27 | 2006-01-27 | 半導体装置の製造方法及び半導体装置の実装装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4758780B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20190080954A1 (en) * | 2017-09-08 | 2019-03-14 | Samsung Electronics Co., Ltd. | Apparatus for manufacturing semiconductor |

| US11637211B2 (en) | 2021-02-02 | 2023-04-25 | Rockwell Collins, Inc. | Optically clear thermal spreader for status indication within an electronics package |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2464102A (en) | 2008-10-01 | 2010-04-07 | Optovate Ltd | Illumination apparatus comprising multiple monolithic subarrays |

| CN103009776B (zh) * | 2011-09-24 | 2017-09-22 | 宸鸿科技(厦门)有限公司 | 基板的贴合方法 |

| JP6839143B2 (ja) * | 2017-09-28 | 2021-03-03 | 芝浦メカトロニクス株式会社 | 素子実装装置、素子実装方法及び素子実装基板製造方法 |

| KR20200135069A (ko) * | 2019-05-24 | 2020-12-02 | (주)포인트엔지니어링 | 마이크로 led 디스플레이 제작 방법 및 이를 이용한 마이크로 led 디스플레이 |

| CN112017988B (zh) * | 2019-05-31 | 2024-03-19 | 成都辰显光电有限公司 | 转移设备 |

| JP2022027096A (ja) * | 2020-07-31 | 2022-02-10 | 日亜化学工業株式会社 | 発光モジュールの製造方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5636196A (en) * | 1979-09-03 | 1981-04-09 | Sony Corp | Apparatus for assembling electronic device circuit |

| JPH0369200A (ja) * | 1989-08-08 | 1991-03-25 | Sanyo Electric Co Ltd | 電子部品自動装着装置 |

| JPH0677317A (ja) * | 1992-08-26 | 1994-03-18 | Mitsubishi Electric Corp | 半導体装置の組立方法 |

| JP2000058924A (ja) * | 1998-08-06 | 2000-02-25 | Shichizun Denshi:Kk | 表面実装型発光ダイオード及びその製造方法 |

| JP4170475B2 (ja) * | 1998-11-12 | 2008-10-22 | 松下電器産業株式会社 | 電子部品の実装装置および実装方法 |

| JP4078825B2 (ja) * | 2001-10-30 | 2008-04-23 | ソニー株式会社 | 回路基板の製造方法、並びに表示装置の製造方法 |

| JP2003163378A (ja) * | 2001-11-26 | 2003-06-06 | Citizen Electronics Co Ltd | 表面実装型発光ダイオード及びその製造方法 |

| JP2003243720A (ja) * | 2002-02-14 | 2003-08-29 | Citizen Electronics Co Ltd | 発光ダイオードの製造方法 |

| JP3924609B2 (ja) * | 2002-04-26 | 2007-06-06 | クロダニューマティクス株式会社 | 真空切換弁装置 |

| JP4296770B2 (ja) * | 2002-11-11 | 2009-07-15 | パナソニック株式会社 | 半導体チップのピックアップ方法 |

| JP4064795B2 (ja) * | 2002-11-28 | 2008-03-19 | 松下電器産業株式会社 | 電子部品実装装置 |

| JP4574251B2 (ja) * | 2003-09-17 | 2010-11-04 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

-

2006

- 2006-01-27 JP JP2006019285A patent/JP4758780B2/ja active Active

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20190080954A1 (en) * | 2017-09-08 | 2019-03-14 | Samsung Electronics Co., Ltd. | Apparatus for manufacturing semiconductor |

| US10804132B2 (en) | 2017-09-08 | 2020-10-13 | Samsung Electronics Co., Ltd. | Apparatus for manufacturing semiconductor |

| US11637211B2 (en) | 2021-02-02 | 2023-04-25 | Rockwell Collins, Inc. | Optically clear thermal spreader for status indication within an electronics package |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007201259A (ja) | 2007-08-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4758780B2 (ja) | 半導体装置の製造方法及び半導体装置の実装装置 | |

| JP6545889B1 (ja) | Ledディスプレイパネル製造のためのマイクロledチップアレイ方法及びこれに用いられるマルチチップキャリア | |

| JP5927179B2 (ja) | 積層された蛍光体層を有するledのウエハー | |

| KR101449834B1 (ko) | 다이 본딩 장치 및 다이 픽업 장치 및 다이 픽업 방법 | |

| WO2002007132A1 (fr) | Unite d'affichage d'images et procede de fabrication correspondant | |

| US20070176197A1 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| KR101568757B1 (ko) | 리드 프레임, 발광 소자 패키지, 백라이트 유닛, 조명 장치 및 발광 소자 패키지의 제조 방법 | |

| CN112768370B (zh) | 微元件的转移方法及转移装置 | |

| JP2014179520A (ja) | 発光装置の封止部材の取り外し方法 | |

| JP2019153718A (ja) | デバイスの移設方法 | |

| JP2008153324A (ja) | マイクロボール搭載方法および搭載装置 | |

| JP2015076410A (ja) | ボンディング方法及びダイボンダ | |

| KR20150110910A (ko) | 발광 소자 패키지, 백라이트 유닛, 조명 장치 및 발광 소자 패키지의 제조 방법 | |

| KR101606818B1 (ko) | 발광 소자 패키지, 백라이트 유닛, 조명 장치 및 발광 소자 패키지의 제조 방법 | |

| JP2002280613A (ja) | 照明装置の製造方法及び部材 | |

| CN111987193B (zh) | 微发光二极管转移装置及其制作方法 | |

| JP2008109119A (ja) | ピックアップ装置及びピックアップ方法 | |

| KR20150061521A (ko) | 발광 소자 패키지, 백라이트 유닛, 조명 장치, 발광 소자 패키지의 제작 방법 및 몰딩 지그 | |

| KR102176615B1 (ko) | 디스플레이 소자의 트랜스퍼 장치 및 트랜스퍼 방법 | |

| JP4848606B2 (ja) | 素子の位置決め方法、素子の取り出し方法、素子の転写方法、素子の配列方法及び画像表示装置の製造方法 | |

| KR101524048B1 (ko) | 발광 소자 패키지, 백라이트 유닛, 조명 장치 및 발광 소자 패키지의 제조 방법 | |

| JP2002231877A (ja) | 素子配列型装置、素子配列型装置の製造方法、及び画像表示装置 | |

| JP2003031847A (ja) | 素子の取り出し方法、及びこれを用いた素子の転写方法、素子の配列方法、画像表示装置の製造方法 | |

| WO2022244804A1 (ja) | 基板処理装置および基板処理方法 | |

| KR101567929B1 (ko) | 발광 소자 패키지, 백라이트 유닛, 조명 장치 및 발광 소자 패키지의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081020 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081020 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090316 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101109 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110105 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110531 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110603 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4758780 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140610 Year of fee payment: 3 |