JP4688703B2 - Usbトランシーバ - Google Patents

Usbトランシーバ Download PDFInfo

- Publication number

- JP4688703B2 JP4688703B2 JP2006066841A JP2006066841A JP4688703B2 JP 4688703 B2 JP4688703 B2 JP 4688703B2 JP 2006066841 A JP2006066841 A JP 2006066841A JP 2006066841 A JP2006066841 A JP 2006066841A JP 4688703 B2 JP4688703 B2 JP 4688703B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- signal

- output signal

- output

- input

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Dc Digital Transmission (AREA)

- Logic Circuits (AREA)

Description

このようなUSBは、2本の信号線を用いてシリアルデータを伝送する方式であり、特に、シリアルデータの受信回路においては、2本の信号線が、差動コンパレータ回路とシングルエンデッドレシーバ回路に接続される。差動コンパレータ回路は、2本の信号線の差分信号を出力し、シングルエンデッドレシーバ回路は、各信号線を波形整形し、コントローラ側に出力する。

図4は図3を用いて説明した従来のUSBトランシーバの各端子における電圧状態を示す波形図である。ここで、PACKET期間は受信入力端子33a、33bのそれぞれからUSBデータが互いに逆位相で入力される期間であり、EOP期間は受信入力端子33a、33bのそれぞれからUSBデータが互いに同一位相で入力される期間である。また、T1、T2、T3、T4は出力波形の時間軸上の各タイミングにおける遅延時間である。

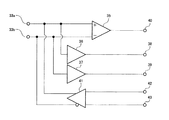

図1は本実施の形態のUSBトランシーバの構成を示す回路ブロック図である。図1において、3a、3bはUSBデータの受信入力端子、5は差動コンパレータ回路、6はシングルエンデッドレシーバ回路、7はシングルエンデッドレシーバインバータ回路、8はシングルエンデッドレシーバ回路6の出力信号、9はシングルエンデッドレシーバインバータ回路7の出力信号、10、13は立ち上がり遅延回路、11、12は立ち下がり遅延回路、14はOR回路、15、16はAND回路、17はNOR回路、18、19、20は出力端子、21はドライバ回路、22、23はコントローラ側から制御される入力端子である。ここで、立ち上がり遅延回路10、13と立ち下がり遅延回路11、12で遅延回路部を構成し、OR回路14とAND回路15、16とNOR回路17で論理回路部を構成する。

図2は本実施の形態のUSBトランシーバにおける動作中の電圧状態を示す波形図である。図2において、PACKET期間は受信入力端子3a、3bのそれぞれからUSBデータが互いに逆位相で入力される期間であり、EOP期間は受信入力端子3a、3bのそれぞれからUSBデータが互いに同一位相で入力される期間である。また、T1、T2、T3、T4は出力波形の時間軸上の各タイミングにおける遅延時間である。また、PACKET期間において、受信入力端子3a、3bには、それぞれスキューのない入力波形201、202の信号が入力されているものとする。

受信入力端子3aから入力された波形201の信号は、シングルエンデッドレシーバ回路6に入力されると同時に、差動コンパレータ回路5の(+)端子にも入力される。また、同様に受信入力端子3bから入力された波形202の信号は、シングルエンデッドレシーバインバータ回路7に入力されると同時に、差動コンパレータ回路5の(−)端子にも入力される。

5、35 差動コンパレータ回路

6、36、37 シングルエンデッドレシーバ回路

7 シングルエンデッドレシーバインバータ回路

8 シングルエンデッドレシーバ回路の出力信号

9 シングルエンデッドレシーバインバータ回路の出力信号

10、13 立ち上がり遅延回路

11、12 立ち下がり遅延回路

14 OR回路

15、16 AND回路

17 NOR回路

18、19、20、38、39、40 出力端子

21、41 ドライバ回路

22、23、42、43 入力端子

PACKET 逆位相入力期間

EOP 同一位相入力期間

T1、T2、T3、T4 遅延時間

Claims (2)

- 第1の信号線と第2の信号線のシリアルデータを送受信するUSBトランシーバであって、

前記第1の信号線と前記第2の信号線にデータ信号をドライブするドライバ回路と、

前記第1の信号線と前記第2の信号線のデータ信号を差動入力する差動コンパレータ回路と、

前記第1の信号線のデータ信号を入力する第1のシングルエンデッドレシーバ回路と、

前記第2の信号線のデータ信号を入力する第2のシングルエンデッドレシーバ回路と、

前記第1のシングルエンデッドレシーバ回路の出力信号を遅延させる第1の遅延回路部と、

前記第2のシングルエンデッドレシーバ回路の出力信号を遅延させる第2の遅延回路部と、

前記差動コンパレータ回路の出力信号と前記第1の遅延回路部の出力信号と前記第2の遅延回路部の出力信号とが入力される論理回路部とを具備し、

前記論理回路部は、

前記第1の信号線と前記第2の信号線のデータ信号が互いに逆位相でレベル変化した場合において、

前記第1の遅延回路部の出力信号を、前記差動コンパレータ回路の出力信号に基いて、前記第1のシングルエンデッドレシーバ回路の出力信号のレベル変化を前記差動コンパレータ回路の出力信号のレベル変化に同期させた信号に変換して、

前記第2の遅延回路部の出力信号を、前記差動コンパレータ回路の出力信号に基いて、前記第2のシングルエンデッドレシーバ回路の出力信号のレベル変化を前記差動コンパレータ回路の出力信号のレベル変化に同期させた信号に変換するよう構成した

ことを特徴とするUSBトランシーバ。 - 請求項1記載のUSBトランシーバであって、

前記第1の遅延回路部は、

前記第1のシングルエンデッドレシーバ回路の出力信号の立ち上がり時のみ遅延させる第1の立ち上がり遅延回路と、立ち下がり時のみ遅延させる第1の立ち下がり遅延回路とを具備し、

前記第2の遅延回路部は、

前記第2のシングルエンデッドレシーバ回路の出力信号の立ち上がり時のみ遅延させる第2の立ち上がり遅延回路と、立ち下がり時のみ遅延させる第2の立ち下がり遅延回路とを具備し、

前記論理回路部は、

前記第1の立ち下がり遅延回路の出力信号と前記差動コンパレータ回路の出力信号とが入力される第1のAND回路と、

前記第1の立ち上がり遅延回路の出力信号と前記第1のAND回路の出力信号とが入力されるOR回路と、

前記第2の立ち下がり遅延回路の出力信号と前記差動コンパレータ回路の出力信号とが入力される第2のAND回路と、

前記第2の立ち上がり遅延回路の出力信号と前記第2のAND回路の出力信号とが入力されるNOR回路とを具備した

ことを特徴とするUSBトランシーバ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006066841A JP4688703B2 (ja) | 2006-03-13 | 2006-03-13 | Usbトランシーバ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006066841A JP4688703B2 (ja) | 2006-03-13 | 2006-03-13 | Usbトランシーバ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007241911A JP2007241911A (ja) | 2007-09-20 |

| JP4688703B2 true JP4688703B2 (ja) | 2011-05-25 |

Family

ID=38587350

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006066841A Expired - Fee Related JP4688703B2 (ja) | 2006-03-13 | 2006-03-13 | Usbトランシーバ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4688703B2 (ja) |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001148719A (ja) * | 1999-11-19 | 2001-05-29 | Teac Corp | デ−タ受信装置 |

-

2006

- 2006-03-13 JP JP2006066841A patent/JP4688703B2/ja not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001148719A (ja) * | 1999-11-19 | 2001-05-29 | Teac Corp | デ−タ受信装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007241911A (ja) | 2007-09-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4960833B2 (ja) | シングルエンド伝送及び差動伝送の切替えが可能なインタフェース回路 | |

| US9001950B2 (en) | Information processing apparatus, serial communication system, method of initialization of communication therefor, and serial communication apparatus | |

| US7495491B2 (en) | Inverter based duty cycle correction apparatuses and systems | |

| US10333690B1 (en) | Calibration pattern and duty-cycle distortion correction for clock data recovery in a multi-wire, multi-phase interface | |

| US7868662B2 (en) | Spike noise eliminating circuit, digital system using the same, and IIC bus | |

| US11133802B2 (en) | Repeater for an open-drain communication system using a current detector and a control logic circuit | |

| US7876857B2 (en) | Data receiving apparatus | |

| US9342097B2 (en) | Microcontroller and method of controlling the same | |

| JP4688703B2 (ja) | Usbトランシーバ | |

| JP2000174826A (ja) | シングルエンドゼロレシーバ回路 | |

| US8786320B2 (en) | Signal input circuit and semiconductor device having the same | |

| JPWO2007049455A1 (ja) | 半導体メモリカード | |

| US20200162064A1 (en) | Debounce circuit using d flip-flops | |

| US20220400035A1 (en) | Latch circuit and equalizer including the same | |

| JP2005234976A (ja) | 記憶装置 | |

| JP5296620B2 (ja) | 信号中継回路 | |

| JP6569682B2 (ja) | 送信装置および通信システム | |

| US20240184730A1 (en) | Eusb repeater for passing repeating mode packets between a differential bus and a single-ended bus | |

| US7598789B2 (en) | Signal transferring system with unequal lengths of connecting paths and method thereof | |

| JP2001177689A (ja) | 画像処理装置 | |

| JP2011155598A (ja) | 伝送回路 | |

| JP2016224588A (ja) | 制御装置及び制御方法 | |

| JP4952167B2 (ja) | データ伝送装置 | |

| JP2009110317A (ja) | シングルエンド伝送及び差動伝送の切替えが可能なインタフェース回路、メモリコントローラ、不揮発性記憶装置、ホスト装置及び不揮発性メモリシステム | |

| CN110932702A (zh) | 集成电路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080430 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080925 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100921 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101122 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110118 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110215 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140225 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |