JP4667051B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4667051B2 JP4667051B2 JP2005019248A JP2005019248A JP4667051B2 JP 4667051 B2 JP4667051 B2 JP 4667051B2 JP 2005019248 A JP2005019248 A JP 2005019248A JP 2005019248 A JP2005019248 A JP 2005019248A JP 4667051 B2 JP4667051 B2 JP 4667051B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- mask pattern

- insulating film

- organic film

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 226

- 238000000034 method Methods 0.000 title claims description 198

- 238000004519 manufacturing process Methods 0.000 title claims description 54

- 239000000758 substrate Substances 0.000 claims description 109

- 239000004020 conductor Substances 0.000 claims description 84

- 239000000463 material Substances 0.000 claims description 82

- 239000007788 liquid Substances 0.000 claims description 56

- 229920001721 polyimide Polymers 0.000 claims description 36

- 239000004642 Polyimide Substances 0.000 claims description 34

- 239000004372 Polyvinyl alcohol Substances 0.000 claims description 33

- 229920002451 polyvinyl alcohol Polymers 0.000 claims description 33

- 229910052710 silicon Inorganic materials 0.000 claims description 31

- 239000010703 silicon Substances 0.000 claims description 30

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 claims description 26

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 claims description 25

- 238000011282 treatment Methods 0.000 claims description 20

- 239000006087 Silane Coupling Agent Substances 0.000 claims description 19

- 229910052731 fluorine Inorganic materials 0.000 claims description 19

- 239000011737 fluorine Substances 0.000 claims description 19

- 229910052760 oxygen Inorganic materials 0.000 claims description 18

- 238000009832 plasma treatment Methods 0.000 claims description 18

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 17

- 239000001301 oxygen Substances 0.000 claims description 17

- 239000012298 atmosphere Substances 0.000 claims description 15

- 238000000059 patterning Methods 0.000 claims description 12

- 239000001257 hydrogen Substances 0.000 claims description 9

- 229910052739 hydrogen Inorganic materials 0.000 claims description 9

- 125000000217 alkyl group Chemical group 0.000 claims description 8

- 125000001424 substituent group Chemical group 0.000 claims description 7

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 4

- 150000004945 aromatic hydrocarbons Chemical class 0.000 claims description 4

- 239000004925 Acrylic resin Substances 0.000 claims description 2

- 229920000178 Acrylic resin Polymers 0.000 claims description 2

- 229920006122 polyamide resin Polymers 0.000 claims description 2

- 239000009719 polyimide resin Substances 0.000 claims description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 claims 2

- 239000010408 film Substances 0.000 description 492

- 239000010410 layer Substances 0.000 description 141

- 239000000203 mixture Substances 0.000 description 91

- 239000007789 gas Substances 0.000 description 74

- 239000004973 liquid crystal related substance Substances 0.000 description 57

- 238000005401 electroluminescence Methods 0.000 description 53

- 238000005530 etching Methods 0.000 description 47

- 229920005989 resin Polymers 0.000 description 45

- 239000011347 resin Substances 0.000 description 45

- 239000010409 thin film Substances 0.000 description 37

- 229910052814 silicon oxide Inorganic materials 0.000 description 35

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 34

- 230000008569 process Effects 0.000 description 33

- 239000011229 interlayer Substances 0.000 description 32

- 229910052581 Si3N4 Inorganic materials 0.000 description 31

- 238000002347 injection Methods 0.000 description 31

- 239000007924 injection Substances 0.000 description 31

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 31

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 30

- 239000012535 impurity Substances 0.000 description 30

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 29

- 239000002245 particle Substances 0.000 description 29

- 239000002904 solvent Substances 0.000 description 28

- 238000007599 discharging Methods 0.000 description 23

- 238000004380 ashing Methods 0.000 description 20

- 230000015572 biosynthetic process Effects 0.000 description 20

- 239000010949 copper Substances 0.000 description 20

- 229910052751 metal Inorganic materials 0.000 description 20

- 239000002184 metal Substances 0.000 description 20

- 229910052709 silver Inorganic materials 0.000 description 19

- 238000002161 passivation Methods 0.000 description 17

- 239000004332 silver Substances 0.000 description 17

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 16

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 16

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 16

- 239000010936 titanium Substances 0.000 description 16

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 15

- 230000006870 function Effects 0.000 description 15

- 239000010931 gold Substances 0.000 description 15

- 239000011159 matrix material Substances 0.000 description 15

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 15

- 230000002940 repellent Effects 0.000 description 15

- 239000005871 repellent Substances 0.000 description 15

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 15

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 14

- 229910052782 aluminium Inorganic materials 0.000 description 14

- 229910052802 copper Inorganic materials 0.000 description 14

- 238000010586 diagram Methods 0.000 description 14

- 238000001035 drying Methods 0.000 description 14

- 150000002894 organic compounds Chemical class 0.000 description 14

- 230000002829 reductive effect Effects 0.000 description 14

- 239000011787 zinc oxide Substances 0.000 description 14

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 13

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 13

- 229910052737 gold Inorganic materials 0.000 description 13

- 238000010438 heat treatment Methods 0.000 description 13

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 13

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 13

- 229910052799 carbon Inorganic materials 0.000 description 12

- 238000010304 firing Methods 0.000 description 12

- 239000011521 glass Substances 0.000 description 12

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 12

- 238000012545 processing Methods 0.000 description 12

- 230000001681 protective effect Effects 0.000 description 12

- 229910021332 silicide Inorganic materials 0.000 description 12

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 12

- 239000000243 solution Substances 0.000 description 12

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 11

- 229910052796 boron Inorganic materials 0.000 description 11

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 10

- 239000011810 insulating material Substances 0.000 description 10

- 239000011777 magnesium Substances 0.000 description 10

- 229910052749 magnesium Inorganic materials 0.000 description 10

- 238000005192 partition Methods 0.000 description 10

- 239000002356 single layer Substances 0.000 description 10

- 239000000126 substance Substances 0.000 description 10

- 238000011161 development Methods 0.000 description 9

- 230000018109 developmental process Effects 0.000 description 9

- 229910052738 indium Inorganic materials 0.000 description 9

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 9

- 239000012212 insulator Substances 0.000 description 9

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 8

- 239000000460 chlorine Substances 0.000 description 8

- 150000002484 inorganic compounds Chemical class 0.000 description 8

- 229910010272 inorganic material Inorganic materials 0.000 description 8

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 8

- 239000003550 marker Substances 0.000 description 8

- 229910052757 nitrogen Inorganic materials 0.000 description 8

- 230000005236 sound signal Effects 0.000 description 8

- 238000004528 spin coating Methods 0.000 description 8

- 229910052719 titanium Inorganic materials 0.000 description 8

- 238000005406 washing Methods 0.000 description 8

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 7

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 7

- 229910021417 amorphous silicon Inorganic materials 0.000 description 7

- 230000004888 barrier function Effects 0.000 description 7

- 239000011248 coating agent Substances 0.000 description 7

- 238000000576 coating method Methods 0.000 description 7

- -1 naphthoquinone diazide compound Chemical class 0.000 description 7

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 6

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 6

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 6

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 6

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 6

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 6

- 239000004952 Polyamide Substances 0.000 description 6

- 229910003902 SiCl 4 Inorganic materials 0.000 description 6

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 6

- 239000011651 chromium Substances 0.000 description 6

- 238000000354 decomposition reaction Methods 0.000 description 6

- 230000005669 field effect Effects 0.000 description 6

- 238000013532 laser treatment Methods 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 229920002647 polyamide Polymers 0.000 description 6

- 229910052718 tin Inorganic materials 0.000 description 6

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 5

- 229910052786 argon Inorganic materials 0.000 description 5

- 235000019441 ethanol Nutrition 0.000 description 5

- 229920006015 heat resistant resin Polymers 0.000 description 5

- 229910052734 helium Inorganic materials 0.000 description 5

- 150000002431 hydrogen Chemical class 0.000 description 5

- 238000003384 imaging method Methods 0.000 description 5

- 239000002105 nanoparticle Substances 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 238000001020 plasma etching Methods 0.000 description 5

- 229910052700 potassium Inorganic materials 0.000 description 5

- 230000009467 reduction Effects 0.000 description 5

- 230000002441 reversible effect Effects 0.000 description 5

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 5

- 239000007787 solid Substances 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- WUPHOULIZUERAE-UHFFFAOYSA-N 3-(oxolan-2-yl)propanoic acid Chemical compound OC(=O)CCC1CCCO1 WUPHOULIZUERAE-UHFFFAOYSA-N 0.000 description 4

- YEJRWHAVMIAJKC-UHFFFAOYSA-N 4-Butyrolactone Chemical compound O=C1CCCO1 YEJRWHAVMIAJKC-UHFFFAOYSA-N 0.000 description 4

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 4

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- UQSXHKLRYXJYBZ-UHFFFAOYSA-N Iron oxide Chemical compound [Fe]=O UQSXHKLRYXJYBZ-UHFFFAOYSA-N 0.000 description 4

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 4

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 4

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 4

- 229910052785 arsenic Inorganic materials 0.000 description 4

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 4

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 4

- 239000011230 binding agent Substances 0.000 description 4

- 229910052980 cadmium sulfide Inorganic materials 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 4

- 238000009792 diffusion process Methods 0.000 description 4

- 238000007865 diluting Methods 0.000 description 4

- 239000002270 dispersing agent Substances 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- 230000009977 dual effect Effects 0.000 description 4

- 229910052732 germanium Inorganic materials 0.000 description 4

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 4

- 230000005525 hole transport Effects 0.000 description 4

- 229910052744 lithium Inorganic materials 0.000 description 4

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 4

- 239000011368 organic material Substances 0.000 description 4

- 239000003960 organic solvent Substances 0.000 description 4

- 229910052698 phosphorus Inorganic materials 0.000 description 4

- 239000011574 phosphorus Substances 0.000 description 4

- 229920000642 polymer Polymers 0.000 description 4

- 239000011591 potassium Substances 0.000 description 4

- 239000010948 rhodium Substances 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 125000006850 spacer group Chemical group 0.000 description 4

- 238000004544 sputter deposition Methods 0.000 description 4

- HYZJCKYKOHLVJF-UHFFFAOYSA-N 1H-benzimidazole Chemical compound C1=CC=C2NC=NC2=C1 HYZJCKYKOHLVJF-UHFFFAOYSA-N 0.000 description 3

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 3

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 3

- 230000003321 amplification Effects 0.000 description 3

- 229910052791 calcium Inorganic materials 0.000 description 3

- 239000011575 calcium Substances 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 229920000840 ethylene tetrafluoroethylene copolymer Polymers 0.000 description 3

- 238000001704 evaporation Methods 0.000 description 3

- 239000010419 fine particle Substances 0.000 description 3

- 229910052733 gallium Inorganic materials 0.000 description 3

- 238000009499 grossing Methods 0.000 description 3

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 3

- 238000003199 nucleic acid amplification method Methods 0.000 description 3

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- 229910000073 phosphorus hydride Inorganic materials 0.000 description 3

- 230000001699 photocatalysis Effects 0.000 description 3

- 239000011295 pitch Substances 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 229910052706 scandium Inorganic materials 0.000 description 3

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- 229910052708 sodium Inorganic materials 0.000 description 3

- 239000011734 sodium Substances 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- RFFLAFLAYFXFSW-UHFFFAOYSA-N 1,2-dichlorobenzene Chemical compound ClC1=CC=CC=C1Cl RFFLAFLAYFXFSW-UHFFFAOYSA-N 0.000 description 2

- HZAXFHJVJLSVMW-UHFFFAOYSA-N 2-Aminoethan-1-ol Chemical compound NCCO HZAXFHJVJLSVMW-UHFFFAOYSA-N 0.000 description 2

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 2

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 2

- 229920001780 ECTFE Polymers 0.000 description 2

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 2

- 229910000799 K alloy Inorganic materials 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- 239000004988 Nematic liquid crystal Substances 0.000 description 2

- 239000002033 PVDF binder Substances 0.000 description 2

- 239000004813 Perfluoroalkoxy alkane Substances 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 2

- 229910018557 Si O Inorganic materials 0.000 description 2

- 125000003668 acetyloxy group Chemical group [H]C([H])([H])C(=O)O[*] 0.000 description 2

- 150000001298 alcohols Chemical class 0.000 description 2

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 2

- 125000003277 amino group Chemical group 0.000 description 2

- 229910052787 antimony Inorganic materials 0.000 description 2

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 2

- QQHJESKHUUVSIC-UHFFFAOYSA-N antimony lead Chemical compound [Sb].[Pb] QQHJESKHUUVSIC-UHFFFAOYSA-N 0.000 description 2

- 125000004429 atom Chemical group 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- 230000006399 behavior Effects 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- QDWJUBJKEHXSMT-UHFFFAOYSA-N boranylidynenickel Chemical compound [Ni]#B QDWJUBJKEHXSMT-UHFFFAOYSA-N 0.000 description 2

- 229910052793 cadmium Inorganic materials 0.000 description 2

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 2

- AQCDIIAORKRFCD-UHFFFAOYSA-N cadmium selenide Chemical compound [Cd]=[Se] AQCDIIAORKRFCD-UHFFFAOYSA-N 0.000 description 2

- 239000012159 carrier gas Substances 0.000 description 2

- 239000003054 catalyst Substances 0.000 description 2

- 239000003795 chemical substances by application Substances 0.000 description 2

- 229910052801 chlorine Inorganic materials 0.000 description 2

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 2

- 229920006026 co-polymeric resin Polymers 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 238000009833 condensation Methods 0.000 description 2

- 230000005494 condensation Effects 0.000 description 2

- 229920001577 copolymer Polymers 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 229910021419 crystalline silicon Inorganic materials 0.000 description 2

- 238000002425 crystallisation Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000010790 dilution Methods 0.000 description 2

- 239000012895 dilution Substances 0.000 description 2

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 125000003700 epoxy group Chemical group 0.000 description 2

- 150000002148 esters Chemical class 0.000 description 2

- 125000001301 ethoxy group Chemical group [H]C([H])([H])C([H])([H])O* 0.000 description 2

- 229910021397 glassy carbon Inorganic materials 0.000 description 2

- 229910002804 graphite Inorganic materials 0.000 description 2

- 239000010439 graphite Substances 0.000 description 2

- 230000005283 ground state Effects 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002367 halogens Chemical group 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- FUZZWVXGSFPDMH-UHFFFAOYSA-M hexanoate Chemical compound CCCCCC([O-])=O FUZZWVXGSFPDMH-UHFFFAOYSA-M 0.000 description 2

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 229910052741 iridium Inorganic materials 0.000 description 2

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 2

- 229910052742 iron Inorganic materials 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 2

- 238000005499 laser crystallization Methods 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 2

- 230000015654 memory Effects 0.000 description 2

- 125000000956 methoxy group Chemical group [H]C([H])([H])O* 0.000 description 2

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 2

- 239000011259 mixed solution Substances 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- 229910052754 neon Inorganic materials 0.000 description 2

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- 229910000484 niobium oxide Inorganic materials 0.000 description 2

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 2

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 230000036961 partial effect Effects 0.000 description 2

- 229920011301 perfluoro alkoxyl alkane Polymers 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 239000003504 photosensitizing agent Substances 0.000 description 2

- 238000002294 plasma sputter deposition Methods 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229920002493 poly(chlorotrifluoroethylene) Polymers 0.000 description 2

- 239000005023 polychlorotrifluoroethylene (PCTFE) polymer Substances 0.000 description 2

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 2

- 239000004810 polytetrafluoroethylene Substances 0.000 description 2

- 229920002689 polyvinyl acetate Polymers 0.000 description 2

- 239000011118 polyvinyl acetate Substances 0.000 description 2

- 229920002620 polyvinyl fluoride Polymers 0.000 description 2

- 229920002981 polyvinylidene fluoride Polymers 0.000 description 2

- BITYAPCSNKJESK-UHFFFAOYSA-N potassiosodium Chemical compound [Na].[K] BITYAPCSNKJESK-UHFFFAOYSA-N 0.000 description 2

- 238000002203 pretreatment Methods 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 229910052702 rhenium Inorganic materials 0.000 description 2

- WUAPFZMCVAUBPE-UHFFFAOYSA-N rhenium atom Chemical compound [Re] WUAPFZMCVAUBPE-UHFFFAOYSA-N 0.000 description 2

- 229910052703 rhodium Inorganic materials 0.000 description 2

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 2

- 150000003377 silicon compounds Chemical group 0.000 description 2

- 239000007921 spray Substances 0.000 description 2

- 239000010935 stainless steel Substances 0.000 description 2

- 229910001220 stainless steel Inorganic materials 0.000 description 2

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 2

- 238000004381 surface treatment Methods 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 2

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 2

- 229910052714 tellurium Inorganic materials 0.000 description 2

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 2

- BGHCVCJVXZWKCC-UHFFFAOYSA-N tetradecane Chemical compound CCCCCCCCCCCCCC BGHCVCJVXZWKCC-UHFFFAOYSA-N 0.000 description 2

- BFKJFAAPBSQJPD-UHFFFAOYSA-N tetrafluoroethene Chemical group FC(F)=C(F)F BFKJFAAPBSQJPD-UHFFFAOYSA-N 0.000 description 2

- PPMWWXLUCOODDK-UHFFFAOYSA-N tetrafluorogermane Chemical compound F[Ge](F)(F)F PPMWWXLUCOODDK-UHFFFAOYSA-N 0.000 description 2

- 229920001187 thermosetting polymer Polymers 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- FZMJEGJVKFTGMU-UHFFFAOYSA-N triethoxy(octadecyl)silane Chemical compound CCCCCCCCCCCCCCCCCC[Si](OCC)(OCC)OCC FZMJEGJVKFTGMU-UHFFFAOYSA-N 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- ZNOKGRXACCSDPY-UHFFFAOYSA-N tungsten trioxide Chemical compound O=[W](=O)=O ZNOKGRXACCSDPY-UHFFFAOYSA-N 0.000 description 2

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 2

- 239000011701 zinc Substances 0.000 description 2

- 229910001928 zirconium oxide Inorganic materials 0.000 description 2

- PEVRKKOYEFPFMN-UHFFFAOYSA-N 1,1,2,3,3,3-hexafluoroprop-1-ene;1,1,2,2-tetrafluoroethene Chemical group FC(F)=C(F)F.FC(F)=C(F)C(F)(F)F PEVRKKOYEFPFMN-UHFFFAOYSA-N 0.000 description 1

- BQCIDUSAKPWEOX-UHFFFAOYSA-N 1,1-Difluoroethene Chemical compound FC(F)=C BQCIDUSAKPWEOX-UHFFFAOYSA-N 0.000 description 1

- QZJJMHGIQXXGSA-UHFFFAOYSA-N 1,2-dichloro-1,1,2-trifluoroethane;ethene Chemical group C=C.FC(Cl)C(F)(F)Cl QZJJMHGIQXXGSA-UHFFFAOYSA-N 0.000 description 1

- POAOYUHQDCAZBD-UHFFFAOYSA-N 2-butoxyethanol Chemical compound CCCCOCCO POAOYUHQDCAZBD-UHFFFAOYSA-N 0.000 description 1

- ZNQVEEAIQZEUHB-UHFFFAOYSA-N 2-ethoxyethanol Chemical compound CCOCCO ZNQVEEAIQZEUHB-UHFFFAOYSA-N 0.000 description 1

- DDFHBQSCUXNBSA-UHFFFAOYSA-N 5-(5-carboxythiophen-2-yl)thiophene-2-carboxylic acid Chemical compound S1C(C(=O)O)=CC=C1C1=CC=C(C(O)=O)S1 DDFHBQSCUXNBSA-UHFFFAOYSA-N 0.000 description 1

- 229910017073 AlLi Inorganic materials 0.000 description 1

- LSNNMFCWUKXFEE-UHFFFAOYSA-M Bisulfite Chemical compound OS([O-])=O LSNNMFCWUKXFEE-UHFFFAOYSA-M 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- KRHYYFGTRYWZRS-UHFFFAOYSA-M Fluoride anion Chemical compound [F-] KRHYYFGTRYWZRS-UHFFFAOYSA-M 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- UFWIBTONFRDIAS-UHFFFAOYSA-N Naphthalene Chemical compound C1=CC=CC2=CC=CC=C21 UFWIBTONFRDIAS-UHFFFAOYSA-N 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- ISWSIDIOOBJBQZ-UHFFFAOYSA-N Phenol Chemical compound OC1=CC=CC=C1 ISWSIDIOOBJBQZ-UHFFFAOYSA-N 0.000 description 1

- QYKIQEUNHZKYBP-UHFFFAOYSA-N Vinyl ether Chemical compound C=COC=C QYKIQEUNHZKYBP-UHFFFAOYSA-N 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- FBAMNQFCCMSBRO-UHFFFAOYSA-N [Sn+2]=O.[In+3].[O-2].[Al+3].[O-2].[O-2].[O-2] Chemical compound [Sn+2]=O.[In+3].[O-2].[Al+3].[O-2].[O-2].[O-2] FBAMNQFCCMSBRO-UHFFFAOYSA-N 0.000 description 1

- 238000005299 abrasion Methods 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 125000003545 alkoxy group Chemical group 0.000 description 1

- 150000004996 alkyl benzenes Chemical class 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 125000003118 aryl group Chemical group 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- 239000002981 blocking agent Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- UUAGAQFQZIEFAH-UHFFFAOYSA-N chlorotrifluoroethylene Chemical group FC(F)=C(F)Cl UUAGAQFQZIEFAH-UHFFFAOYSA-N 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 230000008602 contraction Effects 0.000 description 1

- 239000007822 coupling agent Substances 0.000 description 1

- BAAAEEDPKUHLID-UHFFFAOYSA-N decyl(triethoxy)silane Chemical compound CCCCCCCCCC[Si](OCC)(OCC)OCC BAAAEEDPKUHLID-UHFFFAOYSA-N 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- MTHSVFCYNBDYFN-UHFFFAOYSA-N diethylene glycol Chemical compound OCCOCCO MTHSVFCYNBDYFN-UHFFFAOYSA-N 0.000 description 1

- OLLFKUHHDPMQFR-UHFFFAOYSA-N dihydroxy(diphenyl)silane Chemical compound C=1C=CC=CC=1[Si](O)(O)C1=CC=CC=C1 OLLFKUHHDPMQFR-UHFFFAOYSA-N 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000005538 encapsulation Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 229920001038 ethylene copolymer Polymers 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 1

- 210000003754 fetus Anatomy 0.000 description 1

- 125000001153 fluoro group Chemical group F* 0.000 description 1

- XUCNUKMRBVNAPB-UHFFFAOYSA-N fluoroethene Chemical compound FC=C XUCNUKMRBVNAPB-UHFFFAOYSA-N 0.000 description 1

- NBVXSUQYWXRMNV-UHFFFAOYSA-N fluoromethane Chemical group FC NBVXSUQYWXRMNV-UHFFFAOYSA-N 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 239000005001 laminate film Substances 0.000 description 1

- 238000005461 lubrication Methods 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- QPJSUIGXIBEQAC-UHFFFAOYSA-N n-(2,4-dichloro-5-propan-2-yloxyphenyl)acetamide Chemical compound CC(C)OC1=CC(NC(C)=O)=C(Cl)C=C1Cl QPJSUIGXIBEQAC-UHFFFAOYSA-N 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229920003986 novolac Polymers 0.000 description 1

- MSRJTTSHWYDFIU-UHFFFAOYSA-N octyltriethoxysilane Chemical compound CCCCCCCC[Si](OCC)(OCC)OCC MSRJTTSHWYDFIU-UHFFFAOYSA-N 0.000 description 1

- 229960003493 octyltriethoxysilane Drugs 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 239000012188 paraffin wax Substances 0.000 description 1

- 125000005010 perfluoroalkyl group Chemical group 0.000 description 1

- 238000007781 pre-processing Methods 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 150000003254 radicals Chemical class 0.000 description 1

- 239000002994 raw material Substances 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

- 238000005070 sampling Methods 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 238000005477 sputtering target Methods 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- DENFJSAFJTVPJR-UHFFFAOYSA-N triethoxy(ethyl)silane Chemical compound CCO[Si](CC)(OCC)OCC DENFJSAFJTVPJR-UHFFFAOYSA-N 0.000 description 1

- NBXZNTLFQLUFES-UHFFFAOYSA-N triethoxy(propyl)silane Chemical compound CCC[Si](OCC)(OCC)OCC NBXZNTLFQLUFES-UHFFFAOYSA-N 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical compound [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

本実施形態では、主に図1を参照して、本発明に係るコンタクトホールの形成方法について説明する。

本実施形態では、図2、図3を参照して、本発明に係るボトムゲート型TFTの作製方法のうち、特に、チャネル保護型TFTの作製方法について説明する。

本実施形態では、図4、図5を参照して、本発明に係るボトムゲート型TFTの作製方法のうち、特に、チャネルエッチ型TFTの作製方法について説明する。

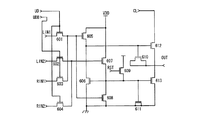

本実施形態では、図6、図7を参照して、本発明に係るトップゲート型TFTの作製方法について説明する。

11 導電膜又は半導体膜

12 有機膜

13 マスクパターン

14 島状有機膜

15 絶縁膜

16 コンタクトホール

17 導電体

100 基板

101 ノズル

102 ゲート電極

103 酸化チタン膜

104 ゲート絶縁膜

104a SiNx膜

104b SiOx膜

104c SiNx膜

105 半導体膜

106 絶縁膜

107 マスクパターン

108 チャネル保護膜

109 n型半導体膜

110 第2のマスクパターン

111 半導体膜

112a ソース領域

112b ドレイン領域

113 有機膜

114 第3のマスクパターン

115 島状有機膜

116 層間絶縁膜

117 コンタクトホール

118a ソース配線

118b ドレイン配線

119 チャネル領域

Claims (10)

- 基板の上方に半導体層又は導電層を形成し、

前記半導体層又は導電層上に有機膜を形成し、

前記有機膜上であって、かつコンタクトホールを形成すべき箇所にマスクパターンを選択的に形成し、

前記マスクパターンをマスクとして、前記有機膜を島状にパターン形成した後に、前記マスクパターンを除去し、

前記島状の有機膜の周囲に絶縁膜を形成した後に、前記島状の有機膜を除去することによりコンタクトホールを形成し、

前記コンタクトホールにおいて前記半導体層又は導電層と電気的に接続される導電体を形成する半導体装置の作製方法であって、

前記有機膜として、前記絶縁膜に対して撥液性を有する膜を形成することを特徴とする半導体装置の作製方法。 - 基板の上方にゲート電極を形成し、

前記ゲート電極の上方に、ゲート絶縁膜を介して半導体層を形成し、

前記半導体層の上方に有機膜を形成し、

前記有機膜上であって、かつコンタクトホールを形成すべき箇所にマスクパターンを選択的に形成し、

前記マスクパターンをマスクとして、前記有機膜を島状にパターン形成した後に、前記マスクパターンを除去し、

前記島状の有機膜の周囲に絶縁膜を形成した後に、前記島状の有機膜を除去することによりコンタクトホールを形成し、

前記コンタクトホールにおいて前記半導体層と電気的に接続される導電体を形成する半導体装置の作製方法であって、

前記有機膜として、前記絶縁膜に対して撥液性を有する膜を形成することを特徴とする半導体装置の作製方法。 - 請求項1又は2において、

前記有機膜は、シランカップリング剤を用いた処理を行うことにより形成することを特徴とする半導体装置の作製方法。 - 請求項3において、

前記シランカップリング剤は、フルオロアルキルシランであることを特徴とする半導体装置の作製方法。 - 請求項1又は2において、

前記有機膜は、フッ素を含む雰囲気下でのプラズマ処理によって形成することを特徴とする半導体装置の作製方法。 - 請求項1乃至5のいずれか一項において、

前記マスクパターンを液滴吐出法によって形成することを特徴とする半導体装置の作製方法。 - 請求項1乃至6のいずれか一項において、

前記マスクパターンは、ポリビニルアルコール、ポリイミド、アクリル、又はシロキサンからなることを特徴とする半導体装置の作製方法。 - 請求項1乃至7のいずれか一項において、

前記絶縁膜をスリットコーター法又はスピンコート法によって形成することを特徴とする半導体装置の作製方法。 - 請求項1乃至8のいずれか一項において、

前記絶縁膜は、ポリイミド系樹脂、アクリル系樹脂、ポリアミド系樹脂、又はシリコンと酸素との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、若しくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料からなることを特徴とする半導体装置の作製方法。 - 請求項1乃至9のいずれか一項において、

前記導電体を液滴吐出法によって形成することを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005019248A JP4667051B2 (ja) | 2004-01-29 | 2005-01-27 | 半導体装置の作製方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004022039 | 2004-01-29 | ||

| JP2005019248A JP4667051B2 (ja) | 2004-01-29 | 2005-01-27 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005244205A JP2005244205A (ja) | 2005-09-08 |

| JP2005244205A5 JP2005244205A5 (ja) | 2008-03-06 |

| JP4667051B2 true JP4667051B2 (ja) | 2011-04-06 |

Family

ID=35025563

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005019248A Expired - Fee Related JP4667051B2 (ja) | 2004-01-29 | 2005-01-27 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4667051B2 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4566575B2 (ja) * | 2004-02-13 | 2010-10-20 | 株式会社半導体エネルギー研究所 | 発光装置の作製方法 |

| TWI338189B (en) * | 2006-01-13 | 2011-03-01 | Hon Hai Prec Ind Co Ltd | Substrate structure and method of manufacturing thin film pattern layer using the same |

| JP2007324510A (ja) * | 2006-06-05 | 2007-12-13 | Sony Corp | 半導体装置の製造方法 |

| KR100809440B1 (ko) * | 2007-03-09 | 2008-03-05 | 한국전자통신연구원 | n-형 및 p-형 CIS를 포함하는 박막트랜지스터 및 그제조방법 |

| JP2009019266A (ja) * | 2007-06-15 | 2009-01-29 | Mec Kk | シランカップリング剤皮膜の形成方法 |

| US20170004978A1 (en) | 2007-12-31 | 2017-01-05 | Intel Corporation | Methods of forming high density metal wiring for fine line and space packaging applications and structures formed thereby |

| JP4937233B2 (ja) * | 2008-11-19 | 2012-05-23 | 三菱電機株式会社 | 太陽電池用基板の粗面化方法および太陽電池セルの製造方法 |

| US20100224880A1 (en) * | 2009-03-05 | 2010-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| EP2256814B1 (en) * | 2009-05-29 | 2019-01-16 | Semiconductor Energy Laboratory Co, Ltd. | Oxide semiconductor device and method for manufacturing the same |

| JP2011175996A (ja) * | 2010-02-23 | 2011-09-08 | Nippon Telegr & Teleph Corp <Ntt> | グラフェントランジスタおよびその製造方法 |

| JP5811560B2 (ja) * | 2011-03-25 | 2015-11-11 | セイコーエプソン株式会社 | 回路基板の製造方法 |

| KR102014876B1 (ko) * | 2011-07-08 | 2019-08-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작 방법 |

| JP2013073813A (ja) * | 2011-09-28 | 2013-04-22 | Toppan Printing Co Ltd | 有機エレクトロルミネッセンスパネルの製造方法 |

| JP6151158B2 (ja) * | 2012-11-28 | 2017-06-21 | 信越化学工業株式会社 | 透明酸化物電極用表面修飾剤、表面修飾された透明酸化物電極、及び表面修飾された透明酸化物電極の製造方法 |

| JP6706653B2 (ja) * | 2018-03-20 | 2020-06-10 | シャープ株式会社 | アクティブマトリクス基板 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07122638A (ja) * | 1993-10-26 | 1995-05-12 | Fujitsu Ltd | 半導体装置の製造方法 |

| JPH09312336A (ja) * | 1996-05-20 | 1997-12-02 | Yamaha Corp | 接続孔形成法 |

-

2005

- 2005-01-27 JP JP2005019248A patent/JP4667051B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07122638A (ja) * | 1993-10-26 | 1995-05-12 | Fujitsu Ltd | 半導体装置の製造方法 |

| JPH09312336A (ja) * | 1996-05-20 | 1997-12-02 | Yamaha Corp | 接続孔形成法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005244205A (ja) | 2005-09-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4667051B2 (ja) | 半導体装置の作製方法 | |

| KR101123749B1 (ko) | 콘택홀의 형성방법, 반도체장치의 제조방법,액정표시장치의 제조방법 및 전계발광 표시장치의 제조방법 | |

| US7572718B2 (en) | Semiconductor device and manufacturing method thereof | |

| US8518728B2 (en) | Semiconductor element, method for manufacturing the same, liquid crystal display device, and method for manufacturing the same | |

| US7868957B2 (en) | Thin film transistor, display device and liquid crystal display device and method for manufacturing the same | |

| US7642038B2 (en) | Method for forming pattern, thin film transistor, display device, method for manufacturing thereof, and television apparatus | |

| US7598129B2 (en) | Light-emitting device and method for manufacturing the same | |

| JP4712361B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP4522904B2 (ja) | 半導体装置の作製方法 | |

| JP2005150710A (ja) | 半導体素子の作製方法 | |

| JP4712352B2 (ja) | 発光装置の作製方法 | |

| JP4583904B2 (ja) | 表示装置の作製方法 | |

| JP4877868B2 (ja) | 表示装置の作製方法 | |

| JP2005203638A (ja) | 半導体膜、半導体膜の成膜方法、半導体装置およびその作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080121 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080121 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101020 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101026 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101208 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110105 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140121 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4667051 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |