JP4642531B2 - データ要求のアービトレーション - Google Patents

データ要求のアービトレーション Download PDFInfo

- Publication number

- JP4642531B2 JP4642531B2 JP2005106228A JP2005106228A JP4642531B2 JP 4642531 B2 JP4642531 B2 JP 4642531B2 JP 2005106228 A JP2005106228 A JP 2005106228A JP 2005106228 A JP2005106228 A JP 2005106228A JP 4642531 B2 JP4642531 B2 JP 4642531B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- memory

- access

- operable

- buses

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000015654 memory Effects 0.000 claims description 172

- 238000012545 processing Methods 0.000 claims description 69

- 238000012546 transfer Methods 0.000 claims description 27

- 238000000034 method Methods 0.000 claims description 12

- 230000004044 response Effects 0.000 claims description 7

- 238000004891 communication Methods 0.000 claims description 3

- 238000010586 diagram Methods 0.000 description 5

- LHMQDVIHBXWNII-UHFFFAOYSA-N 3-amino-4-methoxy-n-phenylbenzamide Chemical compound C1=C(N)C(OC)=CC=C1C(=O)NC1=CC=CC=C1 LHMQDVIHBXWNII-UHFFFAOYSA-N 0.000 description 4

- 230000004913 activation Effects 0.000 description 4

- 230000001154 acute effect Effects 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1605—Handling requests for interconnection or transfer for access to memory bus based on arbitration

- G06F13/1652—Handling requests for interconnection or transfer for access to memory bus based on arbitration in a multiprocessor architecture

- G06F13/1657—Access to multiple memories

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1605—Handling requests for interconnection or transfer for access to memory bus based on arbitration

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/28—Handling requests for interconnection or transfer for access to input/output bus using burst mode transfer, e.g. direct memory access DMA, cycle steal

Description

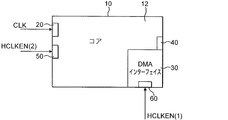

12 一方の部分

20 クロック信号入力

30 直接メモリ・インターフェイス

32 レジスタ

34 ANDゲート

40 読み取り/書き込みポート

42 入力

50 プロセッサ・イネーブル入力

55 AMBAバス

60 アクセス・イネーブル信号入力

70 命令メモリ

75A データ・バス

75B データ・バス

75C データ・バス

80 直接メモリ・アクセス・コントローラ(DMAC)

90 フラッシュ・メモリ

110 アービトレーション・ロジック

120 密結合メモリ

Claims (14)

- アービトレーション・ロジックと、

データ・プロセッサ・コアと

を備えたデータ処理装置であって、

前記データ・プロセッサ・コアが

外部データ・ソースとデータ・プロセッサ・コアに関連付けられている少なくとも1つのメモリとの間でデータ転送操作を実行するように動作可能なメモリ・アクセス・インターフェイス部分と、

データ処理操作を実行するように動作可能なデータ処理部分と、

前記プロセッサ・コアから少なくとも2つのバスにデータを転送するように動作可能な読み取り/書き込みポートであって、前記少なくとも2つのバスが前記プロセッサ・コアと前記少なくとも1つのメモリとの間にデータ通信を提供するように動作可能であり、前記少なくとも1つのメモリが少なくとも2つの部分を含み、前記少なくとも2つのバスのそれぞれが前記少なくとも2つの部分のそれぞれにデータ・アクセスを提供するように動作可能である読み取り/書き込みポートと

を含み、

前記アービトレーション・ロジックは前記読み取り/書き込みポートに関連付けられており、前記アービトレーション・ロジックが、前記メモリ・アクセス・インターフェイスから受信された前記少なくとも1つのメモリの一部にあるデータのアクセスを要求するデータ・アクセス要求を、前記少なくとも1つのメモリの前記一部にアクセスを提供する前記少なくとも2つのバスのうちの一方に経路設定し、前記データ処理部分から受信された前記少なくとも1つのメモリの別の一部にあるデータのアクセスを要求する別のデータ・アクセス要求を、前記少なくとも1つのメモリの前記別の一部にアクセスを提供する前記少なくとも2つのバスのうちのもう一方に経路設定するように動作可能であり、前記データ・アクセス要求の前記経路設定が同じクロック・サイクル中に実行され、

前記メモリの前記少なくとも2つの部分が、命令を格納するように動作可能である命令部分、及びデータ項目を格納するように動作可能である少なくとも1つのデータ部分を含み、前記アービトレーション・ロジックは、転送すべきデータが命令であるとき、前記命令部分へのアクセスを提供する前記少なくとも2つのバスのうちの第1のものに前記アクセス要求を経路設定し、転送すべきデータがデータ項目であるとき、前記少なくとも1つのデータ部分へのアクセスを提供する前記少なくとも2つのバスのうちの第2のものに前記データ・アクセス要求を経路設定するように動作可能であり、

前記少なくとも1つのデータ部分が、偶数アドレスを有するデータを格納するように動作可能な偶数データ部分、及び奇数アドレスを有するデータを格納するように動作可能な奇数データ部分の2つのデータ部分を含み、前記読み取り/書き込みポートが、前記命令部分へのアクセスを提供する第1のバス、前記奇数データ部分へのアクセスを提供する第2のバス、及び前記偶数データ部分へのアクセスを提供する第3のバスの3つのバスを介して前記プロセッサ・コアと前記少なくとも1つのメモリとの間にデータを転送するように動作可能であり、前記アービトレーション・ロジックが、転送すべきデータが命令であるときは前記第1のバスに、転送すべきデータが奇数アドレスに関連付けられているデータ項目であるときは前記第2のバスに、転送すべきデータが偶数アドレスに関連付けられているデータ項目であるときは前記第3のバスにデータ・アクセス要求を経路設定するように動作可能である

データ処理装置。 - 請求項1に記載のデータ処理装置であって、前記アービトレーション・ロジックが、前記データ・アクセス要求に関連付けられている前記少なくとも1つのメモリ内のアドレス位置に基づいて前記データ・アクセス要求を経路設定する前記少なくとも2つのバスのうちの一方を選択するように動作可能であるデータ処理装置。

- 請求項1に記載のデータ処理装置において、前記アービトレーション・ロジックが、前記少なくとも1つのメモリの一部にあるデータへのアクセスを要求する、前記メモリ・アクセス・インターフェイス部分からのデータ・アクセス要求、及び前記データ処理部分からのデータ・アクセス要求の両方のデータ・アクセス要求の受信に応答して、前記処理部分からの前記要求を前記少なくとも2つのバスのうちの前記一方に経路設定する前に、前記メモリ・アクセス・インターフェイス部分からの前記データ・アクセス要求を、前記少なくとも1つのメモリの前記一部にデータ・アクセスを提供する前記少なくとも2つのバスのうちの前記一方に経路設定するように動作可能であるデータ処理装置。

- 請求項1に記載のデータ処理装置であって、前記アービトレーション・ロジックが前記少なくとも1つのメモリの少なくとも1つのビジー部分から待機要求を検出するように動作可能であり、前記アービトレーション・ロジックが、前記待機要求が検出されなくなるまで、任意のデータ・アクセス要求を前記ビジー部分に経路設定しないように動作可能であるデータ処理装置。

- 請求項1に記載のデータ処理装置であって、さらに

少なくとも2つの部分に分割される少なくとも1つのメモリと、

前記少なくとも1つのメモリの前記少なくとも2つの部分のそれぞれの部分へのデータ・アクセスをそれぞれ可能にする少なくとも2つのバスと

を含むデータ処理装置。 - 請求項5に記載のデータ処理装置において、前記少なくとも1つのメモリが、命令を格納するように動作可能な命令部分、並びに偶数アドレスを有するデータを格納するように動作可能な偶数データ部分、及び奇数アドレスを有するデータを格納するように動作可能な奇数データ部分の2つのデータ部分の3つの部分に分割され、前記データ処理装置が3つのバスを含み、前記読み取り/書き込みポートが前記3つのバスを介して前記プロセッサ・コアと前記少なくとも1つのメモリとの間でデータを転送するように動作可能であり、第1のバスが前記命令部分へのアクセスを提供し、第2のバスが前記奇数データ部分へのアクセスを提供し、第3のバスが前記偶数部分へのアクセスを提供するデータ処理装置。

- 請求項5に記載のデータ処理装置において、前記少なくとも1つのメモリが密結合メモリであるデータ処理装置。

- 外部データ・ソースとデータ・プロセッサ・コアに関連付けられている少なくとも1つのメモリとの間にデータを転送する方法であって、前記データ・プロセッサ・コアが、前記外部データ・ソースと前記データ・プロセッサ・コアに関連付けられている前記少なくとも1つのメモリとの間のデータ転送操作を実行するように動作可能であるメモリ・アクセス・インターフェイス部分、及びデータ処理操作を実行するように動作可能であるデータ処理部分を含み、前記方法が

前記メモリ・アクセス・インターフェイス部分から受信された前記少なくとも1つのメモリの一部にあるデータのアクセスを要求するデータ・アクセス要求、及び前記データ処理部分から受信された前記少なくとも1つのメモリの別の部分にあるデータへのアクセスを要求するデータ・アクセス要求に応答して、前記メモリ・アクセス・インターフェイス部分から受信された前記データ・アクセス要求を少なくとも2つのバスのうちの一方に経路設定するステップであって、前記少なくとも2つのバスのうちの前記一方が前記少なくとも1つのメモリの前記一部へのアクセスを提供するステップと、前記データ処理部分から受信された前記データ・アクセス要求を前記少なくとも2つのバスのうちのもう一方のバスに経路設定するステップであって、前記別のバスが前記少なくとも1つのメモリの前記別の部分へのアクセスを提供するステップとを含み、前記データ・アクセス要求の前記経路設定が同じクロック・サイクル中に実行され、

前記メモリの前記少なくとも2つの部分が、命令を格納するように動作可能である命令部分、及びデータ項目を格納するように動作可能である少なくとも1つのデータ部分を含み、前記データ・アクセス要求を経路設定する前記ステップが、転送すべきデータが命令であるとき、前記命令部分へのアクセスを提供する前記少なくとも2つのバスのうちの一方にデータ・アクセス要求を経路設定し、転送すべきデータがデータ項目であるとき、前記少なくとも1つのデータ部分へのアクセスを提供する前記少なくとも2つのバスのうちのもう一方に前記データ・アクセス要求を経路設定するように動作可能であり、

前記少なくとも1つのデータ部分が、偶数アドレスを有するデータを格納するように動作可能な偶数データ部分、及び奇数アドレスを有するデータを格納するように動作可能な奇数データ部分の2つのデータ部分を含み、前記経路設定するステップが、前記命令部分へのアクセスを提供する第1のバス、前記奇数データ部分へのアクセスを提供する第2のバス、及び前記偶数データ部分へのアクセスを提供する第3のバスの3つのバスのうちの1つにデータ・アクセスを経路設定するように動作可能であり、前記経路設定するステップが、転送すべきデータが命令であるときは前記第1のバスに、転送すべきデータが奇数アドレスに関連付けられているデータ項目であるときは前記第2のバスに、転送すべきデータが偶数アドレスに関連付けられているデータ項目であるときは前記第3のバスにデータ・アクセス要求を経路設定するように動作可能である

方法。 - 請求項8に記載の方法において、データ・アクセス要求をそれぞれのデータ・バスに経路設定する前記ステップが、前記データ・アクセス要求に関連付けられている前記少なくとも1つのメモリ内のアドレス位置に基づいて行われる方法。

- 請求項8に記載の方法において、前記経路設定するステップが、前記少なくとも2つのバスのうちの一方によってアクセスされる前記少なくとも1つのメモリの一部にあるデータへのアクセスを要求する、前記メモリ・アクセス・インターフェイス部分からのデータ・アクセス要求、及び前記データ処理部分からのデータ・アクセス要求の両方のデータ・アクセス要求の受信に応答して、前記処理部分からの前記要求を前記少なくとも2つのバスのうちの前記一方に経路設定する前に、前記メモリ・アクセス・インターフェイス部分からの前記データ・アクセス要求を前記少なくとも2つのバスのうちの前記一方に経路設定する方法。

- 請求項8に記載の方法において、前記経路設定するステップが、前記少なくとも1つのメモリの少なくとも1つのビジー部分から待機要求を検出し、前記待機要求の検出に応答して、前記待機要求が検出されなくなるまで、前記ビジー部分にデータ・アクセス要求を経路設定しない方法。

- 請求項8に記載の方法において、前記少なくとも1つのメモリが、命令を格納するように動作可能な命令部分、並びに偶数アドレスを有するデータを格納するように動作可能な偶数データ部分、及び奇数アドレスを有するデータを格納するように動作可能な奇数データ部分の2つのデータ部分の3つの部分に分割され、前記経路設定するステップが、前記データ・アクセス要求に関連付けられている前記データのアドレスに基づいて、受信したデータ・アクセス要求を3つのバスのうちの1つに経路設定し、第1のバスが前記命令部分へのアクセスを提供し、第2のバスが前記奇数データ部分へのアクセスを提供し、第3のバスが前記偶数データ部分へのアクセスを提供する方法。

- 請求項8から12までのいずれか一項による方法の諸ステップを実行するようにデータ・プロセッサを制御するよう動作可能であるアービトレーション・ロジック。

- 請求項1に記載のデータ処理装置において、前記データ・プロセッサ・コアが前記アービトレーション・ロジックを含むデータ処理装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/815,961 US7240144B2 (en) | 2004-04-02 | 2004-04-02 | Arbitration of data transfer requests |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005293596A JP2005293596A (ja) | 2005-10-20 |

| JP2005293596A5 JP2005293596A5 (ja) | 2007-08-30 |

| JP4642531B2 true JP4642531B2 (ja) | 2011-03-02 |

Family

ID=34574887

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005106228A Active JP4642531B2 (ja) | 2004-04-02 | 2005-04-01 | データ要求のアービトレーション |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7240144B2 (ja) |

| JP (1) | JP4642531B2 (ja) |

| GB (1) | GB2412767B (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8510491B1 (en) * | 2005-04-05 | 2013-08-13 | Oracle America, Inc. | Method and apparatus for efficient interrupt event notification for a scalable input/output device |

| CN101118523B (zh) * | 2006-08-01 | 2011-10-19 | 飞思卡尔半导体公司 | 存储器访问控制装置及其方法、存储器访问控制器及其方法 |

| US9015720B2 (en) * | 2008-04-30 | 2015-04-21 | Advanced Micro Devices, Inc. | Efficient state transition among multiple programs on multi-threaded processors by executing cache priming program |

| US20120102242A1 (en) * | 2010-10-26 | 2012-04-26 | Kaminario Technologies Ltd. | Controlling data destaging within a multi-tiered storage system |

| FR2986345B1 (fr) * | 2012-01-27 | 2014-02-28 | Simpulse | Procede de gestion de requetes d'acces a des memoires et systeme de stockage de donnees |

| US10599208B2 (en) | 2015-09-08 | 2020-03-24 | Toshiba Memory Corporation | Memory system and controller |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10509540A (ja) * | 1994-10-04 | 1998-09-14 | アナログ・デバイセス・インコーポレーテッド | ディジタル信号プロセッサ |

| JP2000163312A (ja) * | 1998-12-01 | 2000-06-16 | Fujitsu Ltd | マイクロプロセッサ |

| JP2000215187A (ja) * | 1999-01-01 | 2000-08-04 | Seiko Epson Corp | マルチプロセッサシステム |

| JP2000235560A (ja) * | 1999-02-16 | 2000-08-29 | Hitachi Ltd | マイクロコンピュータ及びマイクロコンピュータシステム |

| JP2003140964A (ja) * | 2001-11-05 | 2003-05-16 | Denso Corp | データ処理システム |

| JP2004062900A (ja) * | 2002-07-29 | 2004-02-26 | Samsung Electronics Co Ltd | バス帯域幅を増加させるためのメモリコントローラ、これを利用したデータ伝送方法及びこれを備えるコンピュータシステム |

Family Cites Families (53)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| NO173304C (no) * | 1984-12-20 | 1993-11-24 | Honeywell Inc | Dobbelt buss-system |

| US4744006A (en) * | 1986-07-10 | 1988-05-10 | Duffield Robert H | Apparatus for expanding the input/output capabilities of a personal computer |

| JPS63236153A (ja) * | 1987-03-24 | 1988-10-03 | Nec Corp | 記憶装置 |

| US4979100A (en) * | 1988-04-01 | 1990-12-18 | Sprint International Communications Corp. | Communication processor for a packet-switched network |

| US5191573A (en) * | 1988-06-13 | 1993-03-02 | Hair Arthur R | Method for transmitting a desired digital video or audio signal |

| US5184282A (en) * | 1989-02-27 | 1993-02-02 | Mips Co., Ltd. | IC card adapter |

| DE3943879B4 (de) * | 1989-04-17 | 2008-07-17 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | Digitales Codierverfahren |

| CA2017471C (en) * | 1989-07-19 | 2000-10-24 | Matthew Eric Krisl | Optical interference coatings and lamps using same |

| WO1991015101A1 (de) * | 1990-03-17 | 1991-10-03 | Amphenol-Tuchel Electronics Gmbh | Kontaktiereinrichtung, insbesondere für ein sim |

| US5049728A (en) * | 1990-04-04 | 1991-09-17 | Rovin George H | IC card system with removable IC modules |

| US5663901A (en) * | 1991-04-11 | 1997-09-02 | Sandisk Corporation | Computer memory cards using flash EEPROM integrated circuit chips and memory-controller systems |

| US5291584A (en) * | 1991-07-23 | 1994-03-01 | Nexcom Technology, Inc. | Methods and apparatus for hard disk emulation |

| JPH06209444A (ja) * | 1992-04-29 | 1994-07-26 | Canon Inf Syst Res Australia Pty Ltd | マルチメディア装置 |

| EP0620933A4 (en) * | 1992-11-12 | 1995-03-01 | New Media Corp | RECONFIGURABLE INTERFACE BETWEEN A COMPUTER AND PERIPHERAL DEVICES. |

| JPH0737049A (ja) * | 1993-07-23 | 1995-02-07 | Toshiba Corp | 外部記憶装置 |

| US5887145A (en) * | 1993-09-01 | 1999-03-23 | Sandisk Corporation | Removable mother/daughter peripheral card |

| FR2710996B1 (fr) * | 1993-10-06 | 1995-12-01 | Gemplus Card Int | Carte portable multi-applications pour ordinateur personnel. |

| US5519577A (en) * | 1993-12-23 | 1996-05-21 | Symbol Technologies, Inc. | Spread spectrum radio incorporated in a PCMCIA Type II card holder |

| US5491774A (en) * | 1994-04-19 | 1996-02-13 | Comp General Corporation | Handheld record and playback device with flash memory |

| US5664231A (en) * | 1994-04-29 | 1997-09-02 | Tps Electronics | PCMCIA interface card for coupling input devices such as barcode scanning engines to personal digital assistants and palmtop computers |

| US5545057A (en) * | 1994-05-27 | 1996-08-13 | Hon Hai Precision Ind. Co., Ltd. | Interconnection system with I/O connector module board |

| US5577230A (en) * | 1994-08-10 | 1996-11-19 | At&T Corp. | Apparatus and method for computer processing using an enhanced Harvard architecture utilizing dual memory buses and the arbitration for data/instruction fetch |

| US5611055A (en) * | 1994-09-27 | 1997-03-11 | Novalink Technologies | Method and apparatus for implementing a PCMCIA auxiliary port connector for selectively communicating with peripheral devices |

| US5611057A (en) * | 1994-10-06 | 1997-03-11 | Dell Usa, L.P. | Computer system modular add-in daughter card for an adapter card which also functions as an independent add-in card |

| US5619396A (en) * | 1995-02-21 | 1997-04-08 | Intel Corporation | Modular PCMCIA card |

| US5818030A (en) * | 1995-03-07 | 1998-10-06 | Reyes; Rene A. | Credit card system with key module |

| US5892213A (en) * | 1995-09-21 | 1999-04-06 | Yamaichi Electronics Co., Ltd. | Memory card |

| DE29518707U1 (de) * | 1995-11-25 | 1996-01-18 | Stocko Metallwarenfab Henkels | Kontaktiereinheit für kartenförmige Trägerelemente elektronischer Baugruppen |

| US5661635A (en) * | 1995-12-14 | 1997-08-26 | Motorola, Inc. | Reusable housing and memory card therefor |

| JP2721329B2 (ja) * | 1995-12-28 | 1998-03-04 | 山一電機株式会社 | カードイン形コネクタ |

| US5787445A (en) * | 1996-03-07 | 1998-07-28 | Norris Communications Corporation | Operating system including improved file management for use in devices utilizing flash memory as main memory |

| FR2747847B1 (fr) * | 1996-04-18 | 1998-07-03 | Itt Composants Instr | Boitier de raccordement electronique, a un ordinateur individuel, equipe d'un connecteur pour une carte a puce |

| US5752857A (en) * | 1996-05-24 | 1998-05-19 | Itt Corporation | Smart card computer adaptor |

| TW332334B (en) * | 1996-05-31 | 1998-05-21 | Toshiba Co Ltd | The semiconductor substrate and its producing method and semiconductor apparatus |

| JPH09327990A (ja) * | 1996-06-11 | 1997-12-22 | Toshiba Corp | カード型記憶装置 |

| EP0833268A3 (de) * | 1996-09-20 | 1999-01-20 | Siemens Aktiengesellschaft | Kartenlesevorrichtung |

| JP3585336B2 (ja) * | 1997-02-24 | 2004-11-04 | 沖電気工業株式会社 | Icカードアダプタ |

| JPH10302030A (ja) * | 1997-02-28 | 1998-11-13 | Toshiba Corp | 接続装置、および情報処理装置 |

| JPH10254767A (ja) * | 1997-03-10 | 1998-09-25 | Sharp Corp | メモリ制御装置及び該メモリ制御装置によるメモリシステム |

| US5876218A (en) * | 1997-05-28 | 1999-03-02 | Gateway 2000, Inc. | Piggy back PC card |

| US5879007A (en) * | 1997-11-12 | 1999-03-09 | Kasri; Omar | Simplified game of chance and skill |

| US5928347A (en) * | 1997-11-18 | 1999-07-27 | Shuttle Technology Group Ltd. | Universal memory card interface apparatus |

| US6102714A (en) * | 1998-03-02 | 2000-08-15 | 3Com Corporation | Electrical connectors having dual biased contact pins |

| KR100278368B1 (ko) * | 1998-04-10 | 2001-01-15 | 윤종용 | 확장 카드를 소켓에 접속시키기 위한 구조를 갖는 휴대형 전자시스템 |

| US5933328A (en) * | 1998-07-28 | 1999-08-03 | Sandisk Corporation | Compact mechanism for removable insertion of multiple integrated circuit cards into portable and other electronic devices |

| US6293464B1 (en) * | 1999-01-05 | 2001-09-25 | Jared Joseph Smalley, Jr. | Card reader |

| US6276943B1 (en) * | 1999-02-22 | 2001-08-21 | Amphenol Corporation | Modular plug connector and improved receptacle therefore |

| US6599147B1 (en) * | 1999-05-11 | 2003-07-29 | Socket Communications, Inc. | High-density removable expansion module having I/O and second-level-removable expansion memory |

| US6353870B1 (en) * | 1999-05-11 | 2002-03-05 | Socket Communications Inc. | Closed case removable expansion card having interconnect and adapter circuitry for both I/O and removable memory |

| JP2001043180A (ja) * | 1999-08-03 | 2001-02-16 | Mitsubishi Electric Corp | マイクロプロセッサおよびそのための記憶装置 |

| US6681283B1 (en) * | 1999-08-12 | 2004-01-20 | Mips Technologies, Inc. | Coherent data apparatus for an on-chip split transaction system bus |

| JP4059473B2 (ja) * | 2001-08-09 | 2008-03-12 | 株式会社ルネサステクノロジ | メモリカード及びメモリコントローラ |

| US6931479B2 (en) * | 2003-03-04 | 2005-08-16 | Micron Technology, Inc. | Method and apparatus for multi-functional inputs of a memory device |

-

2004

- 2004-04-02 US US10/815,961 patent/US7240144B2/en active Active

-

2005

- 2005-03-30 GB GB0506399A patent/GB2412767B/en active Active

- 2005-04-01 JP JP2005106228A patent/JP4642531B2/ja active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10509540A (ja) * | 1994-10-04 | 1998-09-14 | アナログ・デバイセス・インコーポレーテッド | ディジタル信号プロセッサ |

| JP2000163312A (ja) * | 1998-12-01 | 2000-06-16 | Fujitsu Ltd | マイクロプロセッサ |

| JP2000215187A (ja) * | 1999-01-01 | 2000-08-04 | Seiko Epson Corp | マルチプロセッサシステム |

| JP2000235560A (ja) * | 1999-02-16 | 2000-08-29 | Hitachi Ltd | マイクロコンピュータ及びマイクロコンピュータシステム |

| JP2003140964A (ja) * | 2001-11-05 | 2003-05-16 | Denso Corp | データ処理システム |

| JP2004062900A (ja) * | 2002-07-29 | 2004-02-26 | Samsung Electronics Co Ltd | バス帯域幅を増加させるためのメモリコントローラ、これを利用したデータ伝送方法及びこれを備えるコンピュータシステム |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005293596A (ja) | 2005-10-20 |

| US7240144B2 (en) | 2007-07-03 |

| GB2412767A (en) | 2005-10-05 |

| GB0506399D0 (en) | 2005-05-04 |

| GB2412767B (en) | 2006-09-06 |

| US20050223129A1 (en) | 2005-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4821185A (en) | I/O interface system using plural buffers sized smaller than non-overlapping contiguous computer memory portions dedicated to each buffer | |

| JP3218773B2 (ja) | キャッシュ・コントローラ | |

| US20060059489A1 (en) | Parallel processing system, interconnection network, node and network control method, and program therefor | |

| JP4642531B2 (ja) | データ要求のアービトレーション | |

| JP2008276391A (ja) | メモリアクセス制御装置 | |

| US7165126B2 (en) | Direct memory access device | |

| US5594880A (en) | System for executing a plurality of tasks within an instruction in different orders depending upon a conditional value | |

| US7096307B2 (en) | Shared write buffer in a peripheral interface and method of operating | |

| US7254667B2 (en) | Data transfer between an external data source and a memory associated with a data processor | |

| JPH11232213A (ja) | 入出力装置におけるデータ転送方式 | |

| KR920002830B1 (ko) | 다이렉트 메모리 액세스 제어장치 | |

| CA2078913A1 (en) | Interprocessor communication system and method for multiprocessor circuitry | |

| US20080209085A1 (en) | Semiconductor device and dma transfer method | |

| EP0437712A2 (en) | Tandem cache memory | |

| JP2009037639A (ja) | ストリーミングidメソッドによるdmac発行メカニズム | |

| JPH10283302A (ja) | 複数のプロセッサに接続されたバスにデータを供給する方法およびシステム | |

| JP2005107873A (ja) | 半導体集積回路 | |

| JP3077807B2 (ja) | マイクロコンピュータシステム | |

| JP6992616B2 (ja) | データ転送装置、データ転送方法、プログラム | |

| JP4818820B2 (ja) | バスシステムおよびバススレーブならびにバス制御方法 | |

| JP7003752B2 (ja) | データ転送装置、データ転送方法、プログラム | |

| JPH0962633A (ja) | ネットワーク制御装置 | |

| WO2011030498A1 (ja) | データ処理装置及びデータ処理方法 | |

| JP2004220309A (ja) | マルチプロセッサシステム | |

| JP2632859B2 (ja) | メモリアクセス制御回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070711 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070711 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100728 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100803 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101026 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101116 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101201 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4642531 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131210 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |