JP4638544B2 - 不揮発性メモリにおける改善されたプログラムベリファイ操作のための方法および装置 - Google Patents

不揮発性メモリにおける改善されたプログラムベリファイ操作のための方法および装置 Download PDFInfo

- Publication number

- JP4638544B2 JP4638544B2 JP2008548835A JP2008548835A JP4638544B2 JP 4638544 B2 JP4638544 B2 JP 4638544B2 JP 2008548835 A JP2008548835 A JP 2008548835A JP 2008548835 A JP2008548835 A JP 2008548835A JP 4638544 B2 JP4638544 B2 JP 4638544B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- programming

- threshold voltage

- group

- memory cells

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3454—Arrangements for verifying correct programming or for detecting overprogrammed cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3454—Arrangements for verifying correct programming or for detecting overprogrammed cells

- G11C16/3459—Circuits or methods to verify correct programming of nonvolatile memory cells

Description

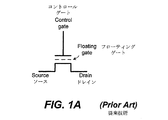

メモリ素子は、通常、カードに搭載され得る1つ以上のメモリチップを含む。各メモリチップは、デコーダおよび消去回路、書き込み回路および読み出し回路のような周辺回路により支援されるメモリセルのアレイを含む。精巧なメモリ素子は、インテリジェントで高レベルのメモリ操作およびインターフェイス操作を実行するコントローラをも伴う。多くの商業的に成功した不揮発性個体メモリ素子が今日使用されている。これらのメモリ素子はいろいろなタイプのメモリセルを採用することができ、その各々のタイプが1つ以上の電荷蓄積素子を有する。

メモリ素子は、通常、行および列を成すように配列されてワード線およびビット線によりアドレス指定できるメモリセルの2次元アレイから構成される。このアレイは、NORタイプまたはNANDタイプのアーキテクチャに従って形成され得る。

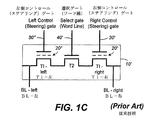

図2は、メモリセルのNORアレイの例を示す。NORタイプのアーキテクチャを有するメモリ素子は、図1Bまたは図1Cに示されているタイプのセルで実現されている。メモリセルの各行は、そのソースおよびドレインによりデイジーチェーン式に接続される。この設計は、時には仮想接地設計と称される。各メモリセル10は、ソース14と、ドレイン16と、コントロールゲート30と、選択ゲート40とを有する。1つの行内のセルの選択ゲートはワード線42に接続される。1つの列内のセルのソースおよびドレインは、選択されたビット線34および36にそれぞれ接続される。メモリセルのコントロールゲートと選択ゲートとが独立して制御される実施形態では、1つのステアリング線36も1つの列内のセルのコントロールゲート同士を接続する。

図3は、図1Dに示されているもののようなメモリセルのNANDアレイの例を示す。NANDチェーンの各列に沿って、ビット線が各NANDチェーンのドレイン端子56に結合されている。NANDチェーンの各行に沿って、ソース線がその全てのソース端子54を接続することができる。また、1つの行に沿うNANDチェーンのコントロールゲートが一連の対応するワード線に接続されている。NANDチェーンの1つの行全体が、選択トランジスタの対(図1Dを参照)を、接続されているワード線を介してそのコントロールゲートに加わる適切な電圧でオンに転換することによって、アドレス指定され得る。NANDチェーンの中の1つのメモリセルを代表するメモリトランジスタが読み出されるとき、そのチェーンを通って流れる電流がその読み出されているセルに蓄積されている電荷のレベルに本質的に依存するように、そのチェーンの中の残りのメモリトランジスタはそれに関連付けられているワード線を介してしっかりオンに転換される。NANDアーキテクチャアレイおよびメモリシステムの一部としてのその動作の例が、米国特許第5,570,315号(特許文献9)、第5,774,397号(特許文献16)および第6,046,935号(特許文献11)において見出される。

NANDメモリをプログラムする場合、選択されたメモリセルのページに接続するワード線にプログラミング電圧パルスが印加される。そのページの中で、プログラムされるべきメモリセルのビット線電圧は0Vにセットされ、プログラムされるべきでない他のメモリセルのビット線電圧はプログラミングを禁止するためにシステム供給電圧Vddにセットされる。ビット線をVddにセットすると、実際上、NANDチェーンのドレイン側の選択トランジスタがオフに転換され、チャネルが浮遊されるという結果がもたらされる。プログラミング中、浮遊されたチャネルの電圧は高いワード線電圧によって昇圧される。これは、実際上、チャネルと電荷蓄積ユニットとの間の電位差を減少させ、これによりプログラミングを行うチャネルから電荷蓄積ユニットへの電子の引っ張り作用を抑制する。

電荷蓄積メモリ素子のプログラミングは、より多くの電荷をその電荷蓄積素子に付け加えるという結果をもたらし得るにすぎない。従って、プログラミング操作の前に、電荷蓄積素子内に存在する電荷が除去(あるいは消去)されなければならない。メモリセルの1つ以上のブロックを消去するために消去回路(図示せず)が設けられる。EEPROMのような不揮発性メモリは、セルのアレイ全体、あるいはアレイに属するセルのかなりのグループが一緒に電気的に(すなわち、一瞬のうちに(in a flash))消去されるとき、「フラッシュ」EEPROMと称される。消去後、そのセルのグループは再プログラムされ得る。一緒に消去可能なセルのグループは、1つ以上のアドレス指定可能な消去ユニットから成り得る。消去ユニットまたはブロックは通常1ページ以上のデータを記憶し、ページはプログラミングおよび読み出しの単位であるが、1操作で2ページ以上がプログラムされるかあるいは読み出され得る。各ページは通常1セクタ以上のデータを記憶し、セクタのサイズはホストシステムにより定められる。一例は、磁気ディスクドライブに対して確立された標準規格に従う512バイトのユーザデータと、そのユーザデータおよび/またはそれが格納されているブロックに関する数バイトのオーバーヘッド情報とから成るセクタである。

普通の2状態EEPROMセルでは、伝導ウィンドウを2つの領域に分割するために少なくとも1つの電流ブレークポイントレベルが確立される。所定の固定された電圧を印加することによってセルが読み出されるとき、そのソース/ドレイン電流は、ブレークポイントレベル(あるいは基準電流IREF )との比較によって1つのメモリ状態に分解される。読み出された電流がブレークポイントレベルのものより大きければ、そのセルは1つの論理状態(例えば、「ゼロ」状態)にあると判定される。一方、電流がブレークポイントレベルのものより少なければ、そのセルは他方の論理状態(例えば、「1」状態)にあると判定される。従って、このよう2状態セルは1ビットのデジタル情報を記憶する。ブレークポイントレベル電流を生成するために、外部からプログラム可能であり得る基準電流源がメモリシステムの一部としてしばしば設けられる。

読み出しおよびプログラミングの性能を改善するために、アレイ内の複数の電荷蓄積素子またはメモリトランジスタが並行して読み出されるかまたはプログラムされる。従って、メモリ素子の1つの論理「ページ」が一緒に読み出されるかまたはプログラムされる。現存するメモリアーキテクチャでは、1つの行は通常数個のインターリーブされたページを含む。1ページのメモリ素子の全てが一緒に読み出されるかまたはプログラムされる。列デコーダは、インターリーブされたページの各々を対応する数の読み出し/書き込みモジュールに選択的に接続する。例えば、1つの実施例では、メモリアレイは532バイト(512バイトと、20バイトのオーバーヘッド)のページサイズを持つように設計される。各列が1つのドレインビット線を含み、行あたりに2つのインターリーブされたページがあるならば、8,512列があり、各ページが4,256列と関連付けられることになる。全ての偶数ビット線または奇数ビット線を並行して読み出しまたは書き込むために接続可能な4,256個のセンスモジュールがある。このようにして、並列の、1ページの4,256ビット(すなわち、532バイト)のデータが、メモリ素子のページから読み出されるかまたはそれにプログラムされる。読み出し/書き込み回路170を形成する読み出し/書き込みモジュールは、種々のアーキテクチャに配列され得る。

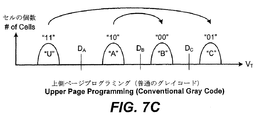

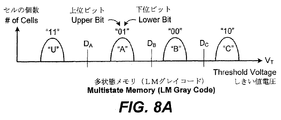

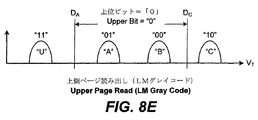

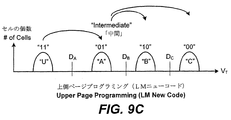

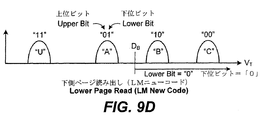

図7A〜7E、図8A〜8E、図9A〜9Eは、それぞれ4状態メモリのためのマルチビット符号化の3つの例を示す。4状態メモリセルでは、4つの状態が2ビットで表され得る。1つの現存する技術は、そのようなメモリをプログラムするために2パスプログラミングを使用する。第1のビット(下側ページビット)は第1のパスによりプログラムされる。その後、所望の第2のビット(上側ページビット)を表すために第2のパスで同じセルがプログラムされる。第2のパスにおいて第1のビットの値を変化させないために、第2のビットのメモリ状態表示は第1のビットの値に依存させられる。

不揮発性メモリの性能における1つの重要な態様はプログラミング速度である。このセクションは、多状態不揮発性メモリのプログラミング性能を改善する方法を論じる。特に、1つの改善されたプログラミング操作が時間節約プログラムベリファイで実現される。

1つの好ましいプログラミング操作は「クイックパス書き込み(Quick Pass Write)」(あるいは「QPW」)と称され、その全体が本願明細書において参照により援用されている、米国特許第6,643,188号(特許文献24)に開示されている。

最新のクイックパス書き込み(QPW)ベリファイ方式は、2つの別々の独特のVLベリファイおよびVHベリファイを組み合わせて1つのベリファイシーケンスとする。この方式ではWLは放電し再充電することなく同じベリファイシーケンスの中でVLからVHへ変化し、これにより、図12および図13に関して説明した2パスプログラミング方式と比べて時間を節約する。しかし、図15から分かるように、各ベリファイサイクルが常にVLサブサイクルとVHサブサイクルとを含む。

ステップ710:並行してプログラムされるべきメモリセルのグループを選択する。

プログラムサイクル

ステップ712:そのグループに共通のワード線に適切なプログラミングパルスを加える。

第1のしきい値に関しての第1のベリファイサブサイクル

ステップ720:そのワード線を第2のしきい値電圧より所定のマージン下の第1のしきい値電圧にプリチャージし、そのとき、プログラムされたセルは第2のしきい値電圧に関してベリファイされる。

ステップ722:そのグループに関連付けられているビット線を感知に適する電圧にプリチャージする。

ステップ724:そのグループのメモリセルを並行して感知する。

ステップ726:いずれかのセルが第1のしきい値電圧に関して首尾よくベリファイされたならば(すなわち、いずれか「1ビット通過」についてのチェック)、ステップ730の第2のベリファイサブサイクルに進み、そうでなければ第2のサブサイクルを省いてステップ712の次のプログラミングパルスに進む。

第2のしきい値に関しての第2のベリファイサブサイクル

ステップ730:プログラミングを低速化するために、ベリファイされたセルのビット線電圧を変更する。

ステップ740:ワード線を、それに関して感知が実行されるところの第2のしきい値電圧にプリチャージする。

ステップ742:そのグループのメモリセルを並行して感知する。

ステップ744:いずれかのセルが第2のしきい値電圧に関して首尾よくベリファイされたならば、ステップ750に進み、そうでなければステップ712の次のプログラミングパルスに進む。

ステップ750:そのグループ中の、第2のしきい値に関してベリファイされる必要のあるセルの全てが首尾よくベリファイされたならば、ステップ760に進み、そうでなければステップ752に進む。

ステップ752:ちょうどベリファイされたばかりのセルがプログラムされるのを妨げ、ステップ712の次のプログラミングパルスに進む。

ステップ760:第2のしきい値電圧に関してのベリファイについて、プログラミングは終了した。

フェーズ1:選択されたワード線WLをVLにプリチャージする。

フェーズ2:ビット線BLを感知に適する電圧にプリチャージする。

フェーズ3:感知し、STBをストローブする(VLストローブ)。

フェーズ4:ワード線WLの電圧をVLからVHに変化させ、ビット線電圧が回復した後、いずれか1つのビットがVLでベリファイしたか否かを判定するためにOBP(1ビット通過)を実行する。

フェーズ1〜4:図17に示されている短縮サイクルのものと同じである。

フェーズ5:感知されたVLデータをデータラッチに転送する(VL走査)。フェーズ4で始まったWL充電は割合に長い時間を必要とするので、時間を節約するために同じベリファイシーケンスにおいていずれかのビットがVLを通過することをOBPが検出した直後にVL走査を実行することが望ましい。

フェーズ6:感知し、ストローブする(第1のVHストローブ)。好ましい実施形態では、これは大電流状態を、それらがサブシーケンス感知を妨げないようにオフに転換され得るように、検出するための予備的急速感知である。

フェーズ7:ビット線BLが適切な電圧に戻ることを許容する。

フェーズ8:感知し、ストローブする(第2のVHストローブ)。

フェーズ9:ワード線WLを放電させる。

フェーズ10:感知されたVHデータをデータラッチに転送する(VH走査)。

フェーズ1:選択されたワード線WLをVLにプリチャージする。

フェーズ2:ビット線BLを感知に適する電圧にプリチャージする。

フェーズ3:感知し、STBをストローブする(VLストローブ)。

フェーズ4:ワード線WLの電圧をVLからVHに変更し、感知されたVLデータをデータラッチに転送する(VL走査)。

フェーズ5:感知し、ストローブする(第1のVHストローブ)。好ましい実施形態では、これはVHレベルより実質的に低い大電流状態を、それらがサブシーケンス感知を妨げないようにオフに転換され得るように、検出するための予備的急速感知である。

フェーズ6:ビット線BLが適切な電圧に戻ることを許容する。

フェーズ7:感知し、感知されたVHデータのためにストローブする(第2のVHストローブ)。

フェーズ8:ワード線WLを放電させる。

フェーズ9:感知されたVHデータをデータラッチに転送する(VH走査)。

SQPWについての前の説明は、所与のしきい値レベルに関してのプログラムベリファイに関連している。それに関してのベリファイが行われるところのしきい値レベルが2つ以上あっても、同じ原理が本質的に当てはまる。これは、3つのしきい値レベルVA、VBおよびVCにより画定される2ビットあるいは4状態のメモリのようなマルチレベルメモリをプログラムするときに起こり得ることである。例えば、図9Cに示されているLMニューコードを用いる上側ページのプログラミングは、3つのしきい値レベルの全てに関してのプログラムベリファイを必要とする。

Claims (28)

- 境界しきい値電圧に関して1グループのメモリセルを並行してプログラムする方法であって、

(a)前記グループのメモリセルにプログラミングパルスを加えるステップと、

(b)前記グループのメモリセルを、前記境界しきい値電圧のものから所定のマージン下の第1の基準しきい値電圧に関してベリファイするステップと、

(c)前記メモリセルのうちの1つが前記第1の基準しきい値電圧に関してベリファイされるまで(a)から(b)までを反復するステップと、

(d)前記第1の基準しきい値電圧でベリファイされたメモリセルのためのプログラミングセットアップを、このメモリセルのためのその後のプログラミングを低速化するためにビット線の電圧を高めることによって変更するステップと、

(e)前記グループのメモリセルにプログラミングパルスを加えるステップと、

(f)前記グループのメモリセルを、前記境界しきい値電圧のものから所定のマージン下の前記第1の基準しきい値電圧に関してベリファイするステップと、

(g)前記第1の基準しきい値電圧でベリファイされたメモリセルのための前記プログラミングセットアップを、このメモリセルのためのその後のプログラミングを低速化するためにビット線の電圧を高めることによって変更するステップと、

(h)前記グループのメモリセルを前記境界しきい値電圧に関してベリファイするステップと、

(i)前記境界しきい値電圧に関してベリファイされたメモリセルがさらにプログラムされるのを妨げるステップと、

(j)前記グループ中の全てのメモリセルが前記境界しきい値電圧に関してプログラムベリファイされるまで(e)から(i)までを反復するステップと、

を含む方法。 - 請求項1記載の方法において、

関連するビット線により前記グループのメモリセルにアクセスするステップと、

供給電圧を提供するステップと、をさらに含み、

前記メモリセルがさらにプログラムされるのを妨げるステップは、妨げられないメモリセルのビット線が実質的にゼロ電圧である間に前記メモリセルと関連する前記ビット線を実質的に前記供給電圧に高めるステップを含む方法。 - 請求項1記載の方法において、

前記プログラミングパルスは、全てのパルスで単調に増大する方法。 - 請求項1記載の方法において、

前記グループのメモリセルは、フラッシュEEPROMの一部分である方法。 - 請求項1記載の方法において、

前記グループのメモリセルは、メモリカードにおいて具体化される方法。 - 境界しきい値電圧に関して1グループのメモリセルを並行してプログラムする方法であって、

交互にプログラミングパルスを加え、前記グループのメモリセルについてのプログラムされた結果を並行してベリファイするステップを含み、

前記ベリファイするステップは、

前記境界しきい値電圧のものから所定のマージン下の第1の基準しきい値電圧に関しての第1のベリファイと、

前記第1の基準しきい値電圧に関してベリファイされた前記メモリセルのプログラミングを低速化するステップと、

前記境界しきい値電圧に関しての第2のベリファイと、

前記境界しきい値電圧に関してベリファイされた前記メモリセルがさらにプログラムされるのを妨げるステップと、をさらに含み、

前記グループのメモリセルのうちの少なくとも1つが前記第1の基準しきい値電圧に関してベリファイされるまで前記第2のベリファイは省かれる方法。 - 請求項6記載の方法において、

関連するビット線により前記グループのメモリセルにアクセスするステップをさらに含み、

プログラミングセットアップを変更するステップは、前記第1の基準しきい値電圧でベリファイされた前記メモリセルの前記プログラミングを低速化するためにビット線の電圧を高めるステップを含む方法。 - 請求項6記載の方法において、

関連するビット線により前記グループのメモリセルにアクセスするステップと、

供給電圧を提供するステップと、をさらに含み、

前記メモリセルがさらにプログラムされるのを妨げるステップは、妨げられないメモリセルのビット線が実質的にゼロ電圧である間に前記メモリセルと関連する前記ビット線を実質的に前記供給電圧に高めるステップを含む方法。 - 請求項6記載の方法において、

前記プログラミングパルスは、全てのパルスで単調に増大する方法。 - 請求項6記載の方法において、

前記グループのメモリセルは、フラッシュEEPROMの一部分である方法。 - 請求項6記載の方法において、

前記グループのメモリセルは、メモリカードにおいて具体化される方法。 - 請求項6〜11のいずれか記載の方法において、

個々のメモリセルは各々2つの状態のうちの一方にプログラム可能であり、前記境界しきい値電圧は前記2つの状態を区別するためのものである方法。 - 請求項6〜11のいずれか記載の方法において、

個々のメモリセルは各々3つ以上の状態のうちの1つにプログラム可能であり、前記境界しきい値電圧は前記3つ以上の状態を区別するための複数の境界しきい値電圧のうちの1つである方法。 - 請求項6〜11のいずれか記載の方法において、

個々のメモリセルは各々3つ以上の状態のうちの1つにプログラム可能であり、前記境界しきい値電圧は前記3つ以上の状態を区別するための複数の境界しきい値電圧のうちの1つであり、前記複数の境界しきい値電圧の各々に関して前記ステップの全てを反復するステップをさらに含む方法。 - 不揮発性メモリであって、

境界しきい値電圧に関してプログラムされるべきメモリセルアレイと、

グループのメモリセルにプログラミングパルスを加えるためのプログラミング回路と、

前記境界しきい値電圧のものから所定のマージン下の第1の基準しきい値電圧に関して前記グループのメモリセルをベリファイする第1の構成を有する感知回路と、

メモリコントローラであって、

前記メモリセルのうちの1つが前記第1の基準しきい値電圧に関してベリファイされるまで前記プログラミング回路と前記第1の構成を有する前記感知回路とを前記メモリコントローラが交互に制御するメモリコントローラと、

前記第1の基準しきい値電圧に関してベリファイされたメモリセルのその後のプログラミングを低速化するためのプログラミング遅延回路と、

前記境界しきい値電圧に関してベリファイされたメモリセルがそれ以上プログラムされることを妨げるためのプログラミング禁止回路と、を含み、

前記グループ中の全てのメモリセルが前記境界しきい値電圧に関してプログラムベリファイされるまで、前記プログラミング回路の操作と、前記境界しきい値電圧に関してのベリファイが次に行われる、前記第1の基準しきい値電圧に関して前記グループのメモリセルをベリファイする前記感知回路の操作とを前記メモリコントローラが交互に制御する不揮発性メモリ。 - 請求項15記載の不揮発性メモリにおいて、

関連するビット線により前記グループのメモリセルにアクセスすることをさらに含み、

プログラミングセットアップを変更することは、前記第1の基準しきい値電圧にベリファイされた前記メモリセルの前記プログラミングを低速化するためにビット線の電圧を高めることを含む不揮発性メモリ。 - 請求項15記載の不揮発性メモリにおいて、

関連するビット線により前記グループのメモリセルにアクセスすることをさらに含み、

前記プログラミング禁止回路は、妨げられないメモリセルのビット線が実質的にゼロ電圧である間に、妨げられるべき前記メモリセルと関連する前記ビット線を実質的に供給電圧に高めることを含む不揮発性メモリ。 - 請求項15記載の不揮発性メモリにおいて、

前記プログラミングパルスは、全てのパルスで単調に増大する不揮発性メモリ。 - 請求項15記載の不揮発性メモリにおいて、

前記グループのメモリセルは、フラッシュEEPROMの一部分である不揮発性メモリ。 - 請求項15記載の不揮発性メモリにおいて、

前記グループのメモリセルは、メモリカードにおいて具体化される不揮発性メモリ。 - 境界しきい値電圧に関してプログラムされるべきメモリセルアレイと、

グループのメモリセルにプログラミングパルスを加えるためのプログラミング回路と、

前記境界しきい値電圧のものから所定のマージン下の第1の基準しきい値電圧に関して前記グループのメモリセルをベリファイする第1の構成を有する感知回路と、

交互にプログラミングパルスを加え、前記グループのメモリセルについてのプログラムされた結果を並行してベリファイするメモリコントローラと、を含む不揮発性メモリであって、

前記ベリファイすることは、

前記境界しきい値電圧のものから所定のマージン下の第1の基準しきい値電圧に関しての第1のベリファイと、

前記第1の基準しきい値電圧に関してベリファイされた前記メモリセルのプログラミングを低速化するステップと、

前記境界しきい値電圧に関しての第2のベリファイと、

前記境界しきい値電圧に関してベリファイされた前記メモリセルがさらにプログラムされるのを妨げることと、をさらに含み、

前記グループのメモリセルのうちの少なくとも1つが前記第1の基準しきい値電圧に関してベリファイされるまで前記第2のベリファイは省かれる不揮発性メモリ。 - 請求項21記載の不揮発性メモリにおいて、

前記グループのメモリセルにアクセスするための1組の関連するビット線と、

前記メモリセルのその後のプログラミングを低速化するために、前記第1の基準しきい値電圧に関してベリファイされた前記メモリセルのビット線の電圧を高めるための供給電圧と、

をさらに含む不揮発性メモリ。 - 請求項21記載の不揮発性メモリにおいて、

前記グループのメモリセルにアクセスするための1組の関連するビット線とをさらに含み、

プログラミング禁止回路は、妨げられないメモリセルのビット線が実質的にゼロ電圧である間に、妨げられるべき前記メモリセルと関連する前記ビット線を実質的に供給電圧に高めることを含む不揮発性メモリ。 - 請求項21記載の不揮発性メモリにおいて、

前記プログラミングパルスは、全てのパルスで単調に増大する不揮発性メモリ。 - 請求項21記載の不揮発性メモリにおいて、

前記グループのメモリセルは、フラッシュEEPROMの一部分である不揮発性メモリ。 - 請求項21記載の不揮発性メモリにおいて、

前記グループのメモリセルは、メモリカードにおいて具体化される不揮発性メモリ。 - 請求項21記載の不揮発性メモリにおいて、

前記グループのメモリセルは、NAND構造で組織されたメモリアレイからのものである不揮発性メモリ。 - 請求項21記載の不揮発性メモリにおいて、

個々のメモリセルは、各々2つ以上のデータビットを格納する不揮発性メモリ。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/323,596 US7224614B1 (en) | 2005-12-29 | 2005-12-29 | Methods for improved program-verify operations in non-volatile memories |

| US11/323,577 US7310255B2 (en) | 2005-12-29 | 2005-12-29 | Non-volatile memory with improved program-verify operations |

| PCT/US2006/062627 WO2007076512A2 (en) | 2005-12-29 | 2006-12-27 | Methods and device for improved program-verify operations in non-volatile memories |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009522707A JP2009522707A (ja) | 2009-06-11 |

| JP2009522707A5 JP2009522707A5 (ja) | 2009-12-24 |

| JP4638544B2 true JP4638544B2 (ja) | 2011-02-23 |

Family

ID=38110643

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008548835A Expired - Fee Related JP4638544B2 (ja) | 2005-12-29 | 2006-12-27 | 不揮発性メモリにおける改善されたプログラムベリファイ操作のための方法および装置 |

Country Status (5)

| Country | Link |

|---|---|

| EP (1) | EP1966802A2 (ja) |

| JP (1) | JP4638544B2 (ja) |

| KR (1) | KR101317625B1 (ja) |

| TW (1) | TWI328231B (ja) |

| WO (1) | WO2007076512A2 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7606076B2 (en) * | 2007-04-05 | 2009-10-20 | Sandisk Corporation | Sensing in non-volatile storage using pulldown to regulated source voltage to remove system noise |

| ITRM20080114A1 (it) * | 2008-02-29 | 2009-09-01 | Micron Technology Inc | Compensazione della perdita di carica durante la programmazione di un dispositivo di memoria. |

| JP5172555B2 (ja) | 2008-09-08 | 2013-03-27 | 株式会社東芝 | 半導体記憶装置 |

| JP5193830B2 (ja) | 2008-12-03 | 2013-05-08 | 株式会社東芝 | 不揮発性半導体メモリ |

| KR101005117B1 (ko) * | 2009-01-23 | 2011-01-04 | 주식회사 하이닉스반도체 | 불휘발성 메모리 장치의 동작 방법 |

| JP5039079B2 (ja) * | 2009-03-23 | 2012-10-03 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| KR101554727B1 (ko) | 2009-07-13 | 2015-09-23 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 그것의 프로그램 방법 |

| US8223556B2 (en) | 2009-11-25 | 2012-07-17 | Sandisk Technologies Inc. | Programming non-volatile memory with a reduced number of verify operations |

| KR101633018B1 (ko) | 2009-12-28 | 2016-06-24 | 삼성전자주식회사 | 플래시 메모리 장치 및 그것의 프로그램 방법 |

| KR101656384B1 (ko) * | 2010-06-10 | 2016-09-12 | 삼성전자주식회사 | 불휘발성 메모리 장치의 데이터 기입 방법 |

| JP2011258289A (ja) * | 2010-06-10 | 2011-12-22 | Toshiba Corp | メモリセルの閾値検出方法 |

| JP5380506B2 (ja) * | 2011-09-22 | 2014-01-08 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2014053060A (ja) | 2012-09-07 | 2014-03-20 | Toshiba Corp | 半導体記憶装置及びその制御方法 |

| JP2014063551A (ja) | 2012-09-21 | 2014-04-10 | Toshiba Corp | 半導体記憶装置 |

| TWI514394B (zh) * | 2013-08-27 | 2015-12-21 | Toshiba Kk | Semiconductor memory device and its control method |

| JP7132443B2 (ja) | 2019-10-12 | 2022-09-06 | 長江存儲科技有限責任公司 | メモリデバイス、システム、及び関連するメモリデバイスをプログラミングする方法 |

| US11594293B2 (en) | 2020-07-10 | 2023-02-28 | Samsung Electronics Co., Ltd. | Memory device with conditional skip of verify operation during write and operating method thereof |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3679544B2 (ja) * | 1997-03-28 | 2005-08-03 | 三洋電機株式会社 | 不揮発性半導体メモリ装置 |

| JP3977799B2 (ja) * | 2003-12-09 | 2007-09-19 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US7136304B2 (en) * | 2002-10-29 | 2006-11-14 | Saifun Semiconductor Ltd | Method, system and circuit for programming a non-volatile memory array |

| US7139198B2 (en) * | 2004-01-27 | 2006-11-21 | Sandisk Corporation | Efficient verification for coarse/fine programming of non-volatile memory |

| US7068539B2 (en) * | 2004-01-27 | 2006-06-27 | Sandisk Corporation | Charge packet metering for coarse/fine programming of non-volatile memory |

| US7170793B2 (en) * | 2004-04-13 | 2007-01-30 | Sandisk Corporation | Programming inhibit for non-volatile memory |

| US7023733B2 (en) | 2004-05-05 | 2006-04-04 | Sandisk Corporation | Boosting to control programming of non-volatile memory |

| ITRM20050310A1 (it) * | 2005-06-15 | 2006-12-16 | Micron Technology Inc | Convergenza a programmazione selettiva lenta in un dispositivo di memoria flash. |

-

2006

- 2006-12-27 JP JP2008548835A patent/JP4638544B2/ja not_active Expired - Fee Related

- 2006-12-27 EP EP06848897A patent/EP1966802A2/en not_active Withdrawn

- 2006-12-27 WO PCT/US2006/062627 patent/WO2007076512A2/en active Application Filing

- 2006-12-27 KR KR1020087015676A patent/KR101317625B1/ko active IP Right Grant

- 2006-12-29 TW TW095150107A patent/TWI328231B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| WO2007076512A2 (en) | 2007-07-05 |

| WO2007076512A3 (en) | 2007-08-16 |

| JP2009522707A (ja) | 2009-06-11 |

| KR101317625B1 (ko) | 2013-10-10 |

| KR20080096645A (ko) | 2008-10-31 |

| TW200746151A (en) | 2007-12-16 |

| TWI328231B (en) | 2010-08-01 |

| EP1966802A2 (en) | 2008-09-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4638544B2 (ja) | 不揮発性メモリにおける改善されたプログラムベリファイ操作のための方法および装置 | |

| US7609556B2 (en) | Non-volatile memory with improved program-verify operations | |

| US7447081B2 (en) | Methods for improved program-verify operations in non-volatile memories | |

| KR101197478B1 (ko) | 파워 절약 독출 및 프로그램 검증 동작들을 구비한비휘발성 메모리 및 방법 | |

| KR101578812B1 (ko) | 가장 빠른 및/또는 가장 느린 프로그래밍 비트를 무시하여 프로그램 검증이 감소된 비휘발성 메모리와 방법 | |

| JP4988156B2 (ja) | 隣接フィールドエラーが低減された不揮発性メモリおよび方法 | |

| JP4898117B2 (ja) | ビットラインクロストークエラーが低減された不揮発性メモリおよび方法 | |

| KR101127413B1 (ko) | 개선된 부분 페이지 프로그램 능력을 가진 비휘발성 메모리및 제어 | |

| JP5266389B2 (ja) | ランプダウンプログラミングのための不揮発性メモリおよび方法 | |

| US8300459B2 (en) | Non-volatile memory and method for power-saving multi-pass sensing | |

| US7447094B2 (en) | Method for power-saving multi-pass sensing in non-volatile memory |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091105 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091105 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20091105 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20091209 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091215 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100315 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100323 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100415 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100422 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100513 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100520 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100609 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100907 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100917 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101102 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101125 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R370 | Written measure of declining of transfer procedure |

Free format text: JAPANESE INTERMEDIATE CODE: R370 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |