JP4635587B2 - 電力変換装置 - Google Patents

電力変換装置 Download PDFInfo

- Publication number

- JP4635587B2 JP4635587B2 JP2004353708A JP2004353708A JP4635587B2 JP 4635587 B2 JP4635587 B2 JP 4635587B2 JP 2004353708 A JP2004353708 A JP 2004353708A JP 2004353708 A JP2004353708 A JP 2004353708A JP 4635587 B2 JP4635587 B2 JP 4635587B2

- Authority

- JP

- Japan

- Prior art keywords

- current

- reverse

- gate

- voltage

- reverse blocking

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Power Conversion In General (AREA)

- Ac-Ac Conversion (AREA)

Description

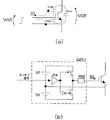

一般的な交流交流直接変換装置としては、例えば図9(b)のようなマトリックスコンバータ(またはサイクロコンバータ)がある。これは、電源Vsと負荷Mの間に、双方向スイッチSru,Srv,Srw,Ssu,Ssv,Ssw,Stu,Stv,Stwを図示のように接続することで、交流電源Vsから供給される交流電力を任意の交流に直接変換して、負荷Mへ供給するものである。

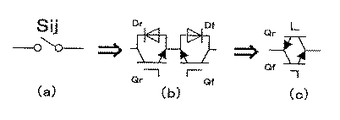

図9(b)で用いるスイッチとしては、双方向にオン・オフ制御できるデバイスが必要になる。ところで、電力変換装置に使用されるスイッチングデバイスは、サイリスタを始めGTOサイリスタ、トランジスタ、MOSFET(金属酸化膜電界効果トランジスタ)などから、IGBT(絶縁ゲートバイポーラトランジスタ)が最も主流となってきた。MOSFETを用いたスイッチ回路は、例えば特許文献1に開示されている。

一方、図9(b)のようなマトリックスコンバータを制御する場合の、双方向スイッチSijに対するオン・オフ制御指令については、特に次の2点に注意する必要がある。(1)電源Vsの短絡を防止するために、デッドタイムを設ける。

(2)負荷Mの開放を防止するために、負荷電流を転流させる重なり期間を設ける。

いま、電源VsのR,S,T相電圧を、図12(b)に示すVr,Vs,Vtで示す3相波形とすると、期間IIIの時刻t0においてそれぞれEr,Es,Etで示される電圧の関係は、Er>Es>Etである。

まず、図13(b)のようにQusにオン指令を与える。Er>Esであるから、Qusには逆方向に電圧が印加されており、負荷電流の状態は変化しない。

ついで、図13(d)のように、Qsuにオン指令を与える。先にQusがオンしているため、また、Qsuは負荷電流の方向と逆向きであるから、負荷電流の状態は変化しない。

さらに、図13(e)のように、Qruにオフ指令を与える。Qruには電圧が逆方向に印加されているため、負荷電流の状態は変化しない。

また、各逆阻止IGBTの電圧印加方向を検出する簡単な手段として、逆阻止IGBTの両端に抵抗による分圧回路を接続するものが考えられるが、外部回路が大きくなるだけでなく、例えば制御信号の伝達などに絶縁回路が必要になること、双方向に電圧を検出する必要があるなど、装置の大型化,コストアップにつながるという問題がある。

したがって、この発明の課題は、電力変換装置を構成する逆阻止IGBTの発生損失を低減し、電力変換装置の効率を向上させることにある。

互いに逆並列に接続される前記逆阻止型半導体素子のゲート端子に流れる電流を個別に検出する電流検出手段と、検出された電流値を比較する比較手段とを設けたことを特徴とする。

一般に、IGBTはゲート端子とエミッタ端子間に、任意に電圧を印加することでIGBTに流れる電流を制御することができる。通常は、制御装置からのオン・オフ信号に基き、ゲート駆動回路(GDU)と呼ばれる増幅器などによりIGBTのゲート電圧を制御する。

このような特徴と、逆阻止IGBTに対し逆方向に電圧が印加されているときに、ゲート端子にオン信号を与えれば漏れ電流が減少する特性を利用して、電力変換装置の高効率化を図る、と言うのがこの発明の課題と言える。

ここでは、逆阻止IGBTQru,Qurを互いに逆並列に接続して双方向スイッチSWrを構成する。各逆阻止IGBTのゲート−エミッタ間には、図示されない制御装置から入力されるオン・オフ信号にもとづき、ゲート電圧を出力するゲート駆動回路GDUf,GDUrが接続されている。また、Qru,Qurに流れるゲート電流を検出するために電流検出器CTf,CTrを挿入し、その出力信号を判定回路IGCに入力する。CTf,CTrの出力信号は積分回路I、サンプルホールド回路S/Hを介して比較器Cmpに入力される。

図2Aは図1の双方向スイッチSWrと同じ構成の双方向スイッチSWsを、SWrと直列に接続し、その直列接続回路を可変電源Er−sに接続するとともに、SWrとSWsとの接続点とEr−sの負極端子間に負荷Lを接続したものである。なお、SWsについてもゲート駆動回路GDUf,GDUrと判定回路IGCが設けられるが、ここでは図示を省略している。

r群スイッチがオンのときはSWrをオン、すなわちQruとQurをオンさせる。次に、r群スイッチからs群スイッチに切り換えるときに、電源短絡および負荷開放を防止するために、以下のようにスイッチを切り換える。

(1)時刻t0でQsuにオン信号を入力する。Qsuには逆電圧が印加されるため、QsuのVCEは減少しない。したがって、帰還容量によるQgの増加はない。

さらに、負荷Lは電流Io1によって蓄えられたエネルギーを放出するために、上記(1)でオン信号によりオンしているQsuを介して電流Io2が流れる(図2A参照)。

(3)時刻t2でQusにオン信号を入力する。(2)でQsuがオンしていることから、Qusの飽和電圧VCE(sat)分のみ逆電圧が印加されている。したがって、Qgの増加はない。

(4)時刻t3でQurにオフ信号を入力する。Qurには逆電圧が印加されているため、オンしない。したがって、Qgの増加はない。

また、図3Bのように、可変電源Er−sの代わりに交流電源Er−sを接続した場合も、QruとQurの動作が反転するだけなので、同様に検出可能である。さらに、図3Cのように、SWsがスイッチングする場合についても同様である。この考え方は3相交流電源の場合も同様に成立し、したがって図9(b)に示すマトリックスコンバータにも適用できることは明らかである。

図4Aのように、判定回路IGCの出力電圧VsはGDUfへ、またVsの反転信号はGDUrに入力される。各GDUf,GDUrに入力されたVsは、フォトカプラPCを介して、制御装置からのオン・オフ信号とともにオア回路ORに入力され、増幅器Asに入力される。

図4Bにおいて、Qruのゲート電流に、帰還電流の放電によりゲート電荷Qgが重畳する。よって、各ゲート電流の積分値はQ=∫idtであるから、

Qg(Qru)<Qg(Qur)

となる時刻t3以降に、サンプルホールド回路S/Hを介して比較器Cmpの出力Vsは負となる。したがって、判定回路IGCの出力電圧VsはGDUf,GDUrに互いに反転した信号が入力され、フォトカプラPCで絶縁された後、オア回路ORでオン・オフ信号とのオアがとられる。

図5(a)ではQru,Qurのゲート電流を検出する電流検出器CTf,CTrの出力信号を、互いに逆並列に接続されている逆阻止IGBTのゲート駆動回路GDUf,GDUrに入力する。ここで、電流検出器CTf,CTrは電気的に絶縁されているので、逆並列に接続されているゲート駆動回路GDUf,GDUrに入力することができる。

遷移する直前では、逆電圧のゲートをオンしなくなる。ただし、図5(b)の特性より、印加される逆電圧が小さいので、漏れ電流Ireakも小さく効率低下には寄与しない。なお、図5(a)では判定回路をゲート駆動回路に設けるようにしたが、電流検出器の出力は主回路とは絶縁されていることから、図6(a)のように制御装置に取り込み、その演算器の結果に応じてオン・オフを決定するようにしても良い。

Claims (4)

- コレクタ−エミッタ間に印加される順方向の電圧は、ゲート駆動回路からゲート端子に対して順電圧または逆電圧を与えることで制御し、コレクタ−エミッタ間に印加される逆方向の電圧は阻止する機能を有する逆阻止型半導体素子を、互いに逆並列に接続した双方向スイッチからなる電力変換装置において、

互いに逆並列に接続される前記逆阻止型半導体素子のゲート端子に流れる電流を個別に検出する電流検出手段と、検出された電流値を比較する比較手段とを設けたことを特徴とする電力変換装置。 - 前記比較手段による比較結果に応じて前記逆阻止型半導体素子のオン・オフを決定することを特徴とする請求項1に記載の電力変換装置。

- 前記電流検出手段の出力を、前記双方向スイッチを構成し逆阻止型半導体素子対応に設けられるゲート駆動回路にそれぞれ入力するとともに、前記比較手段をゲート駆動回路に設け、この比較手段にて前記検出された電流値を比較することを特徴とする請求項1または2に記載の電力変換装置。

- 前記電流検出手段の出力を全て制御装置に取り込み、制御装置による演算結果に応じて前記逆阻止型半導体素子のオン・オフを決定することを特徴とする請求項1に記載の電力変換装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004353708A JP4635587B2 (ja) | 2004-12-07 | 2004-12-07 | 電力変換装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004353708A JP4635587B2 (ja) | 2004-12-07 | 2004-12-07 | 電力変換装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006166582A JP2006166582A (ja) | 2006-06-22 |

| JP4635587B2 true JP4635587B2 (ja) | 2011-02-23 |

Family

ID=36667975

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004353708A Expired - Fee Related JP4635587B2 (ja) | 2004-12-07 | 2004-12-07 | 電力変換装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4635587B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104054253A (zh) * | 2012-03-30 | 2014-09-17 | 富士电机株式会社 | 电力变换装置 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101343189B1 (ko) | 2009-08-26 | 2013-12-19 | 다이킨 고교 가부시키가이샤 | 전력변환장치 및 그 제어방법 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02285971A (ja) * | 1989-04-24 | 1990-11-26 | Yaskawa Electric Mfg Co Ltd | インバータのゲート駆動回路 |

| JP3352840B2 (ja) * | 1994-03-14 | 2002-12-03 | 株式会社東芝 | 逆並列接続型双方向性半導体スイッチ |

| JP3864327B2 (ja) * | 1998-10-30 | 2006-12-27 | 株式会社安川電機 | Pwmサイクロコンバータ |

| JP3857462B2 (ja) * | 1999-03-19 | 2006-12-13 | 株式会社東芝 | 交流スイッチ回路 |

| JP4355873B2 (ja) * | 1999-12-10 | 2009-11-04 | 株式会社安川電機 | 電圧電流極性検出装置 |

| JP3960125B2 (ja) * | 2002-05-14 | 2007-08-15 | 富士電機ホールディングス株式会社 | 直接形電力変換器の転流方法 |

| JP4196765B2 (ja) * | 2002-11-29 | 2008-12-17 | 株式会社日立製作所 | マトリクスコンバータ |

-

2004

- 2004-12-07 JP JP2004353708A patent/JP4635587B2/ja not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104054253A (zh) * | 2012-03-30 | 2014-09-17 | 富士电机株式会社 | 电力变换装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006166582A (ja) | 2006-06-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8531212B2 (en) | Drive circuit for voltage-control type of semiconductor switching device | |

| US9197135B2 (en) | Bi-directional DC/DC converter with frequency control change-over | |

| JP6735900B2 (ja) | 半導体装置、および、電力変換システム | |

| US11101734B2 (en) | Multi-level buck converter capable of reducing component stress | |

| KR101297545B1 (ko) | 양방향 스위치회로 및 이를 구비한 전력변환장치 | |

| WO2023074636A1 (ja) | 電力変換装置及び制御方法 | |

| JP6032393B2 (ja) | 整流回路 | |

| JP6319045B2 (ja) | 半導体素子の駆動回路及び半導体素子の駆動システム | |

| US20100141304A1 (en) | Drive circuit for power element | |

| CN103329412A (zh) | 半导体开关元件的驱动设备 | |

| US9042140B2 (en) | Bridge-less step-up switching power supply device | |

| JP2010252451A (ja) | 電力変換装置のスイッチング素子駆動回路 | |

| WO2013171800A1 (ja) | 電力変換装置 | |

| JP2013141409A (ja) | 電力変換装置のスイッチング素子駆動回路 | |

| US12328064B2 (en) | Noise suppression method and apparatus for totem pole PFC circuit, and electronic device | |

| CN104578811B (zh) | 矩阵变换器 | |

| JP6758486B2 (ja) | 半導体素子の駆動装置および電力変換装置 | |

| JP4635587B2 (ja) | 電力変換装置 | |

| WO2015064206A1 (ja) | 半導体装置 | |

| JP7103139B2 (ja) | スイッチの駆動回路 | |

| JP2009195017A (ja) | 電圧駆動型半導体素子のゲート駆動装置 | |

| Chen et al. | Self-power emitter turn-off thyristor (SPETO) based circuit breaker for power distribution system | |

| JP6022883B2 (ja) | 電源装置 | |

| JP6622405B2 (ja) | インバータ駆動装置 | |

| US20230130625A1 (en) | Drive device, drive method, and power conversion device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101028 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101108 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4635587 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |