JP4635555B2 - スイッチング電源制御回路 - Google Patents

スイッチング電源制御回路 Download PDFInfo

- Publication number

- JP4635555B2 JP4635555B2 JP2004305356A JP2004305356A JP4635555B2 JP 4635555 B2 JP4635555 B2 JP 4635555B2 JP 2004305356 A JP2004305356 A JP 2004305356A JP 2004305356 A JP2004305356 A JP 2004305356A JP 4635555 B2 JP4635555 B2 JP 4635555B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- current

- control circuit

- circuit

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B70/00—Technologies for an efficient end-user side electric power management and consumption

- Y02B70/10—Technologies improving the efficiency by using switched-mode power supplies [SMPS], i.e. efficient power electronics conversion e.g. power factor correction or reduction of losses in power supplies or efficient standby modes

Landscapes

- Dc-Dc Converters (AREA)

Description

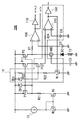

一般にスイッチング電源装置における制御回路100は、第1のバイアス回路(bias1)101、基準電圧回路(ref)102、定電流回路103と、ヒステリシスコンパレータ104によって構成される低電圧誤動作防止(UVLO:Under Voltage Lock Out)回路とを備えている。バイアス回路101、基準電圧回路102、定電流回路103、ヒステリシスコンパレータ104、ラッチ回路(latch)105は、いずれも例えば抵抗やゲート接地されたPチャネル(Pch)FETなどのインピーダンス素子(電圧供給素子)からなる起動抵抗回路120を介して、主電源端子VCCと接続されている。また、定電流回路103と補助電源端子VDDの接続点に接続された第2のバイアス回路(bias2)106、発振回路(osc)107、PWM(Pulse Width Modulation)コンパレータ(PWM)108、駆動回路(drv)109、および過電圧検出回路111はいずれも補助電源端子VDDと接続され、この補助電源端子VDDにICの外付け素子として接続された平滑用のコンデンサC3には、定電流回路103からの電流を積分することにより得られる電圧が供給されている。

ここでは、電源ラインと接地間には、定電流回路13とNchMOSFETN2のドレインとを接続した直列回路が接続され、かつNchMOSFETN2のゲートおよびドレインとNchMOSFETN3のゲートが接続され、NchMOSFETN2とN3のソースがともに接地されてカレントミラー回路(第1のカレントミラー回路)を構成している。また、PchMOSFETP1のゲートおよびドレインとPchMOSFETP2のゲートが接続され、ソースがともに電源ラインに接続されて、別のカレントミラー回路(第2のカレントミラー回路)を構成している。これらのカレントミラー回路は、PchMOSFETP1のドレインが抵抗R21を介してNchMOSFETN3のドレインと接続され、さらにゲート保護用のツェナーダイオードZD1は、そのカソードが電源ラインに接続され、アノードがPchMOSFETP1,P2のゲートに接続されている。また、PchMOSFETP2のドレイン端子は、補助電源端子VDDに接続されている。

したがって、W2/L2=N2、W3/L3=N3とすれば、定電流回路13のバイアス電流は、NchMOSFETN2のドレインからNchMOSFETN3に供給されるときに、カレントミラー回路のミラー比に応じて(N3/N2)倍の大きさとなって流入する。また、PchMOSFETP1,P2においてN2,N3と同様の関係が成り立つとすれば、さらに(P2/P1)倍の大きさのバイアス電流となって、PchMOSFETP2のドレインから補助電源端子VDDへ充電電流として供給されることになる。

(第1の実施形態)

図1は、この発明の第1の実施形態に係るスイッチング電源制御回路200の構成例を示す回路図である。ここには、スイッチング電源制御回路200の電流源回路とその周辺部制御回路の構成だけを示しており、その基本となる全体回路構成は図9に示した従来回路100のものと同じである。したがって、以下では同一部分についての説明を省略する。なお、この実施形態の発明は、特許請求の範囲の請求項4に記載した発明に対応するものである。

この電流制御回路14は、PchMOSFETP12、NchMOSFETN11、抵抗R22〜R24、ツェナーダイオードZD3、ヒステリシスコンパレータ141、インバータ142、および電源E4とから構成されている。ここで、PchMOSFETP12のソースは、第2の電流源であるPchMOSFETP11のドレインと接続され、PchMOSFETP12のドレインは補助電源端子VDDと接続されている。また、NchMOSFETN11のソースは接地され、そのドレインと電源ラインとの間には抵抗R22と抵抗R23との直列回路が接続され、さらに、PchMOSFETP12のゲートが抵抗R22とR23との接続点に接続されている。

Vchgon<Vchgoff<Vthoff<Vthon

のように設定している。

Vchgon<Vthoff<Vchgoff<Vthon

のように設定している。この場合には、スイッチング電源制御回路200の動作は同じであるが、電源投入直後での補助電源端子VDDの端子電圧の立ち上がり方が異なり、図2に示すものと比較したとき、図4に示す充電電圧の方が起動するまでの時間を一層短くすることができる。

Vchg<Vthoff<Vthon

となるが、その場合には、電源投入直後での補助電源端子VDDの端子電圧の立ち上がり方は、図2に示すようになる。このとき、補助電源端子VDDの端子電圧に対する充電電流の制御も上述したものと同様に行われる。

つぎに、この発明の第2の実施形態について説明する。図5は、第2の実施形態に係るスイッチング電源制御回路210の構成例を示す回路図である。なお、この実施形態の発明は、特許請求の範囲の請求項5に記載した発明に対応するものである。

電源投入直後では、補助電源端子VDDの電圧は、第1の制御回路部15によってPchMOSFETP11からの充電電流の供給を停止する閾値電圧Vchgoffには到達していない。そのため、第1の実施形態の図2に示したものと同様に、補助電源端子VDDには第1の電流源P2と第2の電流源P11とからそれぞれ充電電流が供給され、そこに接続されたコンデンサC3ヘの充電が開始される。コンデンサC3が充電されることで、補助電源端子VDDの端子電圧がヒステリシスコンパレータ141の上限の閾値電圧Vchgoffに達すると、第2の電流源P11からの電流供給が停止されるので、スイッチング電源装置が起動して補助電源端子VDDの端子電圧がスイッチング動作を開始する閾値電圧Vthonに達するまで、第1の電流源P2からの充電電流によってコンデンサC3が充電される。

なお、第2の実施形態では、2つの電流源P2,P11からそれぞれ流出する電流の大きさは、いずれもカレントミラー回路のミラー比、あるいは定電流回路13,161におけるバイアス電流の大きさに応じて決定されるものである。ここでは、第1の電流源P2と第2の電流源P11のそれぞれから供給される電流値の大小関係については、特に指定しない。しかし、この発明の主旨からすると、第1の電流源の電流値≦第2の電流源の電流値という関係に設定することが望ましい。

つぎに、この発明の第3の実施形態について説明する。図6は、第3の実施形態に係るスイッチング電源制御回路211の構成例を示す回路図である。

つぎに、この発明の第4の実施形態について説明する。図7は、第4の実施形態に係るスイッチング電源制御回路201の構成例を示す回路図である。

図12は、この発明の第5の実施形態に係るスイッチング電源制御回路300の構成例を示す回路図である。ここでも、スイッチング電源制御回路300の電流源回路とその周辺部制御回路の構成だけを示しており、その基本となる全体回路構成は図9に示した従来回路100と同じである。したがって、以下では同一部分についての説明を省略する。なお、この実施形態の発明は、特許請求の範囲の請求項8に記載した発明に対応するものである。

電源投入直後には、定電流回路13からのバイアス電流によりNchMOSFETN2,N3およびN18は導通状態にある。また、第1の制御回路部15では補助電源端子VDDの電圧は、電源E4からヒステリシスコンパレータ141に出力される基準電圧値より低い。そのため、ヒステリシスコンパレータ141からNchMOSFETN11に出力されるゲート信号がHレベルとなって、NchMOSFETN11とともにPchMOSFETP14は導通状態になる。そこで、制御回路300の第1のカレントミラー回路ではNchMOSFETN3とN18が並列接続された状態となり、定電流回路13からのバイアス電流が(N3+N18/N2)倍の大きさに増幅されて、第2のカレントミラー回路の一次側を構成するPchMOSFETP1に大きなバイアス電流を流すことができる。

0V<Vchgon<Vchgoff<Vthoff<Vthon

とし、あるいは

0V<Vchgon<Vthoff<Vchgoff<Vthon

とすれば、電源投入直後での補助電源端子VDDの端子電圧を前述した図2、あるいは図4に示すように制御できる。さらに、ヒステリシスコンパレータ141に代えて、制御電圧にヒステリシスが無いコンパレータを用いることで、

0V<Vchg<Vthoff<Vthon

のように設定してもよい。

つぎに、この発明の第6の実施形態について説明する。図13は、第6の実施形態に係るスイッチング電源制御回路310の構成例を示す回路図である。なお、この実施形態の発明は、特許請求の範囲の請求項9に記載した発明に対応するものである。

電源投入直後には、定電流回路13からのバイアス電流によりNchMOSFETN2およびN3は導通状態にある。また、補助電源端子VDDの電圧は、電源E4からヒステリシスコンパレータ141に出力される基準電圧値より低い。そのため、ヒステリシスコンパレータ141からNchMOSFETN19に出力されるゲート信号がHレベルとなって、NchMOSFETN19は導通状態になる。そこで、第2のカレントミラー回路では、PchMOSFETP1の一次側電流Ip1が、定電流回路13からのバイアス電流が第1のカレントミラー回路のミラー比(N2:N3)に応じた倍率で流れるだけでなく、電源ラインに対して抵抗R21と抵抗R26に依存した大きさの電流も流れる。したがって、制御回路310の補助電源端子VDDには電流源P2からIp1×(P2/P1)の大きさで充電電流が供給され、そこに接続されたコンデンサC3ヘの充電が開始される。

つぎに、この発明の第7の実施形態について説明する。図14は、第7の実施形態に係るスイッチング電源制御回路301の構成例を示す回路図である。

つぎに、この発明の第8の実施形態について説明する。図15は、第8の実施形態に係るスイッチング電源制御回路311の構成例を示す回路図である。

12 出力電圧検出回路

13 定電流回路

14 電流制御回路

15 第1の制御回路部

16〜19 第2の制御回路部

200,201,210,211,300,301,310,311 制御回路(スイッチング電源制御回路)

101 第1のバイアス回路(bias1)

102 基準電圧回路(ref)

103 定電流回路

104 ヒステリシスコンパレータ

105 ラッチ回路(latch)

106 第2のバイアス回路(bias2)

107 発振回路(osc)

108 PWMコンパレータ

109 駆動回路(drv)

110 インバータ

111 過電圧検出回路

141 ヒステリシスコンパレータ

142 インバータ

161 定電流回路

N1 スイッチングトランジスタ(パワーMOSFET)

T トランス

T1 1次巻線

T2 2次巻線

T3 3次巻線

PT フォトトランジスタ

LED 発光ダイオード

D1 ダイオードブリッジ

D2〜D4 整流ダイオード

C1〜C7 コンデンサ

R1〜R14,R21〜R25 抵抗

N2〜N20 NchMOSFET

P1〜P14 PchMOSFET

ZD1〜ZD4 ツェナーダイオード

Claims (15)

- 交流電源と接続されたコンバータトランスの一次回路側コイルに対して整流平滑出力を供給し、二次回路側コイルから出力される直流電圧を所望する一定値に制御するようにしたスイッチング電源装置のスイッチング電源制御回路において、

前記一次回路側の補助コイルによって充電可能なコンデンサに接続された補助電源端子と、

前記交流電源の投入後の起動期間に前記補助電源端子を介して前記コンデンサに充電電流を供給する電流源と、

前記補助電源端子の電圧信号を検知して、前記電流源から前記コンデンサに供給される充電電流の大きさを制御する電流制御回路と、

を備え、

前記電流源は、前記交流電源の投入時に前記補助電源端子を介して独立にそれぞれ前記コンデンサに充電電流を供給する第1、第2の電流源によって構成され、

前記電流制御回路は、前記補助電源端子の電圧信号が所定の閾値電圧を超えたとき、前記第2の電流源から前記コンデンサへの充電電流を停止制御し、

前記電流制御回路では、前記起動期間に前記電流源から前記コンデンサに供給される充電電流を、前記スイッチング電源装置が間欠動作するときの充電電流より大きな電流値となるように制御したことを特徴とするスイッチング電源制御回路。 - 前記第2の電流源は、1対のトランジスタからなる第1のカレントミラー回路と、前記第1のカレントミラー回路の後段に縦続接続され、前記第1のカレントミラー回路とは別の1対のトランジスタからなる第2のカレントミラー回路とによって構成したことを特徴とする請求項1記載のスイッチング電源制御回路。

- 前記電流制御回路では、前記補助電源端子の電圧信号を検知したときに前記第2のカレントミラー回路のミラー比を変更し、前記コンデンサへの充電電流の大きさを制御するようにしたことを特徴とする請求項2記載のスイッチング電源制御回路。

- 前記第2の電流源は、前記交流電源の投入時に供給される整流平滑出力によって前記第1の電流源とは独立して駆動され、前記補助電源端子の電圧信号が前記所定の閾値電圧を超えたとき、前記電流制御回路によって前記コンデンサへの充電電流を停止制御するようにしたことを特徴とする請求項1記載のスイッチング電源制御回路。

- 前記電流制御回路は、前記補助電源端子と前記第2の電流源との間を接続するスイッチ回路を備え、前記補助電源端子の電圧信号に応じて前記スイッチ回路をオンオフ制御し、前記第2の電流源から前記コンデンサへの充電電流を停止制御することを特徴とする請求項1記載のスイッチング電源制御回路。

- 前記電流制御回路は、さらに、前記補助電源端子の電圧に対して所定のヒステリシスを有する閾値電圧を基準値と比較する比較回路を備えたことを特徴とする請求項5記載のスイッチング電源制御回路。

- 前記電流制御回路は、前記第1のカレントミラー回路のミラー比を変更することによって、前記第2のカレントミラー回路から前記コンデンサに供給される充電電流の大きさを制御するようにしたことを特徴とする請求項2記載のスイッチング電源制御回路。

- 前記電流制御回路は、前記第2のカレントミラー回路の一次側トランジスタと接続され、前記第1のカレントミラー回路の二次側トランジスタと並列接続された電流回路を備えたことを特徴とする請求項2記載のスイッチング電源制御回路。

- 前記交流電源の電源電圧が低下した時にスイッチング動作を停止する高低2通りの閾値電圧をもつヒステリシス低電圧誤動作防止回路を備え、

前記電流制御回路は、前記補助電源端子の電圧信号が前記閾値電圧の範囲を逸脱したとき、前記電流源から前記コンデンサに供給される充電電流を停止制御することを特徴とする請求項1ないし8のいずれかに記載のスイッチング電源制御回路。 - 前記補助電源端子の電圧に対する前記ヒステリシス低電圧誤動作防止回路の高低それぞれの閾値電圧をVthon,Vthoffとし、前記電流制御回路の閾値電圧をVchgとした場合に、

これらの電位関係を

0V<Vchg<Vthoff<Vthon

に設定することを特徴とする請求項9記載のスイッチング電源制御回路。 - 前記電流制御回路は、前記補助電源端子の電圧に対して所定のヒステリシスを有する閾値電圧を基準値と比較する比較回路を備えたことを特徴とする請求項9記載のスイッチング電源制御回路。

- 前記補助電源端子の電圧に対する前記ヒステリシス低電圧誤動作防止回路の高低それぞれの閾値電圧をVthon,Vthoffとし、前記ヒステリシスを有する閾値電圧の上下限値をそれぞれVchgoff,Vchgonとした場合に、これらの電位関係を

0V<Vchgon<Vthoff<Vchgoff<Vthon

に設定することを特徴とする請求項11記載のスイッチング電源制御回路。 - 前記補助電源端子の電圧に対する前記ヒステリシス低電圧誤動作防止回路の高低それぞれの閾値電圧をVthon,Vthoffとし、前記ヒステリシスを有する閾値電圧の上下限値をそれぞれVchgoff,Vchgonとした場合に、これらの電位関係を

0V<Vchgon<Vchgoff<Vthoff<Vthon

に設定することを特徴とする請求項11記載のスイッチング電源制御回路。 - 前記交流電源の投入後に、前記補助電源端子に過電圧が供給され、あるいは過熱状態が検知された場合に、前記電流源から前記コンデンサに供給される充電電流を停止制御することを特徴とする請求項1ないし13のいずれかに記載のスイッチング電源制御回路。

- 前記電流源および前記電流制御回路は、スイッチング電源制御用の集積回路とは独立の回路装置として構成されていることを特徴とする請求項1ないし14のいずれかに記載のスイッチング電源制御回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004305356A JP4635555B2 (ja) | 2003-11-27 | 2004-10-20 | スイッチング電源制御回路 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003397629 | 2003-11-27 | ||

| JP2004305356A JP4635555B2 (ja) | 2003-11-27 | 2004-10-20 | スイッチング電源制御回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005185087A JP2005185087A (ja) | 2005-07-07 |

| JP4635555B2 true JP4635555B2 (ja) | 2011-02-23 |

Family

ID=34797308

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004305356A Expired - Fee Related JP4635555B2 (ja) | 2003-11-27 | 2004-10-20 | スイッチング電源制御回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4635555B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5385014B2 (ja) * | 2009-06-04 | 2014-01-08 | 新電元工業株式会社 | スイッチング電源 |

| CN110752836B (zh) * | 2019-09-11 | 2023-08-18 | 上海智浦欣微电子有限公司 | 信号控制电路及驱动信号产生电路 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07327369A (ja) * | 1994-05-31 | 1995-12-12 | Nec Home Electron Ltd | 電源装置 |

| JP3578124B2 (ja) * | 2001-08-31 | 2004-10-20 | ソニー株式会社 | スイッチング電源装置 |

-

2004

- 2004-10-20 JP JP2004305356A patent/JP4635555B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005185087A (ja) | 2005-07-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10924003B2 (en) | Switching power supply | |

| CN104836421B (zh) | 一种开关电源的供电电路和供电方法 | |

| JP4481879B2 (ja) | スイッチング電源装置 | |

| JP4687958B2 (ja) | Dc−dcコンバータ | |

| US20050078492A1 (en) | Switching power supply | |

| CN110932553B (zh) | 电源控制设备 | |

| US6982889B2 (en) | DC/AC converter and its controller IC | |

| WO2016117270A1 (ja) | 電源制御用半導体装置 | |

| JP7775647B2 (ja) | 集積回路及び電源回路 | |

| WO2006115473A1 (en) | Power supply control method and structure therefor | |

| JP7626826B2 (ja) | エネルギーハーベスティング回路のスタータ回路 | |

| US12362653B2 (en) | Switching control circuit, power supply circuit | |

| US6912140B2 (en) | Switching power supply | |

| JPH11168883A (ja) | Dc/dcコンバータ | |

| US7492620B2 (en) | DC-AC converter and controller IC thereof | |

| KR100697805B1 (ko) | 의사 공진 방식 스위칭 전원 장치 및 이를 이용한 의사공진 방식 스위칭 전원 회로 | |

| KR101011083B1 (ko) | 초기 바이어스 전원 공급부를 갖는 스위칭 모드 파워 서플라이 | |

| JP4635555B2 (ja) | スイッチング電源制御回路 | |

| CN114024434A (zh) | 一种用于电源管理芯片的软启动及漏电防护电路 | |

| JP7199913B2 (ja) | スイッチング電源 | |

| JP3794475B2 (ja) | スイッチング電源回路 | |

| JP2004222472A (ja) | スイッチング電源制御回路 | |

| JP2001112251A (ja) | スイッチング電源装置 | |

| JP4697412B2 (ja) | スイッチング電源装置 | |

| JP2000102248A (ja) | 多出力スイッチング電源装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070914 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20091112 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20091112 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20091112 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100610 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100615 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100802 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101108 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4635555 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |