JP4635286B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4635286B2 JP4635286B2 JP33395899A JP33395899A JP4635286B2 JP 4635286 B2 JP4635286 B2 JP 4635286B2 JP 33395899 A JP33395899 A JP 33395899A JP 33395899 A JP33395899 A JP 33395899A JP 4635286 B2 JP4635286 B2 JP 4635286B2

- Authority

- JP

- Japan

- Prior art keywords

- type impurity

- impurity diffusion

- diffusion region

- type

- gate electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Electrodes Of Semiconductors (AREA)

Description

【発明の属する技術分野】

本発明は、ゲート電極を備えた半導体装置に関する。

【0002】

【従来の技術】

近年、MOSFET(Metal Oxide SemiconductorField Effect Transistor)やIGBT(Insulated Gate Bipolar Transistor)等のゲート電極を備えた半導体装置は、高速スイッチング特性を備えているため様々な分野に広く用いられている。特にIGBTは、MOSFETの高速スイッチング特性とバイポーラトランジスタの高出力特性を兼ね備えており、パワーエレクトロニクスの分野で多く用いられている。

【0003】

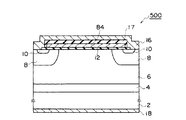

ゲート電極を備えた半導体装置として、図8に従来のIGBT500の断面図が示されている。

【0004】

p型高濃度半導体基板2上にn型高濃度ドリフト層4が選択的に形成されている。このn型高濃度ドリフト層4には、n型低濃度ドリフト領域6が選択的に形成されている。このn型低濃度ドリフト領域6表面には、p型ボディ領域8が形成されている。このp型ボディ領域8の表面にはn型エミッタ領域10が形成されている。そして、ゲート絶縁膜12を介して、n型低濃度ドリフト領域6上及びp型ボディ領域8上にゲート電極84が形成されている。一方、n型エミッタ領域10に接触するようにエミッタ電極16が形成され、p型高濃度半導体基板2の裏面側には、コレクタ電極18が形成される。

【0005】

このIGBT500の動作は原理は以下の通りである。IGBT500を導通させるとき(導通時)には、ゲート電極84にエミッタ電極16に対して正の電圧(正のバイアス電圧)が印加される。ゲート電極84に正のバイアス電圧が印加されると、p型ボディ領域8の表面にn型チャネルが形成され、n型エミッタ領域10からn型低濃度ドリフト領域6及びn型高濃度ドリフト層4へ多数キャリアが注入される。n型低濃度ドリフト領域6及びn型高濃度ドリフト層4へ多数キャリアが注入されると、p型高濃度半導体基板2側から、少数キャリアがn型高濃度ドリフト層4及びn型低濃度ドリフト領域6へ注入され、エミッタ電極16とコレクタ電極18との間に電流が流れる。

【0006】

一方、IGBT500を導通させないとき(非導通時)には、ゲート電極84にエミッタ電極16に対して負の電圧(負のバイアス電圧)が印加される。これにより、前述したn型チャネルが消失し、エミッタ電極16とコレクタ電極18との間に電流が流れなくなる。

【0007】

IGBT500の導通時及び非導通時のエネルギーバンド図が、図9に示されている。図9(a)及び図9(b)には、p型ボディ領域8表面、ゲート絶縁膜12及びゲート電極84のエネルギーバンド図が示されている。また、図9(c)及び(d)には、n型低濃度ドリフト領域6表面及びゲート電極84のエネルギーバンド図が示されている。

【0008】

図9において、qФMはゲート電極84の材料の仕事関数、EFはフェルミ準位、VACは真空準位、Ecは伝導帯下端、Evは価電子帯上端を示している。

【0009】

非導通時(ゲートバイアス電圧Vg=0)では、図9(a)に示されているように、ゲート絶縁膜を介して、ゲート電極とp型ボディ領域とのフェルミ準位が等しくなるように平衡が保たれている。

【0010】

ところが、導通時(Vg>0)となると、図9(b)に示されているように、ゲート電極側のフェルミ準位が下がり、p型ボディ領域側では、p型ボディ領域とゲート絶縁膜との界面で伝導体下端が曲がり、少数キャリア(電子)が蓄積される。

【0011】

非導通時(ゲートバイアス電圧Vg=0)では、図9(c)に示されているように、絶縁膜を介して、ゲート電極とn型低濃度ドリフト領域とのフェルミ準位が等しくなるように平衡が保たれている。

【0012】

一方、導通時(Vg>0)になると、図9(d)に示されているように、ゲート電極側のフェルミ準位が下がり、n型低濃度ドリフト領域側では、n型低濃度ドリフト領域とゲート絶縁膜との界面で伝導体下端が曲がり、多数キャリア(電子)が蓄積される。

【0013】

【発明が解決しようとする課題】

ところで、IGBT500の導通時には、ゲート電極84に正のバイアス電圧が印加されるため、p型ボディ領域8とn型低濃度ドリフト領域6との間の空乏層が濃度の低いn型低濃度ドリフト領域6側へ延びる。この空乏層のために、n型エミッタ領域10側から注入される多数キャリア(電子)が流れる電流路が狭くなり、n型低濃度ドリフト領域6及びn型高濃度ドリフト層4における抵抗(ジャンクションFET抵抗、JFET抵抗)成分が大きくなってしまう。

【0014】

また、JFET抵抗を減らすために、P型ボディ領域8の拡散深さを浅くするとIGBT500がラッチアップを起こしやすくなり、破壊耐量が低下するという問題があった。

【0015】

本発明は、上記課題を解決するためになされたものであり、破壊耐量が大きく、低損失な半導体装置を提供することを目的とする。

【0016】

【課題を解決するための手段】

本発明は、半導体基板内に形成された第1のn型不純物拡散領域と、前記第1の第1導電型不純物拡散領域表面に形成されたp型不純物拡散領域と、前記第2導電型不純物拡散領域表面に形成された第2のn型不純物拡散領域と、ゲート絶縁膜を介して、少なくとも前記第1のn型不純物拡散領域と前記p型不純物拡散領域に隣接するゲート電極と、前記第2のn型不純物拡散領域からp型不純物拡散領域を介して前記第1のn型不純物拡散領域に達するように形成された溝と、を備え、前記ゲート電極は、前記ゲート絶縁膜を介して前記溝内壁に形成されており、前記ゲート電極に電圧を印加したときに、前記第1のn型不純物拡散領域のゲート絶縁膜との界面での伝導体下端の曲がりが、前記p型不純物拡散領域の伝導体下端の曲がりよりも大きくなるように、前記ゲート電極の前記第1のn型不純物拡散領域に隣接する第1部位の材料が有する第1部位仕事関数を、前記ゲート電極の前記p型不純物拡散領域に隣接する第2部位の材料が有する第2部位仕事関数よりも小さくし、且つ前記第1部位をn型不純物ポリシリコンで、前記第2部位をp型不純物ポリシリコンでそれぞれ構成することを特徴とする。

また、本発明の別の形態は、半導体基板内に形成された第1のp型不純物拡散領域と、前記第1の第1導電型不純物拡散領域表面に形成されたn型不純物拡散領域と、前記第2導電型不純物拡散領域表面に形成された第2のp型不純物拡散領域と、ゲート絶縁膜を介して、少なくとも前記第1のp型不純物拡散領域と前記p型不純物拡散領域に隣接するゲート電極と、前記第2のp型不純物拡散領域からn型不純物拡散領域を介して前記第1のp型不純物拡散領域に達するように形成された溝と、を備え、前記ゲート電極は、前記ゲート絶縁膜を介して前記溝内壁に形成されており、前記ゲート電極に電圧を印加したときに、前記第1のp型不純物拡散領域のゲート絶縁膜との界面での伝導体下端の曲がりが、前記n型不純物拡散領域の伝導体下端の曲がりよりも大きくなるように、前記ゲート電極の前記第1のp型不純物拡散領域に隣接する第1部位の材料が有する第1部位仕事関数を、前記ゲート電極の前記n型不純物拡散領域に隣接する第2部位の材料が有する第2部位仕事関数よりも大きくし、且つ前記第1部位をp型不純物ポリシリコンで、前記第2部位をn型不純物ポリシリコンでそれぞれ構成することを特徴とする。

【0017】

上記構成によれば、半導体装置の導通時に、第1の第1導電型(例えば、n型)不純物拡散領域のゲート電極に隣接する部位に蓄積される多数キャリア量が多くなる。そのため、第1の第1導電型不純物拡散領域と第2導電型(例えば、p型)不純物拡散領域との接合部の空乏層の第1の第1導電型不純物拡散領域側への延びが抑えられ、JFET抵抗を減らすことができる。また、第1の第1導電型不純物拡散領域のゲート電極に隣接する部位に蓄積される多数キャリア量が多くなり、第1の第1導電型不純物拡散領域に注入される少数キャリア量が増えるため、第1の第1導電型不純物拡散領域自体の抵抗を減らすことができる。したがって、低損失な半導体装置を提供することが可能である。

【0021】

【発明の実施の形態】

以下、本発明の実施の形態(以下実施形態という)を、図面に従って説明する。尚、各図を通じて、同じ部材には同一の符号が付されている。

【0022】

図1には、本実施形態の半導体装置であるIGBT100が示されている。図1(a)には、IGBT100の平面図が示されており、図1(b)には、図1(a)におけるAA線での断面図が示されている。p型高濃度半導体基板2上にn型高濃度ドリフト層4が選択的に形成されている。このn型高濃度ドリフト層4の表面には、n型低濃度ドリフト領域6が選択的に形成されている。このn型低濃度ドリフト領域6表面には、p型ボディ領域8が形成されている。このp型ボディ領域8の表面にはn型エミッタ領域10が形成されている。そして、ゲート絶縁膜12を介して、少なくともn型低濃度ドリフト領域6及びp型ボディ領域8に隣接するようにポリシリコンを材料とするゲート電極14が形成されている。一方、n型エミッタ領域10に接触するようにエミッタ電極16が形成される。エミッタ電極16は、層間絶縁膜17によって、ゲート電極14と電気的に絶縁されている。p型高濃度半導体基板2の裏面側には、コレクタ電極18が形成される。ゲート電極14は、コンタクト20を介してゲート用アルミ電極24に接続されている。また、エミッタ電極16は、コンタクト22を介してエミッタ用アルミ電極26に接続されている。

【0023】

ゲート電極14は、n型低濃度ドリフト領域6に隣接する第1部位30と、p型ボディ領域8に隣接する第2部位32とを備えている。この第1部位30と第2部位32はポリシリコンを材料としているが、各々不純物濃度が異なっているので、各々仕事関数も異なっている。

【0024】

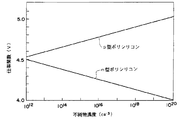

図2には、ポリシリコン中の不純物濃度と仕事関数との関係が示されている。

横軸が不純物濃度を示し、縦軸が仕事関数を示している。ポリシリコン中にヒ素やリン等の不純物を注入し、ポリシリコンをn型にした場合(図2中のn型ポリシリコンの場合)、ポリシリコン中の不純物濃度を高くすると仕事関数が小さくなる。ポリシリコン中にホウ素等の不純物を注入し、ポリシリコンをp型にした場合(図2中のp型ポリシリコンの場合)、ポリシリコン中の不純物濃度を高くすると仕事関数が小さくなる。

【0025】

図2に示された関係を利用して、ゲート電極14の第1部位30のポリシリコン中の不純物濃度と、第2部位32のポリシリコン中の不純物濃度とを、異ならせることによって、第1部位30のポリシリコンと第2部位32のポリシリコンとの仕事関数を変えることができる。

【0026】

本実施形態では、ゲート電極14の第1部位30のポリシリコンのみに不純物としてヒ素を注入し、第1部位30のポリシリコンをn型の導電型にし、第1部位30の仕事関数を第2部位32の仕事関数より小さくしている。尚、第2部位32に不純物としてホウ素を注入することで、第2部位の仕事関数をより大きくし、第1部位30と第2部位32の仕事関数差を大きくしてもよい。

【0027】

このように、第1部位30の仕事関数を第2部位32の仕事関数より小さくすることで、IGBT100の導通時にn型低濃度ドリフト領域6に蓄積される多数キャリア(電子)の量を増やすことができる。

【0028】

次に、IGBT100の導通時のエネルギーバンドの様子を説明することで、n型低濃度ドリフト領域6に蓄積される多数キャリア(電子)の量が増える原理を説明する。

【0029】

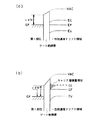

図3には、p型ボディ領域8表面及びゲート電極14の第2部位32でのエネルギーバンド図が示されている。図3において、qФMはゲート電極14の第2部位32の材料の仕事関数、EFはフェルミ準位、VACは真空準位、Ecは伝導帯下端、Evは価電子帯上端を示している。

【0030】

非導通時(ゲートバイアス電圧Vg=0)では、図3(a)に示されているように、ゲート絶縁膜を介して、ゲート電極の第2部位とp型ボディ領域とのフェルミ準位が等しくなるように平衡が保たれている。

【0031】

ところが、導通時(Vg>0)となると、図3(b)に示されているように、ゲート電極側のフェルミ準位が下がり、p型ボディ領域側では、p型ボディ領域とゲート絶縁膜との界面で伝導体下端Ecが曲がり、電子が蓄積される。

【0032】

一方、図4には、本実施形態のゲート電極の第1部位の材料の仕事関数が第2部位の材料の仕事関数より小さい場合のn型低濃度ドリフト領域6表面及びゲート電極の第1部位のエネルギーバンド図が示されている。ここで、qФ’Mを第1部位30の材料の仕事関数とする。

【0033】

非導通状態(ゲートバイアス電圧Vg=0)では、図4(a)に示されているように、ゲート絶縁膜を介して、ゲート電極とn型低濃度ドリフト領域とのフェルミ準位が等しくなるように平衡が保たれている。しかし、ゲート電極の第1部位の材料の仕事関数が第2部位の材料の仕事関数と同じ場合(図9(c))と比較すると、伝導帯下端Ecが大きく曲がっている。

【0034】

一方、導通状態(Vg>0)となると、図4(b)に示されているように、ゲート電極側のフェルミ準位が上がり、n型低濃度ドリフト領域側では、n型低濃度ドリフト領域とゲート絶縁膜との界面で伝導帯下端Ecが曲がり、多数キャリア(電子)が蓄積される。この伝導帯下端Ecの曲がりは、ゲート電極の第1部位の材料の仕事関数が第2部位の材料の仕事関数と同じ場合(図9(d))と比較すると大きくなり、より多くのキャリア(電子)を蓄積することができる。

【0035】

このように、本実施形態においては、ゲート電極14の第1部位30の材料の仕事関数と、ゲート電極14の第2部位32の材料の仕事関数とが異なっており、第1部位30の材料の仕事関数のほうが、第2部位32の仕事関数より小さい。したがって、n型低濃度ドリフト領域6表面のエネルギーバンドの曲がりが大きくなり、n型低濃度ドリフト領域6表面に蓄積される多数キャリア(電子)の量を増やすことができる。したがって、p型ボディ領域8とn型低濃度ドリフト領域6との接合部の空乏層がn型低濃度ドリフト領域6側に延びるのを抑えることができ、JFET抵抗を下げることができる。また、表面に多数キャリア(電子)が多くなるので、コレクタ電極から少数キャリア(正孔)が多く注入され、見かけ上、n型低濃度ドリフト領域6の抵抗を下げることができる。

【0036】

図5には、他の実施形態の半導体装置として、溝(トレンチ)を備えたIGBT200が示されている。図5(a)には、IGBT200の平面図が示されており、図5(b)には、図5(a)におけるBB線での断面図が示されている。このIGBT200は、n型エミッタ領域10からp型ボディ領域8を介してn型低濃度ドリフト領域6へ達するトレンチ50を備えている。このトレンチ50内に、ゲート電極14が形成されている。このゲート電極14は、n型低濃度ドリフト領域6に隣接する第1部位30と、p型ボディ領域8に隣接する第2部位32とを備えている。この第1部位30と第2部位32はポリシリコンを材料としているが、各々不純物濃度が異なっているため、各々仕事関数が異なっている。このように、ゲート電極14の第1部位30のポリシリコン中の不純物濃度と第2部位32のポリシリコン中の不純物濃度とを異ならせることによって、第1部位30のポリシリコンと第2部位32のポリシリコンとの仕事関数を変えることができる。このとき、第1部位30の材料の仕事関数を第2部位32の材料の仕事関数より小さくすると、導通時にn型低濃度ドリフト領域6に蓄積される多数キャリア(電子)の量を増やし、n型低濃度ドリフト領域6の抵抗を減らすことができる。

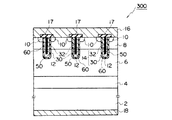

【0037】

前述した実施形態においては、ゲート電極14内部にポリシリコンより抵抗値が小さい別の金属を材料とし、抵抗率が低い異種金属層をCVD法等を用いて形成するのも好適である。図6には、ゲート電極14内に異種金属層60を備えたIGBT300の断面図が示されている。異種金属層60は抵抗値が小さいため、ゲート入力抵抗を下げることができる。

【0038】

前述した実施形態において、各領域においてn型をp型の導電型に、p型をn型の導電型にしてもよい。図7には、図1において導電型を逆にしたIGBT400の断面図が示されている。n型高濃度半導体基板102上にp型高濃度ドリフト層104が選択的に形成されている。このp型高濃度ドリフト層104には、p型低濃度ドリフト領域106が選択的に形成されている。このp型低濃度ドリフト領域106の表面には、n型ボディ領域108が形成されている。このn型ボディ領域108の表面にはp型エミッタ領域110が形成されている。そして、ゲート絶縁膜112を介して、p型低濃度ドリフト領域106及びn型ボディ領域108に隣接するようにポリシリコンを材料とするゲート電極114が形成されている。一方、p型エミッタ領域110に接触するようにエミッタ電極116が形成され、n型高濃度半導体基板102の裏面側には、コレクタ電極118が形成される。

【0039】

ゲート電極114は、p型低濃度ドリフト領域106に隣接する第1部位130と、n型ボディ領域108に隣接する第2部位132とを備えている。この第1部位130及び第2部位132はポリシリコンを材料としているが、各々不純物濃度が異なっており、各々仕事関数も異なっている。このとき、第1部位130の仕事関数を第2部位132の仕事関数より大きく設定することが好適である。

【0040】

ゲート電極114の第1部位130の材料の仕事関数よりゲート電極114の第2部位132の材料の仕事関数が大きいため、p型低濃度ドリフト領域106の伝導体下端が大きく曲がり、多数キャリア(正孔)を多く蓄積することができる。そのため、n型ボディ領域108とp型低濃度ドリフト領域106との接合部の空乏層がp型低濃度ドリフト領域106側に延びるのを抑えることができ、JFET抵抗を下げることができる。また、表面に多数キャリア(正孔)が多くなるので、コレクタ電極118から少数キャリア(電子)が多く注入され、見かけ上、p型低濃度ドリフト領域106の抵抗を下げることができる。

【0041】

各実施形態では、半導体装置としてIGBTを例示したが、IGBTに限定したものではなく、MOSFET等のゲート電極と2つの同一導電型の不純物拡散領域と、その2つの領域に挟まれた1つの他の導電型の不純物拡散領域とを備えた電解効果トランジスタ等に適用することが可能である。

【0042】

【発明の効果】

本発明においては、第1の第1導電型不純物拡散領域にゲート絶縁膜を介して隣接するゲート電極の第1部位と、第2導電型不純物拡散領域にゲート絶縁膜を介して隣接するゲート電極の第2部位との仕事関数を適宜設定することができる。したがって、半導体装置の導通時に、第1の第1導電型不純物拡散領域のゲート電極の隣接する部位に蓄積される多数キャリア量が多くなる。そのため、第1の第1導電型不純物拡散領域と第2導電型不純物拡散領域との接合部の空乏層の第1の第1導電型不純物拡散領域側への延びが抑えられ、JFET抵抗を減らすことができる。また、第1の第1導電型不純物拡散領域のゲート電極の隣接する部位に蓄積される多数キャリア量が多くなり、第1の第1導電型不純物拡散領域に注入される少数キャリア量が増えるため、第1の第1導電型不純物拡散領域自体の抵抗を減らすことができる。したがって、低損失な半導体装置を提供することが可能である。

【図面の簡単な説明】

【図1】 本実施形態のIGBTが示された図である。

【図2】 ポリシリコンの不純物濃度と仕事関数との関係が現れた図である。

【図3】 本実施形態のIGBTのp型ボディ領域表面とゲート電極14の第2部位におけるエネルギーバンドが示された図である。

【図4】 本実施形態のIGBTのn型ボディ領域表面とゲート電極14の第2部位におけるエネルギーバンドが示された図である。

【図5】 他の実施形態のIGBTが示された図である。

【図6】 他の実施形態のIGBTが示された図である。

【図7】 導電型異なった他の実施形態のIGBTが示された図である。

【図8】 従来のIGBTが示された図である。

【図9】 従来のIGBTのp型ボディ領域表面、n型低濃度ドリフト領域表面及びゲート電極におけるエネルギーバンドが示された図である。

【符号の説明】

2 p型高濃度半導体基板、6 n型低濃度ドリフト領域、8 p型ボディ領域、12,112 ゲート絶縁膜、14,84,114 ゲート電極、30,130 第1部位、32,132 第2部位、100,200,300,400 500 IGBT、102 n型高濃度半導体基板、106 p型低濃度ドリフト領域、108 n型ボディ領域。

Claims (2)

- 半導体基板内に形成された第1のn型不純物拡散領域と、

前記第1のn型不純物拡散領域表面に形成されたp型不純物拡散領域と、

前記p型不純物拡散領域表面に形成された第2のn型不純物拡散領域と、

ゲート絶縁膜を介して、少なくとも前記第1のn型不純物拡散領域と前記p型不純物拡散領域に隣接するゲート電極と、

前記第2のn型不純物拡散領域からp型不純物拡散領域を介して前記第1のn型不純物拡散領域に達するように形成された溝と、

を備え、

前記ゲート電極は、前記ゲート絶縁膜を介して前記溝内壁に形成されており、

前記ゲート電極に電圧を印加したときに、前記第1のn型不純物拡散領域のゲート絶縁膜との界面での伝導体下端の曲がりが、前記p型不純物拡散領域の伝導体下端の曲がりよりも大きくなるように、前記ゲート電極の前記第1のn型不純物拡散領域に隣接する第1部位の材料が有する第1部位仕事関数を、前記ゲート電極の前記p型不純物拡散領域に隣接する第2部位の材料が有する第2部位仕事関数よりも小さくし、且つ前記第1部位をn型不純物ポリシリコンで、前記第2部位をp型不純物ポリシリコンでそれぞれ構成することを特徴とする半導体装置。 - 半導体基板内に形成された第1のp型不純物拡散領域と、

前記第1のp型不純物拡散領域表面に形成されたn型不純物拡散領域と、

前記n型不純物拡散領域表面に形成された第2のp型不純物拡散領域と、

ゲート絶縁膜を介して、少なくとも前記第1のp型不純物拡散領域と前記n型不純物拡散領域に隣接するゲート電極と、

前記第2のp型不純物拡散領域からn型不純物拡散領域を介して前記第1のp型不純物拡散領域に達するように形成された溝と、

を備え、

前記ゲート電極は、前記ゲート絶縁膜を介して前記溝内壁に形成されており、

前記ゲート電極に電圧を印加したときに、前記第1のp型不純物拡散領域のゲート絶縁膜との界面での伝導体下端の曲がりが、前記n型不純物拡散領域の伝導体下端の曲がりよりも大きくなるように、前記ゲート電極の前記第1のp型不純物拡散領域に隣接する第1部位の材料が有する第1部位仕事関数を、前記ゲート電極の前記n型不純物拡散領域に隣接する第2部位の材料が有する第2部位仕事関数よりも大きくし、且つ前記第1部位をp型不純物ポリシリコンで、前記第2部位をn型不純物ポリシリコンでそれぞれ構成することを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33395899A JP4635286B2 (ja) | 1999-11-25 | 1999-11-25 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33395899A JP4635286B2 (ja) | 1999-11-25 | 1999-11-25 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001156288A JP2001156288A (ja) | 2001-06-08 |

| JP4635286B2 true JP4635286B2 (ja) | 2011-02-23 |

Family

ID=18271899

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP33395899A Expired - Fee Related JP4635286B2 (ja) | 1999-11-25 | 1999-11-25 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4635286B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5638559B2 (ja) * | 2012-03-26 | 2014-12-10 | 株式会社東芝 | 半導体装置 |

| JP5700027B2 (ja) | 2012-12-07 | 2015-04-15 | トヨタ自動車株式会社 | 半導体装置 |

| JP7095500B2 (ja) * | 2018-08-31 | 2022-07-05 | 株式会社デンソー | スイッチング素子 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| NL8203870A (nl) * | 1982-10-06 | 1984-05-01 | Philips Nv | Halfgeleiderinrichting. |

| JPS6247163A (ja) * | 1985-08-27 | 1987-02-28 | Matsushita Electric Works Ltd | 絶縁ゲ−ト型電界効果トランジスタ |

| JPH0279474A (ja) * | 1988-09-14 | 1990-03-20 | Nec Corp | Mosトランジスタ |

| JPH0669508A (ja) * | 1992-08-14 | 1994-03-11 | Matsushita Electric Works Ltd | 二重拡散型の電界効果トランジスタ |

| JP3400025B2 (ja) * | 1993-06-30 | 2003-04-28 | 株式会社東芝 | 高耐圧半導体素子 |

| JPH09232332A (ja) * | 1996-02-27 | 1997-09-05 | Fuji Electric Co Ltd | 半導体装置 |

| JPH09246545A (ja) * | 1996-03-08 | 1997-09-19 | Fuji Electric Co Ltd | 電力用半導体素子 |

| JP3425316B2 (ja) * | 1997-01-27 | 2003-07-14 | 株式会社東芝 | 半導体装置 |

| JP2000138370A (ja) * | 1998-10-30 | 2000-05-16 | Matsushita Electric Works Ltd | Mosfet |

-

1999

- 1999-11-25 JP JP33395899A patent/JP4635286B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001156288A (ja) | 2001-06-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11901444B2 (en) | Method for manufacturing semiconductor device | |

| US7915617B2 (en) | Semiconductor device | |

| US9299695B2 (en) | Semiconductor device | |

| US9318547B2 (en) | Wide bandgap insulated gate semiconductor device | |

| CN100524809C (zh) | 场效应晶体管半导体器件 | |

| US11094691B2 (en) | Semiconductor device | |

| US20160240614A1 (en) | Semiconductor device and semiconductor package | |

| US10916628B2 (en) | Semiconductor device | |

| JP3704007B2 (ja) | 半導体装置及びその製造方法 | |

| CN116722038A (zh) | 半导体装置 | |

| JP7512920B2 (ja) | 半導体装置およびその製造方法 | |

| JP2018152426A (ja) | 半導体装置 | |

| CN112201690A (zh) | Mosfet晶体管 | |

| US9263560B2 (en) | Power semiconductor device having reduced gate-collector capacitance | |

| US9825027B1 (en) | Semiconductor device | |

| KR102406116B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| JP4635286B2 (ja) | 半導体装置 | |

| CN118738084A (zh) | 一种半导体元件 | |

| JPH11195784A (ja) | 絶縁ゲート形半導体素子 | |

| JP2000031483A (ja) | 静電誘導半導体装置 | |

| CN113871452A (zh) | 半导体器件 | |

| CN118136678B (zh) | 双栅双沟道ldmos器件及制造方法 | |

| CN119630040B (zh) | 用于增强反向恢复性能的SiC沟槽MOSFET超级结及其制备方法 | |

| EP4704515A1 (en) | Insulated gate field effect transistor including trench structure | |

| US20240088250A1 (en) | Semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060616 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100729 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100810 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101004 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101108 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |