JP4542889B2 - パラメトリックモデリングユニットとポリゴンベースレンダリングシステム間のインターフェースをとるインターフェース及びその方法 - Google Patents

パラメトリックモデリングユニットとポリゴンベースレンダリングシステム間のインターフェースをとるインターフェース及びその方法 Download PDFInfo

- Publication number

- JP4542889B2 JP4542889B2 JP2004504186A JP2004504186A JP4542889B2 JP 4542889 B2 JP4542889 B2 JP 4542889B2 JP 2004504186 A JP2004504186 A JP 2004504186A JP 2004504186 A JP2004504186 A JP 2004504186A JP 4542889 B2 JP4542889 B2 JP 4542889B2

- Authority

- JP

- Japan

- Prior art keywords

- patch

- data

- subdivision

- leaf

- polygon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000000034 method Methods 0.000 title claims description 77

- 238000009877 rendering Methods 0.000 title claims description 26

- 238000004364 calculation method Methods 0.000 claims description 80

- 238000012545 processing Methods 0.000 claims description 44

- 230000001788 irregular Effects 0.000 claims description 30

- 239000011159 matrix material Substances 0.000 description 33

- 239000013598 vector Substances 0.000 description 25

- 230000008569 process Effects 0.000 description 21

- 238000010586 diagram Methods 0.000 description 12

- 230000008901 benefit Effects 0.000 description 8

- 238000004422 calculation algorithm Methods 0.000 description 8

- 230000008859 change Effects 0.000 description 7

- 238000006243 chemical reaction Methods 0.000 description 7

- 230000001419 dependent effect Effects 0.000 description 5

- 230000006870 function Effects 0.000 description 5

- 238000007667 floating Methods 0.000 description 4

- 238000007792 addition Methods 0.000 description 3

- 238000009795 derivation Methods 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 230000009466 transformation Effects 0.000 description 3

- 238000013459 approach Methods 0.000 description 2

- 230000006399 behavior Effects 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 238000005336 cracking Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 230000000007 visual effect Effects 0.000 description 2

- 230000009471 action Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000009191 jumping Effects 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 230000008707 rearrangement Effects 0.000 description 1

- 230000008929 regeneration Effects 0.000 description 1

- 238000011069 regeneration method Methods 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 230000001131 transforming effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T17/00—Three dimensional [3D] modelling, e.g. data description of 3D objects

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T17/00—Three dimensional [3D] modelling, e.g. data description of 3D objects

- G06T17/20—Finite element generation, e.g. wire-frame surface description, tesselation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T17/00—Three dimensional [3D] modelling, e.g. data description of 3D objects

- G06T17/30—Polynomial surface description

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Software Systems (AREA)

- Geometry (AREA)

- Computer Graphics (AREA)

- Mathematical Analysis (AREA)

- Pure & Applied Mathematics (AREA)

- Mathematical Physics (AREA)

- Mathematical Optimization (AREA)

- Algebra (AREA)

- Image Generation (AREA)

Description

ここで、x(s,t)、y(s,t)、及びz(s,t)の各々は、同次数のスカラパラメータの多項式であり、0≦s,t≦1である。双三次(すなわち2つの3次式の積)のベジェサーフェスの場合、多項式の次数は6である。ベジェ方程式とサーフェスの制御ポイントの各x、y、z成分とがサーフェスの形状を定義する。

は、次のように表すことができる。

ここでQはスカラー定数行列、Pはサーフェスに対する制御ポイントの行列である。

本発明の第1の態様によれば、請求項12によるインターフェースが提供される。本発明の第1の態様の好適な特徴は、従属請求項13から16で定義される。

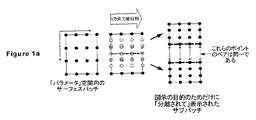

(1)モデルのすべてのパッチを同一の細分割レベルまで細分割する。これは単純であるがリソースを浪費する。

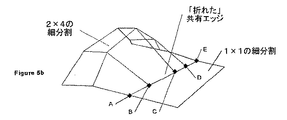

(2)各パッチ内で一様に細分割し、次いでステッチポリゴンを使用して非一様に分割されたパッチ間のギャップを隠す。これは、ステッチポリゴンが追加コストとなり、(図5aに見られるように)方向の急激な変化を誘導する可能性があるので理想的ではない。

(3)Clarkの方法を使用することにより、パッチ内でも非一様な細分割が可能となるが、T−ジョイント問題を欠点として有する。

(4)Clarkの方法にさらなるステッチポリゴンを適用する。

(5)メッシュをマイクロポリゴンに細分割する。

ここで、Ai、Bi、Ci、及びDiは、細分割のカテゴリによる4×4制御点の行列の適切な要素を表す。要素の索引付けが制御される方法は、細分割の各カテゴリに関して以下で説明する。

P=An-1+Bn-1

Q=Bn-1+Cn-1

R=Cn-1+Dn-1

である。

S=P+Q

T=Q+R

である。

U=S+T

である。

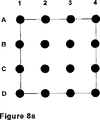

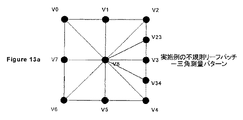

入力マルチプレクサの機能は、n−1番目レベルのパッチ制御点行列の行と列とを入れ替え、下位計算ユニットによって実行される細分割のカテゴリを制御できるようにすることである。

出力マルチプレクサの機能は入力マルチプレクサの機能に類似している。該マルチプレクサは細分割のカテゴリに応じて、細分割ユニットによる暫定的なデータ出力を配置して、要求されたサブパッチ制御点行列を形成する。下位計算ユニットがt方向の上半分の細分割を実行するように設定されたと仮定すると、t方向の下半分の細分割とs方向の左及び右半分の細分割を生成するよう下位計算ユニットの出力を再配置する必要がある。出力マルチプレクサは下位計算ユニットの4つの出力を組み立てて単一の行列にし、入力マルチプレクサによって実行された再配置を反転させて、要求されたサブパッチ制御点行列を生成する。

s方向に細分割、左半分を出力,

s方向に細分割、右半分を出力,

t方向に細分割、上半分を出力,

t方向に細分割、下半分を出力,

バイパス

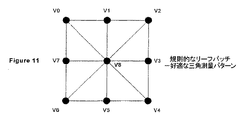

リーフパッチの最終エッジの値の各々が1.0と2.0の間である場合、リーフパッチは規則的であると言える。規則的なリーフパッチが処理されて、変換器により、図11に示されるようなパッチをカバーするように配置された三角形のグリッドの9つの頂点を生成する。好適には変換器はプロセッサ20を組み込む。三角形のテセレーションは、正方形の各辺に規則的配列で並べられた3つの頂点と、正方形の中心に配置された9番目の頂点とを有する正方形をカバーする。三角形は正方形を回転しながら扇形に配置され、その結果8つの三角形の各々は正方形の中心の頂点を共有する。図12に示され、従来技術でよく見られるような別のパターンもまた使用することができる。

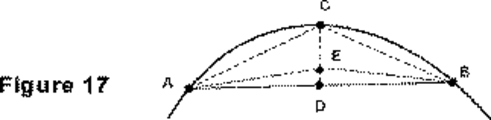

E=wC+(1−w)D …式2

ここでwは、エッジ細分割比率の小数部分から導出された重み付け因子、Dはリーフパッチの細分割レベルで導出された第1の頂点の値、及びCはサブリーフパッチの細分割レベルで導出された第2の頂点の値である。(エッジ比率の小数部分は、その値の2進浮動小数点表示の仮数部を調べることによって自明に得られる点に留意されたい)。

細分割は、関連するエッジのいずれか1つの値が1.0と2.0との間にある場合に、s又はtの任意の方向で終了する。不規則である場合、すなわち1つ又はそれ以上のエッジの値が1.0から2.0の範囲の外にある場合には、リーフパッチのさらなる処理が必要とされる。不規則リーフパッチは、細分割値が隣接するパッチに結合させることが可能な範囲の外にあるエッジ上に追加の頂点を必要とする、規則的なリーフパッチと考えることができる。不規則リーフパッチは最初に規則的なリーフパッチとして取り扱われ、パッチの9つの頂点は上述のようにして計算される。追加の頂点を計算するために、さらなる細分割を実行する。さらなる細分割は、リーフパッチを形成するための細分割と同一の細分割ユニット内で実行することができ、制御ユニット22によって制御することができる。追加の頂点を得るための扇状パッチの変換は、リーフパッチ用の変換器内か、又は別の変換器内で実行することができる。

サーフェス法線生成ユニット24は、細分割ユニット18の出力を取り込み、各頂点に関係するサーフェス法線を計算する。(好適な実施形態では、ユニット20及び24は別個のものであるが、別の実施形態では、これらは共通している幾つかの計算値を共有することができることに留意されたい)。サーフェス法線は、サンプルの点においてモデリングされているサーフェスが面している方向を示すのに使用され、後続のライティングとテクスチャの計算のために必要とされる。方向プロセッサ24は、不規則パッチから計算された任意の追加の頂点を含むリーフパッチの各々の頂点に対する法線を計算する。ポリゴンポッピングのシェーディングされた相似形を最小にするために、式2による前述のような線形補間法が、内部頂点の法線に対して適用され、すなわち出力法線は隣接する頂点の法線と「正しい」法線の混合とすることができる。

パラメータ位置(s、t)(s、t)における有理サーフェスの位置は以下の式で与えられる。

一方、(0,0)における(a,b)方向の単位長さの接線ベクトルの定義は次式で与えられる。

これはまさしく「S」正接と同じ論証に従うので、ここでは説明しない。

ここでサーフェス法線生成ユニット24を図22aに関連して説明する。

ユニット222はTTを計算すること以外はユニット221と同一であり、一方、ユニット223は単にTDiag=DXYZCW−CXYZDWを計算するだけである。

12 入力バッファ

14 フォーマット変換器

16 再帰バッファ

18 細分割ユニット

20 リーフパッチテセレーションユニット

22 制御ユニット

24 サーフェス法線生成ユニット

26 出力バッファ

Claims (19)

- オブジェクトを高次サーフェスとしてモデリングするためのパラメトリックモデリングユニットと表示用にポリゴンにモデリングされたオブジェクトをレンダリングするためのポリゴンベースレンダリングシステムとを備えた3次元グラフィックシステムで使用するためのインターフェースであって、

a)少なくとも1つの高次サーフェスパッチを表すデータを受け取るための入力装置と、

b)前記データを処理して第1のレベルの細分割で前記パッチを表すリーフパッチデータを形成するため、及び前記データをさらに処理して第2のレベルの細分割で前記パッチを表すサブリーフパッチデータを形成するための、前記入力装置に結合された細分割ユニットと、

c)前記リーフパッチを記述するテセレーションポリゴンの頂点を表す第1の複数の値を前記リーフパッチデータから求めるため、及び前記サブパッチを記述するテセレーションポリゴンの頂点を表す第2の複数の値を前記サブリーフパッチデータから求めるための、前記細分割ユニットに結合された変換器と、

d)前記第1及び第2の複数の値を結合して前記第1の細分割レベルで前記ポリゴンの頂点を定義するリーフポリゴンデータを形成するための前記変換器に結合された結合器と、

e)前記リーフポリゴンデータを出力するための、前記結合器に結合された出力装置と、

を備えることを特徴とするインターフェース。 - 前記結合器は前記第1及び第2の複数の値を重み付け平均を行うための重み付けプロセッサであることを特徴とする請求項1に記載のインターフェース。

- 前記細分割ユニットによる前記データの処理を制御するため、並びに前記第1及び第2の複数の値の重み付け平均値において重み付けプロセッサによって使用するための小数値wを生成するために、前記細分割ユニット及び前記重み付けプロセッサに結合された制御ユニットをさらに備えることを特徴とする請求項2に記載のインターフェース。

- 3次元グラフィックシステムにおいてパラメトリックモデリングユニットとポリゴンベースのレンダリングシステムとの間でインターフェースをとる方法であって、

a)少なくとも1つの高次サーフェスパッチを表すデータを受け取り、

b)前記データを処理して第1のレベルの細分割で前記パッチを表すリーフパッチデータを形成し、

c)前記リーフパッチを記述する複数のテセレーションポリゴンの頂点を表す第1の複数の値を前記リーフパッチデータから求め、

d)前記データをさらに処理して第2のレベルの細分割で前記パッチを表すサブリーフパッチデータを形成し、

e)前記サブリーフパッチを記述する前記複数のテセレーションポリゴンの頂点を表す第2の複数の値を前記サブリーフパッチデータから求め、

f)前記第1及び第2の複数の値を組み合わせて前記第1のレベルの細分割で前記ポリゴンの頂点を定義するリーフポリゴンデータを形成し、

g)前記リーフポリゴンデータを出力する、

各段階を含む方法。 - 前記データを処理する段階(d)は、前記リーフパッチデータの単一レベルの細分割を必要とすることを特徴とする請求項4に記載の方法。

- 前記第1及び第2の複数の値を組み合わせる段階(f)は、重み付け平均であることを特徴とする請求項4又は5に記載の方法。

- 前記細分割ユニットによる前記データ処理を制御する段階と、前記重み付け平均で使用するための小数値wを生成する段階とをさらに含む請求項6に記載の方法。

- パラメトリックモデリングユニットとポリゴンベースのレンダリングシステムとを備える3次元グラフィックシステム用のインターフェースであって、

a)少なくとも1つの高次サーフェスパッチを表すデータと、前記パッチのために必要とされる第1のレベルの細分割を表すパッチ細分割データと、前記パッチの少なくとも1つのエッジのために必要とされる第2のレベルの細分割を表すエッジ細分割データとを受け取るための入力装置と、

b)前記データを処理して前記第1のレベルの細分割で前記パッチを表すリーフパッチデータを形成するため、及び前記データをさらに処理して前記第2のレベルの細分割で前記パッチを表す扇状パッチデータを形成するために前記入力装置に結合された細分割ユニットと、

c)前記リーフパッチを記述するテセレーションポリゴンの頂点を表す第1の複数の値を前記リーフパッチデータから決定し、及び前記リーフパッチをさらに記述する前記第1の複数の値によって表されたポリゴンに対して追加のテセレーションポリゴンの頂点を表す扇状パッチの値を前記扇状パッチデータから決定するために前記細分割ユニットに結合された変換器と、

d)前記第1の複数の値と前記扇状パッチの値とを結合して前記第1の細分割レベルでテセレーションポリゴンの不規則なパターンの頂点を定義する不規則なリーフポリゴンデータを形成する前記変換器に結合された結合器と、

e)前記不規則なリーフポリゴンデータを出力するための前記結合器に結合された出力装置と、

を備えることを特徴とするインターフェース。 - 前記細分割ユニットによって前記データの処理を制御して前記パッチを第1の方向に前記第1の方向の必要とされるレベルまで細分割し、続いて前記パッチを第2の方向に前記第2の方向の必要とされるレベルまで細分割する、前記細分割ユニットに結合された制御ユニットをさらに備えることを特徴とする請求項8に記載のインターフェース。

- 3次元グラフィックシステムにおいてパラメトリックモデリングユニットとポリゴンベースのレンダリングシステムとの間でインターフェースをとる方法であって、

a)少なくとも1つの高次サーフェスパッチを表すデータと、前記パッチに必要とされる第1のレベルの細分割を表すパッチ細分割データと、前記パッチの少なくとも1つのエッジに必要とされる第2のレベルの細分割を表すエッジ細分割データとを受け取り、

b)第1のレベルの細分割で前記パッチを表すリーフパッチデータを形成するよう前記データを処理し、

c)前記リーフパッチを記述するテセレーションポリゴンの頂点を表す第1の複数の値を前記リーフパッチデータから求め、

d)前記第2のレベルの細分割で前記パッチを表す扇状パッチデータを形成するよう前記データをさらに処理し、

e)前記第1の複数の値によって表されたポリゴンに対して、前記リーフパッチをさらに記述する追加のテセレーションポリゴンの頂点を表す扇状パッチの値を前記扇状パッチデータから求め、

f)前記第1の複数の値と前記扇状パッチの値を組み合わせて、テセレーションポリゴンの不規則なパターンの頂点を前記第1の細分割レベルで定義する不規則なリーフポリゴンデータを形成し、

g)前記不規則なリーフポリゴンデータを出力する、

各段階を含む方法。 - 前記細分割ユニットによって前記データの処理を制御して前記パッチを第1の方向に前記第1の方向の必要とされるレベルまで細分割し、続いて前記パッチを第2の方向に前記第2の方向の必要とされるレベルまで細分割する段階をさらに含む請求項10に記載の方法。

- パラメトリックモデリングユニットとポリゴンベースのレンダリングシステムとを備えた3次元グラフィックシステム用のインターフェースであって、

a)少なくとも1つの高次サーフェスパッチを表すデータを受け取るための入力装置と、

b)前記データを再配置するための前記入力装置に結合された入力マルチプレクサと、

c)前記データを処理して第1の細分割方向の細分割レベルで前記パッチの一部分を表す暫定的なデータを形成するための、前記入力マルチプレクサに結合された細分割ユニットと、

d)前記暫定的なデータを配列して前記パッチの必要とされる部分を前記細分割レベルで表すリーフパッチデータを形成するために、前記細分割ユニットに結合された出力マルチプレクサと、

e)前記データの再配置と前記暫定的なデータの配置を制御し、前記細分割ユニットの前記第1の細分割方向を用いて必要とされる方向に前記パッチの必要とされる部分の生成を可能にするために、前記入力マルチプレクサ及び前記出力マルチプレクサに結合された制御ユニットと、

f)前記必要とされる方向に前記細分割レベルで前記パッチの必要とされる部分を記述するテセレーションポリゴンの頂点を表すリーフポリゴンデータを求めるための、前記出力マルチプレクサに結合されたポリゴニゼーションプロセッサと、

g)前記リーフポリゴンデータを出力するために前記ポリゴニゼーションプロセッサに結合された出力装置と、

を備えることを特徴とするインターフェース。 - 前記細分割ユニットは、前記入力及び出力マルチプレクサ並びに前記制御ユニットに並列に結合された4つの下位計算ユニットを備え、各下位計算ユニットが1/4のデータを処理して暫定的なデータの1/4を形成し、前記制御ユニットは、各下位計算ユニットが処理するための1/4のデータを前記データから選択することを特徴とする請求項12に記載のインターフェース。

- 各細分割ユニットが、

a)4つの値An-1、Bn-1、Cn-1、及びDn-1を含むデータを受け取るための入力マルチプレクサに結合され且つ第2及び第4の計算段階に結合された、加算:P=An-1+Bn-1、Q=Bn-1+Cn-1、R=Cn-1+Dn-1を並列に実行するため、並びに前記第4の計算段階にPを出力し且つ前記第2の計算段階にP、Q、及びRを出力するための3つの加算器を備える第1の計算段階と、

b)前記第1及び第4の計算段階に結合され並びに第3の計算段階に結合された、加算:S=P+Q、T=Q+Rを並列に実行するため、並びに前記第4の計算段階にSを出力し且つ前記第3の計算段階にSとTとを出力するための2つの加算器を備える第2の計算段階と、

c)前記第2及び第4の計算段階に結合された、加算:U=S+Tを実行するため、並びに前記第4の計算段階にUを出力するための1つの加算器を備える第3の計算段階と、

d)除算:V=P/2、W=S/4、X=U/8を並列に実行するため、並びに出力装置にV、W、及びXを出力するための3つの除算器を備える第4の計算段階と、

e)前記第1及び第4の計算段階並びに前記細分割ユニットの出力マルチプレクサに結合された、1/4の暫定的データ:An=An-1、Bn=V、Cn=W、及びDn=Xを出力するための出力装置と、

を備えることを特徴とする請求項13に記載のインターフェース。 - ルートパッチを表示するデータと処理されたデータとを格納するための、前記入力マルチプレクサ及び前記出力マルチプレクサに結合された再帰バッファをさらに備えることを特徴とする請求項12から請求項14のいずれか1項に記載のインターフェース。

- 3次元グラフィックシステムにおいてパラメトリックモデリングユニットとポリゴンベースのレンダリングシステムとの間でインターフェースをとる方法であって、

a)少なくとも1つの高次サーフェスパッチを表すデータを受け取り、

b)前記データを再配置し、

c)前記再配置されたデータを処理して前記パッチの一部分を第1の細分割方向に細分割レベルで表す暫定的なデータを形成し、

d)前記の暫定的なデータを配置して前記パッチの必要とされる部分を前記細分割レベルで表すリーフパッチデータを形成し、

e)前記データを再配置する段階と前記暫定的なデータを配置する段階を制御し、前記細分割ユニットの前記第1の細分割方向を用いて前記パッチの必要とされる部分を前記必要とされる方向に生成し、

f)前記必要とされる方向に前記必要とされる細分割レベルで前記パッチの必要とされる部分を記述するテセレーションポリゴンの頂点を表すリーフポリゴンデータを求め、

g)前記リーフポリゴンデータを出力する、

各段階を含む方法。 - 前記データを1/4に分割し、該1/4の4つのデータを並列に処理し、1/4の暫定的なデータを組み立てる段階をさらに含む請求項16に記載の方法。

- 各細分割ユニットの前記処理が、

a)4つの値:An-1、Bn-1、Cn-1、及びDn-1を含むデータを受け取り、加算:P=An-1+Bn-1、Q=Bn-1+Cn-1、R=Cn-1+Dn-1を並列に実行し、

b)加算:S=P+Q、T=Q+Rを並列に実行し、

c)加算:U=S+Tを実行し、

d)除算:V=P/2、W=S/4、X=U/8を並列に実行し、

e)前記1/4の暫定的なデータ:An=An-1、Bn=V、Cn=W、及びDn=Xを出力する、

各段階を含む請求項17に記載の方法。 - ルートパッチを表すデータと処理時間を短縮するための処理されたデータとを格納する段階をさらに含む請求項18に記載の方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB0210769A GB2388507B (en) | 2002-05-10 | 2002-05-10 | An interface and method of interfacing between a parametric modelling unit and a polygon based rendering system. |

| PCT/GB2003/001966 WO2003096277A2 (en) | 2002-05-10 | 2003-05-08 | An interface and method of interfacing between a parametric modelling unit and a polygon based rendering system |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010103076A Division JP5124615B2 (ja) | 2002-05-10 | 2010-04-28 | サーフェス法線ベクトルを求めるための装置又は方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005525645A JP2005525645A (ja) | 2005-08-25 |

| JP2005525645A5 JP2005525645A5 (ja) | 2006-07-13 |

| JP4542889B2 true JP4542889B2 (ja) | 2010-09-15 |

Family

ID=9936452

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004504186A Expired - Lifetime JP4542889B2 (ja) | 2002-05-10 | 2003-05-08 | パラメトリックモデリングユニットとポリゴンベースレンダリングシステム間のインターフェースをとるインターフェース及びその方法 |

| JP2010103076A Expired - Lifetime JP5124615B2 (ja) | 2002-05-10 | 2010-04-28 | サーフェス法線ベクトルを求めるための装置又は方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010103076A Expired - Lifetime JP5124615B2 (ja) | 2002-05-10 | 2010-04-28 | サーフェス法線ベクトルを求めるための装置又は方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (4) | US20040113909A1 (ja) |

| EP (1) | EP1537539B1 (ja) |

| JP (2) | JP4542889B2 (ja) |

| GB (3) | GB2388507B (ja) |

| WO (1) | WO2003096277A2 (ja) |

Families Citing this family (48)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| USRE42534E1 (en) * | 2000-07-28 | 2011-07-12 | Adrian Sfarti | Bicubic surface real-time tesselation unit |

| US7245299B2 (en) * | 2003-05-12 | 2007-07-17 | Adrian Sfarti | Bicubic surface real-time tesselation unit |

| US20050156930A1 (en) * | 2004-01-20 | 2005-07-21 | Matsushita Electric Industrial Co., Ltd. | Rendering device and rendering method |

| US7639252B2 (en) * | 2004-08-11 | 2009-12-29 | Ati Technologies Ulc | Unified tessellation circuit and method therefor |

| US20060033737A1 (en) * | 2004-08-16 | 2006-02-16 | Old William M | Methods and system for visualizing data sets |

| US7750914B2 (en) | 2004-08-26 | 2010-07-06 | Intel Corporation | Subdividing geometry images in graphics hardware |

| US7295204B2 (en) * | 2004-12-14 | 2007-11-13 | Adrian Sfarti | Rapid zippering for real time tesselation of bicubic surfaces |

| JP4255449B2 (ja) * | 2005-03-01 | 2009-04-15 | 株式会社ソニー・コンピュータエンタテインメント | 描画処理装置、テクスチャ処理装置、およびテセレーション方法 |

| US8047996B2 (en) | 2005-10-31 | 2011-11-01 | Volcano Corporation | System and method for reducing angular geometric distortion in an imaging device |

| US7785286B2 (en) | 2006-03-30 | 2010-08-31 | Volcano Corporation | Method and system for imaging, diagnosing, and/or treating an area of interest in a patient's body |

| US7612773B2 (en) * | 2006-05-22 | 2009-11-03 | Magnin Paul A | Apparatus and method for rendering for display forward-looking image data |

| JP2010500153A (ja) * | 2006-08-14 | 2010-01-07 | ノベリス・インコーポレーテッド | 画像化装置、画像化システム、および画像化の方法 |

| US20080043023A1 (en) * | 2006-08-15 | 2008-02-21 | Microsoft Corporation | Approximating subdivision surfaces with bezier patches |

| WO2008099269A2 (en) * | 2007-02-14 | 2008-08-21 | Photint Venture Group Inc. | Banana codec |

| US7952580B1 (en) * | 2007-08-31 | 2011-05-31 | Adobe Systems Incorporated | Classification of exterior and interior triangles for artwork rendering |

| US7928979B2 (en) * | 2008-02-01 | 2011-04-19 | Microsoft Corporation | Efficient geometric tessellation and displacement |

| US8643644B2 (en) * | 2008-03-20 | 2014-02-04 | Qualcomm Incorporated | Multi-stage tessellation for graphics rendering |

| JP5078712B2 (ja) * | 2008-04-01 | 2012-11-21 | 任天堂株式会社 | 画像処理プログラム、画像処理装置、画像処理システム及び画像処理方法 |

| US8243075B2 (en) * | 2008-10-14 | 2012-08-14 | Autodesk, Inc. | Graphics processing unit accelerated dynamic radial tessellation |

| US20100186061A1 (en) * | 2009-01-18 | 2010-07-22 | Gavriel Raanan | Distributed processing for interactive video |

| US20100231586A1 (en) * | 2009-03-13 | 2010-09-16 | Zebra Imaging, Inc. | Processing Graphics Primitives in an Epsilon View Volume |

| US20100231585A1 (en) * | 2009-03-13 | 2010-09-16 | Zebra Imaging, Inc. | Systems and Methods for Processing Graphics Primitives |

| US20100253683A1 (en) * | 2009-04-01 | 2010-10-07 | Munkberg Carl J | Non-uniform tessellation technique |

| US8884957B2 (en) * | 2009-09-09 | 2014-11-11 | Advanced Micro Devices, Inc. | Tessellation engine and applications thereof |

| US8698802B2 (en) * | 2009-10-07 | 2014-04-15 | Nvidia Corporation | Hermite gregory patch for watertight tessellation |

| SG183950A1 (en) * | 2010-03-09 | 2012-10-30 | Happy Cloud Inc | Data streaming for interactive decision-oriented software applications |

| US8810572B2 (en) * | 2011-10-31 | 2014-08-19 | Qualcomm Incorporated | Tessellation cache for object rendering |

| CN103268634B (zh) * | 2012-02-24 | 2016-08-24 | 苏州蓝海彤翔系统科技有限公司 | 一种外存模型基于顶点聚类的快速并行自适应简化方法 |

| US10248740B2 (en) * | 2012-04-09 | 2019-04-02 | Autodesk, Inc. | Three-dimensional printing preparation |

| US9007380B1 (en) * | 2012-05-01 | 2015-04-14 | Google Inc. | Animated 3D buildings in virtual 3D environments |

| US9305397B2 (en) * | 2012-10-24 | 2016-04-05 | Qualcomm Incorporated | Vertex order in a tessellation unit |

| WO2014068400A2 (en) * | 2012-11-02 | 2014-05-08 | Imagination Technologies, Ltd. | On demand geometry and acceleration structure creation |

| US9196088B2 (en) * | 2013-03-14 | 2015-11-24 | Robert Bosch Gmbh | System and method for classification of three-dimensional models in a virtual environment |

| US9965893B2 (en) * | 2013-06-25 | 2018-05-08 | Google Llc. | Curvature-driven normal interpolation for shading applications |

| KR102104057B1 (ko) | 2013-07-09 | 2020-04-23 | 삼성전자 주식회사 | 점별로 테셀레이션 팩터를 할당하는 방법과 상기 방법을 수행할 수 있는 장치들 |

| AU2013267004A1 (en) | 2013-12-04 | 2015-06-18 | Canon Kabushiki Kaisha | Method, apparatus and system for tessellating a parametric patch |

| DE102014007914A1 (de) * | 2014-05-27 | 2015-12-03 | Elektrobit Automotive Gmbh | Graphisches Darstellen von Straßen und Routen unter Benutzung von Hardware-Tesselierung |

| US10055857B2 (en) * | 2014-08-29 | 2018-08-21 | Ati Technologies Ulc | Extension of the MPEG/SC3DMC standard to polygon meshes |

| GB2539042B (en) | 2015-06-05 | 2019-08-21 | Imagination Tech Ltd | Tessellation method using displacement factors |

| GB2533443B (en) * | 2015-06-05 | 2018-06-06 | Imagination Tech Ltd | Tessellation method using recursive sub-division of triangles |

| GB2552260B (en) | 2015-06-05 | 2019-04-10 | Imagination Tech Ltd | Tessellation method |

| US10242496B2 (en) | 2017-04-24 | 2019-03-26 | Intel Corporation | Adaptive sub-patches system, apparatus and method |

| GB2572625B (en) * | 2018-04-05 | 2020-06-17 | Imagination Tech Ltd | Ordering in tessellation operations |

| GB2572619B (en) | 2018-04-05 | 2020-06-17 | Imagination Tech Ltd | Hardware Tessellation Units |

| US11017265B1 (en) | 2020-01-29 | 2021-05-25 | ReportsNow, Inc. | Systems, methods, and devices for image processing |

| CN112330556B (zh) * | 2020-11-03 | 2022-04-19 | 燕山大学 | 一种基于有理贝塞尔曲面的球幕投影几何校正方法 |

| WO2022250654A1 (en) * | 2021-05-24 | 2022-12-01 | Uiarmor.Com Llc | Systems, methods, and devices for image processing |

| US11158031B1 (en) | 2021-05-24 | 2021-10-26 | ReportsNow, Inc. | Systems, methods, and devices for image processing |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2726134B2 (ja) * | 1990-01-12 | 1998-03-11 | 三菱電機株式会社 | 立体モデルのサンプリング及び法線ベクトルの算出方法 |

| US5428718A (en) * | 1993-01-22 | 1995-06-27 | Taligent, Inc. | Tessellation system |

| JPH07271999A (ja) * | 1994-03-31 | 1995-10-20 | Oki Electric Ind Co Ltd | 3次元地形出力方法 |

| JPH07311858A (ja) * | 1994-05-18 | 1995-11-28 | Sony Corp | 自由曲面作成方法及び自由曲面作成装置 |

| US6078331A (en) * | 1996-09-30 | 2000-06-20 | Silicon Graphics, Inc. | Method and system for efficiently drawing subdivision surfaces for 3D graphics |

| US5828467A (en) * | 1996-10-02 | 1998-10-27 | Fuji Xerox Co., Ltd. | Block noise prevention by selective interpolation of decoded image data |

| US5995109A (en) * | 1997-04-08 | 1999-11-30 | Lsi Logic Corporation | Method for rendering high order rational surface patches |

| JP3732317B2 (ja) * | 1997-09-17 | 2006-01-05 | 株式会社ソニー・コンピュータエンタテインメント | 情報処理装置および方法、並びに伝送媒体 |

| US6356263B2 (en) * | 1999-01-27 | 2002-03-12 | Viewpoint Corporation | Adaptive subdivision of mesh models |

| JP2001067491A (ja) * | 1999-08-30 | 2001-03-16 | Sega Corp | 再分割多角形を用いる画像表示方法及び装置 |

| JP3377488B2 (ja) * | 2000-02-10 | 2003-02-17 | 株式会社ナムコ | ゲームシステム及び情報記憶媒体 |

| JP4483025B2 (ja) * | 2000-05-18 | 2010-06-16 | ソニー株式会社 | 画像処理装置、情報処理装置 |

| US6707452B1 (en) * | 2000-07-19 | 2004-03-16 | Pixar | Method and apparatus for surface approximation without cracks |

| US6563501B2 (en) * | 2000-07-28 | 2003-05-13 | Adrian Sfarti | Bicubic surface rendering |

| US6597356B1 (en) * | 2000-08-31 | 2003-07-22 | Nvidia Corporation | Integrated tessellator in a graphics processing unit |

| CA2429130A1 (en) * | 2001-02-01 | 2002-09-26 | Mental Images G.M.B.H. & Co. Kg. | Generating smooth feature lines for subdivision surfaces |

| US6940503B2 (en) * | 2001-05-10 | 2005-09-06 | Ati International Srl | Method and apparatus for processing non-planar video graphics primitives |

| JP3522714B2 (ja) * | 2001-06-05 | 2004-04-26 | 松下電器産業株式会社 | 画像生成方法 |

| US6989830B2 (en) * | 2002-07-01 | 2006-01-24 | Alias Systems Corp. | Accurate boolean operations for subdivision surfaces and relaxed fitting |

-

2002

- 2002-05-10 GB GB0210769A patent/GB2388507B/en not_active Expired - Lifetime

- 2002-05-10 GB GB0517745A patent/GB2415118B/en not_active Expired - Lifetime

- 2002-05-10 GB GB0517744A patent/GB2415117B/en not_active Expired - Lifetime

-

2003

- 2003-05-08 WO PCT/GB2003/001966 patent/WO2003096277A2/en active Application Filing

- 2003-05-08 JP JP2004504186A patent/JP4542889B2/ja not_active Expired - Lifetime

- 2003-05-08 EP EP03725375.4A patent/EP1537539B1/en not_active Expired - Lifetime

- 2003-05-09 US US10/435,759 patent/US20040113909A1/en not_active Abandoned

-

2005

- 2005-09-22 US US11/232,760 patent/US7227546B2/en not_active Expired - Lifetime

-

2006

- 2006-12-13 US US11/638,545 patent/US7362328B2/en not_active Expired - Lifetime

-

2008

- 2008-04-16 US US12/148,043 patent/US7768511B2/en not_active Expired - Lifetime

-

2010

- 2010-04-28 JP JP2010103076A patent/JP5124615B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| GB2415117A (en) | 2005-12-14 |

| WO2003096277A3 (en) | 2005-03-17 |

| US7768511B2 (en) | 2010-08-03 |

| GB0517744D0 (en) | 2005-10-12 |

| JP5124615B2 (ja) | 2013-01-23 |

| US7227546B2 (en) | 2007-06-05 |

| JP2005525645A (ja) | 2005-08-25 |

| US20070091086A1 (en) | 2007-04-26 |

| GB2415118B (en) | 2006-04-05 |

| US20060050071A1 (en) | 2006-03-09 |

| GB2388507A (en) | 2003-11-12 |

| GB2388507B (en) | 2005-11-09 |

| GB0517745D0 (en) | 2005-10-12 |

| EP1537539A2 (en) | 2005-06-08 |

| US20040113909A1 (en) | 2004-06-17 |

| EP1537539B1 (en) | 2019-05-01 |

| JP2010191991A (ja) | 2010-09-02 |

| GB0210769D0 (en) | 2002-06-19 |

| WO2003096277A2 (en) | 2003-11-20 |

| US20080273034A1 (en) | 2008-11-06 |

| GB2415117B (en) | 2006-04-12 |

| GB2415118A (en) | 2005-12-14 |

| US7362328B2 (en) | 2008-04-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4542889B2 (ja) | パラメトリックモデリングユニットとポリゴンベースレンダリングシステム間のインターフェースをとるインターフェース及びその方法 | |

| US8289323B2 (en) | Drawing processing apparatus, texture processing apparatus, and tessellation method | |

| US8749576B2 (en) | Method and system for implementing multiple high precision and low precision interpolators for a graphics pipeline | |

| JP2921659B2 (ja) | ビデオ・イメージの寸法変更装置及び方法 | |

| EP0425177A2 (en) | Parametric surface evaluation for a computer graphics display system | |

| US8698802B2 (en) | Hermite gregory patch for watertight tessellation | |

| JP2005525645A5 (ja) | ||

| EP1756769A2 (en) | Method and system for a general instruction raster stage that generates programmable pixel packets | |

| JP2000510268A (ja) | 3次元グラフィックス補間を実行するための乗算器 | |

| CN1501324A (zh) | 于匀相空间中进行三角形插补工作的方法及其可程序装置 | |

| US7106352B2 (en) | Automatic gain control, brightness compression, and super-intensity samples | |

| US8169437B1 (en) | Distributed tessellation topology generator | |

| US7538773B1 (en) | Method and system for implementing parameter clamping to a valid range in a raster stage of a graphics pipeline | |

| US8482559B2 (en) | Method and apparatus for triangle tessellation | |

| US7196703B1 (en) | Primitive extension | |

| US6570575B1 (en) | Associated color texture processor for high fidelity 3-D graphics rendering | |

| US8432394B1 (en) | Method and system for implementing clamped z value interpolation in a raster stage of a graphics pipeline | |

| JP2008505533A (ja) | N次元面体補間 | |

| US7768512B1 (en) | System and method for rasterizing primitives using direct interpolation | |

| JPH11252353A (ja) | 画像補間方法および画像補間装置 | |

| Hall | Efficient Subdivision Surface Evaluation | |

| Carr et al. | Real-Time Procedural Solid Texturing |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060508 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060508 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090629 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090706 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20091005 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20091013 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100208 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100428 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100531 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100628 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4542889 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130702 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |