JP4457570B2 - 固体撮像素子及びその製造方法 - Google Patents

固体撮像素子及びその製造方法 Download PDFInfo

- Publication number

- JP4457570B2 JP4457570B2 JP2003091697A JP2003091697A JP4457570B2 JP 4457570 B2 JP4457570 B2 JP 4457570B2 JP 2003091697 A JP2003091697 A JP 2003091697A JP 2003091697 A JP2003091697 A JP 2003091697A JP 4457570 B2 JP4457570 B2 JP 4457570B2

- Authority

- JP

- Japan

- Prior art keywords

- transfer

- vertical

- electrode

- light receiving

- receiving sensor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Light Receiving Elements (AREA)

Description

【発明の属する技術分野】

本発明は、信号電荷を転送する電荷転送部を有する固体撮像素子及びその製造方法に係わる。

【0002】

【従来の技術】

CCD固体撮像素子に代表される、信号電荷を転送する電荷転送部を有する固体撮像素子においては、信号電荷が各画素の受光センサ部(光電変換部・電荷蓄積部)から電荷転送部(転送レジスタ等)へ一度に又は複数回に分けて読み出され、電荷転送部中で前後の信号電荷と混合しないように転送される。

【0003】

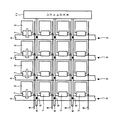

従来のCCD固体撮像素子の概略断面図(平面図)を図8に示す。

縦横に配設された受光センサ部61の各列に対応して垂直転送レジスタ62が設けられている。この垂直転送レジスタ62では、対応する列の各受光センサ部61からの信号電荷を読み出して垂直方向(図中上下方向)に転送する。

垂直転送レジスタ62には、信号電荷を転送する駆動を行うための転送電極63として、第1層の多結晶シリコン層による転送電極53と、第2層の多結晶シリコン層による転送電極54とが設けられている。第1層の多結晶シリコン層による転送電極53は、垂直方向に隣接する受光センサ部61間を水平方向(図中左右方向)に延びるように形成され、垂直転送レジスタ62上において図中下方に櫛歯状に延びる部分を有する平面形状(パターン)となっている。第2層の多結晶シリコン層による転送電極54は、垂直方向に隣接する受光センサ部61間を水平方向(図中左右方向)に延びるように形成され、垂直転送レジスタ62上において図中上方に櫛歯状に延びる部分を有する平面形状(パターン)となっている。そして、これら転送電極53,54により、各受光センサ部61が囲繞されている。

第2層の転送電極54は、その櫛歯状の部分が各受光センサ部61から垂直転送レジスタ62へ信号電荷を読み出す読み出し駆動をする読み出しゲート部となるものである。

【0004】

また、垂直転送レジスタ62の転送先側には、この垂直転送レジスタ62により垂直転送されてきた信号電荷を水平転送方向に転送する水平転送レジスタ(通常1個、複数の場合もある。)が設けられ、この水平転送レジスタの転送先側には、信号電荷を電圧に変換して出力する電荷検出部(図示せず)が設けられる。

【0005】

転送電極63(53,54)に対して、基本的には4相の垂直転送パルスφV1,φV2,φV3,φV4が印加され、それによって垂直転送レジスタ62における信号電荷の転送が行われる。第1層の転送電極53には垂直転送パルスφV2又はφV4が印加され、第2層の転送電極54には垂直転送パルスφV1又はφV3が印加される。このうち、第2層の転送電極54に印加される垂直転送パルスφV1及びφV3には、読み出し時には読み出しパルスが印加されるように構成される。これにより、読み出し時には、図8において矢印71で示すように、受光センサ部61から信号電荷が読み出される。

受光センサ部61から信号電荷が読み出された後には、4相の垂直転送パルスφV1,φV2,φV3,φV4の印加により信号電荷の転送が行われる。

【0006】

第1層の転送電極53及び第2層の転送電極54は、垂直転送レジスタ62における断面図を図9Aに示すように、半導体基板例えばシリコン基板51上に、ゲート絶縁膜52を介して形成されている。また、これら転送電極53及び54は、図8及び図9Aに示すように、垂直転送レジスタ62においては、端部が互いに上下に重なっていると共に、絶縁膜55により互いに絶縁されている。

そして、各転送電極53及び54に垂直転送パルスφV1,φV2,φV3,φV4を印加することにより、図9B〜図9Hに示すように、信号電荷56が図中右方向に転送されていく。

【0007】

従来は、このように、信号電荷が各画素の受光センサ部(光電変換部・電荷蓄積部)から垂直転送レジスタ等の電荷転送部へ一度に又は複数回に分けて読み出される構成となっていた(例えば特許文献1及び特許文献2参照。)。

【0008】

【特許文献1】

特開平6−77450号公報(図7)

【特許文献2】

特開2002−270811号公報(図7、図8)

【0009】

【発明が解決しようとする課題】

しかしながら、従来の固体撮像素子は、受光センサ部、電荷読み出し部、電荷転送部の各領域が、上述した平面配置とされているため、受光センサ部の面積を大きくすると電荷転送部が小さくなり、電荷転送部の面積を大きくすると受光センサ部が小さくなってしまう。

【0010】

このことから、従来の固体撮像素子においては、単位画素サイズを縮小すると、電荷転送部の縮小による飽和出力の低下、又は受光センサ部の縮小による感度の低下の少なくともいずれかの問題が避けられないものとなっていた。

【0011】

さらに、電荷転送部に複数の転送電極が設けられ、各転送電極間に各電極を絶縁するための絶縁膜による隙間が存在しているため、電荷転送を妨げるポテンシャルギャップが形成され、高速電荷転送の実現が困難になってしまっていた。

【0012】

上述した問題の解決のために、本発明においては、画素サイズが縮小化されたときでも、充分な飽和出力及び感度を有すると共に信号電荷を高速で転送することが可能である固体撮像素子及びその製造方法を提供するものである。

【0013】

【課題を解決するための手段】

本発明の固体撮像素子は、画素を構成する受光センサ部が多数マトリクス状に配置され、この受光センサ部の各列に対して、それぞれ垂直方向に延びる垂直電荷転送部が設けられ、各垂直電荷転送部が、半導体基体内に形成された転送領域と、この転送領域が形成された部分の半導体基体上に絶縁膜を介して形成された1枚の垂直転送電極とにより構成され、垂直電荷転送部の転送領域と垂直転送電極とが同じ幅に形成され、各垂直電荷転送部の受光センサ部と対向する部分に、受光センサ部から信号電荷を読み出すための読み出し用電極が、垂直電荷転送部の垂直転送電極とは独立して設けられ、この読み出し用電極が受光センサ部の各行毎に電気的に接続され、垂直転送電極に一定間隔で電圧供給部が設けられ、この電圧供給部を通じて、垂直転送電極の一部分に電圧が供給されるものである。

【0014】

上記本発明の固体撮像素子において、さらに受光センサ部の表面に透明電極が接続され、この透明電極が受光センサ部の各行毎に連続して形成されている構成とすることが可能である。

【0015】

本発明の固体撮像素子の製造方法は、画素を構成する受光センサ部が多数マトリクス状に配置され、この受光センサ部の各列に対して、それぞれ垂直方向に延びる垂直電荷転送部が設けられ、各垂直電荷転送部が1枚の垂直転送電極により構成された固体撮像素子を製造する際に、半導体基体上に絶縁層を形成し、垂直電荷転送部となる部分の絶縁層を除去する工程と、この絶縁層をマスクとして用いて、半導体基体にイオン注入により垂直電荷転送部の転送領域となる半導体領域を形成する工程と、その後、絶縁層の除去された部分に垂直電荷転送部の垂直転送電極を形成する工程と、絶縁層を除去する工程とを少なくとも有するものである。

【0016】

上述の本発明の固体撮像素子の構成によれば、各垂直電荷転送部が1枚の垂直転送電極により構成されていることにより、垂直電荷転送部の転送領域において、ポテンシャル障壁を生じない。

従って、受光センサ部から読み出した信号電荷を、垂直電荷転送部の広い領域に蓄積させることが可能になり、垂直電荷転送部の最大電荷転送量を大きくすることが可能になる。しかも、ポテンシャル障壁を生じないので、垂直電荷転送部において、信号電荷を高速で転送することができる。

【0017】

また、各垂直電荷転送部の受光センサ部と対向する部分に、受光センサ部から信号電荷を読み出すための読み出し用電極が、垂直電荷転送部の垂直転送電極とは独立して設けられ、この読み出し用電極が受光センサ部の各行毎に電気的に接続されていることにより、受光センサ部の各行毎に信号電荷の読み出しを行うことができ、信号電荷の読み出しと信号電荷の転送とをそれぞれ独立して制御することが可能になる。

【0018】

特に、受光センサ部の表面に透明電極が接続され、この透明電極が受光センサ部の各行毎に連続して形成されている構成としたときには、この透明電極から受光センサ部において生じた余剰電荷を排出することができ、この透明電極が受光センサ部の各行毎に連続して形成されているため、各行毎に余剰電荷の排出を行うことができる。

そして、読み出し用電極が各行毎に電気的に接続され、各行毎に読み出しが行われるので、読み出しと余剰電荷の排出を各行毎に行って、各行の受光センサ部の蓄積時間を揃えることが可能になる。

【0019】

上述の本発明の固体撮像素子の製造方法によれば、絶縁層をマスクとして用いて、半導体基体にイオン注入により垂直電荷転送部の転送領域となる半導体領域を形成した後に、絶縁層の除去された部分に垂直電荷転送部の垂直転送電極を形成し、絶縁層を除去することにより、同じ絶縁層の除去された部分に上下に垂直転送電極と転送領域が形成される。従って、垂直転送電極と転送領域を自己整合して形成することが可能になる。

【0020】

【発明の実施の形態】

本発明の固体撮像素子は、画素を構成する受光センサ部が多数マトリクス状に配置され、この受光センサ部の各列に対して、それぞれ垂直方向に延びる垂直電荷転送部が設けられた固体撮像素子であって、各垂直電荷転送部が、半導体基体内に形成された転送領域と、この転送領域が形成された部分の半導体基体上に絶縁膜を介して形成された1枚の垂直転送電極とにより構成され、垂直電荷転送部の転送領域と垂直転送電極とが同じ幅に形成され、各垂直電荷転送部の受光センサ部と対向する部分に、受光センサ部から信号電荷を読み出すための読み出し用電極が、垂直電荷転送部の垂直転送電極とは独立して設けられ、この読み出し用電極が受光センサ部の各行毎に電気的に接続され、垂直転送電極に一定間隔で電圧供給部が設けられ、この電圧供給部を通じて、垂直転送電極の一部分に電圧が供給されるものである。

【0022】

また、上記本発明の固体撮像素子において、受光センサ部の表面に透明電極が接続され、この透明電極が受光センサ部の各行毎に連続して形成されている構成を可能とする。

【0023】

また、上記本発明の固体撮像素子において、垂直転送電極に設けられた電圧供給部が、受光センサ部と同一基板に形成されたシフトレジスタに電気的に接続されている構成を可能とする。

【0025】

図1は、本発明の一実施の形態として、固体撮像素子の概略構成図(断面図)を示す。本実施の形態は、本発明をCSD構造の電荷転送部を有する固体撮像素子に適用したものである。

この固体撮像素子1は、受光センサ部2がマトリクス状に配置され、受光センサ部2の各列の一側に、垂直電荷転送部として、垂直方向(図中上下方向)Vに延びる垂直転送レジスタ3が設けられている。

【0026】

受光センサ部2は、それぞれが画素を構成するものであり、光を電荷に変換する光電変換部と、変換された電荷を蓄積する電荷蓄積部とを有する。

【0027】

本実施の形態の固体撮像素子1においては、特に、各垂直転送レジスタ3の転送電極(垂直転送電極)4を、単一の電極層(1枚の電極層)により構成している。

この転送電極4は、例えば高抵抗の多結晶シリコン膜により構成され、例えばノンドープの多結晶シリコン膜を形成した後に、低濃度の不純物のドープを行うことにより形成することができる。

この転送電極4により、CSD構造の垂直転送レジスタ3が構成されている。転送電極4の下にある、半導体基板又は半導体層には、信号電荷が転送される転送領域として、信号電荷が転送される転送チャネル(図示せず)が、転送電極4と自己整合して形成されている。

【0028】

高抵抗の転送電極4は、例えば数kΩ/□程度のシート抵抗とすればよい。

高抵抗にすることから、転送電極4を細くして抵抗が高くなっても問題ない。従って、垂直転送レジスタ3の幅を狭くして、その分受光センサ部2の面積の割合を大きくすることが可能になり、受光センサ部2の面積を1画素の領域の面積の70%程度にすることも可能になる。

【0029】

転送電極4は、各画素に対応する一定間隔のコンタクト部5において、それぞれ水平方向に延びる電圧供給線(配線)6とコンタクトさせることにより、転送電極4に電位の分布を与えて、転送電極4下の転送チャネル領域において、一般的なCCD構造の電荷転送部と同様に信号電荷の転送を行うことが可能な構成とする。

【0030】

電圧供給線6は、水平方向(図中左右方向)Hに延びる導線部と、垂直転送レジスタ3に沿って櫛歯状に垂直方向Vに延びる遮光部とを有している。

電圧供給線6の材料としては、光を遮ることができる、例えばアルミニウム、タングステン等の金属が用いられ、特に垂直転送レジスタ3に沿って形成された遮光部により、転送電極4の下の転送チャネルに光が入射することを抑制することができる。

そして、導線部は、垂直方向Vの画素間の部分に配置形成されている。

また、下方向に延びる遮光部に、前述した転送電極4と接続するためのコンタクト部5が設けられている。

【0031】

また、本実施の形態の固体撮像素子1においては、各画素に対して、垂直転送レジスタ3を構成する転送電極(垂直転送電極)4とは独立して、読み出し用電極7を設けている。

即ち、この読み出し用電極7は、転送電極4とは図示しない絶縁膜により絶縁され、それぞれ独立して電圧を印加することができるように構成されている。

そして、読み出し用電極7は、画素(受光センサ部2)の各列毎に、水平方向Hに延びる配線部8に連結されている。配線部8は、垂直方向Vの画素間の部分に配置され、電圧供給線6の導線部の下層に形成されている。

【0032】

この読み出し用電極7の材料としては、例えば多結晶シリコンやタングステンシリサイド等の導電性の物質が挙げられる。

そして、読み出し用電極7は、垂直転送レジスタ3の図中右側の受光センサ部2から垂直転送レジスタ3の転送電極4に亘って形成され、転送電極4上に一部重なりをもって形成されている。

また、読み出し用電極7は、電圧供給線6の遮光部よりは下層(半導体基体側)に形成されている。

【0033】

配線部8を通じて、各読み出し用電極7に、それぞれ読み出し電圧を印加することにより、受光センサ部2に蓄積された信号電荷を垂直転送レジスタ3の転送チャネルに読み出すことができる。

各配線部8は、画素(受光センサ部2)の各行に1本ずつ形成されているため、画素(受光センサ部2)の行(ライン)毎に信号電荷の読み出しを行うことができる。

【0034】

そして、配線部8を通じて読み出し用電極7に印加する読み出し電圧の態様を変えることにより、垂直方向Vに隣接する画素における信号電荷の混合、信号電荷の間引き、信号電荷を加算しない全画素読み出しのいずれにも対応することが可能になる。

【0035】

受光センサ部2は、図中斜線で示す領域に形成されている。左右方向は転送電極4又は読み出し用電極7の端部まで、上下方向は電圧供給線6の下を除いた部分に形成されている。

【0036】

さらに、本実施の形態の固体撮像素子1においては、受光センサ部2の表面上に透明電極9を設け、この透明電極9をコンタクト部10を介して受光センサ部2と電気的に接続している。

この透明電極9は、各行(各ライン)毎に余剰電荷を排出するためのものであり、それぞれ受光センサ部2の各行毎に1本ずつ互いに独立して設けられている。

【0037】

従来のCCD固体撮像素子では、例えば基板側に余剰電荷を排出する縦型オーバーフロードレイン構造が採られている。この縦型オーバーフロードレイン構造を採用すると、全画素に対して一度に余剰電荷の排出が行われる。従来のCCD固体撮像素子では、信号電荷の読み出しが全画素で一度に行われたり、一行おきに二度にわたって行われたりするため、信号電荷の読み出しの回数が少ない。このため、全画素の余剰電荷の排出が一度に行われても蓄積時間にほとんど差を生じないため、問題にはならない。

【0038】

これに対して、本実施の形態の固体撮像素子1の構成においては、各ライン毎に設けられた読み出し用電極7によりライン毎に受光センサ部2の信号電荷の読み出しを行うため、一度に全画素に対して余剰電荷の排出を行ってしまうと、ライン毎に受光センサ部2の蓄積時間に差ができてしまい、読み出し順序の早いラインと読み出し順序の遅いラインとで蓄積時間が大きく違ってしまう。

そこで、本実施の形態の固体撮像素子1では、受光センサ部2の各ライン毎に1本ずつ互いに独立して透明電極9を設けており、これにより、各ラインの受光センサ部2の蓄積時間を同一にするように駆動することが可能になっている。

【0039】

そして、透明電極9を、例えば読み出し用電極7と同期させて駆動することも可能である。

【0040】

一方、受光センサ部2内の電荷蓄積部に蓄積される電荷量は、受光センサ部2の表面に接続された透明電極9の電位を任意の電圧とすることで制御される。

この透明電極9の電位を電荷蓄積部の電位より大きくすることにより、電荷蓄積部に蓄えられた電荷を全て排出することも可能である。

【0041】

さらに、必要に応じて、カラーフィルタやオンチップマイクロレンズ等が配置されて固体撮像素子1が構成される。

【0042】

なお、図示しない水平転送レジスタの構成は、従来の固体撮像素子と同様である。

【0043】

次に、本実施の形態の固体撮像素子1の動作について説明する。

ここで、本実施の形態の固体撮像素子1の模式的平面図を図2に示す。

【0044】

まず、受光センサ部2に入射した光は、受光センサ部2の光電変換部において電荷に変換され、電荷蓄積部に蓄積される。

次に、読み出し時に、受光センサ部2の電荷蓄積部に蓄積された信号電荷が、ライン毎に隣接した読み出し用電極7を経由して電荷転送路である転送チャネル(転送領域)に読み出される。

具体的には、配線部8を通じて読み出し用電極7に読み出しパルスが印加されることにより、同一ラインにある各受光センサ部2において、図2中矢印で示すように、受光センサ部2から垂直転送レジスタ3の転送電極4下にある転送チャネルに信号電荷の読み出しが行われる。

【0045】

続いて、垂直転送レジスタ3の転送チャネルに読み出された信号電荷が順次水平転送レジスタへ転送される。

具体的には、転送電極4に接続された電圧供給線6に、図2中右側にあるシフトレジスタ11から順次電圧を印加することにより、転送電極4下の転送チャネルの電位が変動して、読み出された信号電荷が転送される。

シフトレジスタ11は、各電圧供給線6と接続されており、例えば固体撮像素子1と同一基板上に形成される。

なお、シフトレジスタ11の代わりに、外部基板に設けられた同様の機能を有する回路を用いて、電圧供給線6に電圧を供給するようにしてもよい。

電圧供給線6は、シフトレジスタ11もしくは外部基板からの電圧供給を受けて、高速に動作される。

【0046】

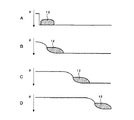

このときの垂直転送レジスタ3の転送チャネル内における電荷転送を模式的に図3に示す。

まず、図3Aに示すように、信号電荷12が左端部にある状態から、電圧供給により、図3Bに示すように信号電荷12が移動し始める。

さらに、電圧供給を、各電圧供給線6から順次行っていくことにより、図3C及び図3Dに示すように、図中右側、実際には水平転送レジスタ側に、信号電荷を転送していくことができる。

【0047】

また、電圧供給線6を通じて供給される電圧パルスの一形態を図4に示す。本実施の形態の固体撮像素子1では、電圧供給線6を画素(受光センサ部2)のライン毎に1本ずつ設けているので、図4では、第1ライン、第2ライン、第3ライン、・・・第nライン(水平転送レジスタ側の最終ライン)というように、「ライン」という記載にしている。

【0048】

一番水平転送レジスタから遠い第1ラインでは、最初に低いレベルの電圧V1から高いレベルの電圧V2にパルスが立ち上がる。このときシフトレジスタ11において電流Iが流れる。

以後は高いレベルの電圧V2がしばらく保持される。この間は電流が流れないので、トータルの電流量を少なくすることができる。

そして、水平転送レジスタに信号電荷12が転送されると、低いレベルの電圧V1に下がる。このときもシフトレジスタ11において電流Iが流れる。

【0049】

第2ラインでは、第1ラインよりもある時間遅れて低いレベルの電圧V1から高いレベルの電圧V2にパルスが立ち上がる。以後高いレベルの電圧V2がしばらく保持され、第1ラインと同じく水平転送レジスタに信号電荷12が転送されると、低いレベルの電圧V1に下がる。この第2ラインでも、電圧の上下の際にシフトレジスタ11において電流が流れるが、この第2ライン以降は図示を省略する。

【0050】

また、第3ラインでは、第2ラインよりもある時間遅れて低いレベルの電圧V1から高いレベルの電圧V2にパルスが立ち上がる。以後高いレベルの電圧V2がしばらく保持され、第1ラインと同じく水平転送レジスタに信号電荷12が転送されると、低いレベルの電圧V1に下がる。

そして、最終の第nラインでは、一番遅くに低いレベルの電圧V1から高いレベルの電圧V2にパルスが立ち上がり、第1ラインと同じく、水平転送レジスタに信号電荷12が転送されると低いレベルの電圧V1に下がる。

このように第1ラインから第nラインの各電圧供給線6にパルス電圧が供給されることにより、図3に示したような信号電荷12の転送が行われる。

【0051】

このようなパルス電圧により信号電荷12の転送を行うことにより、電圧パルスの上下の回数が低減されるため、信号電荷を転送する駆動に必要な電流が低減される。これは、前述したように、電圧パルスの立ち上がりの所と電圧パルスが下がる所だけ電流Iが流れるためであり、従来の1ライン送る毎に上下していた電圧パルスと比較して、大幅に電流量を低減することができる。

【0052】

具体的に印加する電圧としては、例えば、低いレベルの電圧V1を0V(接地電位)に、高いレベルの電圧V2を+5Vに、それぞれ設定することができる。

【0053】

上述の本実施の形態の固体撮像素子1の構成によれば、垂直転送レジスタ3が1枚の転送電極4により構成されていることにより、画素毎の信号電荷が1枚の長い転送電極4で転送されるため、垂直転送レジスタ3の最大電荷転送量を大きくすることができる。また、垂直転送レジスタ3において、ポテンシャルギャップ(ポテンシャル障壁)が存在しなくなり、高速、低振幅で信号電荷を転送することができる。

特に、図2に示したように電圧供給線6への電圧供給を固体撮像素子1と同一基板上に形成されたシフトレジスタ11を用いることにより、電圧供給を高速で行い、信号電荷の転送を高速に行うことができる。

このように、信号電荷の転送を高速に行うことができるため、転送中の信号電荷に偽信号(スミア)が混入されにくくなり、信号/雑音比を向上することが可能になる。

【0054】

また、電圧供給線6への電圧供給をシフトレジスタ11により行って、シフトレジスタ11から電圧供給線6に供給する電圧パルスを、図4に示したように、最初に高い電圧レベルV2に立ち上がり、高い電圧レベルV2を維持した後、垂直転送レジスタ3から水平転送レジスタに転送するときに低い電圧レベルV1に立ち下がる電圧パルスとすることが可能になる。

これにより、電流が流れるのが、パルスの立ち上げ時と立ち下げ時との合わせて2回だけになり、従来のCCD固体撮像素子の信号電荷の転送と比較して、電流量を大幅に低減することができる。

従って、固体撮像素子1の消費電力を低減することができる。

【0055】

また、転送電極4とは独立して、各受光センサ部2に対して読み出し用電極7を設けたことにより、各受光センサ部2から垂直転送レジスタ3への信号電荷の読み出しと、垂直転送レジスタ3における信号電荷の転送とをそれぞれ独立して制御することができる。

【0056】

また、読み出し用電極7を配線部8により、画素(受光センサ部2)のライン毎に接続していることにより、配線部8を通じて読み出し電圧を読み出し用電極7に印加して、ライン毎に受光センサ部2の信号電荷を読み出すことができる。このように、ライン毎に信号電荷を読み出すことにより、最大電荷転送量を大きくした垂直転送レジスタ3を利用して、各ラインの信号電荷を多く転送することができるため、受光センサ部2に蓄積される信号電荷を多くしても、読み出した信号電荷を転送することができる。

【0057】

さらに、読み出し電圧が印加される読み出し用電極7を適宜選択することにより、読み出しを行う画素の間引きや信号電荷の加算、並びに飛び越し走査等を任意に行うことができる。

【0058】

また、転送電極4が1枚の電極層で形成され、電圧供給線6から電圧が供給されている構成としているため、転送電極4を高抵抗の電極層とすることが可能になり、転送電極4の幅を縮小して抵抗が高くなることが許容される。これにより、転送電極4の幅の縮小に従って、電荷転送路である転送チャネルの幅も縮小される。

さらに、転送チャネルと転送電極4とを自己整合させて形成したことにより、特に転送チャネルの幅を縮小することができる。

従って、転送電極4及び転送チャネルの幅を縮小し、受光センサ部2の面積の相対的割合を増大させて、感度の向上を図ることができる。

【0059】

従来のCCD固体撮像素子では、遮光膜を転送電極の側面側も覆うように形成していた。

これに対して、本実施の形態の固体撮像素子1では、転送電極4が狭くなっている分、遮光膜となる電圧供給線6の遮光部の幅も小さくなっている。これにより、受光センサ部2上の開口を相対的に広くすることができ、これによっても、感度の向上を図ることができる。

【0060】

そして、前述したように、垂直転送レジスタ3の最大電荷転送量を大きくしているため、飽和出力も大きくすることができることから、固体撮像素子1を縮小化したときでも、充分な飽和出力と感度を得ることが可能になる。

【0061】

また、受光センサ部2の表面に、受光センサ部2のライン毎に接続された透明電極9を接続したことにより、この透明電極9を用いて信号電荷の掃き捨て動作をライン毎に行うことが可能になる。これにより、各ラインの受光センサ部2の蓄積時間を揃えることができる。

【0062】

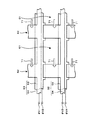

本実施の形態の固体撮像素子1は、例えば次のようにして製造することができる。製造工程の工程図を図5A〜図7Jに示すが、図5A〜図7Iは図1のA−Aにおける断面図を示し、図7Jは図1のB−Bにおける断面図を示している。

【0063】

まず、図5Aに示すように、N型のシリコン基板21の深部にP型領域22を形成し、シリコン基板21の表面側にN型領域23を形成する。なお、図5Aにおいて、シリコン基板21の表面には表面保護のための熱酸化膜24が形成されている。

【0064】

その後、表面を覆って絶縁膜(例えばシリコン酸化膜)25を厚く(例えば、膜厚30nm〜500nm)成膜し、図5Bに示すように、電荷転送路、即ち垂直転送レジスタ3となる部分のみ、絶縁膜25及び熱酸化膜24を除去する。

【0065】

次に、熱酸化等の方法を用いて、電荷転送路となる部分に、絶縁膜26を例えば膜厚5nm〜90nmで形成し、図5Cに示すように、垂直転送レジスタ3とならない部分の絶縁膜25を利用して、自己整合的に絶縁膜26の下方のシリコン基板に対して、P型領域27と、その上層のN型領域28とをそれぞれ形成する。

なお、図5C以降は熱酸化膜24の図示を省略している。

【0066】

次に、図5Dに示すように、この電荷転送路となる部分を充分に埋める膜厚(例えば、100nm〜800nm)の多結晶シリコン膜29を成膜する。この多結晶シリコン膜29は、成膜時に微量の不純物ドーピングを行う、または成膜後に不純物のイオン注入を行う、等の方法を用いて高抵抗の多結晶シリコン膜29とする。従来の固体撮像素子の転送電極の多結晶シリコン膜と比較して不純物濃度を充分小さく、例えば100分の1程度とする。

【0067】

続いて、図6Eに示すように、成膜された多結晶シリコン膜が電荷転送路とならない部分から完全に除去されるまで、エッチバック法やCMP(化学的機械的研磨)法等により、表面を平坦化する。これにより、電荷転送路となる部分に、多結晶シリコン膜29から成る転送電極4が形成される。

【0068】

次に、図6Fに示すように、転送電極4となった多結晶シリコン膜29を利用して、自己整合的に電荷転送路とならない部分の絶縁膜25を、ドライエッチング法等を用いて除去する。

【0069】

次に、図6Gに示すように、絶縁膜30を形成した後に、多結晶シリコン膜を成膜し、エッチングによりパターニングして読み出し用電極7を形成する。

このとき、パターニングにより、読み出し用電極7と共に、読み出し用電極7に連続した配線部8も同時に形成される。

【0070】

さらに、図6Hに示すように、この読み出し用電極7及び転送電極4を用いて、自己整合的にシリコン基板21の表面にイオン注入を行って、P+領域を形成し、受光センサ部2の光電変換部31を形成する。

このP+領域から成る光電変換部31の直下のN型領域23が、受光センサ部2の電荷蓄積部となる。また、読み出し用電極7の下に残ったN型領域23が読み出し領域となる。そして、転送電極4とP型領域27とN型領域28により垂直転送レジスタ3が構成される。

【0071】

次に、表面に絶縁膜(例えばシリコン酸化膜)32を成膜し、続いて光電変換部31の最表面に接続可能な部分の絶縁膜32を除去する。

続いて、透明導電材料を成膜した後に、図7Iに示すように、エッチング法等により所望の形状の透明電極9を形成する。

【0072】

次に、表面を覆って厚く絶縁膜(例えばシリコン酸化膜)33を成膜する。

続いて、転送電極4とのコンタクト部5となる所定の部分の絶縁膜33のみ、エッチングにより除去する。

その後に、転送電極4に接続して配線層(例えばアルミニウム、タングステン)を成膜し、これをパターンエッチングして、電圧供給線6及びその転送電極4とのコンタクト部5を形成する。

さらに、上層に保護絶縁膜(例えばシリコン窒化膜、シリコン窒化酸化膜)34を成膜し、図7Jに断面図を示す画素構造を得ることができる。

【0073】

上述した製造方法によれば、垂直転送レジスタ3となる部分の厚い絶縁膜25を除去して、この絶縁膜25をマスクとして用いてイオン注入により垂直転送レジスタ3の転送領域等となるP型領域27及びN型領域28を形成し、その後絶縁膜25の除去された部分に転送電極4を形成し、絶縁膜25を除去していることにより、転送電極4と垂直転送レジスタ3の転送領域等となるP型領域27及びN型領域28とを自己整合して形成することができる。

これにより、これら転送電極4と垂直転送レジスタ3の転送領域等となるP型領域27及びN型領域28とを、共に狭い幅に形成することができる。

【0074】

なお、上述の製造工程の説明では、転送電極4や読み出し用電極7等の電極層を、多結晶シリコン膜により形成する、として説明を行っているが、タングステンシリサイド等の金属材料を用いて形成してもよい。また、各絶縁膜は、シリコン酸化膜以外のシリコン窒化酸化膜、シリコン窒化膜等でもよい。

【0075】

また、上述の製造工程の説明では、シリコン基板21の表面付近に垂直転送レジスタ3のN型領域28や光電変換部31のP+領域を形成しているが、シリコン基板21の代わりにその他の半導体基板を用いたり、また半導体基板上に半導体エピタキシャル層を形成した半導体基体を用いたりすることが可能である。

これらの半導体基板や半導体基体を用いた場合も、受光センサ部や垂直転送レジスタ等の各半導体領域を形成して、固体撮像素子を形成することができる。

【0076】

なお、上述した実施の形態では、転送電極4と転送領域が自己整合して形成され、また受光センサ部2が転送電極4や読み出し用電極7と自己整合して形成されていたが、本発明の固体撮像素子では、これらが必ずしも自己整合して形成されている構成に限定されているものではなく、それぞれ個別に形成されている場合も含まれる。

【0077】

また、上述した実施の形態では、電圧供給線6が画素(受光センサ部2)の1ラインに1本ずつ設けられていたが、1ラインに2本以上設けられた構成も可能である。このように電圧供給線6の本数を多くすると、信号電荷の転送をより細かく制御することが可能になる。ただし、画素間に複数の電圧供給線6を配置することが必要になるため、画素間が厚くなる。

いずれの本数にする場合においても、電圧供給線6と転送電極4とのコンタクト部5の間隔は、ほぼ一定間隔にすることが望ましい。

【0078】

上述の実施の形態では、受光センサ部2の最終ラインからすぐに水平転送レジスタに信号電荷が転送される構成、即ちIT(インターライン)方式の固体撮像素子の構成として、信号電荷の転送の説明を行ったが、IT方式に限らず、受光センサ部2の最終ラインと水平転送レジスタとの間に電荷蓄積領域が設けられている構成、即ちFIT(フレームインターライン)方式の固体撮像素子にも、同様に本発明を適用することができる。

【0079】

本発明は、上述の実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲でその他様々な構成が取り得る。

【0080】

【発明の効果】

上述の本発明の固体撮像素子によれば、最大電荷転送量を減少させることなく、単位画素面積に対する電荷転送路の面積を小さくすることができる。

これにより、受光センサ部(光電変換領域、電荷蓄積領域)を拡大して、感度の向上を図ることができるため、最大電荷蓄積量が大きく、かつ感度が高い固体撮像素子を実現することができる。

【0081】

また、垂直電荷転送部を1枚の電荷転送電極により構成しているため、電荷転送効率を低下させることなく、高速で信号電荷の転送を行うことが可能となるため、電荷転送中に偽信号(スミア)が混入されにくくなり、信号/雑音比を向上することができる。

このように高速で信号電荷の転送を行うことができ、スミアが少なくなるため、遮光膜を従来の固体撮像素子よりも小さくすることが可能になる。

【0082】

さらに、各受光センサ部の表面に透明電極が接続され、この透明電極が受光センサ部の各行毎に連続して形成されている構成としたときには、読み出し用電極と透明電極とによって、信号電荷の読み出し及び余剰電荷の掃き出しを任意の行毎に行うことができるため、飛び越し走査、信号電荷の加算、間引き読み出し等の特殊な走査を容易に行うことができる。

【0083】

上述の本発明の固体撮像素子の製造方法によれば、垂直電荷転送部の転送電極と転送領域とを自己整合して形成することができ、これらを共に狭い幅に形成することができる。

【図面の簡単な説明】

【図1】本発明の固体撮像素子の一実施の形態の概略構成図(平面図)である。

【図2】図1の固体撮像素子の模式的平面図である。

【図3】A〜D 図1の固体撮像素子の垂直転送レジスタにおける信号電荷の転送を示す図である。

【図4】転送電極へ各ラインの電圧供給線を通じて供給される電圧パルスの一形態を示す図である。

【図5】A〜D 図1の固体撮像素子の製造工程を示す工程図である。

【図6】E〜H 図1の固体撮像素子の製造工程を示す工程図である。

【図7】I、J 図1の固体撮像素子の製造工程を示す工程図である。

【図8】従来の固体撮像素子の模式的平面図である。

【図9】A 図8の固体撮像素子の垂直転送レジスタに沿った断面図である。

B〜H 図8の固体撮像素子の垂直転送レジスタにおける信号電荷の転送を示す図である。

【符号の説明】

1 固体撮像素子、2 受光センサ部、3 垂直転送レジスタ、4 転送電極、5,10 コンタクト部、6 電圧供給線、7 読み出し用電極、9 透明電極、11 シフトレジスタ、12 信号電荷

Claims (4)

- 画素を構成する受光センサ部が多数マトリクス状に配置され、

前記受光センサ部の各列に対して、それぞれ垂直方向に延びる垂直電荷転送部が設けられた固体撮像素子であって、

各前記垂直電荷転送部が、半導体基体内に形成された転送領域と、前記転送領域が形成された部分の前記半導体基体上に絶縁膜を介して形成された1枚の垂直転送電極とにより構成され、

前記垂直電荷転送部の転送領域と前記垂直転送電極とが同じ幅に形成され、

各前記垂直電荷転送部の前記受光センサ部と対向する部分に、前記受光センサ部から信号電荷を読み出すための読み出し用電極が、前記垂直電荷転送部の前記垂直転送電極とは独立して設けられ、

前記読み出し用電極が、前記受光センサ部の各行毎に電気的に接続され、

前記垂直転送電極に一定間隔で電圧供給部が設けられ、前記電圧供給部を通じて、前記垂直転送電極の一部分に電圧が供給される

固体撮像素子。 - 各前記受光センサ部の表面に透明電極が接続され、前記透明電極が前記受光センサ部の各行毎に連続して形成されている請求項1に記載の固体撮像素子。

- 前記垂直転送電極に設けられた前記電圧供給部が、前記受光センサ部と同一基板に形成されたシフトレジスタに電気的に接続されている請求項1に記載の固体撮像素子。

- 画素を構成する受光センサ部が多数マトリクス状に配置され、

前記受光センサ部の各列に対して、それぞれ垂直方向に延びる垂直電荷転送部が設けられ、

各前記垂直電荷転送部が1枚の垂直転送電極により構成された固体撮像素子を製造する方法であって、

半導体基体上に絶縁層を形成し、前記垂直電荷転送部となる部分の前記絶縁層を除去する工程と、

前記絶縁層をマスクとして用いて、前記半導体基体にイオン注入により前記垂直電荷転送部の転送領域となる半導体領域を形成する工程と、

その後、前記絶縁層の除去された部分に、前記垂直電荷転送部の前記垂直転送電極を形成する工程と、

前記絶縁層を除去する工程とを少なくとも有する

固体撮像素子の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003091697A JP4457570B2 (ja) | 2003-03-28 | 2003-03-28 | 固体撮像素子及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003091697A JP4457570B2 (ja) | 2003-03-28 | 2003-03-28 | 固体撮像素子及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004303773A JP2004303773A (ja) | 2004-10-28 |

| JP4457570B2 true JP4457570B2 (ja) | 2010-04-28 |

Family

ID=33405008

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003091697A Expired - Fee Related JP4457570B2 (ja) | 2003-03-28 | 2003-03-28 | 固体撮像素子及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4457570B2 (ja) |

-

2003

- 2003-03-28 JP JP2003091697A patent/JP4457570B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004303773A (ja) | 2004-10-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20020047139A1 (en) | Solid state image pickup device and its driving method | |

| TWI521689B (zh) | 利用電荷積分的多重線性影像感測器 | |

| US8847285B2 (en) | Depleted charge-multiplying CCD image sensor | |

| JP2008192813A (ja) | Ccd固体撮像素子 | |

| KR101159032B1 (ko) | 고체 촬상 소자 | |

| JP2007299840A (ja) | Ccd型固体撮像素子及びその製造方法 | |

| JP4457570B2 (ja) | 固体撮像素子及びその製造方法 | |

| US6846695B2 (en) | Solid state imaging device and method for manufacturing the same | |

| US7321392B2 (en) | Solid state imaging device with lateral overflow drain and driving method thereof achieving low power consumption | |

| JP3718103B2 (ja) | 固体撮像装置とその駆動方法、およびこれを用いたカメラ | |

| JP2002043559A (ja) | 固体撮像装置およびその駆動方法 | |

| JP5030323B2 (ja) | 固体撮像素子 | |

| CN101728410B (zh) | 固态摄像元件、固态摄像装置及其制造方法 | |

| JP2002151673A (ja) | 固体撮像素子 | |

| JP4867226B2 (ja) | 固体撮像装置およびその製造方法、並びにカメラ | |

| JP2897689B2 (ja) | 固体撮像装置 | |

| JP3047965B2 (ja) | 固体撮像装置 | |

| JP3028823B2 (ja) | 電荷結合素子およびこれを用いた固体撮像装置 | |

| JP7765306B2 (ja) | 固体撮像素子 | |

| JP4295702B2 (ja) | 固体撮像装置及び固体撮像装置の駆動方法 | |

| JP2003060188A (ja) | 固体撮像素子及びその駆動方法 | |

| JP2002208692A (ja) | 固体撮像素子 | |

| JPH09181292A (ja) | 固体撮像素子とその駆動方法 | |

| JP2004031966A (ja) | 固体撮像素子 | |

| JP2004247696A (ja) | 固体撮像素子、固体撮像素子の製造方法及び固体撮像素子の駆動方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20051027 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090119 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090127 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090330 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100119 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100201 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130219 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |