JP4312466B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4312466B2 JP4312466B2 JP2003018377A JP2003018377A JP4312466B2 JP 4312466 B2 JP4312466 B2 JP 4312466B2 JP 2003018377 A JP2003018377 A JP 2003018377A JP 2003018377 A JP2003018377 A JP 2003018377A JP 4312466 B2 JP4312466 B2 JP 4312466B2

- Authority

- JP

- Japan

- Prior art keywords

- laser

- film

- insulating film

- semiconductor film

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Description

【発明の属する技術分野】

本発明は、結晶構造を有する半導体膜を用いて形成される半導体装置及びその作製方法に係り、絶縁表面上に形成された結晶性半導体膜でチャネル形成領域を含む島状の半導体領域を形成した電界効果型トランジスタ、特に薄膜トランジスタを含む半導体装置及びその作製方法に関する。

【0002】

【従来の技術】

近年、基板上にTFTを形成する技術が大幅に進歩し、アクティブマトリクス型の半導体表示装置への応用開発が進められている。特に、多結晶半導体膜を用いたTFTは、従来の非晶質半導体膜を用いたTFTよりも電界効果移動度(モビリティともいう)が高いので、高速動作が可能である。そのため、従来基板の外に設けられた駆動回路で行っていた画素の制御を、画素と同一の基板上に形成した駆動回路で行うことが可能である。

【0003】

ところで半導体装置に用いる基板は、コストの面から単結晶シリコン基板よりも、ガラス基板が有望視されている。そしてガラス等による絶縁基板上に非晶質珪素膜を形成し、レーザ処理により結晶化させる技術が知られている。ガラス基板は耐熱性に劣り、熱変形しやすい。そのため、ガラス基板上にポリシリコンTFTを形成する場合において、半導体膜の結晶化にレーザアニールを用いることは、ガラス基板の熱変形を避けるのに非常に有効である。その結晶性珪素膜を用いて作製される薄膜トランジスタ(以下、TFTと記す)は、例えば、液晶表示装置等に応用されている。

【0004】

レーザアニールの特徴は、輻射加熱或いは伝導加熱を利用するアニール法と比較して処理時間を大幅に短縮できることや、半導体又は半導体膜を選択的、局所的に加熱して、基板に殆ど熱的損傷を与えないことなどが上げられている。

【0005】

なお、ここでいうレーザアニール法とは、半導体基板又は半導体膜に形成された損傷層を再結晶化する技術や、基板上に形成された半導体膜を結晶化させる技術、結晶構造を有する半導体膜(結晶性半導体膜)の結晶性を向上させる技術等を指している。また、半導体基板又は半導体膜の平坦化や表面改質に適用される技術も含んでいる。適用されるレーザ発振装置は、エキシマレーザに代表される気体レーザ発振装置、YAGレーザに代表される固体レーザ発振装置であり、レーザ光の照射によって半導体の表面層を数十ナノ〜数十マイクロ秒程度のごく短時間加熱して結晶化させるものとして知られている。

【0006】

レーザ光の照射による非晶質半導体膜の結晶化の一例は、下記特許文献1で開示されているように、レーザ光の走査速度をビームスポット径×5000/秒以上として高速走査により非晶質半導体膜を完全な溶融状態に至らしめることなく多結晶化するものや、下記特許文献2には島状に形成された半導体領域に、引き延ばされたレーザ光を照射して実質に単結晶領域を形成する技術が開示されている。或いは下記特許文献3に開示のレーザ処理装置のように光学系にて線状にビームを加工して照射する方法が知られている。

【0007】

さらに、下記特許文献4に開示されているようにNd:YVO4レーザなど固体レーザ発振装置を用いて、その第2高調波であるレーザ光を非晶質半導体膜に照射して、従来に比べ結晶粒径の大きい結晶性半導体膜を形成し、TFTを作製する技術が開示されている。

【0008】

【特許文献1】

特開昭62−104117号公報(第92頁)

【0009】

【特許文献2】

米国特許4,330,363号明細書(Fig.4)

【0010】

【特許文献3】

特開平8−195357号公報(第3−4頁、第1−5図)

【0011】

【特許文献4】

特開2001−144027号公報(第4頁)

【0012】

絶縁表面上に単結晶半導体膜を形成する試みは古くから成され、より積極的な試みとしてグラフォエピタキシー(graphoepitaxy)という技術が考案されている。グラフォエピタキシーは石英基板の表面に段差を形成し、この上に非晶質半導体膜又は多結晶半導体膜を形成してから、レーザービームやヒーターで加熱させ、石英基板上に形成された段差形状を核として、エピタキシャル的な成長層を形成するという技術である。この技術は例えば非特許文献1等に開示されている。

【0013】

【非特許文献1】

J. Vac. Sci. Technol.,"Grapho-epitaxy of silicon on fused silica using surface micropatterns and laser crystallization", 16(6),1979,pp1640-1643.

【0014】

また、例えば非特許文献2にも、グラフォエピタキシーと呼ばれる半導体膜の結晶化技術について開示されている。これは人為的に作られた非晶質基板表面のレリーフ格子(surface relief grating)の誘導によって半導体膜のエピ成長を試みるものであった。上記非特許文献3には、グラフォエピタキシーの技術とは、絶縁膜の表面に段差を設け、該絶縁膜上に形成された半導体膜に加熱又はレーザー光の照射等の処理を施すことで、該半導体膜の結晶をエピタキシャル成長させることが開示されている。

【0015】

【非特許文献2】

M. W. Geis, et al.,"CRYSTALLINE SILICON ON INSULATORS BY GRAPHOEPITAXY" Technical Digest of International Electron Devices Meeting, 1979, pp.210.

【0016】

【発明が解決しようとする課題】

レーザはその発振方法により、パルス発振と連続発振の2種類に大別される。パルス発振のレーザは出力エネルギーが比較的高いため、レーザビームの大きさを数cm2以上として量産性を上げることができる。特に、レーザビームの形状を光学系を用いて加工し、長さ10cm以上の線状にすると、基板へのレーザ光の照射を効率的に行うことができ、量産性をさらに高めることができる。そのため、半導体膜の結晶化には、パルス発振のレーザを用いるのが主流となりつつあった。

【0017】

しかし近年では、半導体膜の結晶化においてパルス発振のレーザよりも連続発振のレーザを用いる方が、半導体膜内に形成される結晶の粒径が大きくなることが見出された。半導体膜内の結晶粒径が大きくなると、該半導体膜を用いて形成されるTFTの移動度が高くなる。そのため、連続発振のレーザはにわかに脚光を浴び始めている。

【0018】

パルス発振と連続発振とに大別されるレーザアニール法を用いて作製される結晶性半導体膜は、一般的に複数の結晶粒が集合して形成される。その結晶粒の位置と大きさはランダムなものであり、結晶粒の位置や大きさを指定して結晶性半導体膜を形成する事は難しい。そのため前記結晶性半導体膜を島状にパターニングすることで形成された活性層中には、結晶粒の界面(粒界)が存在することがある。

【0019】

結晶粒内と異なり、粒界には非晶質構造や結晶欠陥などに起因する再結合中心や捕獲中心が無数に存在している。この捕獲中心にキャリアがトラップされると、粒界のポテンシャルが上昇し、キャリアに対して障壁となるため、キャリアの電流輸送特性が低下することが知られている。よって、TFTの活性層、特にチャネル形成領域中に粒界が存在すると、TFTの移動度が著しく低下したり、オン電流が低減したり、また粒界において電流が流れるためにオフ電流が増加したりと、TFTの特性に重大な影響を及ぼす。また同じ特性が得られることを前提に作製された複数のTFTにおいて、活性層中の粒界の有無によって特性がばらついたりする。

【0020】

半導体膜にレーザ光を照射したときに、得られる結晶粒の位置と大きさがランダムになるのは、以下の理由による。レーザ光の照射によって完全溶融した液体半導体膜中に固相核生成が発生するまでには、ある程度の時間が掛かる。そして時間の経過と共に、完全溶融領域において無数の結晶核が発生し、該結晶核からそれぞれ結晶が成長する。この結晶核の発生する位置は無作為であるため、不均一に結晶核が分布する。そして、互いの結晶粒がぶつかり合ったところで結晶成長が終了するため、結晶粒の位置と大きさはランダムなものとなる。

【0021】

よって、TFTの特性に重大な影響を及ぼすチャネル形成領域を、粒界の影響を排除して単一の結晶粒で形成することが理想的であるが、粒界の存在しない結晶質珪素膜をレーザアニール法で形成するのは殆ど不可能であった。そのためレーザアニール法を用いて結晶化された結晶質珪素膜を活性層とするTFTで、単結晶シリコン基板に作製されるMOSトランジスタの特性と同等なものは、今日まで得られていない。

【0022】

欠陥や結晶粒界又は結晶亜粒界が少なく、且つ、配向の揃った高品質の結晶性半導体膜を絶縁表面上に形成するためには、帯域溶融法などとして知られているように単結晶基板上の半導体膜を高温に加熱して溶融状態としてから再結晶化する方法が主流であった。

【0023】

公知のグラフォエピタキシー技術のように下地の段差を利用しているので、その段差に沿って結晶が成長し、形成された単結晶半導体膜の表面にその段差が残ることが問題であると考えられている。さらに、歪み点が比較的低いガラス基板上にグラフォエピタキシーを用いて単結晶半導体膜を形成することは出来なかった。

【0024】

いずれにしても、結晶化によって起こる半導体の体積収縮、下地との熱応力や格子不整合などによる欠陥、結晶粒界又は亜粒界の存在しない結晶性半導体膜を形成することは出来なかった。よって、張り合わせSOI(Silicon on Insulator)を省いては、絶縁表面上に形成され、結晶化又は再結晶化された結晶性半導体膜をもって、単結晶基板に形成されるMOSトランジスタと同等の品質を得ることはできなかった。

【0025】

本発明は上記問題点に鑑みなされたものであり、絶縁表面上に、少なくともチャネル長方向と交差する結晶粒界又は結晶亜粒界が可能な限り存在しない結晶性半導体膜を形成し、高速で電流駆動能力の高い半導体素子により構成される半導体装置の提供を課題とする。

【0026】

またTFTのチャネル形成領域に粒界が形成されるのを防ぎ、粒界によってTFTの移動度が著しく低下したり、オン電流が低減したり、オフ電流が増加したりするのを防ぐことができるレーザ結晶化法を用いた、半導体装置の作製方法及び該作製方法を用いて作製された半導体装置の提供を課題とする。

【0027】

【課題を解決するための手段】

本発明者らは、凹凸を有する絶縁膜上に半導体膜を形成し、該半導体膜にレーザ光を照射すると、結晶化された半導体膜の、絶縁膜の凸部上に位置する部分において選択的に粒界が形成されることを見出した。

【0028】

図19に、凹凸を有する絶縁膜上に形成された200nmの非単結晶半導体膜に、連続発振のレーザ光を走査速度が5cm/secとなるように照射したときの、レーザ光の走査方向と垂直な方向におけるTEMの断面像を示す。図19(A)において、8001及び8002は絶縁膜に形成された凸部である。そして結晶化された半導体膜8004は、凸部8001、8002の上部において粒界8003を有している。

【0029】

図19(B)に、図19(A)に示したTEMの断面像を模式的に図示する。図19(B)に示すとおり、凸部8001、8002の上部において粒界8003が形成されている。本発明者らは、これはレーザ光の照射により一次的に半導体膜が溶融することで、絶縁膜の上部に位置していた半導体膜が凹部の底部方向に向かって体積移動し、そのため凸部の上に位置する半導体膜が薄くなり、応力に耐えられなくて粒界が生じたのではないかと考えた。そして、このように結晶化された半導体膜は、凸部の上部において粒界が選択的に形成される一方、凹部(点線で示す領域)8001、8002に位置する部分には粒界が形成されにくい。なお凹部は、凸部が形成されていない窪んだ領域を指す。

【0030】

そこで本発明者らは、意図的に該半導体膜に応力が集中的にかかる部分を形成することで、粒界が形成される位置を選択的に定めることができるのではないかと考えた。本発明では、基板上に凹凸を設けた絶縁膜を形成し、該絶縁膜上に半導体膜を形成することで、レーザ光による結晶化の際に、該半導体膜に応力が集中的にかかる部分を選択的に形成する。具体的には、該半導体膜に凹凸を設ける。そして、該半導体膜に形成された凹凸の長手方向に沿って、連続発振のレーザ光を照射する。なおこのとき、連続発振のレーザ光を用いるのが最も好ましいが、パルス発振のレーザ光を用いても良い。なおレーザ光の走査方向に対して垂直な方向における凸部の断面は、矩形、三角形または台形であっても良い。

【0031】

上記構成により、レーザ光の照射による結晶化の際、半導体膜の凸部上において粒界が選択的に形成される。そして絶縁膜の凹部上に位置する半導体膜は比較的粒界が形成されにくい、絶縁膜の凹部上に位置する半導体膜は結晶性が優れているが、必ずしも粒界を含まないわけではない。しかし、たとえ粒界が存在したとしても絶縁膜の凸部上に位置する半導体膜に比較すると、その結晶粒は大きく、結晶性が比較的優れたものと言える。よって、絶縁膜の形状を設計した段階で、半導体膜の粒界の形成される位置をある程度予測することができる。つまり本発明では粒界が形成される位置を選択的に定めることができるので、活性層、より望ましくはチャネル形成領域に粒界がなるべく含まれないように、活性層をレイアウトすることが可能になる。

【0032】

本発明では、絶縁膜の凹部上に位置する半導体膜を、TFTの活性層として積極的に用いることで、TFTのチャネル形成領域に粒界が形成されるのを防ぐことができ、粒界によってTFTの移動度が著しく低下したり、オン電流が低減したり、オフ電流が増加したりするのを防ぐことができる。なお、どこまでを凸部または凹部のエッジ近傍としてパターニングで除去するかは、設計者が適宜定めることができる。

【0033】

また上記問題点を解決するために本発明は、絶縁表面を有する基板上に開口部が設けられた絶縁膜を形成し、絶縁膜及び該開口部に非単結晶半導体膜を形成し、非単結晶半導体膜を溶融して結晶化又は再結晶化することにより、その開口部を充填する形態で結晶性半導体膜を形成するものであり、該開口部を充填する結晶性半導体膜とゲート電極とがゲート絶縁膜を介して重畳するように形成する各段階を有することを特徴とするものである。

【0034】

当該開口部は絶縁基板の表面をエッチング処理して形成しても良いし、酸化珪素、窒化珪素、又は酸窒化珪素膜等を用い、それをエッチング処理して開口部を形成しても良い。開口部は、薄膜トランジスタのチャネル形成領域を含む島状の半導体領域の配置に合わせて形成されるべきものであり、少なくともチャネル形成領域に合致するように形成されていることが望ましい。

【0035】

非単結晶半導体膜は、プラズマCVD法、スパッタリング法、減圧CVD法で形成される非晶質半導体膜又は多結晶半導体膜、或いは、固相成長により形成された多結晶半導体膜などが適用される。尚、本発明でいう非晶質半導体膜とは、狭義の意味で完全な非晶質構造を有するものだけではなく、微細な結晶粒子が含まれた状態、又はいわゆる微結晶半導体膜、局所的に結晶構造を含む半導体膜を含む。代表的には非晶質シリコン膜が適用され、その他に非晶質シリコンゲルマニウム膜、非晶質シリコンカーバイト膜などを適用することもできる。

【0036】

非単結晶半導体膜を溶融して結晶化させる手段としては、気体レーザ発振装置、固体レーザ発振装置を光源とするパルス発振又は連続発振レーザ光を適用する。照射するレーザ光は光学系にて線状に集光されたものであり、その強度分布が長手方向において均一な領域を有し、短手方向に分布を持っていても良く、光源として用いるレーザ発振装置は、矩形ビーム固体レーザ発振装置が適用され、特に好ましくは、スラブレーザ発振装置が適用される。或いは、Nd、Yb、Tm、Hoをドープしたロッドを用いた固体レーザ発振装置であり、特にYAG、YVO4、YLF、YAlO3などの結晶にNd、Tm、Hoをドープした結晶を使った固体レーザ発振装置にスラブ構造増幅器を組み合わせたものでも良い。スラブ材料としては、Nd:YAG、Nd:GGG(ガドリニウム・ガリウム・ガーネット)、Nd:GsGG(ガドリニウム・スカンジウム・ガリウム・ガーネット)等の結晶が使用される。スラブレーザでは、この板状のレーザ媒質の中を、全反射を繰り返しながらジグザグ光路で進む。

【0037】

また、それに準ずる強光を照射しても良い。例えば、ハロゲンランプ、キセノンランプ、高圧水銀灯、メタルハライドランプ、エキシマランプから放射される光を反射鏡やレンズ等により集光したエネルギー密度の高い光であっても良い。

【0038】

線状に集光及び拡張されたレーザ光又は強光は非単結晶半導体膜に照射し、かつ、レーザ光の照射位置と単結晶半導体膜が形成された基板とを相対的に動かして、レーザ光が一部又は全面を走査することにより非単結晶半導体膜の溶融と結晶化又は再結晶化が成される。レーザ光の走査方向は、開口部の長手方向又はチャネル長方向に沿って行うのが望ましい。これによりレーザ光の走査方向に沿って結晶が成長し、結晶粒界又は結晶亜粒界がチャネル長方向と交差することを防ぐことができる。しかし本発明は必ずしもこれに限定されない。

【0039】

上記の如く作製される本発明の半導体装置は、絶縁表面を有する基板上に開口部が形成された絶縁膜が設けられ、基板上に形成された結晶性半導体膜は前記開口部を充填する領域を有し、当該充填領域にチャネル形成領域が備えられていることを特徴としている。

【0040】

また他の構成は、絶縁表面を有する基板上にチャネル長方向に延在する開口部が形成された絶縁膜が設けられ、基板上に形成された結晶性半導体膜は前記開口部を充填する領域を有し、当該充填領域にチャネル形成領域が備えられていて、開口部は前記結晶性半導体膜と同じかそれ以上の深さを有していることを特徴としている。

【0041】

また他の構成は、絶縁表面に形成された矩形又は帯状に延在する開口部に結晶性半導体が設けられていて、結晶性半導体とゲート電極とがゲート絶縁膜を介して重畳していることを特徴としている。

【0042】

また他の構成は、絶縁表面に形成されたチャネル長方向に延在する開口部に結晶性半導体が設けられていて、結晶性半導体とゲート電極とがゲート絶縁膜を介して重畳していることを特徴としている。

【0043】

開口部の深さを半導体膜の厚さと同程度かそれ以上とすることにより、レーザ光又は強光の照射により溶融した半導体が表面張力により開口部(即ち凹部)に凝集して固化する。その結果、凸部にある半導体膜の厚さは薄くなり、そこに応力歪みを集中させることができる。また開口部の側面は結晶方位をある程度規定する効力を持つ。開口部の側面の角度は基板表面に対して5〜120度、好ましくは80〜100度で形成する。

【0044】

半導体膜がレーザ光又は強光の照射により溶融した後、固化を開始するのは開口部の底面と側面とが交わる領域からであり、ここから結晶成長が始まる。例えば、図17に示すように絶縁膜(1)と絶縁膜(2)により段差形状が形成された系においてA〜D点における熱解析シミュレーションを行った結果、図18のような特性が得られている。熱の逃げる場所として▲1▼直下の絶縁膜(2)と側面に存在する絶縁膜(1)の両方があるため、B点が最も早く温度が下がることになる。以降、A点、C点、D点の順である。このシミュレーション結果は側壁の角度が45度の場合であるが、90度の場合にも定性的には同様な現象が考えられる。

【0045】

即ち、半導体膜を一旦溶融状態とし、表面張力により絶縁表面上に形成した開口部に凝集させ、開口部の底部と側壁の概略交点から結晶成長させることにより結晶化に伴い発生する歪みを開口部以外の領域に集中させることができる。即ち、開口部に充填されるように形成した結晶性半導体膜においては歪みから開放することができる。

【0046】

なお、レーザ光のレーザビームのエッジの近傍は、中央付近に比べて一般的にエネルギー密度が低く、半導体膜の結晶性も劣る場合が多い。そのためレーザ光を走査する際に、後にTFTのチャネル形成領域となる部分と、その軌跡のエッジとが重ならないようにするのが望ましい。

【0047】

そこで本発明では、まず設計の段階で得られた、基板上面から見た絶縁膜または半導体膜の形状のデータ(パターン情報)を記憶手段に記憶する。そしてそのパターン情報と、レーザ光のレーザビームの走査方向と垂直な方向における幅とから、少なくともTFTのチャネル形成領域となる部分と、レーザ光の軌跡のエッジとが重ならないように、レーザ光の走査経路を決定する。そして、マーカーを基準として基板の位置を合わせ、決定された走査経路にしたがってレーザ光を基板上の半導体膜に対して照射する。

【0048】

上記構成により、基板全体にレーザ光を照射するのではなく、少なくとも必要不可欠な部分にのみレーザ光を走査するようにすることができる。よって、不必要な部分にレーザ光を照射するための時間を省くことができ、よって、レーザ光照射にかかる時間を短縮化することができ、なおかつ基板の処理速度を向上させることができる。また不必要な部分にレーザ光を照射し、基板にダメージが与えられるのを防ぐことができる。

【0049】

なお、マーカーは、基板を直接レーザ光等によりエッチングすることで形成しても良いし、凹凸を有する絶縁膜を形成する際に、同時に絶縁膜の一部にマーカーを形成するようにしても良い。また、実際に形成された絶縁膜または半導体膜の形状をCCD等の撮像素子を用いて読み取り、データとして第1の記憶手段に記憶し、第2の記憶手段に設計の段階で得られた絶縁膜または半導体膜のパターン情報を記憶し、第1の記憶手段に記憶されているデータと、第2の記憶手段に記憶されているパターン情報とを照合することで、基板の位置合わせを行うようにしても良い。

【0050】

絶縁膜の一部にマーカーを形成したり、絶縁膜の形状をマーカーとして用いることで、マーカー用のマスクを1枚減らすことができ、なおかつ基板にレーザ光で形成するよりも、正確な位置にマーカーを形成することができ、位置合わせの精度を向上させることができる。

【0051】

なお、レーザ光のエネルギー密度は、一般的には完全に均一ではなく、レーザビーム内の位置によりその高さが変わる。本発明では、最低限チャネル形成領域となる部分、より好ましくは凹部の平らな面全体または凸部の平らな面全体に、一定のエネルギー密度のレーザ光を照射することが必要である。よって本発明では、レーザ光の走査により、均一なエネルギー密度を有する領域が、最低限チャネル形成領域となる部分、より好ましくは凹部の平らな面全体または凸部の平らな面全体と完全に重なるような、エネルギー密度の分布を有するレーザビームを用いることが必要である。上記エネルギー密度の条件を満たすためには、レーザビームの形状を、矩形または線形等にすることが望ましいと考えられる。

【0052】

さらにスリットを介し、レーザビームのうちエネルギー密度の低い部分を遮蔽するようにしても良い。スリットを用いることで、比較的均一なエネルギー密度のレーザ光を凹部の平らな面全体または凸部の平らな面全体に照射することができ、結晶化を均一に行うことができる。またスリットを設けることで、絶縁膜または半導体膜のパターン情報によって部分的にレーザビームの幅を変えることができ、チャネル形成領域、さらにはTFTの活性層のレイアウトにおける制約を小さくすることができる。なおレーザビームの幅とは、走査方向と垂直な方向におけるレーザビームの長さを意味する。

【0053】

また複数のレーザ発振装置から発振されたレーザ光を合成することで得られた1つのレーザビームを、レーザ結晶化に用いても良い。上記構成により、各レーザ光のエネルギー密度の低い部分を補い合うことができる。

【0054】

また半導体膜を成膜した後、大気に曝さないように(例えば希ガス、窒素、酸素等の特定されたガス雰囲気または減圧雰囲気にする)レーザ光の照射を行い、半導体膜を結晶化させても良い。上記構成により、クリーンルーム内における分子レベルでの汚染物質、例えば空気の清浄度を高めるためのフィルター内に含まれるボロン等が、レーザ光による結晶化の際に半導体膜に混入するのを防ぐことができる。

【0055】

なお、従来のグラフォエピタキシー(graphoepitaxy)と呼ばれる半導体膜の結晶化技術は、人為的に作られた非晶質基板表面のレリーフ格子(surface relief grating)の誘導によって半導体膜のエピ成長を試みるものであった。このグラフォエピタキシーに関する技術は、上記非特許文献2等に記載されている。上記論文等には、グラフォエピタキシーの技術とは、絶縁膜の表面に段差を設け、該絶縁膜上に形成された半導体膜に加熱又はレーザ光の照射等の処理を施すことで、該半導体膜の結晶をエピタキシャル成長させることが開示されている。しかし、エピタキシャル成長に必要な温度は、少なくとも700℃程度は必要であり、ガラス基板上においてエピタキシャル成長を行おうとすると、絶縁膜の凹部または凸部のエッジ近傍において半導体膜に粒界が形成されてしまう。本発明では、アイランドのマスクをレイアウトして、該アイランドとなる部分における結晶性を高められるように、絶縁膜の凹部または凸部の形状及びエッジの位置を、アイランドのレイアウトに合わせて設計する。具体的には凹部または凸部のエッジ及び凹部または凸部のエッジ間の中央付近と、アイランドとが重ならないように、凹部または凸部の形状、サイズ等を定める。そしてアイランドのレイアウトに合わせて設計された絶縁膜を用い、意図的に粒界の位置を選択的に定める。そして該半導体膜の選択的に形成された粒界の存在する部分をパターニングにより除去し、結晶性の比較的優れている部分をアイランドとして用いる。よって本発明において開示する技術は、従来のグラフォエピタキシーと、段差を設けた絶縁膜上に半導体膜を形成し、該段差を用いて半導体膜を結晶化させる点では一致しているが、従来のグラフォエピタキシーには段差を用いて粒界の位置を制御し、アイランド内の粒界を少なくするという概念は含まれておらず、本発明とは似て非なるものである。

【0056】

【発明の実施の形態】

以下、図面を参照して本発明の実施の態様について説明する。図1において示す斜視図は、基板101上に第1絶縁膜102と帯状にパターン形成された第2絶縁膜103〜105が形成された形態を示している。ここでは、第2絶縁膜による帯状のパターンが3本示されているが、勿論その数に限定されることはない。基板は市販の無アルカリガラス基板、石英基板、サファイア基板、単結晶又は多結晶半導体基板の表面を絶縁膜で被覆した基板、金属基板の表面を絶縁膜で被覆した基板を適用することができる。

【0057】

帯状に形成される第2絶縁膜の幅W1は0.1〜10μm(好ましくは0.5〜1μm)隣接する第2絶縁膜の間隔W2は0.1〜5μm(好ましくは0.5〜1μm)であり、第2絶縁膜の厚さdはその上に形成する非単結晶半導体膜の厚さと同程度かそれ以上の厚さをもって形成する。また、段差形状は規則的な周期パターンである必要はなく、TFTのチャネル形成領域を含む島状の半導体領域の配置及び形状に合わせて形成すれば良い。よって、第2絶縁膜の長さLも限定はなく、例えばTFTのチャネル形成領域を形成することができる程度の長さがあれば良い。

【0058】

第1絶縁膜は、窒化珪素又は窒酸化珪素を用いて形成する。また、第2絶縁膜は酸化珪素又は酸窒化珪素を用いて形成する。酸化珪素はオルトケイ酸テトラエチル(Tetraethyl Ortho Silicate:TEOS)とO2とを混合しプラズマCVD法で形成することができる。窒酸化珪素膜はSiH4、NH3、N2O又は、SiH4、N2Oを原料として用いプラズマCVD法で形成することができる。

【0059】

図1の形態であるように、開口部による凹凸形状を第1絶縁膜と第2絶縁膜により形成する場合には、エッチング加工における選択比を確保するために、第2絶縁膜のエッチング速度が相対的に早くなるように材料及び成膜条件を適宜調整することが望ましい。そして、第2絶縁膜で形成される開口部の側壁の角度は5〜120度、好ましくは80〜100度の範囲で適宜設定すれば良い。

【0060】

図2で示すように、この第1絶縁膜102と第2絶縁膜103〜105から成る表面上および開口部を覆う非晶質半導体膜106を50〜200nmの厚さに形成する。非晶質半導体膜は、珪素、珪素とゲルマニウムの化合物又は合金、珪素と炭素の化合物又は合金を適用することができる。

【0061】

そして、この非晶質半導体膜106に連続発振レーザ光を照射して結晶化を行う。適用されるレーザ光は光学系にて線状に集光及び拡張されたものであり、その強度分布が長手方向において均一な領域を有し、短手方向に分布を持っていても良く、光源として用いるレーザ発振装置は、矩形ビーム固体レーザ発振装置が適用され、特に好ましくは、スラブレーザ発振装置が適用される。或いは、Nd、Tm、Hoをドープしたロッドを用いた固体レーザ発振装置であり、特にYAG、YVO4、YLF、YAlO3などの結晶にNd、Tm、Hoをドープした結晶を使った固体レーザ発振装置にスラブ構造増幅器を組み合わせたものでも良い。そして、図中に矢印で示すように、線状の長手方向に対し交差する方向に走査する。この時、下地絶縁膜に形成される帯状のパターンの長手方向と平行な方向に走査することが最も望ましい。尚、ここでいう線状とは、短手方向の長さに対し、長手方向の長さの比が1対10以上のものをもって言う。

【0062】

スラブ材料としては、Nd:YAG、Nd:GGG(ガドリニウム・ガリウム・ガーネット)、Nd:GsGG(ガドリニウム・スカンジウム・ガリウム・ガーネット)等の結晶が使用される。スラブレーザでは、この板状のレーザ媒質の中を、全反射を繰り返しながらジグザグ光路で進む。

【0063】

また、連続発振レーザ光の波長は、非晶質半導体膜の光吸収係数を考慮して400〜700nmであることが望ましい。このような波長帯の光は、波長変換素子を用いて基本波の第2高調波、第3高調波を取り出すことで得られる。波長変換素子としてはADP(リン酸二水素化アンモニウム)、Ba2NaNb5O15(ニオブ酸バリウムナトリウム)、CdSe(セレンカドミウム)、KDP(リン酸二水素カリウム)、LiNbO3(ニオブ酸リチウム)、Se、Te、LBO、BBO、KB5などが適用される。特にLBOを用いることが望ましい。代表的な一例は、Nd:YVO4レーザ発振装置(基本波1064nm)の第2高調波(532nm)を用いる。また、レーザの発振モードはTEM00モードであるシングルモードを適用する。

【0064】

最も適した材料として選ばれる珪素の場合、吸収係数が103〜104cm-1である領域はほぼ可視光域にある。ガラスなど可視光透過率の高い基板と、珪素により30〜200nmの厚さをもって形成される非晶質半導体膜を結晶化する場合、波長400〜700nmの可視光域の光を照射することで、当該半導体領域を選択的に加熱して、下地絶縁膜にダメージを与えずに結晶化を行うことができる。具体的には、非晶質珪素膜に対し、波長532nmの光の侵入長は概略100nm〜1000nmであり、膜厚30nm〜200nmで形成される非晶質半導体膜106の内部まで十分達することができる。即ち、半導体膜の内側から加熱することが可能であり、レーザ光の照射領域における半導体膜のほぼ全体を均一に加熱することができる。

【0065】

レーザ光の照射により溶融した半導体は、表面張力が働いて開口部(凹部)に集まる。それにより固化した状態では、図3で示すように表面がほぼ平坦になる。さらに結晶の成長端や結晶粒界又は結晶亜粒界は第2絶縁膜上(凸部上)に形成される(図中ハッチングで示す領域110)。こうして結晶性半導体膜107が形成される。

【0066】

その後図4で示すように、結晶性半導体膜107をエッチングして島状の半導体領域108、109を形成する。この時、成長端や結晶粒界又は結晶亜粒界が集中する領域110をエッチング除去することにより良質な半導体領域のみ残すことができる。そして、この島状の半導体領域108、109の、特に開口部(凹部)を充填する結晶性半導体を使ってチャネル形成領域が位置せしめるようにゲート絶縁膜及びゲート電極を形成する。このような各段階を経てTFTを完成させることができる。

【0067】

図5は第1絶縁膜102及び第2絶縁膜103〜105により形成される開口部の溝(段差)の深さ及び間隔と結晶成長の関係を模式的に説明する図である。尚、図5で示す長さに関する符号に関し、t01:第2絶縁膜上(凸部)の非晶質半導体膜の厚さ、t02:開口部(凹部)の非晶質半導体膜の厚さ、t11:第2絶縁膜上(凸部)の結晶性半導体膜の厚さ、t12:開口部(凹部)の結晶性半導体膜の厚さ、d:第2絶縁膜の厚さ(開口部の深さ)、W1:第2絶縁膜の幅、W2:開口部の幅、である。

【0068】

図5(A)は、d<t02、W1,W2≦1μmの場合であり、開口部の溝の深さが非晶質半導体膜106よりも小さい場合には、溶融結晶化の過程を経ても開口部に半導体が充填されることはなく結晶性半導体膜の表面が平坦化されることはない。即ち、結晶性半導体膜の下地の凹凸形状が概略保存されたまま残ってしまう。

【0069】

図5(B)は、d≧t02、W1,W2≦1μmの場合であり、開口部の溝の深さが非晶質半導体膜106とほぼ等しいかそれより大きい場合には、表面張力が働いて開口部(凹部)に集まる。それにより固化した状態では、図5(B)で示すように表面がほぼ平坦になる。この場合、t11<t12となり、膜厚が薄い部分120に応力が集中しここに歪みが蓄積され、また、結晶の成長端が形成されることになる。

【0070】

図5(C)は、d>>t02、W1,W2≦1μmの場合であり、この場合は結晶性半導体膜107が開口部を充填するように形成され、第2絶縁膜上には殆ど残存しない。

【0071】

図5(D)は、d≧t02、W1,W2>1μmの場合であり、開口部の幅が広がると結晶性半導体膜が開口部を充填して平坦化の効果はあるものの、開口部の中央付近には結晶粒界や結晶亜粒界が発生してくる。また、第2絶縁膜上にも同様に応力が集中しここに歪みが蓄積され、また、結晶の成長端が形成される。これは、間隔が広がることで応力緩和の効果が低減するためであると推察される。

【0072】

図5(E)は、d≧t02、W1,W2>>1μmの場合であり、図5(D)の状態がさらに顕在化してくる。

【0073】

以上、図5を用いて説明したように、半導体素子を形成する場合、特にTFTを形成する場合には、図5(B)の条件が最も適していると考えられる。

【0074】

以上の説明において、結晶性半導体膜を形成する下地の凹凸形状は、第1絶縁膜と第2絶縁膜で形成する一例を示したが、ここで示す形態に限定されず同様な形状を有するものであれば良い。例えば、石英基板の表面に直接開口部を形成して凹凸形状を設けても良い。

【0075】

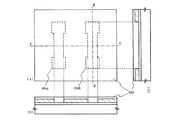

図6は、結晶化に際し適用することのできるレーザ処理装置の構成の一例を示す。図6はレーザ発振装置301、シャッター302、高変換ミラー303〜306、スリット307、シリンドリカルレンズ308、309、載置台311、載置台311をX方向及びY方向に変位させる駆動手段312、313、当該駆動手段をコントロールする制御手段314、予め記憶されたプログラムに基づいてレーザ発振装置301や制御手段314に信号を送る情報処理手段315等から成っているレーザ処理装置の構成を正面図と側面図により示すものである。

【0076】

シリンドリカルレンズ308、309により照射面の断面形状において線状に集光されるレーザ光は、載置台311上の基板320表面に対し斜めに入射させる。これは、非点収差などの収差により焦点位置がずれ、照射面またはその近傍において線状の集光面を形成することができる。シリンドリカルレンズ308、309は合成石英製とすれば、高い透過率が得られ、レンズの表面に施されるコーティングは、レーザ光の波長に対する透過率が99%以上を実現するために適用される。勿論、照射面の断面形状は線状に限定されず、矩形状、楕円形又は長円形など任意な形状としても構わない。いずれにしても、短軸と長軸の比が、1対10〜1対100の範囲に含まれるものを指している。また、波長変換素子310は基本波に対する高調波を得るために備えられている。

【0077】

上述の如く、レーザ発振装置は矩形ビーム固体レーザ発振装置が適用され、特に好ましくは、スラブレーザ発振装置が適用される。或いは、YAG、YVO4、YLF、YAlO3などの結晶にNd、Tm、Hoをドープした結晶を使った固体レーザ発振装置にスラブ構造増幅器を組み合わせたものでも良い。スラブ材料としては、Nd:YAG、Nd:GGG(ガドリニウム・ガリウム・ガーネット)、Nd:GsGG(ガドリニウム・スカンジウム・ガリウム・ガーネット)等の結晶が使用される。その他にも、連続発振可能な気体レーザ発振装置、固体レーザ発振装置を適用することもできる。連続発振固体レーザ発振装置としてはYAG、YVO4、YLF、YAlO3などの結晶にCr、Nd、Er、Ho、Ce、Co、Ti又はTmをドープした結晶を使ったレーザ発振装置を適用する。発振波長の基本波はドープする材料によっても異なるが、1μmから2μmの波長で発振する。より高い出力を得る為には、ダイオード励起の固体レーザ発振装置が適用され、カスケード接続されていても良い。

【0078】

また、載置台311を駆動手段312、313により二軸方向に動かすことにより基板320のレーザ処理を可能としている。一方の方向への移動は基板320の一辺の長さよりも長い距離を1〜200cm/sec、好ましくは5〜50cm/secの等速度で連続的に移動させることが可能であり、他方へは線状ビームの長手方向と同程度の距離を不連続にステップ移動させることが可能となっている。レーザ発振装置301の発振と、載置台311は、マイクロプロセッサを搭載した情報処理手段315により同期して作動するようになっている。

【0079】

載置台311は図中で示すX方向に直線運動をすることにより、固定された光学系から照射されるレーザ光で基板全面の処理を可能としている。位置検出手段316は基板320がレーザ光の照射位置にあることを検出して、その信号を情報処理手段315に伝送し、情報処理手段315によりレーザ発振装置301の発振動作とのタイミングを同期させている。つまり、基板320がレーザ光の照射位置にない時は、レーザの発振を止め、その寿命を延長させている。

【0080】

このような構成のレーザ照射装置により基板320に照射されるレーザ光は、図中に示すX方向又はY方向に相対移動させることにより半導体膜の所望の領域または全面を処理することができる。

【0081】

以上のように、非晶質半導体膜に連続発振レーザ光を照射する結晶化において、下地絶縁膜に段差形状を設けることにより、その部分に結晶化に伴う歪み又は応力を集中させることができ、活性層とする結晶性半導体にその歪み又は応力がかからないようにすることができる。歪み又は応力から開放された結晶性半導体膜にチャネル形成領域が配設されるようにTFTを形成することにより、高速で電流駆動能力を向上させることが可能となり、素子の信頼性を向上させることも可能となる。

【0082】

また、図20を用いて、本発明で用いられるレーザ光の照射方法について説明する。

【0083】

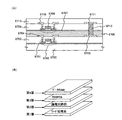

まず、図20(A)に示すように基板上に絶縁膜からなる第1の下地膜9101を形成する。そして、第1の下地膜9101上に矩形状の絶縁膜からなる第2の下地膜9102が形成され、第1及び第2の下地膜9101、9102を覆うように、第3の下地膜9103が形成されている。本実施の形態では、第1の下地膜9101として窒化珪素を用い、第2の下地膜9102として酸化珪素を用い、第3の絶縁膜9103として酸化珪素膜を用いた。なお第1乃至第3の下地膜9101〜9103の材料はこれに限定されず、後の工程における熱処理に耐え得る材料で、なおかつ後に形成される半導体膜に、TFTの特性に悪影響を与えうるアルカリ金属が混入するのを防ぐことができ、凹凸を形成することができる絶縁膜であれば良い。なおこの凹凸の形成の仕方については、後段において詳しく説明する。また、これらの他の絶縁膜を用いても良い。また2つ以上の膜の積層構造であってもよい。

【0084】

そして図20では第1乃至第3の下地膜を区別して示しているが、3つの下地膜を合わせて下地膜9104と総称する。なお、本実施の形態では3つの下地膜を使って凹凸を有する下地膜9104を形成しているが、本発明で用いる下地膜の構成はこれに限定されない。

【0085】

このとき、下地膜9104と同時に、下地膜の一部を利用してマーカーを形成するようにしても良い。

【0086】

基板(図示せず)は、後の工程の処理温度に耐えうる材質であれば良く、例えば石英基板、シリコン基板、バリウムホウケイ酸ガラスまたはアルミノホウケイ酸ガラスなどのガラス基板、金属基板またはステンレス基板の表面に絶縁膜を形成した基板を用いることができる。また、処理温度に耐えうる程度に耐熱性を有するプラスチック基板を用いてもよい。

【0087】

次に、下地膜9104を覆うように、半導体膜9105を形成する。半導体膜9105は、公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)により成膜することができる。なお、半導体膜は非晶質半導体膜であっても良いし、微結晶半導体膜、結晶性半導体膜であっても良い。また珪素だけではなくシリコンゲルマニウムを用いるようにしても良い。また、第3の下地膜9103を成膜した後、大気開放せずに連続的に成膜することで、半導体膜と下地膜との間に不純物が混入するのを防ぐことができる。

【0088】

なお、下地膜9104の凸部の形状及びそのサイズついては、設計者が適宜設定することができるが、後に形成される半導体膜が凸部のエッジ近傍において膜切れを起こさない程度の厚さに設定する必要がある。

【0089】

次に、図20(B)に示すように、半導体膜9105にレーザ光を照射する。レーザ光の照射により、半導体膜9105は一次的に溶融し、白抜きの矢印で示したように、凸部の上部から凹部に向かってその体積が移動する。そして表面が平坦化され、なおかつ結晶性が高められた半導体膜(LC後)9106が形成される。レーザ光のエネルギー密度は、レーザビームのエッジの近傍において低くなっており、そのためエッジの近傍は結晶粒が小さく、結晶の粒界に沿って突起した部分(リッジ)が出現する。そのため、レーザ光のレーザビームの軌跡のエッジと、チャネル形成領域となる部分または半導体膜9105の凹部上に位置する部分とが重ならないように照射する。

【0090】

なおレーザ光の走査方向は、下地膜9104の凸部の長手方向と平行になるように定める。

【0091】

本発明では公知のレーザを用いることができる。レーザ光は連続発振であることが望ましいが、パルス発振であってもある程度本発明の効果を得ることができると考えられる。レーザは、気体レーザもしくは固体レーザを用いることができる。気体レーザとして、エキシマレーザ、Arレーザ、Krレーザなどがあり、固体レーザとして、YAGレーザ、YVO4レーザ、YLFレーザ、YAlO3レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、Y2O3レーザなどが挙げられる。固体レーザとしては、Cr、Nd、Er、Ho、Ce、Co、Ti、Yb又はTmがドーピングされたYAG、YVO4、YLF、YAlO3などの結晶を使ったレーザが適用される。当該レーザの基本波はドーピングする材料によって異なり、1μm前後の基本波を有するレーザ光が得られる。基本波に対する高調波は、非線形光学素子を用いることで得ることができる。

【0092】

またさらに、固体レーザから発せられらた赤外レーザ光を非線形光学素子でグリーンレーザ光に変換後、さらに別の非線形光学素子によって得られる紫外レーザ光を用いることもできる。

【0093】

半導体膜(LC後)9106は、レーザ光の照射による体積移動により、下地膜9104の凹部上において膜厚が厚くなり、逆に凸部上において膜厚が薄くなっている。そのため応力によって凸部上に粒界9149が発生しやすく、逆に凹部上においてはほぼ結晶性の良い状態が得られる。なお、凹部上において半導体膜(LC後)9106が必ずしも粒界を含まないわけではない。しかし、たとえ粒界が存在したとしても結晶粒が大きいので、結晶性は比較的優れたものとなっている。

【0094】

次に、半導体膜(LC後)9106の表面をエッチングしていき、下地膜9104の凸部上面を露出させる。なお本実施の形態では、下地膜9104の凸部上面を露出させるように、半導体膜(LC後)9106をエッチングする。そして、図20(C)に示すように、下地膜9104の凹部に結晶性半導体膜(アイランド)9107が形成される。

【0095】

上述した一連の工程によって得られたアイランドをTFTの活性層、より望ましくはTFTのチャネル形成領域として用いることで、TFTのチャネル形成領域に粒界が形成されるのを防ぐことができ、粒界によってTFTの移動度が著しく低下したり、オン電流が低減したり、オフ電流が増加したりするのを防ぐことができる。なお、どこまでを凹部または凸部のエッジ近傍としてパターニングで除去するかは、設計者が適宜定めることができる。

【0096】

【実施例】

以下、本発明の実施例について説明する。

【0097】

(実施例1)

本実施例は、開口部を有する下地絶縁膜上に結晶性珪素膜を形成し、その開口部に充填された充填領域にチャネル形成領域が配設されるTFTを作製する一例を示す。

【0098】

図7において、ガラス基板601上に100nmの窒酸化珪素膜でなる第1絶縁膜602を形成する。その上に酸化珪素膜を形成し、写真蝕刻により矩形状のパターンを有する第2絶縁膜603を形成する。酸化珪素膜はプラズマCVD法でTEOSとO2とを混合し、反応圧力40Pa、基板温度400℃とし、高周波(13.56MHz)電力密度0.6W/cm2で放電させ150nmの厚さに堆積し、その後エッチングにより開口部604a、604bを形成する。

【0099】

尚、図7において(A)は上面図、(B)はA−A'線に対応する縦断面図、(C)はB−B'線に対応する縦断面図を示す。以降、図8〜図12は同様の扱いとする。

【0100】

そして図8で示すように第1絶縁膜602及び第2絶縁膜603を覆う非晶質珪素膜605を150nmの厚さで形成する。非晶質珪素膜605はプラズマCVD法でSiH4を原料気体として用い形成する。

【0101】

そして、図9で示すように連続発振レーザ光を照射して結晶化させる。結晶化の条件は、連続発振モードのYVO4レーザ発振器を用い、その第2高調波(波長532nm)の出力5.5Wを長手方向に400μm、短手方向に50〜100μmに光学系にて長手方向に均一なエネルギー密度分布を有するように集光し、50cm/secの速度で走査して結晶化させる。均一なエネルギー密度分布とは、完全に一定であるもの以外を排除することではなく、エネルギー密度分布において許容される範囲は±20%である。このようなレーザ光の照射は、図6で示す構成のレーザ処理装置を適用することができる。光学系にて集光したレーザ光は、その強度分布が長手方向において均一な領域を有し、短手方向に分布を持っていても良い。結晶化はこの強度分布が長手方向において均一な領域で成されるようにし、これによりレーザ光の走査方向と平行な方向に結晶成長する効力を高めることができる。

【0102】

この条件でレーザ光を照射することにより、非晶質珪素膜は瞬間的に溶融し溶融帯が移動しながら結晶化が進行する。溶融した珪素は表面張力が働いて開口部(凹部)に凝集し固化する。これにより、開口部604a、604bを充填する形態で結晶性半導体膜606が形成される。

【0103】

その後図10に示すように、少なくとも開口部604a、604bに結晶性半導体膜が残存するようにマスクパターンを形成してエッチング処理を施し、チャネル形成領域を含む島状の半導体領域607、608を形成する。

【0104】

図11は、半導体領域607、608の上層側にゲート絶縁膜609、ゲート電極610、611が形成された状態を示している。ゲート絶縁膜609は80nmの酸化珪素膜をプラズマCVD法で形成すれば良い。ゲート電極610、611はタングステン又はタングステンを含有する合金で形成する。このような構造とすることにより、開口部604a、604bを充填する島状の半導体領域にチャネル形成領域を設けることができる。

【0105】

以降、ソース及びドレイン領域、低濃度ドレイン領域等を適宜形成すればTFTを完成させることができる。

【0106】

(実施例2)

実施例1と同様な工程で形成されるものであるが、図12で示すように、第2絶縁膜603に形成する開口部の形状を、細長い短冊状の領域とそれと連接する領域とで形成し、その開口部604cに合わせて結晶性珪素膜で成る島状の半導体領域620を形成し、ゲート絶縁膜621、ゲート電極622を形成することにより、シングルゲート・マルチチャネル型のTFTを形成することができる。

【0107】

(実施例3)

実施例2において、第2絶縁膜を非晶質半導体膜の厚さよりも厚く形成し、例えば350nmで形成することで、図13に示すように、結晶性半導体膜で形成される島状の半導体領域620を開口部604dに完全に埋め込むことができる。そして、ゲート絶縁膜621及びゲート電極622を同様に形成すればシングルゲート・マルチチャネル型のTFTを形成することができる。

【0108】

(実施例4)

図14はシングルゲート・マルチチャネル型のTFTの他の一例を示している。基板601上に第1絶縁膜602、第2絶縁膜603、島状の半導体領域630、ゲート絶縁膜631、ゲート電極632は実施例1乃至3と同様に形成するものである。図14において異なる部分は、第2絶縁膜603で形成される開口部604eの他に、島状の半導体領域630が形成された後において、チャネル形成領域が形成される当該半導体領域の周辺の第2絶縁膜を除去して第2の開口部625を形成している点にある。

【0109】

チャネル形成領域付近の形態を図14(D)に拡大図として示すが、島状の半導体領域630の側面及び上面に接してゲート絶縁膜631が形成され、それを覆う形でゲート電極632が形成されることになり、この場合チャネル形成領域は半導体領域630の上部634と側面部635の両方に形成されることになる。これにより空乏化領域を増やすことができ、TFTの電流駆動能力を向上させることができる。

【0110】

(実施例5)

本発明は様々な半導体装置に適用できるものであり、実施例1乃至4に基づいて作製される表示パネルの形態を説明する。

【0111】

図15において、基板900には画素部902、ゲート信号側駆動回路901a、901b、データ信号側駆動回路901c、入力端子935、配線又は配線群917が備えられている。シールパターン940はゲート信号側駆動回路901a、901b、データ信号側駆動回路901c及び当該駆動回路部と入力端子935とを接続する配線又は配線群917と一部が重なっていても良い。このようにすると、表示パネルの額縁領域(画素部の周辺領域)の面積を縮小させることができる。入力端子935には、FPC936が固着されている。

【0112】

さらに、本発明のTFTを用いてマイクロプロセッサ、メモリ、又はメディアプロセッサ/DSP(Digital Signal Processor)等が形成されたチップ950が実装されていても良い。これらの機能回路は、画素部902、ゲート信号側駆動回路901a、901b、データ信号側駆動回路901cとは異なるデザインルールで形成されるものであり、具体的には1μm以下のデザインルールが適用される。実装の方法に限定はなくCOG方式等が適用されている。

【0113】

実施例1〜4で示すTFTは画素部902のスイッチング素子として、さらにゲート信号側駆動回路901a、901b、データ信号側駆動回路901cを構成する能動素子として適用することができる。

【0114】

図16は画素部902の一画素の構成を示す一例であり、TFT801〜803が備えられている。これらは、画素に備える発光素子や液晶素子を制御するそれぞれスイッチング用、リセット用、駆動用のTFTである。

【0115】

これらのTFTのチャネル形成領域を含む島状の半導体領域812〜814は、その下層に形成されている下地絶縁膜の開口809〜811に合わせて形成されている。島状の半導体領域812〜814は実施例1〜5に基づいて形成することができる。島状の半導体領域812〜814の上層には、ゲート線815〜817が形成され、パッシベーション膜及び平坦化膜を介して信号線818、電源線819、その他各種配線820、821及び画素電極823が形成されている。

【0116】

このように、本発明は何ら影響を与えることなく表示パネルを完成させることができる。

【0117】

(実施例6)

本実施例では、本発明の半導体装置に用いられる、互いに分離した複数のチャネル形成領域を有する、所謂マルチチャネル型のTFTの作製工程について述べる。

【0118】

まず図21(A)に示すように、絶縁表面上に凸部を有する下地膜9120を形成する。なお、図21(A)のA−A’における断面図を図21(B)に示し、図21(A)のB−B’における断面図を図21(C)に示す。

【0119】

本実施例では、実施の形態において示したのと同じ構成を有する下地膜9120を用いる。下地膜9120は、3つの下地膜からなり、まず窒化珪素からなる第1の下地膜9121上に、矩形状の酸化珪素から成る第2の下地膜9122が形成されており、第1及び第2の下地膜9121、9122を覆うように、酸化珪素からなる第3の下地膜9123が形成されている。本実施例では、第1乃至第3の下地膜9121〜9123で下地膜9120が形成されている。そして下地膜9120の凸部9124は、矩形状の第2の絶縁膜9122と、第3の絶縁膜9123のうち第1の絶縁膜9121ではなく第2の絶縁膜9122に接している部分と、で構成されている。

【0120】

なお、凸部9124の形状及びそのサイズついては、設計者が適宜設定することができるが、後に形成される半導体膜が凸部9124のエッジ近傍において膜切れを起こさない程度の厚さに設定する必要がある。本実施例では凸部9124の高さを0.1〜1μm程度にする。

【0121】

なお、基板の歪がそのまま後に形成される下地膜の形状に影響を与えることになる。下地膜の歪は後に形成される半導体膜の結晶性の均一性を乱す原因になるので、基板の表面を、その歪の差が10nm以下に抑えられるように化学的機械的研磨法(CMP法)を用いて研磨したり、後の工程における加熱処理により基板が歪まないように、下地膜を形成する前に予め基板に加熱処理を施しておくと良い。

【0122】

そして、下地膜9120を覆って非晶質半導体膜9125を形成する。非単結晶半導体膜9125は、公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)により成膜することができる。本実施例ではプラズマCVD法により300nmの非単結晶半導体膜9125を成膜した。

【0123】

次に、図22(A)に示すように、非単結晶半導体膜9125にレーザ光を照射し、結晶化を行なう。なお、図22(B)は、図22(A)の破線A−A’における断面図に相当する。本実施例では連続発振のYVO4レーザを用い、50cm/secの走査速度で照射を行った。このとき、レーザ光の走査方向は、後に形成されるチャネル形成領域においてキャリアが移動する方向と同じ方向に揃える。本実施例では、白抜きの矢印で示したように、走査方向を矩形の凸部9124の長手方向に揃えてレーザ光を照射した。レーザ光の照射により、非単結晶半導体膜9125は溶融し、凸部9124上から凹部上に体積が移動し、結晶性半導体膜9126が形成される。

【0124】

次に、図23(A)に示すように結晶性半導体膜9126をパターニングすることで、サブアイランド9127を形成する。なお、図23(B)は、図23(A)の破線A−A’における断面図に相当する。サブアイランド9127は、凸部9124間に形成される凹部上にその一部が存在する。目的とするマルチチャネル型TFTのチャネル形成領域は、結晶性半導体膜9126の凹部上に位置する部分を用いて形成されるので、そのチャネル形成領域の数、チャネル長、チャネル幅を考慮して、サブアイランド9127と凸部9124との位置関係を定めることが肝要である。

【0125】

次に、図24(A)に示すようにサブアイランド9127を上面から、下地膜9120の凸部9124の上面を露出させる程度に除去することで、アイランド9128を形成する。なお、図24(B)は、図24(A)の破線A−A’における断面図に相当する。サブアイランド9127の上面からの除去は、どのような方法を用いて行っても良く、例えばエッチングにより行っても良いし、CMP法により行っても良い。

【0126】

このサブアイランド9127の上面からの除去により、凸部9124上の粒界が存在する部分が除去され、凸部9124間に相当する凹部の上には、粒界が殆ど存在しておらず、後にチャネル形成領域となる部分において結晶性に優れた半導体膜が残される。そして、図24(A)、(B)に示すような、チャネル形成領域の部分のみ分離したスリット状のアイランド9128が形成される。なお、ソース領域またはドレイン領域となる部分はチャネル形成領域ほど半導体膜の結晶性によるTFTの特性への影響が大きくない。そのため、ソース領域またはドレイン領域となる部分が、チャネル形成領域となる部分に比べて結晶性が芳しくなくても然程問題にはならない。

【0127】

次に、図25(A)に示すように、アイランド9128を用いてTFTを作製する。なお、TFTの構造及びその作製方法は様々である。図25(B)は、図25(A)の破線A−A’における断面図に相当し、図25(C)は、図25(A)の破線B−B’における断面図に相当し、図26(A)は、図25(A)の破線C−C’における断面図に相当し、図26(B)は、図25(A)の破線D−D’における断面図に相当する。

【0128】

アイランド9128が有するチャネル形成領域9130は、ゲート絶縁膜9131を間に挟んでゲート電極9132と重なっている。またチャネル形成領域9130は、同じくアイランド9128が有する2つの不純物領域9133に挟まれている。なお、2つの不純物領域9133はソース領域又はドレイン領域として機能する。

【0129】

そして、アイランド9128、ゲート絶縁膜9131及びゲート電極9132を覆って、第1の層間絶縁膜9134が形成されている。そして第1の層間絶縁膜9134を覆って、第2の層間絶縁膜9135が形成されている。なお、第1の層間絶縁膜9134は無機の絶縁膜であり、第2の層間絶縁膜9135が有する炭素等の不純物がアイランド9128に入るのを防ぐことができる。また第2の層間絶縁膜9135は有機樹脂膜であり、後に形成される配線が断線されないように、表面を平坦化する効果がある。

【0130】

そして、ゲート絶縁膜9131、第1の層間絶縁膜9134及び第2の層間絶縁膜9135に形成されたコンタクトホールを介して、不純物領域9133に接続された配線9136が、第2の層間絶縁膜9135上に形成されている。

【0131】

上記作製工程によって、互いに分離した複数のチャネル形成領域を有するTFTが完成する。このような構成にすることで、TFTを駆動させることで発生した熱を効率的に放熱することができる。

【0132】

なお本発明において、TFTの構造は図25に示したものに限定されない。また、チャネル形成領域の数は4つに限定されず、1つまたは4以外の数のチャネル形成領域を有していても良い。

【0133】

また、TFTの構造は上記構成に限定されず、例えば、図27に示すような構成を有していても良い。図27(A)に示すTFTは、2層の導電膜9140、9141からなるゲート電極を有している。該導電膜9140の上面及び導電膜9141の側面に接するように、絶縁膜からなるサイドウォール9142が形成されている。例えば導電膜9140としてTaN、導電膜9141としてWを用い、サイドウォール9142としてSiO2などを用いることができる。図27(B)に示すTFTは、2層の導電膜9144、9145からなるゲート電極を有している。該導電膜9144は不純物領域の一部と重なっている。

【0134】

なお、上記工程において、レーザ光の照射後または結晶質珪素膜を下地膜の凸部9124が露出する程度にエッチングした後において、500〜600℃で1分から60分程度加熱することで、半導体膜内において生じている応力を緩和することができる。

【0135】

本発明では、絶縁膜の凹部上に位置する半導体膜を、TFTの活性層として積極的に用いることで、TFTのチャネル形成領域に粒界が形成されるのを防ぐことができ、粒界によってTFTの移動度が著しく低下したり、オン電流が低減したり、オフ電流が増加したりするのを防ぐことができる。

【0136】

(実施例7)

本実施例では、実施例6とは工程順序が異なる、アイランドの作製方法について説明する。なお、各工程の詳しい説明については、実施例6を参照する。

【0137】

図28(A)に示すように、まず矩形状の凸部9301を有する下地膜を形成し、該下地膜上に非単結晶半導体膜9302を形成する。次に、該非単結晶半導体膜9302にレーザ光を照射し、結晶性半導体膜9303を形成する(図28(B))。

【0138】

次に、結晶性半導体膜9303を、凸部9301の上面が露出する程度まで、その表面から一部を除去していく。なお、本実施例ではエッチングを用いて除去を行い、除去後の結晶性半導体膜をここでは結晶性半導体膜(エッチング後)9304とする(図28(C))。

【0139】

次に、結晶性半導体膜(エッチング後)9304をパターニングし、アイランド9305を形成する(図28(D))。

【0140】

なお、上記工程において、レーザ光の照射後、結晶性半導体膜を下地膜の凸部が露出する程度にエッチングした後またはアイランドを形成した後において、500〜600℃で1分から60分程度加熱することで、半導体膜内において生じている応力を緩和することができる。

【0141】

上記工程によって、アイランドを形成する前に、結晶性半導体膜を下地膜の凸部が露出する程度にエッチングすることで、アイランドの端部及び側面が一部エッチングによって除去されてしまうのを防ぐことができる。

【0142】

(実施例8)

本実施例では、実施例6、7とは工程順序が異なる、アイランドの作製方法について説明する。なお、各工程の詳しい説明については、実施例6を参照する。

【0143】

図29(A)に示すように、まず矩形状の凸部9311を有する下地膜を形成し、該下地膜上に非単結晶半導体膜9312を形成する。

【0144】

次に、非単結晶半導体膜9312をパターニングし、サブアイランド9313を形成する(図29(B))。

【0145】

次に、該サブアイランド9313にレーザ光を照射し、結晶化させる。本実施例では結晶化後のサブアイランドをサブアイランド(結晶化後)9314とする(図29(C))。

【0146】

次に、サブアイランド(結晶化後)9314を、凸部9311の上面が露出する程度まで、その表面から一部を除去していく。なお、本実施例ではエッチングを用いて除去を行い、アイランド9315を形成する(図29(D))。

【0147】

なお、上記工程において、レーザ光の照射後またはアイランドを形成した後において、500〜600℃で1分から60分程度加熱することで、半導体膜内において生じている応力を緩和することができる。

【0148】

(実施例9)

本実施例では、複数の凸部を用いて、マルチチャネル型のTFTと、チャネル形成領域を1つだけ有するシングルチャネル型のTFTとを形成する例について説明する。

【0149】

図30(A)に、矩形状の複数の凸部9330を有する下地膜を示す。該下地膜上に形成されたアイランドを用いたTFTを、図30(B)に示す。図30(B)では、4つのチャネル形成領域を有するマルチチャネル型TFT9331と、2つのチャネル形成領域を有するマルチチャネル型TFT9332と、シングルチャネル型TFT9333とを有している。

【0150】

各TFTは、チャネル形成領域が凸部9330間に位置する凹部上に形成されている。より好ましくは、チャネル形成領域と、LDD領域とが凸部9330間に位置する凹部上に形成されていることが望ましい。

【0151】

本実施例は、実施例6〜8と組み合わせて実施することが可能である。

【0152】

(実施例10)

本実施例では、半導体膜の結晶化に際し、レーザ光の照射の工程と、触媒を用いて半導体膜を結晶化させる工程とを組み合わせた例について説明する。触媒元素を用いる場合、特開平7−130652号公報、特開平8−78329号公報で開示された技術を用いることが望ましい。

【0153】

まず図31(A)に示すように、凸部9350を有する下地膜9351上に、非単結晶半導体膜9352を成膜する。次に触媒元素を用いて非単結晶半導体膜9352を結晶化させる(図31(B))。例えば特開平7−130652号公報に開示されている技術を用いる場合、重量換算で10ppmのニッケルを含む酢酸ニッケル塩溶液を非単結晶半導体膜9352に塗布してニッケル含有層9353を形成し、500℃、1時間の脱水素工程の後、500〜650℃で4〜12時間、例えば550℃、8時間の熱処理を行い、結晶性が高められた結晶性半導体膜9354を形成する。尚、使用可能な触媒元素は、ニッケル(Ni)以外にも、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)、といった元素を用いても良い。

【0154】

そして、レーザ光照射により、NiSPCにより結晶化された結晶性半導体膜(NiSPC後)9354から、結晶性がさらに高められた結晶性半導体膜(LC後)9355が形成される(図31(C))。結晶性半導体膜(LC後)9355は、レーザ光の照射の際に一次的に溶融し、凸部9350の上部から凹部に向かって体積移動し、表面が平坦化される。そして、凸部9350上においてその膜厚が薄くなっており、応力によって粒界9356ができやすくなっている。

【0155】

次に、結晶性半導体膜(LC後)9355中の触媒元素をゲッタリングする工程について説明する。なお本実施例ではゲッタリングをレーザ光の照射後に行なっているが、結晶性半導体膜(LC後)9355をエッチングしてから行っても良い。

【0156】

結晶性半導体膜(LC後)9355に珪素を主成分とするバリア層9357を形成する(図31(D))。なお、このバリア層9357は極薄いものでよく、自然酸化膜であってもよいし、酸素を含む雰囲気下において紫外線の照射によりオゾンを発生させて酸化させる酸化膜であってもよい。また、このバリア層9357として、炭素、即ち有機物の除去のために行われるヒドロ洗浄と呼ばれる表面処理に使用するオゾンを含む溶液で酸化させた酸化膜であってもよい。このバリア層9357は、主にエッチングストッパーとして用いるものである。また、このバリア層9357を形成した後、チャネルドープを行い、その後、強光を照射して活性化させてもよい。

【0157】

次いで、バリア層9357上にゲッタリング用の第1半導体膜9358を形成する。このゲッタリング用の第1半導体膜9358は非晶質構造を有する半導体膜であってもよいし、結晶構造を有する半導体膜であってもよい。このゲッタリング用の第1半導体膜9358の膜厚は、5〜50nm、好ましくは10〜20nmとする。ゲッタリング用の第1半導体膜9358には、酸素(SIMS分析での濃度が5×1018atoms/cm3以上、好ましくは1×1019atoms/cm3以上)を含有させてゲッタリング効率を向上させることが望ましい。

【0158】

次に、ゲッタリング用の第1半導体膜9358上に希ガス元素を含む第2の半導体膜(ゲッタリングサイト)9359を形成する。このゲッタリング用の第2半導体膜9359はプラズマCVD法、減圧熱CVD法、またはスパッタ法を用いた非晶質構造を有する半導体膜であってもよいし、結晶構造を有する半導体膜であってもよい。第2の半導体膜は、成膜段階で希ガス元素を含む半導体膜であってもよいし、希ガス元素を含んでいない半導体膜の成膜後に希ガス元素を添加してもよい。本実施例では成膜段階で希ガス元素を含むゲッタリング用の第2半導体膜9359を形成した後、さらに希ガス元素を選択的に添加してゲッタリング用の第2半導体膜9359を形成した例を示した。また、ゲッタリング用の第1半導体膜と第2半導体膜とを大気に触れることなく連続的に成膜してもよい。また、第1の半導体膜の膜厚と第2の半導体膜の膜厚との和は30〜200nm、例えば50nmとすればよい。

【0159】

本実施例は、ゲッタリング用の第1半導体膜9358によって、結晶性半導体膜(LC後)9355と第2の半導体膜9359との間隔を空けている。ゲッタリングの際、結晶性半導体膜(LC後)9355中に存在する金属等の不純物元素は、ゲッタリングサイトの境界付近に集まりやすい傾向があるため、本実施例のようにゲッタリング用の第1半導体膜9358によって、ゲッタリングサイトの境界を結晶性半導体膜(LC後)9355から遠ざけてゲッタリング効率を向上させることが望ましい。加えて、ゲッタリング用の第1半導体膜9358は、ゲッタリングの際、ゲッタリングサイトに含まれる不純物元素が拡散して第1の半導体膜の界面に達することがないようにブロッキングする効果も有している。また、ゲッタリング用の第1半導体膜9358は、希ガス元素を添加する場合、結晶性半導体膜(LC後)9355にダメージを与えないように保護する効果も有している。

【0160】

次いで、ゲッタリングを行う。ゲッタリングを行う工程としては、窒素雰囲気中で450〜800℃、1〜24時間、例えば550℃にて14時間の熱処理を行えばよい。また、熱処理に代えて強光を照射してもよい。また、加熱したガスを噴射して基板を加熱するようにしても良い。この場合、600℃〜800℃、より望ましくは650℃〜750℃で1〜60分加熱を行えば良く。時間を短縮化することができる。このゲッタリングにより、図31(D)中の矢印に示したように第2半導体膜9359に不純物元素が移動し、バリア層9357で覆われた結晶性半導体膜(LC後)9355に含まれる不純物元素の除去、または不純物元素の濃度の低減が行われる。このゲッタリングにより、含まれる不純物元素がほとんど存在しない、即ち膜中の不純物元素濃度が1×1018atoms/cm3以下、望ましくは1×1017atoms/cm3以下になるような結晶性半導体膜(ゲッタリング後)9360が形成される。

【0161】

次いで、バリア層9357をエッチングストッパーとして、ゲッタリング用の第1半導体膜9358と、第2の半導体膜9359を選択的に除去する。

【0162】

そしてバリア層9357をエッチング条件を変えて除去した後、図31(E)に示すように、凸部9350の上面を露出させる程度に結晶性半導体膜(ゲッタリング後)9360をエッチングし、エッチング後の結晶性半導体膜9361が凹部に形成される。

【0163】

なお、結晶化前の半導体膜に触媒元素を含む溶液を塗布した後に、SPCではなく、レーザ光の照射により結晶成長を行うようにしても良い。またゲッタリングは、特開平10−135468号公報または特開平10−135469号公報等に記載された技術を用いても良い。

【0164】

なお本実施例ではレーザ光を照射した後にゲッタリングを行っているが、本発明はこの構成に限定されない。図31(E)のエッチングを行った後にゲッタリングをするようにしても良い。

【0165】

本実施例は、実施例6〜9と組み合わせて実施することが可能である。

【0166】

(実施例11)

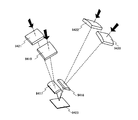

次に、本発明において用いられるレーザ照射装置の構成について、図32を用いて説明する。9151はレーザ発振装置である。図32では4つのレーザ発振装置を用いているが、レーザ照射装置が有するレーザ発振装置はこの数に限定されない。

【0167】

なお、レーザ発振装置9151は、チラー9152を用いてその温度を一定に保つようにしても良い。チラー9152は必ずしも設ける必要はないが、レーザ発振装置9151の温度を一定に保つことで、出力されるレーザ光のエネルギーが温度によってばらつくのを抑えることができる。

【0168】

また9154は光学系であり、レーザ発振装置9151から出力された光路を変更したり、そのレーザビームの形状を加工したりして、レーザ光を集光することができる。さらに、図32のレーザ照射装置では、光学系9154によって、複数のレーザ発振装置9151から出力されたレーザ光のレーザビームを互いに一部を重ね合わせることで、合成することができる。

【0169】

なお、レーザ光の進行方向を極短時間で変化させるAO変調器9153を、被処理物である基板9156とレーザ発振装置9151との間の光路に設けても良い。また、AO変調器9153の代わりに、アテニュエイター(光量調整フィルタ)を設けて、レーザ光のエネルギー密度を調整するようにしても良い。

【0170】

また、被処理物である基板9156とレーザ発振装置9151との間の光路に、レーザ発振装置9151から出力されたレーザ光のエネルギー密度を測定する手段(エネルギー密度測定手段)9165を設け、測定したエネルギー密度の経時変化をコンピューター9160において監視するようにしても良い。この場合、レーザ光のエネルギー密度の減衰を補うように、レーザ発振装置9151からの出力を高めるようにしても良い。

【0171】

合成されたレーザビームは、スリット9155を介して被処理物である基板9156に照射される。スリット9155は、レーザ光を遮ることが可能であり、なおかつレーザ光によって変形または損傷しないような材質で形成するのが望ましい。そして、スリット9155はスリットの幅が可変であり、該スリットの幅によってレーザビームの幅を変更することができる。

【0172】

なお、スリット9155を介さない場合の、レーザ発振装置9151から発振されるレーザ光の基板9156におけるレーザビームの形状は、レーザの種類によって異なり、また光学系により成形することもできる。

【0173】

基板9156はステージ9157上に載置されている。図32では、位置制御手段9158、9159が、被処理物におけるレーザビームの位置を制御する手段に相当しており、ステージ9157の位置が、位置制御手段9158、9159によって制御されている。

【0174】

図32では、位置制御手段9158がX方向におけるステージ9157の位置の制御を行っており、位置制御手段9159はY方向におけるステージ9157の位置制御を行う。

【0175】

また図32のレーザ照射装置は、メモリ等の記憶手段及び中央演算処理装置を兼ね備えたコンピューター9160を有している。コンピューター9160は、レーザ発振装置9151の発振を制御し、レーザ光の走査経路を定め、なおかつレーザ光のレーザビームが定められた走査経路にしたがって走査されるように、位置制御手段9158、9159を制御し、基板を所定の位置に移動させることができる。

【0176】

なお図32では、レーザビームの位置を、基板を移動させることで制御しているが、ガルバノミラー等の光学系を用いて移動させるようにしても良いし、その両方であってもよい。

【0177】

さらに図32では、コンピューター9160によって、該スリット9155の幅を制御し、マスクのパターン情報に従ってレーザビームの幅を変更することができるようにしても良い。なおスリットは必ずしも設ける必要はない。

【0178】

さらにレーザ照射装置は、被処理物の温度を調節する手段を備えていても良い。また、レーザ光は指向性およびエネルギー密度の高い光であるため、ダンパーを設けて、反射光が不適切な箇所に照射されるのを防ぐようにしても良い。ダンパーは、反射光を吸収させる性質を有していることが望ましく、ダンパー内に冷却水を循環させておき、反射光の吸収により隔壁の温度が上昇するのを防ぐようにしても良い。また、ステージ9157に基板を加熱するための手段(基板加熱手段)を設けるようにしても良い。

【0179】

なお、マーカーをレーザで形成する場合、マーカー用のレーザ発振装置を設けるようにしても良い。この場合、マーカー用のレーザ発振装置の発振を、コンピューター9160において制御するようにしても良い。さらにマーカー用のレーザ発振装置を設ける場合、マーカー用のレーザ発振装置から出力されたレーザ光を集光するための光学系を別途設ける。なおマーカーを形成する際に用いるレーザは、代表的にはYAGレーザ、CO2レーザ等が挙げられるが、無論この他のレーザを用いて形成することは可能である。

【0180】

またマーカーを用いた位置合わせのために、CCDカメラ9163を1台、場合によっては数台設けるようにしても良い。なおCCDカメラとは、CCD(電荷結合素子)を撮像素子として用いたカメラを意味する。

【0181】

なお、マーカーを設けずに、CCDカメラ9163によって絶縁膜または半導体膜のパターンを認識し、基板の位置合わせを行うようにしても良い。この場合、コンピューター9160に入力されたマスクによる絶縁膜または半導体膜のパターン情報と、CCDカメラ9163において収集された実際の絶縁膜または半導体膜のパターン情報とを照らし合わせて、基板の位置情報を把握することができる。この場合マーカーを別途設ける必要がない。

【0182】

また、基板に入射したレーザ光は該基板の表面で反射し、入射したときと同じ光路を戻る、いわゆる戻り光となるが、該戻り光はレーザの出力や周波数の変動や、ロッドの破壊などの悪影響を及ぼす。そのため、前記戻り光を取り除きレーザの発振を安定させるため、アイソレータを設置するようにしても良い。

【0183】

なお、図32では、レーザ発振装置を複数台設けたレーザ照射装置の構成について示したが、レーザ発振装置は1台であってもよい。図33にレーザ発振装置が1台の、レーザ照射装置の構成を示す。図33において、9201はレーザ発振装置、9202はチラーである。また9215はエネルギー密度測定手段、9203はAO変調器、9204は光学系、9205はスリット、9213はCCDカメラである。基板9206はステージ9207上に設置し、ステージ9207の位置はX方向位置制御手段9208、Y方向位置制御手段9209によって制御されている。そして図32に示したものと同様に、コンピューター9210によって、レーザ照射装置が有する各手段の動作が制御されており、図32と異なるのはレーザ発振装置が1つであることである。また光学系9204は図32の場合と異なり、1つのレーザ光を集光する機能を有していれば良い。

【0184】

なお、半導体膜全体にレーザ光を走査して照射するのではなく、少なくとも必要不可欠な部分を最低限結晶化できるようにレーザ光を走査することで、半導体膜を結晶化させた後パターニングにより除去される部分にレーザ光を照射する時間を省くことができ、基板1枚あたりにかかる処理時間を大幅に短縮することができる。

【0185】

本実施例は、実施例6〜10と組み合わせて実施することが可能である。

【0186】

(実施例12)

本実施例では、凹凸を有する下地膜の形成の仕方について説明する。

【0187】

まず、図34(A)に示すように、基板9250上に絶縁膜からなる第1の下地膜9251を成膜する。第1の下地膜9251は本実施例では酸化窒化珪素を用いるがこれに限定されず、第2の下地膜とエッチングにおける選択比が大きい絶縁膜であれば良い。本実施例では第1の下地膜9251をCVD装置でSiH4とN2Oを用いて50〜200nmの厚さになるように形成した。なお第1の下地膜は単層であっても、複数の絶縁膜を積層した構造であってもよい。

【0188】

次に、図34(B)に示すように、第1の下地膜9251に接するように絶縁膜からなる第2の下地膜9252を形成する。第2の下地膜9252は後の工程においてパターニングし、凹凸を形成したときに、その後に成膜される半導体膜の表面に凹凸が現れる程度の膜厚にする必要がある。本実施例では第2の下地膜9252として、プラズマCVD法を用いて30nm〜300nmの酸化珪素を形成する。

【0189】

次に、図34(C)に示すようにマスク9253を形成し、第2の下地膜9252をエッチングする。なお本実施例では、フッ化水素アンモニウム(NH4HF2)を7.13%とフッ化アンモニウム(NH4F)を15.4%含む混合溶液(ステラケミファ社製、商品名LAL500)をエッチャントとし、20℃においてウエットエッチングを行う。このエッチングにより、矩形状の凸部9254が形成される。本明細書では、第1の下地膜9251と凸部9254とを合わせて1つの下地膜とみなす。

【0190】

なお、第1の下地膜9251として窒化アルミニウム、窒化酸化アルミニウムまたは窒化珪素を用い、第2の下地膜9252として酸化珪素膜を用いる場合、RFスパッタ法を用いて第2の下地膜9252をパターニングすることが望ましい。第1の下地膜9251として窒化アルミニウム、窒化酸化アルミニウムまたは窒化珪素は熱伝導度が高いので、発生した熱をすばやく拡散することができ、TFTの劣化を防ぐことができる。

【0191】

次に、第1の下地膜9251と凸部9254を覆うように半導体膜を形成する。本実施例では凸部の厚さが30nm〜300nmであるので、半導体膜の膜厚を50〜200nmとするのが望ましく、ここでは60nmとする。なお、半導体膜と下地膜との間に不純物が混入すると、半導体膜の結晶性に悪影響を与え、作製するTFTの特性ばらつきやしきい値電圧の変動を増大させる可能性があるため、下地膜と半導体膜とは連続して成膜するのが望ましい。そこで本実施例では、第1の下地膜9251と凸部9254とからなる下地膜を形成した後は、酸化珪素膜9255を薄く該下地膜上に成膜し、その後大気にさらさないように連続して半導体膜9256を成膜する。酸化珪素膜の厚さは設計者が適宜設定することができるが、本実施例では5nm〜30nm程度とした。

【0192】

次に、図34とは異なる下地膜の形成の仕方について説明する。まず図35(A)に示すように基板9260上に絶縁膜からなる第1の下地膜9261を形成する。第1の下地膜は、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜などで形成する。

【0193】

酸化珪素膜を用いる場合には、プラズマCVD法で、オルトケイ酸テトラエチル(Tetraethyl Orthosilicate:TEOS)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。酸化窒化珪素膜を用いる場合には、プラズマCVD法でSiH4、N2O、NH3から作製される酸化窒化珪素膜、またはSiH4、N2Oから作製される酸化窒化珪素膜で形成すれば良い。この場合の作製条件は反応圧力20〜200Pa、基板温度300〜400℃とし、高周波(60MHz)電力密度0.1〜1.0W/cm2で形成することができる。また、SiH4、N2O、H2から作製される酸化窒化水素化珪素膜を適用しても良い。窒化珪素膜も同様にプラズマCVD法でSiH4、NH3から作製することが可能である。

【0194】

第1の下地膜は20〜200nm(好ましくは30〜60nm)の厚さに基板の全面に形成した後、図35(B)に示すように、フォトリソグラフィーの技術を用いマスク9262を形成する。そして、エッチングにより不要な部分を除去して、矩形状の凸部9263を形成する。第1の下地膜9261に対してはフッ素系のガスを用いたドライエッチング法を用いても良いし、フッ素系の水溶液を用いたウエットエッチング法を用いても良い。後者の方法を選択する場合には、例えば、フッ化水素アンモニウム(NH4HF2)を7.13%とフッ化アンモニウム(NH4F)を15.4%含む混合溶液(ステラケミファ社製、商品名LAL500)でエッチングすると良い。

【0195】

次いで、凸部9263及び基板9260を覆うように、絶縁膜からなる第2の下地膜9264を形成する。この層は第1の下地膜9261と同様に酸化珪素膜、窒化珪素膜、酸化窒化珪素膜などで50〜300nm(好ましくは100〜200nm)の厚さに形成する。

【0196】

上記作製工程によって、凸部9263及び第2の下地膜9264からなる下地膜が形成される。なお、第2の下地膜9264を形成した後、大気に曝さないように連続して半導体膜を成膜するようにすることで、半導体膜と下地膜の間に大気中の不純物が混入するのを防ぐことができる。

【0197】

本実施例は実施例6〜11と自由に組み合わせて実施することが可能である。

【0198】

(実施例13)

本実施例では、複数のレーザビームを重ね合わせることで合成される、レーザビームの形状について説明する。

【0199】

図36(A)に、複数のレーザ発振装置からそれぞれ発振されるレーザ光の、スリットを介さない場合の被処理物におけるレーザビームの形状の一例を示す。図36(A)に示したレーザビームは楕円形状を有している。なお本発明において、レーザ発振装置から発振されるレーザ光のレーザビームの形状は、楕円に限定されない。レーザビームの形状はレーザの種類によって異なり、また光学系により成形することもできる。例えば、ラムダ社製のXeClエキシマレーザ(波長308nm、パルス幅30ns)L3308から射出されたレーザ光の形状は、10mm×30mm(共にビームプロファイルにおける半値幅)の矩形状である。また、YAGレーザから射出されたレーザ光の形状は、ロッド形状が円筒形であれば円状となり、スラブ型であれば矩形状となる。このようなレーザ光を光学系により、さらに成形することにより、所望の大きさのレーザ光をつくることもできる。

【0200】

図36(B)に図36(A)に示したレーザビームの長軸Y方向におけるレーザ光のエネルギー密度の分布を示す。図36(A)に示すレーザビームは、図36(B)におけるエネルギー密度のピーク値の1/e2のエネルギー密度を満たしている領域に相当する。レーザビームが楕円形状であるレーザ光のエネルギー密度の分布は、楕円の中心Oに向かうほど高くなっている。このように図36(A)に示したレーザビームは、中心軸方向におけるエネルギー密度がガウス分布に従っており、エネルギー密度が均一だと判断できる領域が狭くなる。

【0201】

次に、図36(A)に示したレーザビームを有するレーザ光を合成したときの、レーザビームの形状を、図36(C)に示す。なお図36(C)では4つのレーザ光のレーザビームを重ね合わせることで1つの線状のレーザビームを形成した場合について示しているが、重ね合わせるレーザビームの数はこれに限定されない。

【0202】

図36(C)に示すように、各レーザ光のレーザビームは、各楕円の長軸が一致し、なおかつ互いにレーザビームの一部が重なることで合成され、1つのレーザビーム9360が形成されている。なお以下、各楕円の中心Oを結ぶことで得られる直線をレーザビーム9360の中心軸とする。

【0203】

図36(D)に、図36(D)に示した合成後のレーザビームの、中心軸y方向におけるレーザ光のエネルギー密度の分布を示す。なお、図36(C)に示すレーザビームは、図36(B)におけるエネルギー密度のピーク値の1/e2のエネルギー密度を満たしている領域に相当する。合成前の各レーザビームが重なり合っている部分において、エネルギー密度が加算される。例えば図示したように重なり合ったビームのエネルギー密度E1とE2を加算すると、ビームのエネルギー密度のピーク値E3とほぼ等しくなり、各楕円の中心Oの間においてエネルギー密度が平坦化される。

【0204】

なお、E1とE2を加算するとE3と等しくなるのが理想的だが、現実的には必ずしも等しい値にはならない。E1とE2を加算した値とE3との値のずれの許容範囲は、設計者が適宜設定することが可能である。

【0205】

レーザビームを単独で用いると、エネルギー密度の分布がガウス分布に従っているので、絶縁膜の平坦な部分に接している半導体膜またはアイランドとなる部分全体に均一なエネルギー密度のレーザ光を照射することが難しい。しかし、図36(D)からわかるように、複数のレーザ光を重ね合わせてエネルギー密度の低い部分を互いに補い合うようにすることで、複数のレーザ光を重ね合わせないで単独で用いるよりも、エネルギー密度が均一な領域が拡大され、半導体膜の結晶性を効率良く高めることができる。

【0206】

なお、計算によって求めた図36(C)のB−B’、C−C’におけるエネルギー密度の分布を、図37に示す。なお、図37は、合成前のレーザビームの、ピーク値の1/e2のエネルギー密度を満たしている領域を基準としている。合成前のレーザビームの短軸方向の長さを37μm、長軸方向の長さを410μmとし、中心間の距離を192μmとしたときの、B−B’、C−C’におけるエネルギー密度は、それぞれ図37(A)、図37(B)に示すような分布を有している。B−B’の方がC−C’よりも弱冠小さくなっているが、ほぼ同じ大きさとみなすことができ、合成前のレーザビームのピーク値の1/e2のエネルギー密度を満たしている領域における、合成されたレーザビームの形状は、線状と言い表すことができる。

【0207】

図38(A)は、合成されたレーザビームのエネルギー分布を示す図である。9361で示した領域はエネルギー密度が均一な領域であり、9362で示した領域はエネルギー密度が低い領域である。図38において、レーザビームの中心軸方向の長さをWTBWとし、エネルギー密度が均一な領域9361における中心軸方向の長さをWmaxとする。WTBWがWmaxに比べて大きくなればなるほど、結晶化に用いることができるエネルギー密度が均一な領域9361に対する、半導体膜の結晶化に用いることができないエネルギー密度が均一ではない領域9362の割合が大きくなる。エネルギー密度が均一ではない領域9362のみが照射された半導体膜は、微結晶が生成し結晶性が芳しくない。よって半導体膜のアイランドとなる領域と、領域9362のみを重ねないように、走査経路及び絶縁膜の凹凸のレイアウトを定める必要が生じ、領域9361に対する領域9362の比率が高くなるとその制約はさらに大きくなる。よってスリットを用いて、エネルギー密度が均一ではない領域9362のみが絶縁膜の凹部または凸部上に形成された半導体膜に照射されるのを防ぐことは、走査経路及び絶縁膜の凹凸のレイアウトの際に生じる制約を小さくするのに有効である。

【0208】

本実施例は実施例6〜12と組み合わせて実施することが可能である。

【0209】

(実施例14)

本実施例では、本発明に用いられるレーザ照射装置の光学系と、各光学系とスリットとの位置関係について説明する。

【0210】

楕円形状のレーザビームを有するレーザ光は、走査方向と垂直な方向におけるエネルギー密度の分布がガウス分布に従っているので、エネルギー密度の低い領域の全体に占める割合が、矩形または線形のレーザビームを有するレーザ光に比べて高い。そのため本発明では、レーザ光のレーザビームが、エネルギー密度の分布が比較的均一な矩形または線形であることが望ましい。

【0211】

図39は、レーザビームを4つ合成して1つのレーザビームにする場合の光学系を示している。図39に示す光学系は、6つのシリンドリカルレンズ9417〜9422を有している。矢印の方向から入射した4つのレーザ光は、4つのシリンドリカルレンズ9419〜9422のそれぞれに入射する。そしてシリンドリカルレンズ9419、9421において成形された2つのレーザ光は、シリンドリカルレンズ9417において再びそのレーザビームの形状が成形されて被処理物9423に照射される。一方シリンドリカルレンズ9420、9422において成形された2つのレーザ光は、シリンドリカルレンズ9418において再びそのレーザビームの形状が成形されて被処理物9423に照射される。

【0212】

被処理物9423における各レーザ光のレーザビームは、互いに一部重なることで合成されて1つのレーザビームを形成している。

【0213】

各レンズの焦点距離及び入射角は設計者が適宜設定することが可能であるが、被処理物9423に最も近いシリンドリカルレンズ9417、9418の焦点距離は、シリンドリカルレンズ9419〜9422の焦点距離よりも小さくする。例えば、被処理物9423に最も近いシリンドリカルレンズ9417、9418の焦点距離を20mmとし、シリンドリカルレンズ9419〜9422の焦点距離を150mmとする。そしてシリンドリカルレンズ9417、9418から被処理物9400へのレーザ光の入射角は、本実施例では25°とし、シリンドリカルレンズ9419〜9422からシリンドリカルレンズ9417、9418へのレーザ光の入射角を10°とするように各レンズを設置する。なお、戻り光を防ぎ、また均一な照射を行なうために、レーザ光の基板への入射角度を0°より大きく、望ましくは5〜30°に保つのが望ましい。

【0214】

図39では、4つのレーザビームを合成する例について示しており、この場合4つのレーザ発振装置にそれぞれ対応するシリンドリカルレンズを4つと、該4つのシリンドリカルレンズに対応する2つのシリンドリカルレンズとを有している。合成するレーザビームの数はこれに限定されず、合成するレーザビームの数は2以上8以下であれば良い。n(n=2、4、6、8)のレーザビームを合成する場合、nのレーザ発振装置にそれぞれ対応するnのシリンドリカルレンズと、該nのシリンドリカルレンズに対応するn/2のシリンドリカルレンズとを有している。n(n=3、5、7)のレーザビームを合成する場合、nのレーザ発振装置にそれぞれ対応するnのシリンドリカルレンズと、該nのシリンドリカルレンズに対応する(n+1)/2のシリンドリカルレンズとを有している。

【0215】

そして、レーザビームを5つ以上重ね合わせるとき、光学系を配置する場所及び干渉等を考慮すると、5つ目以降のレーザ光は基板の反対側から照射するのが望ましく、その場合スリットを基板の反対側にも設ける必要がある。また、基板は透過性を有していることが必要である。

【0216】

なお、戻り光がもときた光路をたどって戻るのを防ぐために、基板に対する入射角は、0より大きく90°より小さくなるように保つようにするのが望ましい。

【0217】

また、均一なレーザー光の照射を実現するためには、照射面に垂直な平面であって、かつ合成前の各ビームの形状をそれぞれ長方形と見立てたときの短辺を含む面または長辺を含む面のいずれか一方を入射面と定義すると、前記レーザー光の入射角度θは、入射面に含まれる前記短辺または前記長辺の長さがW、前記照射面に設置され、かつ、前記レーザー光に対して透光性を有する基板の厚さがdであるとき、θ≧arctan(W/2d)を満たすのが望ましい。この議論は合成前の個々のレーザー光について成り立つ必要がある。なお、レーザー光の軌跡が、前記入射面上にないときは、該軌跡を該入射面に射影したものの入射角度をθとする。この入射角度θでレーザー光が入射されれば、基板の表面での反射光と、前記基板の裏面からの反射光とが干渉せず、一様なレーザー光の照射を行うことができる。以上の議論は、基板の屈折率を1として考えた。実際は、基板の屈折率が1.5前後のものが多く、この数値を考慮に入れると上記議論で算出した角度よりも大きな計算値が得られる。しかしながら、ビームスポットの長手方向の両端のエネルギーは減衰があるため、この部分での干渉の影響は少なく、上記の算出値で十分に干渉減衰の効果が得られる。上記のθに対する不等式は、基板がレーザビームに対して透光性のあるもの以外には適用されない。

【0218】

なお本発明に用いられるレーザ照射装置が有する光学系は、本実施

例で示した構成に限定されない。

【0219】

また、複数のレーザビームを組み合わせなくとも矩形または線形のレーザビームを得られるガスレーザとして代表的なのはエキシマレーザがあり、固体レーザとして代表的なのはスラブレーザである。本発明では、これらのレーザを用いていても良い。また光ファイバーを用いて、エネルギー密度が均一な線状又は矩形状のレーザビームを形成することも可能である。

【0220】

本実施例は実施例6〜13と組み合わせて実施することが可能である。

【0221】

(実施例15)

本実施例では、レーザビームを重ね合わせたときの、各レーザビームの中心間の距離と、エネルギー密度との関係について説明する。

【0222】

図40に、各レーザビームの中心軸方向におけるエネルギー密度の分布を実線で、合成されたレーザビームのエネルギー密度の分布を破線で示す。レーザビームの中心軸方向におけるエネルギー密度の値は、一般的にガウス分布に従っている。

【0223】

合成前のビームスポットにおいて、ピーク値の1/e2以上のエネルギー密度を満たしている中心軸方向の距離を1としたときの、各ピーク間の距離をXとする。また、合成されたビームスポットにおいて、合成後のピーク値と、バレー値の平均値に対するピーク値の割増分をYとする。シミュレーションで求めたXとYの関係を、図41に示す。なお図41では、Yを百分率で表した。

【0224】

図41において、エネルギー差Yは以下の式1の近似式で表される。

【0225】

【式1】

Y=60−293X+340X2(Xは2つの解のうち大きい方とする)

【0226】

式1に従えば、例えばエネルギー差を5%程度にしたい場合、X≒0.584となるようにすれば良いということがわかる。Y=0となるのが理想的だが、それではビームスポットの長さが短くなるので、スループットとのバランスでXを決定すると良い。

【0227】

次に、Yの許容範囲について説明する。図42に、レーザビームが楕円形状を有している場合の、中心軸方向におけるビーム幅に対するYVO4レーザの出力(W)の分布を示す。斜線で示す領域は、良好な結晶性を得るために必要な出力エネルギーの範囲であり、3.5〜6Wの範囲内に合成したレーザ光の出力エネルギーが納まっていれば良いことがわかる。

【0228】

合成後のビームスポットの出力エネルギーの最大値と最小値が、良好な結晶性を得るために必要な出力エネルギー範囲にぎりぎりに入るとき、良好な結晶性が得られるエネルギー差Yが最大になる。よって図42の場合は、エネルギー差Yが±26.3%となり、上記範囲にエネルギー差Yが納まっていれば良好な結晶性が得られることがわかる。

【0229】

なお、良好な結晶性を得るために必要な出力エネルギーの範囲は、どこまでを結晶性が良好だと判断するかによって変わり、また出力エネルギーの分布もレーザビームの形状によって変わってくるので、エネルギー差Yの許容範囲は必ずしも上記値に限定されない。設計者が、良好な結晶性を得るために必要な出力エネルギーの範囲を適宜定め、用いるレーザの出力エネルギーの分布からエネルギー差Yの許容範囲を設定する必要がある。

【0230】

本実施例は、実施例6〜14と組み合わせて実施することが可能である。

【0231】

(実施例16)

本発明は様々な半導体装置に適用できるものであり、実施例6〜10に基づいて作製される表示パネルの形態を図43と図44を用いて説明する。

【0232】

図43は基板9901には画素部9902、ゲート信号側駆動回路9901a、9901b、データ信号側駆動回路9901c、入出力端子部9908、配線又は配線群9904が備えられている。シールドパターン9905はゲート信号側駆動回路9901a、9901b、データ信号側駆動回路9901c及び当該駆動回路部と入力端子とを接続する配線又は配線群9904と一部が重なっていても良い。このようにすると、表示パネルの額縁領域(画素部の周辺領域)の面積を縮小させることができる。入出力端子部9908には、FPC9903が固着されている。

【0233】

本発明は、画素部9902、ゲート信号側駆動回路9901a、9901b、データ信号側駆動回路9901cを構成する能動素子に用いることができる。

【0234】

図44は図43で示す画素部9902の一画素の構成を示す一例である。本実施例では本発明の半導体装置の1つである発光装置の、画素について説明する。なお、発光装置とは、基板上に形成された発光素子を該基板とカバー材の間に封入した表示用パネルおよび該表示用パネルにTFT等を実装した表示用モジュールを総称したものである。なお、発光素子は、電場を加えることで発生するルミネッセンス(Electro Luminescence)が得られる有機化合物を含む層(発光層)と陽極と、陰極とを有する。

【0235】

なお本実施例で用いられる発光素子は、正孔注入層、電子注入層、正孔輸送層または電子輸送層等が、無機化合物単独で、または有機化合物に無機化合物が混合されている材料で形成されている形態をも取り得る。また、これらの層どうしが互いに一部混合していても良い。

【0236】

9801は画素に入力されるビデオ信号の入力を制御するスイッチング素子としてのTFT(スイッチング用TFT)であり、9802はビデオ信号が有する情報に基づき、画素電極に電流を供給するためのTFT(駆動用TFT)である。

【0237】

スイッチング用TFT9801は、1〜2μm程度のチャネル幅の、複数のチャネル形成領域を有する活性層9803と、ゲート絶縁膜(図示せず)と、ゲート線9804の一部であるゲート電極9805とを有している。スイッチング用TFT9801は、ゲート信号側駆動回路9901a、9901bからゲート線9804に入力される選択信号によって、そのスイッチングが制御されている。

【0238】

スイッチング用TFT9801の活性層9803が有するソース領域とドレイン領域は、一方はデータ信号側駆動回路9901cによってビデオ信号が入力される信号線9806に、もう一方は素子の接続用の配線9807に接続されている。

【0239】

9820は活性層9803を形成する際に用いた下地膜の凸部である。

【0240】

一方、駆動用TFT9802は、1〜2μm程度のチャネル幅の、複数のチャネル形成領域を有する活性層9808と、ゲート絶縁膜(図示せず)と、容量用配線9809の一部であるゲート電極9810とを有している。

【0241】

駆動用TFT9802の活性層9808が有するソース領域とドレイン領域は、一方は電源線9811に、もう一方は画素電極9812に接続されている。

【0242】

9821は活性層9808を形成する際に用いた下地膜の凸部である。

【0243】

9813は容量用の半導体膜であり、ゲート絶縁膜を間に挟んで容量用配線9809と重なっている。容量用の半導体膜9813は電源線9811と接続されている。この容量用の半導体膜9813とゲート絶縁膜と容量用配線9809とが重なっている部分が駆動用TFT9802のゲート電圧を保持するための容量として機能する。また、容量用配線9809と電源線9811は、間に層間絶縁膜(図示せず)を間に挟んで重なっている。この容量用配線9809と、層間絶縁膜と、電源線9811とが重なり合っている部分も、駆動用TFT9802のゲート電圧を保持するための容量として機能させることは可能である。

【0244】

なお本明細書において接続とは、特に記載のない限り電気的な接続を意味する。

【0245】

スイッチング用TFT9801の活性層9803と、駆動用TFT9802の活性層9808とがそれぞれ有するチャネル形成領域のキャリアが移動する方向は、全て矢印に示したレーザ光の走査方向と揃っている。

【0246】

駆動用TFT9802の活性層9808が有するチャネル形成領域の数は、スイッチング用TFT9801の活性層9803が有するチャネル形成領域の数よりも多くすることが望ましい。なぜなら、駆動用TFT9802の方がスイッチング用TFT9801よりも大きな電流能力が必要であり、チャネル形成領域が多いほどオン電流を大きくすることができるからである。

【0247】

なお本実施例では発光装置に用いられるTFT基板の構成について説明したが、本実施例の作製工程を用いて液晶表示装置を作製することもできる。

【0248】

本実施例は、実施例6〜実施例10と自由に組み合わせて実施することが可能である。

【0249】

(実施例17)

本発明の半導体装置が有するTFTは、チャネル形成領域において結晶性が優れているため、通常は単結晶シリコンを用いた素子で形成される回路、例えばLSIを用いたCPU、各種ロジック回路の記憶素子(例えばSRAM)、カウンタ回路、分周回路ロジック等を、形成することができる。

【0250】

超LSIは最小寸法がサブミクロン領域に近づいており、より高集積化を目指すためには部分的な素子の三次元化が必要である。本実施例では、スタック構造を有する本発明の半導体装置の構造について説明する。

【0251】

図46に本実施例の半導体装置の断面図を示す。基板9700上に第1の絶縁膜9701が形成されている。そして、第1の絶縁膜9701上に第1のTFT9702が形成されている。なお、第1のTFT9702のチャネル形成領域のチャネル幅は、1〜2ミクロン程度である。

【0252】

第1のTFT9702を覆うように第1の層間絶縁膜9703が形成されており、第1の層間絶縁膜9703上に、第1の接続配線9705と、第1のTFT9702に電気的に接続されている配線9704とが形成されている。

【0253】

そして、配線9704、第1の接続配線9705を覆うように、第2の層間絶縁膜9706が形成されている。第2の層間絶縁膜9706は無機の絶縁膜で形成されており、酸化珪素、酸化窒化珪素などに、後の工程において照射されるレーザ光を吸収するような物質、例えば有色の顔料やカーボンを混入したものを混ぜたものを用いる。

【0254】

そして、第2の層間絶縁膜9706の上面を、化学的機械研磨法(CMP法)を用いて研磨しておくと、後に形成される第2の絶縁膜がより平坦化され、第2の絶縁膜上に形成される半導体膜をレーザ光により結晶化するときに、その結晶性をより高めることができる。

【0255】

そして第2の層間絶縁膜9706上に第2の絶縁膜9708が形成されている。そして、第2の絶縁膜9707上に第2のTFT9708が形成されている。なお、第2の絶縁膜9707のチャネル形成領域のチャネル幅は、1〜2ミクロン程度である。

【0256】

第2のTFT9708を覆うように第3の層間絶縁膜9709が形成されており、第3の層間絶縁膜9709上に、第2の接続配線9711と、第2のTFT9708に電気的に接続されている配線9710とが形成されている。なお、第1の接続配線9705と第2の接続配線9711との間にはダマシンプロセス等によって埋め込み配線(プラグ)9712が形成されている。

【0257】

そして、配線9710、第2の接続配線9711を覆うように、第4の層間絶縁膜9713が形成されている。

【0258】

本実施例では、第1のTFT9702と第2のTFT9708とを、層間絶縁膜を介して重ね合わせることができる、所謂スタック構造を有している。図46(A)では、2層のスタック構造を有する半導体装置について示したが、3層以上のスタック構造を有していても良い。その場合、下層に形成された素子にレーザ光が照射されるのを防ぐため、各層の間に、第2の層間絶縁膜9706のようなレーザ光を吸収する無機の絶縁膜を設けるようにする。

【0259】

このように三次元化された半導体装置は高集積化が可能であり、また各素子間を電気的に接続する配線を短くすることができるので、配線の容量による信号の遅延を防ぎ、より高速な動作が可能になる。

【0260】

なお本発明を用いたTFTは、第4回新機能素子技術シンポジウム予稿集、1985年7月p205.に記載されている、CAM、RAM共存チップにも用いることができる。図46(B)は、メモリ(RAM)に対応するプロセッサを配置した連想メモリ(CAM)と、RAMの共存チップ化を図ったモデルである。第1層目はワード処理系の回路が形成された層であり、第2層目は3層目のRAMに対応したプロセッサが各種論理回路によって形成された層であり、第3層目はRAMセルが形成された層である。第2層目のプロセッサと3層目のRAMセルとによって連想メモリ(CAM)が形成される。さらに、第4層目はデータ用のRAM(データRAM)であり、2層目及び3層目で形成される連想メモリと共存している。

【0261】

このように、本発明は、三次元化された様々な半導体装置に応用することが可能である。

【0262】

本実施例は、実施例6〜11と自由に組み合わせて実施することが可能である。

【0263】

(実施例18)

本発明を用いて作製されるTFTを搭載した半導体装置は、様々な電子機器への適用が可能である。その一例は、携帯情報端末(電子手帳、モバイルコンピュータ、携帯電話等)、ビデオカメラ、デジタルカメラ、パーソナルコンピュータ、テレビ受像器、携帯電話、投影型表示装置等が挙げられる。それら電子機器の具体例を図45に示す。

【0264】

図45(A)は表示装置であり、筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含む。本発明の半導体装置を表示部2003に用いることで、本発明の表示装置が完成する。発光装置は自発光型であるためバックライトが必要なく、液晶ディスプレイよりも薄い表示部とすることができる。なお、表示装置は、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

【0265】

図45(B)はデジタルスチルカメラであり、本体2101、表示部2102、受像部2103、操作キー2104、外部接続ポート2105、シャッター2106等を含む。本発明の半導体装置を表示部2102に用いることで、本発明のデジタルスチルカメラが完成する。

【0266】

図45(C)はノート型パーソナルコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を含む。本発明の半導体装置を表示部2203に用いることで、本発明のノート型パーソナルコンピュータが完成する。

【0267】

図45(D)はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。本発明の半導体装置を表示部2302に用いることで、本発明のモバイルコンピュータが完成する。

【0268】

図45(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体2401、筐体2402、表示部A2403、表示部B2404、記録媒体(DVD等)読み込み部2405、操作キー2406、スピーカー部2407等を含む。表示部A2403は主として画像情報を表示し、表示部B2404は主として文字情報を表示する。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。本発明の半導体装置を表示部A、B2403、2404に用いることで、本発明の画像再生装置が完成する。

【0269】

図45(F)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体2501、表示部2502、アーム部2503を含む。本発明の半導体装置を表示部2502に用いることで、本発明のゴーグル型ディスプレイが完成する。

【0270】

図45(G)はビデオカメラであり、本体2601、表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609、接眼部2610等を含む。本発明の半導体装置を表示部2602に用いることで、本発明のビデオカメラが完成する。

【0271】

ここで図45(H)は携帯電話であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。なお、表示部2703は黒色の背景に白色の文字を表示することで携帯電話の消費電流を抑えることができる。本発明の半導体装置を表示部2703に用いることで、本発明の携帯電話が完成する。

【0272】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また、本実施例は実施例6〜12に示したいずれの構成とも組み合わせて実施することが可能である。

【0273】

(実施例19)

本発明の半導体装置が有するマルチチャネルTFTは、フラットな絶縁膜上において結晶化された半導体膜を用いて形成されるシングルチャネルTFT及びマルチチャネルTFTよりも、S値、移動度、閾値などのばらつきが抑えられる。

【0274】

図47(A)に、本発明のn型のマルチチャネルTFTの、S値の度数分布を示す。本発明のマルチチャネルTFTは、凹凸を有する絶縁膜上において、レーザー光の照射により結晶化された半導体膜を用いている。絶縁膜の凸部と凹部の幅はそれぞれ1.25μm、1.50μmであり、TFTのチャネル長は8μm、トータルのチャネル幅は12μmである。

【0275】

また比較のために、図47(B)に、フラットな絶縁膜上において結晶化されたn型のシングルチャネルTFTの、S値の度数分布を示す。TFTのチャネル長は8μm、チャネル幅は8μmである。また、図47(C)に、フラットな絶縁膜上において結晶化されたn型のマルチチャネルTFTの、S値の度数分布を示す。TFTのチャネル長は8μm、トータルのチャネル幅は12μm、各チャネルの幅が2μm、チャネル間の間隔が2μmである。

【0276】

図47(B)では標準偏差がσ=15.8mV/dec.、図47(C)では標準偏差がσ=19.9mV/dec.なのに対し、図47(A)では標準偏差がσ=8.1mV/dec.となっており、先の2つに比べて小さい。よって図47(A)に示す本発明のn型のマルチチャネルTFTはS値のばらつきが抑えられていることがわかる。

【0277】

なお、図47(B)のTFTのチャネル幅は、図47(A)のTFTのトータルのチャネル幅よりも短い。また図47(C)のTFTは図47(A)のTFTよりも各チャネルの幅とチャネル間の間隔が長い。しかし、これらの条件を考慮に入れても図47(B)及び図47(C)に比べて図47(A)の標準偏差は著しく小さいと考えられ、よって、本発明のnチャネル型のTFTは、S値が抑えられるという効果を有すると推測される。

【0278】

次に図48(A)に、本発明のn型のマルチチャネルTFTの、閾値の度数分布を示す。図48(A)のTFTの構成は図47(A)の場合と同じである。また比較のために、図48(B)に、フラットな絶縁膜上において結晶化されたn型のシングルチャネルTFTの、閾値の度数分布を示す。図48(B)のTFTの構成は図47(C)の場合と同じである。また、図48(C)に、フラットな絶縁膜上において結晶化されたn型のマルチチャネルTFTの、閾値の度数分布を示す。図48(C)のTFTの構成は図47(B)の場合と同じである。

【0279】

図48(B)では標準偏差がσ=126mV、図48(C)では標準偏差がσ=153mVなのに対し、図48(A)では標準偏差がσ=80mVとなっており、先の2つに比べて小さい。よって図48(A)に示す本発明のn型のマルチチャネルTFTは閾値のばらつきが抑えられていることがわかる。

【0280】

なお、図48(B)のTFTのチャネル幅は、図48(A)のTFTのトータルのチャネル幅よりも短い。また図48(C)のTFTは図48(A)のTFTよりも各チャネルの幅とチャネル間の間隔が長い。しかし、これらの条件を考慮に入れても図48(B)及び図48(C)に比べて図48(A)の標準偏差は著しく小さいと考えられ、よって、本発明のnチャネル型のTFTは、閾値が抑えられるという効果を有すると推測される。

【0281】

次に図49(A)に、本発明のn型のマルチチャネルTFTの、移動度の度数分布を示す。図49(A)のTFTの構成は図47(A)の場合と同じである。また比較のために、図49(B)に、フラットな絶縁膜上において結晶化されたn型のシングルチャネルTFTの、移動度の度数分布を示す。図49(B)のTFTの構成は図47(B)の場合と同じである。また、図49(C)に、フラットな絶縁膜上において結晶化されたn型のマルチチャネルTFTの、移動度の度数分布を示す。図49(C)のTFTの構成は図47(B)の場合と同じである。

【0282】

図49(B)では標準偏差がσ=7.9%、図49(C)では標準偏差がσ=9.2%なのに対し、図49(A)では標準偏差がσ=5.2%となっており、先の2つに比べて小さい。よって図49(A)に示す本発明のn型のマルチチャネルTFTは移動度のばらつきが抑えられていることがわかる。なお図49(A)ではチャネル幅の設計値を用いて移動度を計算しているので、実際の移動度は2割程度低いと考えられる。

【0283】

図49(B)のTFTのチャネル幅は、図49(A)のTFTのトータルのチャネル幅よりも短い。また図49(C)のTFTは図49(A)のTFTよりも各チャネルの幅とチャネル間の間隔が長い。

しかし、これらの条件を考慮に入れても図49(B)及び図49(C)に比べて図49(A)の標準偏差は著しく小さいと考えられ、よって、本発明のnチャネル型のTFTは、移動度が抑えられるという効果を有すると推測される。

【0284】

次に図50(A)に、本発明のp型のマルチチャネルTFTの、閾値の度数分布を示す。図50(A)のTFTの構成は、極性が異なるだけで図47(A)の場合と同じである。また比較のために、図50(B)に、フラットな絶縁膜上において結晶化されたp型のシングルチャネルTFTの、閾値の度数分布を示す。図50(B)のTFTの構成は、極性が異なるだけで図47(B)の場合と同じである。また、図50(C)に、フラットな絶縁膜上において結晶化されたp型のマルチチャネルTFTの、閾値の度数分布を示す。図50(C)のTFTの構成は、極性が異なるだけで図47(C)の場合と同じである。

【0285】

図50(B)では標準偏差がσ=218mV、図50(C)では標準偏差がσ=144mVなのに対し、図50(A)では標準偏差がσ=77mVとなっており、先の2つに比べて小さい。よって図50(A)に示す本発明のp型のマルチチャネルTFTは閾値のばらつきが抑えられていることがわかる。

【0286】

なお、図50(B)のTFTのチャネル幅は、図50(A)のTFTのトータルのチャネル幅よりも短い。また図50(C)のTFTは図50(A)のTFTよりも各チャネルの幅とチャネル間の間隔が長い。しかし、これらの条件を考慮に入れても図50(B)及び図50(C)に比べて図50(A)の標準偏差は著しく小さいと考えられ、よって、本発明のpチャネル型のTFTは、閾値が抑えられるという効果を有すると推測される。

【0287】

次に図51(A)に、本発明のp型のマルチチャネルTFTの、移動度の度数分布を示す。図51(A)のTFTの構成は、極性が異なるだけで図47(A)の場合と同じである。また比較のために、図51(B)に、フラットな絶縁膜上において結晶化されたp型のシングルチャネルTFTの、移動度の度数分布を示す。図51(B)のTFTの構成は、極性が異なるだけで図47(B)の場合と同じである。また、図51(C)に、フラットな絶縁膜上において結晶化されたp型のマルチチャネルTFTの、移動度の度数分布を示す。図51(C)のTFTの構成は、極性が異なるだけで図47(B)の場合と同じである。

【0288】

図51(B)では標準偏差がσ=7.6%、図51(C)では標準偏差がσ=5.9%なのに対し、図51(A)では標準偏差がσ=4.6%となっており、先の2つに比べて小さい。よって図51(A)に示す本発明のp型のマルチチャネルTFTは移動度のばらつきが抑えられていることがわかる。なお図51(A)ではチャネル幅の設計値を用いて移動度を計算しているので、実際の移動度は2割程度低いと考えられる。

【0289】

なお、図51(B)のTFTのチャネル幅は、図51(A)のTFTのトータルのチャネル幅よりも短い。また図51(C)のTFTは図51(A)のTFTよりも各チャネルの幅とチャネル間の間隔が長い。しかし、これらの条件を考慮に入れても図51(B)及び図51(C)に比べて図51(A)の標準偏差は著しく小さいと考えられ、よって、本発明のpチャネル型のTFTは、移動度が抑えられるという効果を有すると推測される。

【0290】

図47〜図51に示したように、本発明のマルチチャネルTFTは特性のばらつきが抑えられるという効果を有している。本発明のマルチチャネルTFTは、フラットな絶縁膜上において結晶化を行なったシングルチャネルTFT及びマルチチャネルTFTに比べて、各チャネルの結晶方位が回転しやすいので、種々の結晶方位を含んでいる。よって結晶方位に起因する特性のばらつきが平均化され易いのではないかと考えられる。

【0291】

【発明の効果】

絶縁表面上に形成した開口部に半導体を充填するように溶融結晶化させることにより、結晶化に伴い発生する歪みを開口部以外の領域に集中させることができる。即ち、開口部に充填されるように形成した結晶性半導体膜においては歪みから開放することができる。

【0292】

即ち、非単結晶半導体膜に連続発振レーザ光を照射する結晶化において、下地絶縁膜に開口部を設け、溶融結晶化の過程において当該開口部に半導体を充填するように形成することにより、結晶化に伴う歪みや結晶粒界又は結晶亜粒界を開口部以外の領域に集中させることができる。そして、開口部の結晶性半導体膜にチャネル形成領域が配設されるようにTFTを形成することにより、高速で電流駆動能力を向上させることが可能となり、素子の信頼性を向上させることも可能となる。

【0293】

本発明では、下地膜の凹部上に位置する半導体膜を、TFTの活性層として積極的に用いることで、TFTのチャネル形成領域に粒界が形成されるのを防ぐことができ、粒界によってTFTの移動度が著しく低下したり、オン電流が低減したり、オフ電流が増加したりするのを防ぐことができる。なお、どこまでを凸部または凹部のエッジ近傍としてパターニングで除去するかは、設計者が適宜定めることができる。

【0294】

また、TFTの複数のチャネル形成領域が互いに分離していることで、チャネル形成領域のうち、ゲート絶縁膜を間に挟んでゲート電極と重なっている領域を広く取ることができるので、チャネル幅を長くすることができる。チャネル幅を長くすることでオン電流を確保しつつ、TFTを駆動させることで発生した熱を効率的に放熱することができる。

【図面の簡単な説明】

【図1】 本発明における結晶化方法を説明する斜視図。

【図2】 本発明における結晶化方法を説明する斜視図。

【図3】 本発明における結晶化方法を説明する斜視図。

【図4】 本発明における結晶化方法を説明する斜視図。

【図5】 結晶化における開口部の形状と結晶性半導体膜の形態との関係の詳細を説明する縦断面図。

【図6】 本発明に適用するレーザ照射装置の一態様を示す配置図。

【図7】 本発明により作製されるTFTの作製工程を説明する上面図及び縦断面図。

【図8】 本発明により作製されるTFTの作製工程を説明する上面図及び縦断面図。

【図9】 本発明により作製されるTFTの作製工程を説明する上面図及び縦断面図。

【図10】 本発明により作製されるTFTの作製工程を説明する上面図及び縦断面図。

【図11】 本発明により作製されるTFTの作製工程を説明する上面図及び縦断面図。

【図12】 本発明により作製されるTFTの一例を説明する上面図及び縦断面図。

【図13】 本発明により作製されるTFTの一例を説明する上面図及び縦断面図。

【図14】 本発明により作製されるTFTの一例を説明する上面図及び縦断面図。

【図15】 表示パネルの外観図。

【図16】 本発明を用いて作製される表示パネルの画素部の構造を説明する上面図。

【図17】 熱解析のシミュレーションに用いた構造を示す断面図。

【図18】 熱解析のシミュレーションの結果を示すグラフ。

【図19】 凸部を有する下地膜上に形成された半導体膜にレーザ光を照射して結晶化させた後のTEMの断面像と、その模式図。

【図20】 本発明の半導体膜の結晶化の流れを示す図。

【図21】 本発明のTFTの作製工程を示す図。

【図22】 本発明のTFTの作製工程を示す図。

【図23】 本発明のTFTの作製工程を示す図。

【図24】 本発明のTFTの作製工程を示す図。

【図25】 本発明のTFTの作製工程を示す図。

【図26】 本発明のTFTの断面図。

【図27】 本発明のTFTの断面図。

【図28】 本発明のTFTの作製工程を示す図。

【図29】 本発明のTFTの作製工程を示す図。

【図30】 下地膜上に形成された複数のTFTの上面図。

【図31】 触媒元素を用いた本発明の半導体膜の結晶化の流れを示す図。

【図32】 レーザ照射装置の図。

【図33】 レーザ照射装置の図。

【図34】 凸部を有する下地膜の作製方法を示す図。

【図35】 凸部を有する下地膜の作製方法を示す図。

【図36】 レーザビームのエネルギー密度の分布を示す図。

【図37】 レーザビームのエネルギー密度の分布を示す図。

【図38】 レーザビームのエネルギー密度の分布を示す図。

【図39】 光学系の図。

【図40】 重ね合わせたレーザビームの中心軸方向におけるエネルギー密度の分布を示す図。

【図41】 レーザビームの中心間の距離とエネルギー差の関係を示す図。

【図42】 レーザビームの中心軸方向における出力エネルギーの分布を示す図。

【図43】 本発明の半導体装置の一例である発光装置の構造を示す図。

【図44】 本発明の半導体装置の一例である発光装置の画素の構造を示す図。

【図45】 本発明の半導体装置を用いた電子機器の図。

【図46】 スタック構造を有するTFTの断面図及びそれを用いた半導体装置の構成の一例。

【図47】 S値の度数分布を示す図。

【図48】 閾値の度数分布を示す図。

【図49】 移動度の度数分布を示す図。

【図50】 閾値の度数分布を示す図。

【図51】 移動度の度数分布を示す図。

Claims (8)

- 所定の間隔を隔てて互いに平行に配列された複数の短冊状の領域と、前記複数の短冊状の領域それぞれの一端に連接して設けられた第1の領域と、前記複数の短冊状の領域それぞれの他端に連接して設けられた第2の領域とからなる開口部が設けられた絶縁膜を基板上に形成し、

前記開口部及び前記絶縁膜上に半導体膜を形成し、

前記半導体膜にレーザ光を照射して結晶性半導体膜を形成し、

前記結晶性半導体膜のうち、前記開口部上に形成された前記結晶性半導体膜を用いて島状の半導体領域を形成し、

前記複数の短冊状の領域上に形成された前記島状の半導体領域の周辺部に設けられた前記絶縁膜をエッチングして、前記複数の短冊状の領域上に形成された前記島状の半導体領域の側面部を露出させ、

前記島状の半導体領域及び前記エッチングされた絶縁膜を覆うようにゲート絶縁膜を形成し、

前記ゲート絶縁膜を介して、前記複数の短冊状の領域上に形成された前記島状の半導体領域の側面部及び上面部と重なるようにゲート電極を形成することを特徴とする半導体装置の作製方法。 - 基板上に第1の絶縁膜を形成し、

所定の間隔を隔てて互いに平行に配列された複数の短冊状の領域と、前記複数の短冊状の領域それぞれの一端に連接して設けられた第1の領域と、前記複数の短冊状の領域それぞれの他端に連接して設けられた第2の領域とからなる開口部が設けられた第2の絶縁膜を前記第1の絶縁膜上に形成し、

前記開口部及び前記第2の絶縁膜上に半導体膜を形成し、

前記半導体膜にレーザ光を照射して結晶性半導体膜を形成し、

前記結晶性半導体膜のうち、前記開口部上に形成された前記結晶性半導体膜を用いて島状の半導体領域を形成し、

前記複数の短冊状の領域上に形成された前記島状の半導体領域の周辺部に設けられた前記第2の絶縁膜をエッチングして、前記複数の短冊状の領域上に形成された前記島状の半導体領域の側面部を露出させ、

前記島状の半導体領域及び前記エッチングされた第2の絶縁膜を覆うようにゲート絶縁膜を形成し、

前記ゲート絶縁膜を介して、前記複数の短冊状の領域上に形成された前記島状の半導体領域の側面部及び上面部と重なるようにゲート電極を形成することを特徴とする半導体装置の作製方法。 - 請求項1または2において、前記基板としてガラス基板、石英基板、サファイア基板、または耐熱性を有するプラスチック基板を用いることを特徴とする半導体装置の作製方法。

- 請求項1または2において、前記基板として単結晶半導体基板、多結晶半導体基板、金属基板、またはステンレス基板の表面を絶縁膜で被覆した基板を用いることを特徴とする半導体装置の作製方法。

- 請求項1乃至4のいずれか一において、前記レーザ光は連続発振であることを特徴とする半導体装置の作製方法。

- 請求項1乃至5のいずれか一において、前記レーザ光は、YAGレーザ、YVO4レーザ、YLFレーザ、YAlO3レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、Y2O3レーザまたはNd:YVO4レーザから選ばれた一種または複数種を用いて出力されていることを特徴とする半導体装置の作製方法。

- 請求項1乃至6のいずれか一において、前記レーザ光はスラブ構造増幅器を用いて出力されていることを特徴とする半導体装置の作製方法。

- 請求項1乃至7のいずれか一において、前記レーザ光は第2高調波または第3高調波であることを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003018377A JP4312466B2 (ja) | 2002-01-28 | 2003-01-28 | 半導体装置の作製方法 |

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002-19286 | 2002-01-28 | ||

| JP2002019286 | 2002-01-28 | ||

| JP2002-27381 | 2002-02-04 | ||

| JP2002027381 | 2002-02-04 | ||

| JP2003018377A JP4312466B2 (ja) | 2002-01-28 | 2003-01-28 | 半導体装置の作製方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005198205A Division JP2005340852A (ja) | 2002-01-28 | 2005-07-07 | 半導体装置及び電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003297751A JP2003297751A (ja) | 2003-10-17 |

| JP2003297751A5 JP2003297751A5 (ja) | 2006-03-09 |

| JP4312466B2 true JP4312466B2 (ja) | 2009-08-12 |

Family

ID=29407496

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003018377A Expired - Fee Related JP4312466B2 (ja) | 2002-01-28 | 2003-01-28 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4312466B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006066908A (ja) * | 2004-07-30 | 2006-03-09 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| US7700463B2 (en) | 2005-09-02 | 2010-04-20 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR102103913B1 (ko) * | 2012-01-10 | 2020-04-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작 방법 |

| JP6781872B2 (ja) | 2016-07-20 | 2020-11-11 | 株式会社ブイ・テクノロジー | レーザ照射装置および薄膜トランジスタの製造方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5886717A (ja) * | 1981-11-18 | 1983-05-24 | Nec Corp | 単結晶シリコン膜形成法 |

| JPH02143417A (ja) * | 1988-11-24 | 1990-06-01 | Sharp Corp | 半導体装置の製造方法 |

| JP3150840B2 (ja) * | 1994-03-11 | 2001-03-26 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP3216861B2 (ja) * | 1995-04-10 | 2001-10-09 | シャープ株式会社 | 多結晶シリコン膜の形成方法および薄膜トランジスタの製造方法 |

| JPH11121753A (ja) * | 1997-10-14 | 1999-04-30 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP2000068520A (ja) * | 1997-12-17 | 2000-03-03 | Matsushita Electric Ind Co Ltd | 半導体薄膜、その製造方法、および製造装置、ならびに半導体素子、およびその製造方法 |

| JP2000183351A (ja) * | 1998-12-11 | 2000-06-30 | Sony Corp | 薄膜半導体装置の製造方法 |

| JP3897965B2 (ja) * | 1999-08-13 | 2007-03-28 | 株式会社半導体エネルギー研究所 | レーザー装置及びレーザーアニール方法 |

| JP4836333B2 (ja) * | 2000-01-28 | 2011-12-14 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2001274433A (ja) * | 2000-03-24 | 2001-10-05 | Japan Steel Works Ltd:The | シリコン膜の結晶化方法及び多結晶シリコン膜の製造方法並びに多結晶シリコン膜を用いたディバイス |

| JP5057613B2 (ja) * | 2000-04-27 | 2012-10-24 | 株式会社半導体エネルギー研究所 | 半導体装置及び電子機器 |

| JP4683761B2 (ja) * | 2000-05-12 | 2011-05-18 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

-

2003

- 2003-01-28 JP JP2003018377A patent/JP4312466B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003297751A (ja) | 2003-10-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5997802B2 (ja) | 半導体装置 | |

| US7737506B2 (en) | Semiconductor device and method of manufacturing the same | |

| US10515983B2 (en) | Semiconductor device and semiconductor device production system | |

| US7709895B2 (en) | Semiconductor device having insulating stripe patterns | |

| KR20030057484A (ko) | 반도체 장치 및 그 반도체 장치의 생산 시스템 | |

| JP4312466B2 (ja) | 半導体装置の作製方法 | |

| JP4387099B2 (ja) | 半導体装置の生産方法 | |

| JP4397599B2 (ja) | 半導体装置の作製方法 | |

| JP2005340852A (ja) | 半導体装置及び電子機器 | |

| JP4627135B2 (ja) | 半導体装置の生産方法 | |

| JP4137461B2 (ja) | 半導体装置の作製方法 | |

| JP4526764B2 (ja) | 半導体装置及び半導体装置の生産システム | |

| CN101299412B (zh) | 半导体器件及其制造方法 | |

| JP4338996B2 (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060119 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060119 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080714 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080805 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080917 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090512 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090513 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120522 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120522 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120522 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130522 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130522 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140522 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |