JP4299370B2 - 双極静電チャックにおけるプラズマバイアス電圧のオフセット方法および装置 - Google Patents

双極静電チャックにおけるプラズマバイアス電圧のオフセット方法および装置 Download PDFInfo

- Publication number

- JP4299370B2 JP4299370B2 JP50568999A JP50568999A JP4299370B2 JP 4299370 B2 JP4299370 B2 JP 4299370B2 JP 50568999 A JP50568999 A JP 50568999A JP 50568999 A JP50568999 A JP 50568999A JP 4299370 B2 JP4299370 B2 JP 4299370B2

- Authority

- JP

- Japan

- Prior art keywords

- output

- voltage

- resistor

- power supply

- control circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6831—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using electrostatic chucks

- H01L21/6833—Details of electrostatic chucks

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02N—ELECTRIC MACHINES NOT OTHERWISE PROVIDED FOR

- H02N13/00—Clutches or holding devices using electrostatic attraction, e.g. using Johnson-Rahbek effect

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T279/00—Chucks or sockets

- Y10T279/23—Chucks or sockets with magnetic or electrostatic means

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Container, Conveyance, Adherence, Positioning, Of Wafer (AREA)

Description

【0001】

本発明は、半導体装置と半導体製造用装置に関する。より詳細には、本発明は、プラズマ処理チャンバにおいて半導体基板を双極静電チャックにクランプするための改良装置および方法に関する。

【背景技術】

【0002】

プラズマ処理システムにおける双極静電チャックの使用は、広く知られている。説明を容易にするため、双極静電チャックの使用に適したチャンバを表す基板処理チャンバの概略図を図1に示す。図1において、基板プラズマ処理システム100はプラズマ処理チャンバ110を含む。チャンバ110の内部にはRF発生器108によって励磁されるシャワヘッド型またはTCPコイルを表す電極104が配置されている。

【0003】

チャンバ110の上部には、ガス状原料物質(例えば、エッチングガス)が送り込まれるガスオリフィス102が電極104の上部へと延出するように設けられている。この実施例ではシャワヘッド型電極104は、半導体基板またはフラットパネルディスプレイなどを表す基板112上のRF誘導プラズマ領域134へとガス状原料物質を拡散させるための複数のバッフル106を含む。ガス状原料物質は、チャンバの壁に穿設されたポートから、または基板の下に配置されたガスリング装置から放出される。

【0004】

チャンバ110に挿入された基板112は、双極静電チャック114上に載置される。双極静電チャック114は、下部電極116と一体的に取付けられ、電気的に接続されている。したがって、双極静電チャック114と下部電極116のRF電位は同一となる。下部電極116は一般的にRF発生器108からRF出力を受けとる。電源170は、導線123により第1埋込板152に負バイアス電圧VNを送るとともに、導線124により第2埋込板150に正バイアスVPを供給する。

【0005】

RF発生器108により供給されるRFエネルギーから電源170を保護するため、電源170とRF発生器108との間にRFフィルタ(従来型なので、簡略化のため図1では省略)を配設してもよい。同様にRF発生器108が、電源170から供給される直流電位レベルの影響を受けないよう、電源170とRF発生器108との間に直流阻止コンデンサ(従来型なので、簡略化のため図1では省略)を設けてもよい。

【0006】

下部電極116と静電チャック114の両者を貫通し、冷却剤ポート122が延在している。加圧された(一実施例では、例えば約5−10Torr)ヘリウム冷却ガスが冷却材オリフィス122から導入される。ヘリウム冷却ガスは基板112の下面に衝突し、処理中に基板の温度を正確に調節するための熱伝導媒体として作用するので、均一かつ反復的な処理結果が得られる。プラズマ処理中にあっては、ポート160からガスを抜くことによりチャンバ110内の圧力は低く、例えば一実施例では約5から25Torrに維持されることが望ましい。エッチングに適したチャンバ温度(例えば一実施例では約70℃)に維持するため、複数のヒータ(簡略化のため、図1では省略)を設けることができる。接地への電気経路を設けるため、通常、チャンバ110の壁111は接地されている。

【0007】

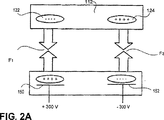

図2Aは図1の双極静電チャック114の断面を詳細に示す。名前が示すように双極静電チャック114は、2枚の埋込板、すなわち負帯電埋込板152と正帯電埋込板150とを有する。双極静電チャック114の両埋込板は図1の電源に接続されている。電源170がオンになると、埋込板150は電源170により共通の基準電位レベルに対して正にバイアスされる。電源170はまた、共通の基準電位レベルに対して埋込板152を負にバイアスする。埋込板150と152は固定位置にあるため、帯電埋込板により発生する静電界は、各埋込板の周囲領域に良好に画定される。

【0008】

p型の半導体ウエハの場合、基板112の孔は負バイアス埋込板152を直接被覆する基板領域へと移動する。この結果、埋込板152により静電チャック114に発生する電界と電界強度が同じであると共に極性が逆の実効正電荷領域が形成される。結果的に、正バイアス埋込板150を直接被覆する基板112の領域に、実効負電荷領域が形成される。同様にして、n型半導体ウエハの場合も基板112内の電子は正の埋込板150を直接被覆する基板112の領域へと移動する。したがって、埋込板150により静電チャック114に発生する電界と電界強度は同じで極性が逆の実効負電荷領域が形成される。その結果、負バイアス埋込板152を直接被覆する基板112の領域に実効正電荷領域が形成される。

【0009】

当業者には周知であるように、基板112と静電チャック114のバイアス板150,152とに互いに逆の電荷を持つ領域が存在することにより、基板112と静電チャック114とを結合させる誘導静電力が発生する。一例として図2Aには正帯電板150と基板112の負帯電領域122との間に静電力F1が図示されている。図2Aには、負帯電板152と基板112の正帯電領域124との間に静電力F2も図示されている。当業者にとって周知のように、力F1の強さは、バイアス板150と帯電領域122との間の電位差に正比例する。同様にF2の強さはバイアス板152と帯電領域124との電位差に正比例する。この例では静電力F1とF2は基板112を静電チャック114にクランプする作用を行う。

【0010】

一般的にプラズマ処理中は、加工物すなわち基板に印加されるクランプ力が平衡を保つ(すなわち静電力F1と静電力F2の強さは概ね等しい)ことが望ましい。

【0011】

しかし、チャンバ110に負帯電プラズマを導入すると、基板112はプラズマ誘導バイアス−VBにより静電チャックに対して負バイアスされる。一例として図2Bには静電クランプ力F1とF2への負帯電プラズマ180の影響が図示されている。基板112のプラズマ誘導バイアス−VBにより、基板112の誘導帯電領域122と124およびバイアス埋込板150と152(電源170により共通の接地に対して一定の電位に保持される)との間の相対的電圧電位低下がオフセットされる。静電力F1とF2は領域122,124と板150,152との間の相対的電位差に正比例するため、プラズマ誘導バイアス−VBはクランプ力F1を増大させ力F2を減少させることによりクランプ力F1と力F2との平衡を崩す。

【0012】

この状態を説明するため、電源170が共通の基準電圧レベルに対して正電極204を+350V、負電極206を−350Vにバイアスする場合を検討する。プラズマをオフにすると、基板の電位は共通の基準電圧レベルに対して0Vとなり、双極チャック114の両極とこれらを被覆する基板領域との間の電位差はそれぞれ+350Vと−350Vとなる。

【0013】

しかしプラズマの存在により基板112が負に帯電すると、基板と双極静電チャックの二極との間の電位差は非対称となる。例えば基板バイアス電圧はプラズマがオンになると−100Vとなる。この場合、正極と負バイアス基板の間の電位差は+450V(すなわち+350V−(−100V))まで上昇する。しかし負極と負バイアス基板の間の電位差は−250V(すなわち−350V−(−100V))までしか低下しない。電位差の低下により、負極とウエハ間の静電保持力が低下する。結果的に何らかの熱交換ガスが放出されて、温度調節および/または処理の変動は不適切なものとなる。場合によっては、基板を双極チャックに保持する静電力は、ヘリウム冷却圧力とチャンバ内の低圧との間の圧力差により基板に加えられる力に抗するのに不十分なほど弱くなることもあり、その結果、基板がチャックの表面から「突然離れてしまう」ことになる。

【0014】

さらに、プラズマ誘導負基板バイアスは、負バイアス基板と双極チャックの正極との間の電位差を過度に増加させることがある。電位差が極端に高いと、基板の下面とチャックの上面の間にアーク(すなわちスパーク)を発生させたり過剰な電流をプラズマに出入りさせ、その結果、食孔跡損傷(ピットマークダメージ)を引き起こす。チャックの表面は時間とともに、熱交換ガスが正常にシールされた状態に維持するのが不可能となるほどの損傷を受ける。

【0015】

プラズマ誘導バイアスを補償するための先行技術による試みが、図3に示されている。静電チャック414は、負バイアス埋込板420と正バイアス板418とを含む。直流電源406と直流電源408は、基板416に反対かつ等しい帯電領域を形成するため可変接地基準ノード407に対して必要な電圧電位を板418と420にそれぞれ供給する。この反対かつ概ね等しい帯電領域は、必要なクランプ力を生み出す。ピックアップピン402は、ウエハ416で発生したプラズマ誘導バイアスを検出するようにチャンバ内に配置され、このようにして基準ノード407を変えるのに必要な入力を提供する。可変接地基準ノード407は、板418と420に印加される電位を適当に上下させることにより、誘導プラズマバイアスを補償するという効果を持つ。

【0016】

しかしピックアップピン402の使用には不都合な点が多い。その一つは、ピックアップピン402は基板416におけるプラズマ誘導バイアスを概算するのみという点にある。さらにこの概算は、ユーザによる制御が不可能な多くの要因に影響される。一例を挙げると、ピックアップピン402は、時間超過に伴って強力なプラズマイオンがピックアップピンの粒子を離脱させてチャンバ内のプラズマを汚染させるスパッタリングとして当該技術分野で周知のプラズマ誘導ダメージを受ける。このダメージは、望ましくない汚染を生じさせるだけでなく、定期的な校正と調整(すなわち、ピックアップピン420の電気的性質の変化を補償するための抵抗器ブリッジ450を設けること)に加えて、最終的には著しい稼働休止時間と生産高の損失をもたらす交換を必要とするのでピックアップピンの電気的性質を変えてしまうこともある。

【0017】

ピックアップピン402が位置する領域のプラズマと、基板416の表面に衝突するプラズマとが大きく異なっている場合、ピックアップピン402によっては基板416のプラズマ誘導バイアスを適切に補償することはできない。このピックアップピン402で見られるプラズマとウエハ416のプラズマとの違いは、例えば空間的変化(すなわちプラズマの密度/温度の径方向の分布)、不規則な幾何学形状によるプラズマ自体の不均一性といった要因による。実際、これらの要因のいずれか一つでも存在する場合、プラズマ誘導バイアス補償機構としてのピックアップピン402の使用は満足のいくものとならない。

【発明の開示】

【発明が解決しようとする課題】

【0018】

以上から見て、プラズマの存在下では特に、双極静電チャックへの基板のクランプを改良するための技術向上が望ましい。コスト削減および/または汚染低減のため、ピックアップピンおよび/または第2電源もしくは複雑な制御回路の使用を必要としないことが、改良技術にとって望ましい。

【課題を解決するための手段】

【0019】

一実施形態において本発明は、静電チャック電源の基準ノードの基準電圧を制御するよう構成された制御回路に関する。静電チャック電源は、基板を双極静電チャックにクランプするよう構成されている。静電チャックは、第1埋込導体と第2埋込導体とを有する。静電チャック電源は、第1埋込導体と接続されるよう構成された第1出力を有する。第1出力は、基準ノードの基準電圧を基準とする第1出力電圧を有する。静電チャック電源は、第2埋込導体と接続されるよう構成された第2出力をさらに有する。第2出力は、基準ノードの基準電圧を基準とする第2出力電圧を有する。

【0020】

制御回路は、第1出力に直列接続された第1抵抗器と、第1抵抗器における第1電圧降下を検出するため第1抵抗器に接続された第1増幅器と、第2出力に直列接続された第2抵抗器と、第2抵抗器における第2電圧降下を検出するため第2抵抗器に接続された第2増幅器とを含む。

【0021】

別の実施形態では、第1埋込導体と第2埋込導体とを有する双極静電チャックと接続されるよう構成された電源が開示されている。電源は、基準ノードと、第1出力が基準ノードを基準とする第1出力電圧を有するよう、第1埋込導体と接続される構成の第1出力とを含む。この電源は、第2埋込導体と接続されるよう構成された第2出力をさらに有し、第2出力は、基準ノードを基準とする第2出力電圧を有する。この電源は、第1出力と第2出力とに接続された制御回路をさらに含む。この制御回路は、第1出力の第1電流と第2出力の第2電流との電流差を検出する。この制御回路は、制御回路の制御出力において、基準ノードの電位レベルを制御するための制御電圧を出力する。制御電圧は、電流差に概ね比例する。

【0022】

さらに別の実施形態では、プラズマ処理センターで基板を第1埋込導体と第2埋込導体とを有するチャックにクランプする方法が開示されている。この方法には以下の作業工程が含まれる。基準ノードと第1出力と第2出力とを有し、前記第1出力および第2出力が制御回路に接続されている第1電源を提供する工程。この実施例では、第1埋込導体が第1出力に接続され第2埋込導体が第2出力に接続され、第1出力の第1電流と第2出力の第2電流との電流差が制御回路によって検出される。制御回路は、電流差に概ね比例すると共に、第2電源から出力される電位レベルを制御する制御電圧を第2の電源に対して出力し、第2電源は受け取った制御電圧に応じて、基準ノードに電位レベルを出力する。制御電圧は、電流差に概ね比例する。

【0023】

また別の実施形態では、静電チャック電源の基準ノードの基準電圧を制御するよう構成された制御回路が開示されている。静電チャック電源は、第1埋込導体と第2埋込導体とを有する双極静電チャックに基板をクランプするように構成されている。静電チャック電源は、第1埋込導体に接続されよう構成された第1出力を有する。第1出力は、基準ノードの基準電圧を基準とする第1出力電圧を有する。静電チャック電源は、第2埋込導体に接続されるよう構成された第2出力をさらに有する。第2出力は、基準ノードの基準電圧を基準とする第2出力電圧を有する。制御回路は、第1出力に直列接続された第1抵抗手段を含む。第1抵抗手段での第1電圧降下を検出するため、第1検出手段が第1抵抗手段に接続されている。制御回路は、第2検出手段とともに第2出力に直列接続された第2抵抗手段をさらに含む。第2検出手段は、第2抵抗手段での第2電圧降下を検出するため、第2抵抗手段に接続されている。

【0024】

添付図面の図において本発明は限定のためではなく例示のために図示されている。理解を容易にするため以下の図では、同様の参照番号は同様または類似の要素を示す。

【発明を実施するための最良の形態】

【0025】

添付図面に図示された、いくつかの好適な実施例について、本発明を詳細に説明する。以下の説明では、本発明の完全な理解を促すために特定の詳細事項が数多く記載されている。しかしながら、これら特定の詳細の一部または全てがない場合でも、本発明を実行できることは当業者にとって明らかであろう。他の例では、本発明が不必要に不明瞭となることを避けるため周知の処理工程については詳細に記されていない。

【0026】

本発明は、自己バイアス電源の使用による、プラズマ処理チャンバ内の双極静電チャックにおけるプラズマ誘導バイアス電圧の補償に関する。本発明の一実施例では、電源は、プラズマ処理中に印加されるバイアス電圧の量を測定するため静電チャックの漏れ電流特性を利用する。バイアス電圧は電源の正の導線と負の導線の間で漏れ電流をオフセットする。これにより、プラズマ誘導バイアス電圧を補償する接地基準のオフセット効果を最終的に有するフィードバックループへの入力が形成される。

【0027】

図4は、本発明の一実施例にしたがって、双極静電チャック、例えば図4のチャック414の板に不均衡な電圧を供給するための自己バイアス静電チャック電源500を示す。図4の構成では、自己バイアス静電チャック電源500には、可変電圧電源510が含まれている。可変電圧電源510は、制御信号516(例えば0Vから5Vの直流信号)を入力として受信し、正または負の接地基準ノード407を出力端子502にて出力する。本実施例では、可変電圧電源510は、カリフォルニア州エル・ケイジョン(El Cajon)市所在のアメリカン・ハイ・ボルテージ社(American High Voltage, Inc.)のTC5電圧電源を表しているが、他の従来型電源(可変の有無を問わず)も使用され得る。

【0028】

可変電圧電源510の出力端子502は、接地基準ノード407により直流電源の陽極406と直流電源の陰極408とに接続されている。直流電源の陰極406は、自己バイアス静電チャック電源500の第1脚部412により静電チャック414の埋込板418に接続されている。この実施例では埋込板418と直流電源の陰極406とに、抵抗器532が直列接続されている。抵抗器532は絶縁増幅器508の入力ノードに並列接続され、抵抗器532における電圧降下V1によって絶縁増幅器508の入力が決まることが望ましい。

【0029】

図4の実施例では、直流電源の陽極408は、自己バイアス静電チャック電源500の第2脚部410により、静電チャック414の埋込板420に接続される。この実施例では、埋込板420と直流電源408の陽極408とに抵抗器530が直列接続される。抵抗器530は絶縁増幅器504の入力ノードに並列接続され、抵抗器530における電圧降下V2によって絶縁増幅器504の入力が形成されることが望ましい。

【0030】

この例では、絶縁増幅器504と絶縁増幅器508とは、カリフォルニア州サンタクララ市所在のアナログ・デバイシズ(Analog Devices)社製のAD202KY絶縁増幅器を表すが、他の従来型絶縁増幅器(可変の有無を問わず)を使用してもよい。抵抗器530と抵抗器532は、一例では約500kΩ+/−1%の抵抗値を持つとよい。

【0031】

既述の実施例によれば、絶縁増幅器508の出力ノード512と絶縁増幅器504の出力ノード514は各々、差動増幅器506への一対の入力の一つを形成する。差動増幅器506は可変電源510への入力制御信号を形成する出力信号516を有する。このようにして、絶縁増幅器504,508、さらに差動増幅器506を含む制御回路570が形成される。この例では差動増幅器506はカリフォルニア州サンタクララ市所在のアナログ・デバイシズ社製のOP490GP差動増幅器が使用されているが、他の従来型差動増幅器も使用可能である。

【0032】

上述の実施例では、抵抗器530,532は固定式でも可変式でも、抵抗要素の任意の組合せでもよい。可変抵抗器の場合、ユーザは、制御回路570に固有の不均衡の補償、および/または、システム校正および/または操作中の誘導変化(例えば静電チャック414またはチャンバの電気的特性)の調整を行うことができる。

【0033】

上の実施例では、静電チャック414は抵抗材料で形成される。一例を挙げると、106−1018Ω-cmの範囲、より望ましくは108−1014Ω-cmの範囲の抵抗率を持つ材料が望ましく、1010−1011Ω-cmの範囲が好適である。基板416は、抵抗率が1040Ω-cmのn型またはp型の半導体材料の形式をとる。抵抗材料が電位差にさらされると電流が流れることは、当該技術分野では周知である。オームの法則I=V/R(I:電流、V:抵抗Rにおける電位差(すなわち電圧降下))にしたがって、電流は高電位領域から低電位領域に流れる。図5において、抵抗Rは単一の抵抗器または複数の抵抗器群などの個別要素である。別の実施例では、Rは埋込板418と埋込板420間の領域のような分散要素でもよい。一例を挙げると、埋込板418、420が基準ノード407に対してそれぞれ+Vと−Vにバイアスされると、電位差2VRにより漏れ電流ICHUCKが板418から板420に流れる。漏れ電流ICHUCKは板418と420に印加されたバイアスの差に概ね左右される。

【0034】

作業時に半導体ウエハ416で表される加工物は、プラズマチャンバ110にプラズマを導入する前に静電チャック414上に載置される。ウエハ416を静電チャック414に取付け固定するため、直流電源406は基準ノード407に対して+Vボルトまで埋込板418にバイアスをかける。同時に直流電源408は、埋込板420にも基準ノード407に対して−Vボルトまでバイアスをかける。上述のように、バイアスをかけられた埋込板418により、ウエハ416の領域422には強度が等しく極性が逆の電界が誘導される。同様にバイアスをかけられた埋込板420により、ウエハ416の領域424には強度が等しく極性が逆の電界が誘導される。説明した実施例では、プラズマの不在下で、実効電荷が概ね等しい領域422と424が存在することにより、ウエハ416を静電チャック414にクランプする平衡状態の静電力が得られる。

【0035】

図5も、クランプされた基板と静電チャック間に存在する漏れ電流を示す。図示のように、漏れ電流I1WAFERは埋込板418からウエハ416の領域422に流れ、戻り電流I2WAFERはウエハ416の領域424から埋込板420に流れる。

【0036】

当業者には周知のように、電流I1, I2, ICHUCK, I1WAFER, I2WAFERはキルヒホッフの法則により以下のように関連付けられる。

I1=ICHUCK+I1WAFER

I2=ICHUCK+I2WAFER

【0037】

この実施例では、板418は静電チャック電源500の第1脚部412に接続されているので、第1電流I1(上述のようにICHUCKとI1WAFERの合計に等しい)が抵抗器532を流れる。同様に、板420は電源500の第2脚部410に接続されているので、第2電流I2(上述のようにICHUCKとI2WAFERの合計に等しい)が抵抗器530を流れる。

【0038】

プラズマの不在下、ウエハ416には実効バイアスは誘導されない。したがってI1WAFERはI2WAFERに等しい(ウエハ416へ流入する電流は、ウエハ416から出る電流と等しい)。上述のようにI1はI2と等しいので、結果的に抵抗器532においてI1により発生される電圧V1と、抵抗器530においてI2により発生される電圧V2とは概ね等しくなる。電圧V1とV2によってそれぞれ絶縁増幅器508と504の入力が決まるので、絶縁増幅器508、504の出力512、514は概ね等しくなる。上述のように、差動増幅器506は電圧V1とV2の差(ゆえにI1とI2の差)に基づき作動し、可変電源510の入力制御信号を画定する出力/入力信号516を生成する。電圧V1とV2(同様にI1とI2)が概ね等しい場合、出力/入力信号516は概ね0Vとなる。出力/入力信号516が概ね0Vであると、可変電源510は基準ノード407をオフセットするためのバイアス電圧を生成しない。このようにプラズマが不在の状況では、制御回路570は初期休止状態となっている。

【0039】

別の実施例では、プラズマが存在しないときであっても、漏れ電流I1とI2の初期の差をもたらす回路に固有の不均衡により、異なる初期均衡状態が生じる。この実施例では電源510により発生されたオフセット電圧は基準ノード407にバイアスをかけ、漏れ電流I1とI2に見られる初期の差を除去する。

【0040】

ウエハ416が静電チャック414にクランプされるとともに制御回路570が平衡である(すなわちI1がI2と概ね等しい)初期セットアップに続き、負帯電プラズマ180がプラズマチャンバ110に導入される。別の実施例では正帯電プラズマが導入される。図6は、負帯電プラズマ180の存在下、ウエハ416と静電チャック414に誘導される様々な漏れ電流を表している。上述の実施例ではプラズマ180は、陰極が接地され(すなわちチャンバの壁111に接続され)、陽極がウエハ416に接続された、固定バイアス電位源182(すなわちバッテリ)として表される。当業者にとって周知のように、プラズマ180により、基板416から接地までの電流IPLASMAの電流経路が形成される。

【0041】

先に説明したように、プラズマ誘導バイアスVBIASは、ウエハ416をチャック414に保持するための静電クランプ力に関して不均衡を生み出す。このクランプ力の不均衡は、埋込板418とウエハ416の領域422との電位差を増大させるとともに、埋込板420とウエハ416の領域424との電位差を減少させるプラズマ誘導バイアスVBIASによるものである。

【0042】

漏れ電流I1WAFERとI2WAFERも、埋込板とウエハ416の関連領域との電位差の変化に応じて変化する。上述の実施例では、負帯電プラズマ180は、埋込板418とウエハ416の領域422との電位差の増加により、ウエハ416への電流I1WAFERを増加させる。同時に、ウエハ416から流出する電流I2WAFERは、埋込板420とウエハ416の領域424との間の電位差の減少に伴い減少する。I1WAFERとI2WAFERの正味の差がIPLASMAとなる。この例ではIPLASMAがプラズマ180に流入する。他の実施例では正帯電プラズマにより正反対の結果が得られる。(注:上記実施例において、約2VRでは、埋込板418と420の電位差は不変なので、漏れ電流ICHUCKは基本的に不変となる。)

【0043】

一例を挙げると、図6のように、プラズマ180がチャンバ110に導入されると、ウエハ416に対してプラズマ誘導バイアス−VBIAS(正帯電プラズマの場合、プラズマ誘導バイアスは+VBIASとなる。)がかかる。プラズマ誘導バイアス−VBIASは、埋込板418とウエハ416の領域422との電位差を+VR−(−VBIAS)またはVR+VBIASまで上昇させる(埋込板418は基準ノード407に対して固定電位+VRのままである)。ウエハ416の領域422と埋込板418との電位差が増加すると、ウエハ416に流入する漏れ電流I1WAFERも同時に増加する。I1=I1WAFER+ICHUCK(キルヒホッフの法則)は変化しないので、プラズマ誘導バイアスVBIASによりI1WAFERが増加すると、比例した量だけ第1脚部の電流I1が増加する。

【0044】

同様にして、埋込板420は基準ノードに対して固定電位−VRに維持されるので、プラズマ誘導バイアス−VBIASにより、埋込板420とウエハ416の領域424との電位差が−VR−(−VBIAS)または−VR+VBIASまで減少する。このように電位差が減少すると、ウエハ416から流出する漏れ電流I2WAFERが減少することになる。I2=I2WAFER+ICHUCK(キルヒホッフの法則)でICHUCKは変化しないので、プラズマ誘導バイアス−VBIASによりI2WAFERが減少すると第2脚部の電流I2が、その比例分だけ減少する。

【0045】

上述したように、ICHUCKは基本的に不変状態が維持されており、I1とI2の間の差ΔIは、ウエハ416にプラズマ180の存在下で誘導される、オフセット電位の尺度となる。差ΔIは制御回路570により構成されるフィードバックループの入力を画定する。制御回路570により画定されるフィードバックループは、ΔIを概ねゼロまで減少させるように設計されている(すなわちI1とI2は概ね等しい)。この実施例では、制御回路570は埋込板418と410に対して基準ノード407をオフセットすることによりΔIを減少させる。このようにして埋込板418,420とウエハ416の関連領域422,424との間の電位差は、漏れ電流I1とI2の間で観察される差に関連している。

【0046】

一例を挙げると、オームの法則から、I1は抵抗器532における電圧降下V1を引き起こし、I2は抵抗器530における電圧降下V2を引き起こす。V1とV2は、差動増幅器506への入力を画定する出力512と514をそれぞれ有する絶縁増幅器508と504への入力を画定する。上記の実施例によれば、差動増幅器506はV1とV2の差(上記のオームの法則によればI1とI2に直接関係する)に比例する出力/制御信号516を発する。出力/制御信号516は基準ノード407により発生され基準ノードに印加される出力バイアス電圧を決定する。

【0047】

基準ノード407が何らかの変化を示すと、ノードに関連している埋込板418と420のバイアスが直接変化する。一例を挙げると、直接電源406が埋込板418に+VRのバイアスを印加すると、基準ノード407は正バイアス+Vrefとなり、次に板418の電位は+VR−(+Vref )となる。同様にして直流電源408が埋込板420に−VRのバイアスを印加すると、基準ノード407は+Vrefの正バイアスとなり、次に板420の電位は−VR−Vrefとなる。

【0048】

上記からも明らかなように、埋込板418,420とウエハ416の関連領域422,424との電位差は、静電チャック414内の影響漏れ電流I1WAFERとI2WAFERに影響を及ぼすことになる。I1WAFERまたはI2WAFERが何らかの変化を示すと、第1脚部の漏れ電流I1と第2脚部の漏れ電流I2に影響を及ぼし、フィードバックループを完成させる。

【0049】

上述した本発明の実施例は、信頼性がなく汚れる可能性のあるプローブピンを使用せずに、双極静電チャックへの不平衡電圧を補償するという目標を達成する。本発明の別の好適な局面によれば、基板からプラズマへに流入する電流を減少または除去して、アークの危険を減らし、放電時間を短くして処理能力を高め、基板を静電チャックに効果的にクランプするのに必要な電圧を下げる。

【0050】

本実施例のさらなる長所は、信頼性がなく汚染の可能性のあるプローブピンを使用することなく、双極静電チャックへの不平衡な電圧を補償できる能力を含むことにある。本実施例の別の長所によれば、基板からプラズマへ流れる電流を減らすまたは除去することが可能である。基板からプラズマへの電流を減らすことにより、または除去することにより、アークの危険を減らし、処理能力を高め(放電時間が短くなるため)、基板を基板に効果的にクランプするのに必要な電圧を下げることになる。

【0051】

また別の長所として、電源を他のシステムに合わせて容易に更新でき、工程の支障となり、設置のためにはチャンバの物理的構成に変更を加えねばならないような外部測定装置(プローブピンのような)が不要であることが挙げられる。いくつかの好適な実施例について本発明を説明したが、本発明の範囲に包含される代替物、置換物、均等物が存在する。例えば、実施例ではプラズマエッチング反応器について説明したが、本発明の自己バイアス双極ESCチャック電源は、蒸着に用いられるものなど、他のプラズマ反応器でも使用できる。本発明の方法および装置を実行する他の方法も存在することに注意すべきである。したがって、以下に添付された特許請求の範囲は、本発明の真の趣旨と本発明の範囲とに含まれる代替物、置換物、均等物をすべて含むものとして解釈されるべきである。

【図面の簡単な説明】

【0052】

【図1】説明を容易にするため一般的なプラズマ基板処理システムを示す。

【図2A】誘導電荷とその結果生じるクランプ力との分布を示す、双極静電チャックと基板との断面図である。

【図2B】誘導電荷とその結果生じる不均衡なクランプ力の分布に対する負帯電プラズマの影響を示す、図2Aに示した双極静電チャックと基板の断面図である。

【図3】ウエハのプラズマ誘導バイアスを補償するためのピックアップピンの使用に基づく従来技術の回路を示す。

【図4】本発明の一実施例に従う双極静電チャックの板にプラズマ誘導バイアス補償電圧を供給するための自己バイアス静電チャック電源を示す。

【図5】本発明の一実施例に従うプラズマが不存在の場合における静電チャックにクランプされた基板における漏れ電流を示す。

【図6】本発明の一実施例に従うプラズマ導入後に自己バイアス電源に接続された静電チャックに載置された基板に存在する漏れ電流を示す。

Claims (17)

- 静電チャック電源の基準ノードの基準電圧を制御するよう構成された制御回路であって、該静電チャック電源が第1埋込導体と第2埋込導体とを有する双極静電チャックに基板をクランプするように構成され、該静電チャック電源が前記第1埋込導体に接続するように構成された第1出力を有し、該第1出力が前記基準電圧を基準とする第1出力電圧を有し、前記第1出力電圧は、前記基準電圧に定電圧を足した値であり、該静電チャック電源が、該第2埋込導体に接続されるよう構成された第2出力をさらに有し、該第2出力が、前記基準電圧を基準とする第2出力電圧を有し、前記第2出力電圧は、前記基準電圧から前記定電圧を引いた値であり、前記第1出力電圧と前記第2出力電圧との差は、前記定電圧の2倍に等しく、

前記第1出力と前記第1埋込導体との間に直列接続された第1抵抗器と、

前記第1抵抗器における第1電圧降下を検出するため該第1抵抗器に接続された第1増幅器と、

前記第2出力と前記第2埋込導体との間に直列接続された第2抵抗器と、

前記第2抵抗器における第2電圧降下を検出するため該第2抵抗器に接続された第2増幅器と、

前記第1増幅器と前記第2増幅器との出力に接続され、制御信号を出力するための出力を有する差動増幅器であって、前記制御信号は、前記第1電圧降下と前記第2電圧降下との差に概ね比例すると共に、前記第1抵抗器における第1電流と前記第2抵抗器における第2電流との差に概ね比例する、差動増幅器と、

前記基準ノードに接続された出力と前記差動増幅器の出力に接続された入力とを有し、前記制御信号に応じて、出力側において、前記第1電流と前記第2電流との前記差を概ね0に低減する前記基準電圧の値を生成する可変電圧電源とを備える制御回路。 - 請求項1に記載の制御回路において、前記チャックは、106Ω-cmから1018Ω-cmの範囲の抵抗率を有する抵抗材料によって形成されている制御回路。

- その内部に配置されている第1埋込導体と第2埋込導体とを有する双極静電チャックに接続されるよう構成された電源であって、

可変基準電圧を有する基準ノードと、

前記第1埋込導体に接続されるよう構成され、前記基準ノードを基準とする第1出力電圧を有する第1出力であって、前記第1出力電圧は、前記基準電圧に定電圧を足した値である第1出力と、

前記第2埋込導体に接続されるよう構成され、前記基準ノードを基準とする第2出力電圧を有する第2出力であって、前記第2出力電圧は、前記基準電圧から前記定電圧を引いた値であり、前記第1出力電圧と前記第2出力電圧との差は、前記定電圧の2倍に等しい第2出力と、

前記第1出力の第1電流と前記第2出力の第2電流との電流差を検出するため該第1出力と該第2出力とに接続された制御回路であって、該電流差に概ね比例する制御電圧を、該制御回路の制御出力に出力する制御回路と、

前記制御電圧を受けるよう構成された供給回路であって、前記制御回路に応じて、前記基準電圧を前記基準ノードに出力して、前記電流差を概ね0に駆動する供給回路とを備える電源。 - 請求項3に記載の電源において、前記制御回路はさらに、

前記第1出力と前記第1埋込導体との間の直列の第1抵抗器と、

前記第1抵抗器における第1電圧降下を検出するため該第1抵抗器に接続された第1増幅器と、

前記第2出力と前記第2埋込導体との間の直列の第2抵抗器と、

前記第2抵抗器における第2電圧降下を検出するため該第2抵抗器に接続された第2増幅器とを含む電源。 - 請求項4に記載の電源において、前記制御回路はさらに、前記制御電圧を発生させるため前記第1増幅器と前記第2増幅器の出力に接続された差動増幅器を含む電源。

- 請求項4に記載の電源であって、前記チャックは、106Ω-cmから1018Ω-cmの範囲の抵抗率を有する抵抗材料によって形成されている電源。

- プラズマ処理センターにおいて基板を第1埋込導体と第2埋込導体とを有するチャックにクランプする方法であって、

基準ノードと第1出力と第2出力とを有する第1電源を提供し、前記第1出力および第2出力は制御回路に接続され、前記第1出力は前記基準ノードを基準とする第1出力電圧を有し、前記第2出力は前記基準ノードを基準とする第2出力電圧を有し、

前記第1埋込導体を前記第1出力に接続し、

前記第2埋込導体を前記第2出力に接続し、

前記第1出力の第1電流と前記第2出力の第2電流との電流差を前記制御回路によって検出し、

前記制御回路から、前記電流差に概ね比例すると共に、第2電源から出力される電位レベルを制御する制御電圧を前記第2の電源に対して出力し、

前記第2電源は、ノードにおいて前記制御電圧を受け取り、受け取った前記制御電圧に応じて、前記基準ノードに前記電位レベルを出力することを備える方法。 - 請求項7に記載の方法において、前記制御回路は、前記第1出力と前記第1埋込導体との間の直列の第1抵抗器と前記第2出力と前記第2埋込導体との間の直列の第2抵抗器とを含み、該制御回路はさらに前記第1抵抗器における電圧降下を検出するための第1増幅器と、前記第2抵抗器における電圧降下を検出するための第2増幅器とを含む方法。

- 請求項8に記載の方法において、前記第1抵抗器と前記第2抵抗器の値が概ね等しい方法。

- 請求項8に記載の方法において、前記第1抵抗器が500kΩ+/−1%の値を有し、前記第2抵抗器が500kΩ+/−1%の値を有する方法。

- 請求項8に記載の方法において、前記制御回路はさらに、前記制御電圧を発生させるため前記第1増幅器の出力と前記第2増幅器の出力とに接続された差動増幅器を含む方法。

- 請求項10に記載の方法において、前記チャックは1010Ω-cmから1011Ω-cmの範囲の抵抗率を有する材料にて形成される方法。

- 静電チャック電源の基準ノードの基準電圧を制御するように構成された制御回路であって、該静電チャック電源は第1埋込導体と第2埋込導体を有する双極静電チャックに基板をクランプするように構成され、該静電チャック電源は該第1埋込導体に接続されるよう構成された第1出力を有し、該第1出力は該基準電圧を基準とする第1出力電圧を有し、該静電チャック電源はさらに該第2埋込導体に接続されるよう構成された第2出力を有し、該第2出力は該基準電圧を基準とする第2出力電圧を有し、

前記第1出力と前記第1埋込導体との間に直列接続された第1抵抗手段と、

前記第1抵抗手段における第1電圧降下を検出するため該第1抵抗手段に接続された第1検出手段と、

前記第2出力と前記第2埋込導体との間の直列の第2抵抗手段と、

前記第2抵抗手段における電圧降下を検出するため該第2抵抗手段に接続された第2検出手段と、

制御電圧を発生させるために前記第1検出手段と前記第2検出手段との出力に接続された差動増幅手段と、

前記差動増幅手段の出力に接続され、前記制御電圧に応じて、前記基準ノードに前記基準電圧を出力するよう構成された回路手段とを備える制御回路。 - 請求項3に記載の電源において、前記供給回路は可変電圧電源を含む電源。

- 請求項13に記載の制御回路において、前記第1抵抗手段は第1抵抗器であり、前記第2抵抗手段は第2抵抗器である制御回路。

- 請求項13に記載の制御回路において、前記第1検出手段は第1増幅器であり、前記第2検出手段は第2増幅器である制御回路。

- 請求項13に記載の制御回路において、前記回路手段は可変電圧電源である制御回路。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/883,068 | 1997-06-27 | ||

| US08/883,068 US5933314A (en) | 1997-06-27 | 1997-06-27 | Method and an apparatus for offsetting plasma bias voltage in bi-polar electro-static chucks |

| PCT/US1998/013159 WO1999000889A1 (en) | 1997-06-27 | 1998-06-24 | A method and an apparatus for offsetting plasma bias voltage in bipolar electrostatic chucks |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002507326A JP2002507326A (ja) | 2002-03-05 |

| JP2002507326A5 JP2002507326A5 (ja) | 2005-12-22 |

| JP4299370B2 true JP4299370B2 (ja) | 2009-07-22 |

Family

ID=25381907

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP50568999A Expired - Lifetime JP4299370B2 (ja) | 1997-06-27 | 1998-06-24 | 双極静電チャックにおけるプラズマバイアス電圧のオフセット方法および装置 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US5933314A (ja) |

| EP (1) | EP0992106B1 (ja) |

| JP (1) | JP4299370B2 (ja) |

| KR (1) | KR100543319B1 (ja) |

| AT (1) | ATE301880T1 (ja) |

| DE (1) | DE69831152T2 (ja) |

| TW (1) | TW383417B (ja) |

| WO (1) | WO1999000889A1 (ja) |

Families Citing this family (57)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5662770A (en) | 1993-04-16 | 1997-09-02 | Micron Technology, Inc. | Method and apparatus for improving etch uniformity in remote source plasma reactors with powered wafer chucks |

| US6177023B1 (en) * | 1997-07-11 | 2001-01-23 | Applied Komatsu Technology, Inc. | Method and apparatus for electrostatically maintaining substrate flatness |

| US6198616B1 (en) * | 1998-04-03 | 2001-03-06 | Applied Materials, Inc. | Method and apparatus for supplying a chucking voltage to an electrostatic chuck within a semiconductor wafer processing system |

| US6346428B1 (en) * | 1998-08-17 | 2002-02-12 | Tegal Corporation | Method and apparatus for minimizing semiconductor wafer arcing during semiconductor wafer processing |

| US6965506B2 (en) * | 1998-09-30 | 2005-11-15 | Lam Research Corporation | System and method for dechucking a workpiece from an electrostatic chuck |

| US6790375B1 (en) * | 1998-09-30 | 2004-09-14 | Lam Research Corporation | Dechucking method and apparatus for workpieces in vacuum processors |

| US6228278B1 (en) * | 1998-09-30 | 2001-05-08 | Lam Research Corporation | Methods and apparatus for determining an etch endpoint in a plasma processing system |

| US6125025A (en) * | 1998-09-30 | 2000-09-26 | Lam Research Corporation | Electrostatic dechucking method and apparatus for dielectric workpieces in vacuum processors |

| US6361645B1 (en) | 1998-10-08 | 2002-03-26 | Lam Research Corporation | Method and device for compensating wafer bias in a plasma processing chamber |

| US6188564B1 (en) * | 1999-03-31 | 2001-02-13 | Lam Research Corporation | Method and apparatus for compensating non-uniform wafer processing in plasma processing chamber |

| US6898064B1 (en) * | 2001-08-29 | 2005-05-24 | Lsi Logic Corporation | System and method for optimizing the electrostatic removal of a workpiece from a chuck |

| US6898065B2 (en) * | 2002-07-26 | 2005-05-24 | Brad Mays | Method and apparatus for operating an electrostatic chuck in a semiconductor substrate processing system |

| KR100545169B1 (ko) * | 2003-09-03 | 2006-01-24 | 동부아남반도체 주식회사 | 반도체 제조 설비의 정전척 및 이를 이용한 웨이퍼 척킹방법 |

| US7264676B2 (en) * | 2003-09-11 | 2007-09-04 | United Microelectronics Corp. | Plasma apparatus and method capable of adaptive impedance matching |

| US6972524B1 (en) | 2004-03-24 | 2005-12-06 | Lam Research Corporation | Plasma processing system control |

| US7041989B1 (en) * | 2004-10-22 | 2006-05-09 | Asml Netherlands B.V. | Lithographic apparatus and device manufacturing method |

| JP2007048986A (ja) * | 2005-08-10 | 2007-02-22 | Hitachi High-Technologies Corp | プラズマ処理装置およびプラズマ処理方法 |

| JP5085567B2 (ja) * | 2006-03-08 | 2012-11-28 | フラウンホッファー−ゲゼルシャフト ツァ フェルダールング デァ アンゲヴァンテン フォアシュンク エー.ファオ | 非同期機の対称インピーダンス及び非対称インピーダンスをシミュレートする装置 |

| JP4802018B2 (ja) * | 2006-03-09 | 2011-10-26 | 筑波精工株式会社 | 静電保持装置及びそれを用いた真空環境装置並びにアライメント装置又は貼り合わせ装置 |

| KR101213103B1 (ko) * | 2006-06-30 | 2013-01-09 | 엘지디스플레이 주식회사 | 합착 장치 및 이를 이용한 전계발광소자의 제조방법 |

| US7768766B2 (en) * | 2007-06-01 | 2010-08-03 | Lam Research Corporation | Plasma processing system ESC high voltage control |

| US8043470B2 (en) * | 2007-11-21 | 2011-10-25 | Lam Research Corporation | Electrode/probe assemblies and plasma processing chambers incorporating the same |

| US7558045B1 (en) * | 2008-03-20 | 2009-07-07 | Novellus Systems, Inc. | Electrostatic chuck assembly with capacitive sense feature, and related operating method |

| FR2930561B1 (fr) * | 2008-04-28 | 2011-01-14 | Altatech Semiconductor | Dispositif et procede de traitement chimique en phase vapeur. |

| US8901935B2 (en) * | 2009-11-19 | 2014-12-02 | Lam Research Corporation | Methods and apparatus for detecting the confinement state of plasma in a plasma processing system |

| JP2011187881A (ja) * | 2010-03-11 | 2011-09-22 | Hitachi High-Technologies Corp | プラズマ処理装置および方法 |

| US9076831B2 (en) * | 2011-11-04 | 2015-07-07 | Lam Research Corporation | Substrate clamping system and method for operating the same |

| US9017513B2 (en) | 2012-11-07 | 2015-04-28 | Lam Research Corporation | Plasma monitoring probe assembly and processing chamber incorporating the same |

| US9101038B2 (en) | 2013-12-20 | 2015-08-04 | Lam Research Corporation | Electrostatic chuck including declamping electrode and method of declamping |

| CN106796909A (zh) | 2014-06-17 | 2017-05-31 | 瑞士艾发科技 | 具有射频分路的静电卡盘 |

| US10002782B2 (en) | 2014-10-17 | 2018-06-19 | Lam Research Corporation | ESC assembly including an electrically conductive gasket for uniform RF power delivery therethrough |

| JP6407694B2 (ja) * | 2014-12-16 | 2018-10-17 | 株式会社日立ハイテクノロジーズ | プラズマ処理装置 |

| CN106298615B (zh) * | 2015-05-27 | 2019-03-12 | 北京北方华创微电子装备有限公司 | 静电卡盘、反应腔室及半导体加工设备 |

| JP6708358B2 (ja) * | 2016-08-03 | 2020-06-10 | 株式会社日立ハイテク | プラズマ処理装置及び試料の離脱方法 |

| US10636630B2 (en) * | 2017-07-27 | 2020-04-28 | Applied Materials, Inc. | Processing chamber and method with thermal control |

| US10555412B2 (en) | 2018-05-10 | 2020-02-04 | Applied Materials, Inc. | Method of controlling ion energy distribution using a pulse generator with a current-return output stage |

| US20200048770A1 (en) * | 2018-08-07 | 2020-02-13 | Lam Research Corporation | Chemical vapor deposition tool for preventing or suppressing arcing |

| US11476145B2 (en) * | 2018-11-20 | 2022-10-18 | Applied Materials, Inc. | Automatic ESC bias compensation when using pulsed DC bias |

| CN113169026B (zh) | 2019-01-22 | 2024-04-26 | 应用材料公司 | 用于控制脉冲电压波形的反馈回路 |

| US11508554B2 (en) | 2019-01-24 | 2022-11-22 | Applied Materials, Inc. | High voltage filter assembly |

| US11462388B2 (en) | 2020-07-31 | 2022-10-04 | Applied Materials, Inc. | Plasma processing assembly using pulsed-voltage and radio-frequency power |

| US11776835B2 (en) | 2020-09-29 | 2023-10-03 | Applied Materials, Inc. | Power supply signal conditioning for an electrostatic chuck |

| US11594440B2 (en) * | 2020-10-21 | 2023-02-28 | Applied Materials, Inc. | Real time bias detection and correction for electrostatic chuck |

| US11901157B2 (en) | 2020-11-16 | 2024-02-13 | Applied Materials, Inc. | Apparatus and methods for controlling ion energy distribution |

| US11798790B2 (en) | 2020-11-16 | 2023-10-24 | Applied Materials, Inc. | Apparatus and methods for controlling ion energy distribution |

| JP7350995B2 (ja) | 2021-02-25 | 2023-09-26 | 株式会社日立ハイテク | プラズマ処理装置 |

| US11495470B1 (en) | 2021-04-16 | 2022-11-08 | Applied Materials, Inc. | Method of enhancing etching selectivity using a pulsed plasma |

| US11948780B2 (en) | 2021-05-12 | 2024-04-02 | Applied Materials, Inc. | Automatic electrostatic chuck bias compensation during plasma processing |

| US11791138B2 (en) | 2021-05-12 | 2023-10-17 | Applied Materials, Inc. | Automatic electrostatic chuck bias compensation during plasma processing |

| US11967483B2 (en) | 2021-06-02 | 2024-04-23 | Applied Materials, Inc. | Plasma excitation with ion energy control |

| US20220399185A1 (en) | 2021-06-09 | 2022-12-15 | Applied Materials, Inc. | Plasma chamber and chamber component cleaning methods |

| US11810760B2 (en) | 2021-06-16 | 2023-11-07 | Applied Materials, Inc. | Apparatus and method of ion current compensation |

| US11569066B2 (en) | 2021-06-23 | 2023-01-31 | Applied Materials, Inc. | Pulsed voltage source for plasma processing applications |

| US11776788B2 (en) | 2021-06-28 | 2023-10-03 | Applied Materials, Inc. | Pulsed voltage boost for substrate processing |

| US11476090B1 (en) | 2021-08-24 | 2022-10-18 | Applied Materials, Inc. | Voltage pulse time-domain multiplexing |

| US11694876B2 (en) | 2021-12-08 | 2023-07-04 | Applied Materials, Inc. | Apparatus and method for delivering a plurality of waveform signals during plasma processing |

| US11972924B2 (en) | 2022-06-08 | 2024-04-30 | Applied Materials, Inc. | Pulsed voltage source for plasma processing applications |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2678381B2 (ja) * | 1987-05-06 | 1997-11-17 | ユニサーチ・リミテッド | 交流電界励振を利用した静電チャック |

| US5444597A (en) * | 1993-01-15 | 1995-08-22 | Blake; Julian G. | Wafer release method and apparatus |

| US5557215A (en) * | 1993-05-12 | 1996-09-17 | Tokyo Electron Limited | Self-bias measuring method, apparatus thereof and electrostatic chucking apparatus |

| TW293231B (ja) * | 1994-04-27 | 1996-12-11 | Aneruba Kk | |

| GB2293689A (en) * | 1994-09-30 | 1996-04-03 | Nec Corp | Electrostatic chuck |

| US5708250A (en) * | 1996-03-29 | 1998-01-13 | Lam Resarch Corporation | Voltage controller for electrostatic chuck of vacuum plasma processors |

| US5737175A (en) * | 1996-06-19 | 1998-04-07 | Lam Research Corporation | Bias-tracking D.C. power circuit for an electrostatic chuck |

-

1997

- 1997-06-27 US US08/883,068 patent/US5933314A/en not_active Expired - Lifetime

-

1998

- 1998-06-24 JP JP50568999A patent/JP4299370B2/ja not_active Expired - Lifetime

- 1998-06-24 KR KR1019997012241A patent/KR100543319B1/ko not_active IP Right Cessation

- 1998-06-24 WO PCT/US1998/013159 patent/WO1999000889A1/en active IP Right Grant

- 1998-06-24 DE DE69831152T patent/DE69831152T2/de not_active Expired - Lifetime

- 1998-06-24 EP EP98932840A patent/EP0992106B1/en not_active Expired - Lifetime

- 1998-06-24 AT AT98932840T patent/ATE301880T1/de not_active IP Right Cessation

- 1998-09-01 TW TW087110395A patent/TW383417B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| KR100543319B1 (ko) | 2006-01-20 |

| EP0992106B1 (en) | 2005-08-10 |

| EP0992106A1 (en) | 2000-04-12 |

| DE69831152T2 (de) | 2006-04-20 |

| US5933314A (en) | 1999-08-03 |

| DE69831152D1 (de) | 2005-09-15 |

| WO1999000889A1 (en) | 1999-01-07 |

| KR20010014170A (ko) | 2001-02-26 |

| TW383417B (en) | 2000-03-01 |

| JP2002507326A (ja) | 2002-03-05 |

| ATE301880T1 (de) | 2005-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4299370B2 (ja) | 双極静電チャックにおけるプラズマバイアス電圧のオフセット方法および装置 | |

| JP4299368B2 (ja) | 動的フィードバック静電ウエハ・チャック | |

| KR100586430B1 (ko) | 플라스마 처리실에서 웨이퍼의 바이어스를 보상하는방법과 장치 | |

| US6198616B1 (en) | Method and apparatus for supplying a chucking voltage to an electrostatic chuck within a semiconductor wafer processing system | |

| KR100779444B1 (ko) | 플라즈마 리액터에서의 무선주파수 전력 변동율에 대한 전압제어 센서 및 제어 인터페이스 | |

| US5708250A (en) | Voltage controller for electrostatic chuck of vacuum plasma processors | |

| KR100281935B1 (ko) | 자기 바이어스 측정방법 및 그 장치와 정전 흡착장치 | |

| EP1376682B1 (en) | Apparatuses for clamping and declamping a semiconductor wafer in a wafer processing system | |

| US6304424B1 (en) | Method and apparatus for minimizing plasma destabilization within a semiconductor wafer processing system | |

| JP4169792B2 (ja) | 不平衡二極静電チャック電源供給装置およびその方法 | |

| US6625003B2 (en) | Method and apparatus for balancing an electrostatic force produced by an electrostatic chuck | |

| US5835333A (en) | Negative offset bipolar electrostatic chucks | |

| JP3306677B2 (ja) | 自己バイアス測定方法及び装置並びに静電吸着装置 | |

| KR100227821B1 (ko) | 웨이퍼 고정용 정전척의 전원공급장치 | |

| KR100491190B1 (ko) | 웨이퍼처리시스템에서반도체웨이퍼를클램핑하고디클램핑하는방법과장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050624 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050624 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080408 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080704 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080819 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20081118 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20090105 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090217 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090407 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090417 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120424 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120424 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130424 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130424 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140424 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |