JP4230682B2 - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP4230682B2 JP4230682B2 JP2001246050A JP2001246050A JP4230682B2 JP 4230682 B2 JP4230682 B2 JP 4230682B2 JP 2001246050 A JP2001246050 A JP 2001246050A JP 2001246050 A JP2001246050 A JP 2001246050A JP 4230682 B2 JP4230682 B2 JP 4230682B2

- Authority

- JP

- Japan

- Prior art keywords

- liquid crystal

- data

- signal

- pixel

- input

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/003—Details of a display terminal, the details relating to the control arrangement of the display terminal and to the interfaces thereto

- G09G5/006—Details of the interface to the display terminal

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/3406—Control of illumination source

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3614—Control of polarity reversal in general

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2360/00—Aspects of the architecture of display systems

- G09G2360/16—Calculation or use of calculated indices related to luminance levels in display data

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3696—Generation of voltages supplied to electrode drivers

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

Description

【発明の属する技術分野】

本発明は液晶表示装置に係り、たとえばアクティブ・マトリクス型の液晶表示装置に関する。

【0002】

【従来の技術】

アクティブ・マトリクス型の液晶表示装置は、液晶を介して対向配置される一対の基板のうち一方の基板の液晶側の面に、そのx方向に延在しy方向に並設されるゲート信号とy方向に延在しx方向に並設されるドレイン信号線が形成され、これら各信号線によって囲まれた領域を画素領域としている。

【0003】

これら各画素領域には、片側のゲート信号線からの走査信号によって作動するスイッチング素子と、このスイッチング素子を介して片側のドレイン信号線からの映像信号が供給される画素電極とが備えられている。

【0004】

この画素電極は前記一対の基板のうちいずれかの基板の液晶側の面に形成された対向電極との間に電界を発生せしめ、この電界によって液晶の光透過率を制御させるようにしている。

【0005】

また、各ゲート信号線は、垂直走査駆動回路からの走査信号によってその1つが選択され、そのタイミングに合わせて、各ドレイン信号線には映像信号駆動回路から映像信号が供給されるようになっている。

【0006】

そして、このような構成において、液晶に直流成分の電圧が長時間印加されてその分極による液晶劣化を防止するために、たとえば隣接する画素領域のそれぞれの液晶の印加電圧極性を反転(交流化)させ、かつフレーム毎にも液晶印加電圧極性を反転させるいわゆるドット反転駆動方式が知られている。

【0007】

また、液晶表示装置における表示の態様としてドットマトリクス表示とキャラクタ表示とがあるが、前記映像信号駆動回路に入力されるデータはドットマトリクスデータからなっていた。

【0008】

さらに、いわゆる透過型と称される液晶表示装置は、その液晶表示パネルの背面にバックライトを備えるものであるが、このバックライトの輝度は一定にして行っているのが通常である。

【0009】

【発明が解決しようとする課題】

しかし、このような液晶表示装置において、前記ドット反転駆動方式が用いられているものにあって、液晶駆動の交流化を相殺する表示パターンが必ず存在し、この場合においてフリッカが発生してしまうということが指摘されている。

【0010】

また、前記映像信号駆動回路に入力されるドットマトリクスデータは、その転送のための消費電力が大きくなってしまうことが指摘されている。

【0011】

さらに、近年、表示画像として静画像はもちろんのこと動画像も多く映像されるようになり、その動画像の場合に輝度が若干暗くなり該動画像を明確に認識できなくなることが指摘されている。

【0012】

本発明は、このような事情に基づいてなされたもので、その目的は、フリッカの発生を抑制した液晶表示装置を提供することにある。

【0013】

また、本発明の他の目的は、消費電力を低減させた液晶表示装置を提供することにある。

【0014】

さらに、本発明の他の目的は、動画像を明確に表示できるようにした液晶表示装置を提供することにある。

【0015】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0016】

手段1.

まず、ゲート信号線に沿った画素群をラインとしてマトリクス状に配置された各画素を有し、交流化信号により一フレーム中の各画素の液晶に印加する電圧の極性を変化させる手段が備えられた液晶表示装置であって、

各フレーム毎に、各奇数ラインの画素データの信号レベルの累算値および各偶数ラインの画素データの信号レベルの累算値を得る手段と、これら各累算値を減算する手段と、この各累算値を減算する手段からの減算値が基準値以上の場合に前記交流化信号と異なる他の交流化信号を送出させる手段とを備えることを特徴とするものである。

【0017】

このように構成された液晶表示装置は、電圧印加極性と表示データが偏ることがなくなり、該液晶印加電圧がコモン電圧に対して均一化されるようになる。このため、コモン電極の電流量が増加することがなく消費電力を抑制できる。

【0018】

手段2.

キャラクタ表示を含むドットマトリクスデータを入力し、この入力データからディスプレィイネーブル信号がHighの際にドットマトリクスデータを取り出す手段と、前記入力データから前記ディスプレィイネーブル信号がLowの際にキャラクタデータを生成する手段と、該キャラクタデータを前記ドットマトリクスデータと合成して表示データを出力させる手段とを備えることを特徴とするものです。

【0019】

このように構成された液晶表示装置は、ドットマトリクス表示とともにキャラクタ表示をする場合、該キャラクタ表示のための入力データをキャラクタデータとして取り込み、ドットマトリクスデータと合成する構成となっている。これにより、データ転送の消費電力の低減を図ることができる。

【0020】

手段3.

入力表示データが入力される液晶表示パネルと、この液晶表示パネルの背面に配置されるバックライトとを有し、

前記入力表示データから各画素データの階調を検出する第1手段と、予め定められた階調の各段階において前記第1手段によって検出された画素データの階調の有無を検出する第2手段と、この第2手段によって検出された階調の有の数を加算する第3手段と、前記バックライトの明るさの制御範囲を複数に区分し前記第3手段による前記加算の値の大きさを前記区分に対応させて前記バックライトへの制御信号を出力する第4手段と、を備えることを特徴とする。

【0021】

このように構成された液晶表示装置は、その液晶表示パネルに表示される動画像は、静画像が表示される場合よりも輝度が明るくなって表示されるようになる。

【0022】

これにより、動画像の動きを明確に表示できるようになる。一方、静画像の場合にはその輝度があまり大きくなくても明確に表示できることが確かめられている。

【0023】

また、このように、動画像と静画像との区別を検知し、それに応じた最適な輝度表示を行っているため、消費電力の低減が図れる効果を奏する。

【0024】

【発明の実施の形態】

以下、本発明による液晶表示装置の各実施例を図面を用いて説明をする。

〔実施例1〕

《液晶表示パネルPNLの回路図》

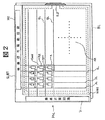

図2は、液晶表示パネルPNLの回路を示す図である。同図は回路図であるが実際の幾何学的配置に対応させて描いている。

【0025】

まず、透明基板SUB1があり、その表面(後述の透明基板SUB2と対向する面)には、そのx方向に延在しy方向に並設されるゲート信号線GLが形成され、また、y方向に延在しx方向に並設されるドレイン信号線DLが形成されている。

【0026】

ゲート信号線GLとドレイン信号線DLで囲まれる領域は画素領域(画素)を構成し、これら各画素がマトリックス状に配置された領域内で液晶表示部ARを構成するようになっている。

【0027】

各画素領域には、片側のゲート信号線GLからの走査信号によって作動されるスイッチング素子(薄膜トランジスタ)TFTと、このスイッチング素子TFTを介して片側のドレイン信号線DLからの映像信号が供給される画素電極PIXとが形成されている。

【0028】

この画素電極PIXは、各透明基板のいずれかの側に設けられた対向電極CT(図示せず)との間に電界を発生せしめ、この電界によって液晶の光透過率を制御するようになっている。

【0029】

各ゲート信号線GLはその一端側において垂直走査駆動回路Vに接続され、この垂直走査駆動回路Vから各ゲート信号線GLに走査信号が供給されるようになっている。

【0030】

また、各ドレイン信号線DLはその一端側において映像信号駆動回路Heに接続され、この映像信号駆動回路Heから各ドレイン信号線DLに映像信号が供給されるようになっている。

【0031】

なお、各ドレイン信号線DLは、たとえばその左端側からカラー表示のR、G、B、が順次繰り返された信号線となっており、これにより各ゲート信号線GLが担当する画素であって互いに隣接する3つの画素がカラー表示における一画素として構成されている。

【0032】

前記透明基板SUB1は液晶を介して他の透明基板SUB2と対向配置され、前記液晶表示部ARを囲んで液晶の封止を兼ねるシール材SLによって、前記透明基板SUB1とSUB2との固着がなされている。

【0033】

また、このように構成された液晶表示パネルPNLはいわゆる透過型のもので、その背面にはバックライトBLが配置されるようになっている。

【0034】

《液晶表示パネルPNLとその周辺回路》

図3は、前記液晶表示パネルPNLとその周辺回路を示す図である。

同図に示す液晶表示装置は、説明を簡単にするため、たとえば256色のカラー表示の場合を示している。

【0035】

まず、マイクロコンピュータシステム等に対応するインターフェース部は、タイミングコンバータTCONによって構成されている。

【0036】

このタイミングコンバータTCONの入力端子には、標準的なカラーCRT(陰極線管)のR、G、Bの入力に対応したカラーデータR0〜R7、G0〜G7、B0〜B7と、水平同期信号HSYNC、垂直同期信号VSYNC、表示タイミング信号YDISP等が入力されるようになっている。

【0037】

また、その出力端子からは、前記入力端子からの各データを変換して液晶表示パネルPNLを駆動するための信号が出力されるようになっている。

【0038】

なお、タイミングコンバータTCONには、フェーズ・ロックド・ループ回路PLLが接続され、このフェーズ・ロックド・ループ回路PLLによって1ドットクロックパルスDOTCLKを入力させるようになっている。

【0039】

液晶表示パネルPNLに搭載されている垂直走査駆動回路Vは、たとえばダイナミック型のシフトレジスタとドライバとから構成され、前記タイミングコンバータTCONの出力端子からはフレーム信号FLM信号と走査タイミングに対応したパルスCL2が入力されるようになっている。

【0040】

これにより、垂直走査駆動回路Vの出力端子にそれぞれ接続されているゲート信号線GLのそれぞれには順次走査信号が出力されるようになっている。

【0041】

また、液晶表示パネルPNLに搭載されている映像信号駆動回路Heには、前記タイミングコンバータTCONの出力端子からクロックパルスCL1と信号バスを介してシリアルに送出される数ビット単位のデータが入力されるようになっている。

【0042】

クロックパルスCL1は、上記シリアルに転送された1ライン分のデータをラッチするために用いられるようになっている。

【0043】

すなわち、クロックパルスCL1は、1ライン分のデータ転送が終了すると発生され、転送されたデータを保持し、それに基づいて1ライン分の駆動電圧が形成され、前記垂直走査駆動回路Vにより選択されたゲート信号線GLと対応した1ライン分の画素にパラレルに書き込まれるようになっている。

【0044】

この場合、前記画素の書き込みと並行して上記クロックパルスCL1によって次のラインに対応したデータのシリアル取り込みが行われるようになっている。

【0045】

一方、電源安定化回路PWがあり、たとえば+5Vと−24Vのような2つの電圧を受け、駆動電圧に必要な+5Vと−20Vのような安定化電圧を発生させるようになっている。

【0046】

電源安定化回路PWは、前記タイミングコンバータTCONからの表示制御信号DISP/ONを受けてその動作が有効にされるようになっている。

【0047】

また、この電源安定化回路PWからの安定化電圧は駆動電圧発生回路CPに供給され、該駆動電圧発生回路CPは、各階調毎に振り分けられたそれぞれの駆動電圧を発生させ、それら各駆動電圧は映像信号駆動回路Heに供給されるようになっている。

【0048】

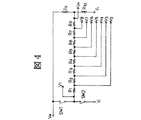

《駆動電圧発生回路》

図4は前記駆動電圧発生回路CPの一実施例を示しており、階調に応じて出力される駆動電圧がゲート信号線GL毎、およびフレーム毎に正/負極性に交互に極性反転するように構成されている。

【0049】

このようにした場合、液晶はいわゆる交流駆動される(この場合、対向電極は一定)ことになり、該液晶に直流成分が印加されることがなく、その寿命を向上させることができる効果を奏する。

【0050】

同図において、高レベル側の電圧VHと低レベル側の電圧VLの間にはスイッチSW1とSW2による直列回路が接続され、これら各スイッチSW1とSW2の接続点からは駆動電圧V1として出力される。

【0051】

また、高レベル側の電圧VHと低レベル側の電圧VLの間には抵抗R9とR10による直列回路が接続され、これら各抵抗R9とR10の接続点からは駆動電圧V M として出力される。

【0052】

スイッチSW1とSW2は、その一方がオン状態の時には他方がオフ状態となり、この切り替えはたとえばゲート信号線GLの切り替えに応じてなされるようになっている。

【0053】

そして、前記各抵抗R9とR10の接続点とスイッチSW1とSW2の接続点の間には抵抗R1ないし抵抗R8の直列回路が接続されており、各抵抗R1ないしR8のそれぞれの間からはそれぞれ駆動電圧V2ないしV8が出力されるようになっている。

【0054】

出力される各駆動電圧は8段階の電圧からなり、駆動電圧V1ないしV8の順に小さくなっている。

【0055】

このような構成において、たとえば、奇数ゲート信号線GLが選択された場合には、前記タイミングコンバータYCONからの信号MによってスイッチSW1がオン状態となり、高レベルVHと中点電圧VMにより正極性の駆動電圧+V1ないし+V8を形成する。そして、偶数ゲート信号線GLが選択された場合には、前記タイミングコンバータYCONからの信号MによってスイッチSW2がオン状態となり、低レベルV L と中点電圧VMにより負極性の駆動電圧−V1ないし−V 8 を形成する。

【0056】

このようなスイッチSW1とSW2の切り替えはフレームの切り替え毎にも行われるようになっている。

【0057】

なお、本実施例は、各ゲート信号線GLのそれぞれによって駆動される画素群において、互いに隣接する画素のそれぞれの液晶の印加電圧極性も反転させている。この場合の反転は、たとえば前記映像信号駆動回路He内で行うようになっている。

【0058】

《電圧極性反転調整回路》

図1は、上述した液晶への印加電圧極性の反転をタイミングコントローラTCONに入力される入力データ(以下、入力表示データと称す)に基づいて調整する回路であり、たとえば前記タイミングコントローラTCONに組み込まれる回路となっている。

【0059】

同図において、まず、シリアル−パラレル変換器102があり、このシリアル−パラレル変換器102に入力表示データ101が入力されるようになっている。

【0060】

これら入力表示データ101は多数の画素データからなり、該シリアル−パラレル変換器102によって、液晶表示部の垂直走査における奇数ラインの画素データおよび偶数ラインの画素データに区別されて出力されるようになっている。

【0061】

また、入力表示データ101の各画素データにはそれぞれカラー表示の赤(R)、緑(G)、青(B)の各情報が含まれており、入力表示データ101のシリアル−パラレル変換器102への入力は、各画素データ毎に赤(R)、緑(G)、青(B)の各情報が対応する異なる入力端子Rdata、Gdata、Bdataを通してなされるようになっており、シリアル−パラレル変換器102からの入力表示データ101の出力は、奇数ラインの各画素データの赤(R)、緑(G)、青(B)の各情報が対応する異なる出力端子Rodd、Godd、Boddを通してなされ、偶数ラインの各画素データの赤(R)、緑(G)、青(B)の各情報が対応する異なる出力端子Reven、Geven、Bevenを通してなされるようになっている。

【0062】

このような動作は、該シリアル−パラレル変換器102にクロック信号113が入力されて、カラー情報の異なる各画素毎に行われるようになっている。

【0063】

そして、シリアル−パラレル変換器102の出力端子Rodd、Bodd、Gevenからの出力は累算器A103に入力され、該シリアル−パラレル変換器102の出力端子Godd、Reven、Bevenからの出力は累算器B104に入力されるようになっている。

【0064】

累算器A103ではそれに入力される各画素データの信号レベル(輝度に対応する)が順次累積され、その累積値はレジスタA105に一旦格納されるようになっている。

【0065】

また、同様に、累算器B104ではそれに入力される各画素データの信号レベルが順次累積され、その累積値はレジスタB106に一旦格納されるようになっている。

【0066】

累算器A103、B104にはそれぞれクロック信号113が入力されて、各累算器A103、B104における累算はカラー情報の異なる各画素毎に行われ、レジスタA105、B106にはそれぞれ垂直同期信号112が入力されて、各レジスタA105、B106における累算は液晶表示の各フレーム毎に行われるようになっている。

【0067】

すなわち、これにより、各フレーム毎に、各奇数ラインの画素データ(R、G、B)の信号レベルの累算値、および各偶数ラインの画素データ(R、G、B)の信号レベルの累算値が得られることになる。

【0068】

そして、これら各累算値に相当する信号が減算器107に入力され、この減算器107によって、レジスタA105に格納された累算値とレジスタB106に格納された累算値の減算がなされるようになっている。

【0069】

この減算器107では、それによって算出された減算値が基準値以上の場合には交流化選択信号116を出力するようになっている。

ここで、前記減算器107には前記基準値を変更できる基準値変更手段120からの信号が入力できるようになっており、前記基準値を任意に設定できるようになっている。

【0070】

なお、前記基準値変更手段120はたとえば液晶の表示面の観察に基づいてオペレータが所定の基準値に設定できるようになっている。

【0071】

一方、交流化信号生成回路108があり、この交流化信号生成回路108は水平同期信号111および垂直同期信号112の入力に基づいて互いに位相が180°ずれた交流化信号A109および交流化信号B110を生成するようになっている。

【0072】

これら各交流化信号A109、B110はセレクタ114に入力されるようになっているとともに、該セレクタ114には前記交流化選択信号116の選択によって前記各交流化信号A109、B110の一方を切替えて出力させるようになっている。

【0073】

この交流化選択信号116は、前記駆動電圧発生回路CPのスイッチSW1、SW2を切り替えるための信号、および映像信号駆動回路Heにおいて、各ラインにおける画素群の隣接する画素どうしの極性反転のために用いられる。

【0074】

このように構成した液晶表示装置は、一フレームの正極と負極の表示データ量に偏りがある場合を検知し、これにより液晶の交流化周期を変化させ、フリッカの発生と消費電力の増加を抑制するようになっている。

【0075】

このように構成されていない従来の液晶表示装置の液晶交流化周期の生成では、

その交流化を相殺する表示パターンが存在してフリッカが発生したり、また、液晶印加電圧極性の正極と負極での表示データの偏りによってコモン電極の電流が大きくなり消費電力が大きくなってしまうという不都合があった。

【0076】

図5は、上述した構成によって、液晶印加電圧と交流化信号の関係の一実施例を示した図である。

【0077】

同図から明らかとなるように、ドット毎およびライン毎の白黒反転パターンが入力されているのに対し、交流化信号をドット毎および2ライン毎に変化されている。このため、電圧印加極性と表示データ301〜308が偏ることがなくなり、液晶印加電圧329がコモン電圧311、316、321、326に対して均一化されるようになる。このため、コモン電極の電流量が増加することがなく、消費電力が抑制できるようになる。

【0078】

また、同様の理由から、液晶表示パネルの表示面にコモン電圧の不均一によるフリッカの発生を抑制できるようになる。

【0079】

ちなみに、図6は、従来の液晶表示装置における液晶印加電圧と交流化信号の関係の一例を示した図で、図5と対応した図となっている。この図から明らかなように、交流化信号は固定されており、表示データがドット毎およびライン毎の白黒反転パターンでは電圧印加極性と表示データ201〜208が偏るために、液晶印加電圧229がコモン電圧に対して偏ることになる。

【0080】

〔実施例2〕

図7は、本発明による液晶表示装置の他の実施例を示す回路図で、たとえば前記タイミングコンバータTCON内に組み込まれる回路となっている。

【0081】

同図において、入力表示データ101は、まずディスプレィイネーブル信号204がHighの期間においてドットマトリクスデータ213として取り込まれ、該ディスプレィイネーブル信号204がLowの期間(帰線期間)においてカラーコード202、キャラクタコード203、キャラクタアドレスコード204として取り込まれるようになっている。

【0082】

ドットマトリクスデータ213として取り込まれたデータは画像合成回路205に入力され、この画像合成回路205において後述の各データと合成がなされるようになっている。

【0083】

カラーコード202として取り込まれたデータはカラーパレット変換回路206に入力され、このカラーパレット変換回路206においてカラーデータ209を生成し、これを出力するようになっている。

【0084】

キャラクタコード203として取り込まれたデータはキャラクタ発生回路207に入力され、このキャラクタ発生回路207においてキャラクタドットマトリクスデータ210を生成し、これを出力するようになっている。

【0085】

キャラクタアドレスコード204として取り込まれたデータはキャラクタアドレス生成回路208に入力され、このキャラクタアドレス生成回路208においてキャラクタ表示アドレスデータ211を生成し、これを出力するようになっている。

【0086】

前記カラーデータ209、キャラクタドットマトリクスデータ210、およびキャラクタ表示アドレスデータ211は、それぞれ前記画像合成回路205に入力され、これらの各データは前記ドットマトリクスデータ213とともに合成されるようになっている。

【0087】

そして、これら合成されたデータは出力表示データ211として出力されるようになり、図3に示す映像駆動回路に入力されるようになっている。

【0088】

このように構成された液晶表示装置は、ドットマトリクス表示とともにキャラクタ表示をする場合、該キャラクタ表示のための入力データをキャラクタデータとして取り込み、ドットマトリクスデータと合成する構成となっている。これにより、データ転送の消費電力の低減を図ることができる。

【0089】

このことは、画素表示においてキャラクタ表示をする頻度が高い場合において該効果が顕著となり、たとえば消費電力の大幅な低減を要求される携帯電話の液晶表示ディスプレィに適用させることもできる。

【0090】

〔実施例3〕

図8は、本発明による液晶表示装置の他の実施例を示す回路図で、たとえば前記タイミングコンバータTCON内に組み込まれる回路となっている。

【0091】

同図において、まず、階調デコーダ302があり、この階調デコーダ302に入力表示データ101が入力されるようになっている。

【0092】

入力表示データ101は0からNまでの各階調をもつ多数の画素データからなり、前記階調デコーダ302ではこれら各画素データのそれぞれを前記階調毎に区分けし、それぞれの階調に応じてその階調に相当する画素データがある場合には、たとえば”1”の信号を出力し、ない場合にはたとえば”0”の信号を出力するようになっている。

【0093】

すなわち、階調デコーダ302は(N+1)個の出力端子を備え、入力表示データ101から0階調の画素データの有無を示す信号、1階調の画素データの有無を示す信号、2階調の画素データの有無を示す信号、……、N階調の画素データの有無を示す信号をそれに対応する出力端子から出力するようになっている。

【0094】

ここで、階調デコーダ302は入力表示データ101にたとえばN階調の画素データが複数個あった場合であっても、その数には関係なく、対応する出力端子からは”1”の信号を出力するようになっている。

【0095】

そして、階調デコーダ302からの前記各出力は、それぞれ0階調レジスタ、1階調レジスタ、……N階調レジスタからなる階調レジスタ群303に入力されるようになっている。

【0096】

すなわち、階調デコーダ302によって出力される0階調の画素データの有無を示す信号は0階調レジスタへ、1階調の画素データの有無を示す信号は1階調レジスタへ、……、N階調の画素データの有無を示す信号はN階調レジスタへ入力されるようになっている。

【0097】

これにより、階調レジスタ群303の各階調レジスタのそれぞれには”1”の信号および”0”の信号のうちいずれかが格納されることになる。

さらに、各階調レジスタからの各出力は加算器304に入力されるようになっている。

【0098】

加算器304は各階調レジスタからの各出力を加算し、その加算した値に相当する信号を出力するようになっている。

【0099】

たとえば、0階調レジスタ、1階調レジスタ、……、N階調レジスタから、それぞれ全て”1”の信号が入力された場合には、それぞれの各信号の加算値(N+1)に相当する信号が出力され、また、4階調レジスタおよび6階調レジスタから”1”の信号が入力され他の残りの各階調レジスタからは”0”の信号が出力された場合には、それぞれの各信号の加算値(2)に相当する信号が入力されるようになっている。

【0100】

このことから明らかなように、加算器304は入力表示データ101における階調の変化度合いを検出するようになっている。

【0101】

すなわち、加算器304は、入力表示データ101の階調の変化度合いを検出し、その変化度合いの大小によって、該入力表示データ101が動画のデータか否かを前記加算器304の出力で判定するようになっている。

【0102】

階調の変化度合いが、大きい場合には動きがともなう画像であると見做して動画像と判定し、小さい場合には動きがともなわない画像であると見做してたとえばワープロ、表計算、メール等で用いられる静画像と判定するようになっている。

【0103】

そして、加算器304からの出力はレジスタ305に入力されてホールドされた後にバックライト制御信号306として出力されるようになっている。このバックライト制御信号306は前記液晶表示パネルPNLの背面に配置されるバックライトBLに入力され、該バックライトBLの輝度を変化させるようになっている。

【0104】

なお、前記階調レジスタ群303の各階調レジスタ、およびレジスタ105にはそれぞれ垂直同期信号307が入力され、この垂直同期信号307によって前記各階調レジスタ群303の各レジスタおよびレジスタ305をリセットするようになっている。

【0105】

これにより、レジスタ305からのバックライトBLへの制御信号は一画面に相当する入力表示データ毎に生成されるようになる。

【0106】

このように構成された液晶表示装置は、その液晶表示パネルPNLに表示される動画像は、静画像が表示される場合よりも輝度が明るくなって表示されるようになる。

【0107】

これにより、動画像の動きを明確に表示できるようになる。一方、静画像の場合にはその輝度があまり大きくなくても明確に表示できることが確かめられている。

【0108】

また、このように、動画像と静画像との区別を検知し、それに応じた最適な輝度表示を行っているため、消費電力の低減が図れる効果を奏する。

【0109】

なお、上述した各実施例は、それぞれ別々に示したものであるが、それぞれの実施例に示す回路が二つあるいは全て組み込まれるようにして構成してもよいことはいうまでもない。

【0110】

そして、従来の構成に対して切り替え手段を介して、それぞれの回路が作動できるように構成してもよいことはいうまでもない。

【0111】

【発明の効果】

以上説明したことから明らかなように、本発明による液晶表示装置によれば、フリッカの発生を抑制できるようになる。また、消費電力を低減させることができるようになる。さらに、動画像を明確に表示できるようになる。

【図面の簡単な説明】

【図1】本発明による液晶表示装置の一実施例を示す要部回路図である。

【図2】本発明による液晶表示装置の液晶表示パネルの一実施例を示す等価回路図である。

【図3】本発明による液晶表示装置の液晶表示パネルとその周辺の回路を示す回路図である。

【図4】本発明による液晶表示装置の駆動電圧発生回路の一実施例を示す回路図である。

【図5】本発明による液晶表示装置の図1に示す回路の具備によって得られる効果を示した説明図である。

【図6】従来の液晶表示装置の場合の不都合を示した説明図で、図5と対応した図となっている。

【図7】本発明による液晶表示装置の他の実施例を示す要部回路図である。

【図8】本発明による液晶表示装置の他の実施例を示す要部回路図である。

【符号の説明】

GL……ゲート信号線、DL……ドレイン信号線、PIX……画素電極、TFT……薄膜トランジスタ、V……垂直走査回路、He……映像信号駆動回路。TCON……タイミングコントローラ、PW……電源安定化回路、CP……駆動電圧発生回路、102……シリパラ変換回路、103、104……累算器、105、106……レジスタ、107……減算器、108……交流化信号生成回路、206……カラーパレット変換回路、207……キャラクタ発生回路、208……キャラクタアドレス生成回路、205……画像合成回路、302……諧調デコーダ、303……諧調レジスタ群、304……加算器、305……レジスタ、306……バックライト制御信号。

Claims (4)

- ゲート信号線に沿った画素群をラインとしてマトリクス状に配置された各画素を有し、交流化信号により一フレーム中の各画素の液晶に印加する電圧の極性を変化させる手段が備えられた液晶表示装置であって、

各奇数ラインの画素データの信号レベルの各フレームにおける累積値および各偶数ラインの画素データの信号レベルの各フレームにおける累積値を得る手段と、

前記各累積値同士を減算する手段と、

前記減算する手段からの減算値が基準値以上の場合に前記交流化信号と異なる他の交流化信号を送出させる手段とを備えることを特徴とする液晶表示装置。 - 前記基準値を変更する手段が設けられていることを特徴とする請求項1に記載の液晶表示装置。

- 一フレームにおける正極の表示データの累積値と、一フレームにおける負極の表示データの累積値との差異が基準値以上の場合、位相が180°ずれた交流化信号を使用することを特徴とする液晶表示装置。

- 前記一フレームにおける正極の表示データの累積値とは、入力される表示データの第1の画素の赤と青と、第2の画素の緑の表示データを累積したものであり、

前記一フレームにおける負極の表示データの累積値とは、入力される表示データの第2の画素の赤と青と、第1の画素の緑の表示データを累積したものであることを特徴とする請求項3に記載の液晶表示装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001246050A JP4230682B2 (ja) | 2001-08-14 | 2001-08-14 | 液晶表示装置 |

| US10/212,208 US7027025B2 (en) | 2001-08-14 | 2002-08-06 | Liquid crystal display device |

| US11/318,583 US20060097977A1 (en) | 2001-08-14 | 2005-12-28 | Liquid crystal display device |

| US12/411,903 US20090184909A1 (en) | 2001-08-14 | 2009-03-26 | Liquid Crystal Display Device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001246050A JP4230682B2 (ja) | 2001-08-14 | 2001-08-14 | 液晶表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008215193A Division JP2009009151A (ja) | 2008-08-25 | 2008-08-25 | 液晶表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003058123A JP2003058123A (ja) | 2003-02-28 |

| JP2003058123A5 JP2003058123A5 (ja) | 2005-09-15 |

| JP4230682B2 true JP4230682B2 (ja) | 2009-02-25 |

Family

ID=19075684

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001246050A Expired - Fee Related JP4230682B2 (ja) | 2001-08-14 | 2001-08-14 | 液晶表示装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US7027025B2 (ja) |

| JP (1) | JP4230682B2 (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4299049B2 (ja) * | 2003-04-24 | 2009-07-22 | 株式会社 日立ディスプレイズ | 表示デバイス用制御信号の検査方法及び検査装置並びにこの検査機能を備えた表示装置 |

| TWI220243B (en) * | 2003-07-15 | 2004-08-11 | Sunplus Technology Co Ltd | Clock generator of flat panel display and generation method of polarity distribution control signal |

| CN100452128C (zh) * | 2003-07-28 | 2009-01-14 | 凌阳科技股份有限公司 | 平面显示器的时序产生器及其极性分布控制信号产生方法 |

| JP2005283702A (ja) * | 2004-03-29 | 2005-10-13 | Sony Corp | 表示パネル、表示装置、半導体集積回路及び電子機器 |

| KR100827453B1 (ko) * | 2004-12-29 | 2008-05-07 | 엘지디스플레이 주식회사 | 일렉트로 루미네센스 표시소자 및 그 구동방법 |

| JP2006251122A (ja) * | 2005-03-09 | 2006-09-21 | Seiko Epson Corp | 液晶パネルの駆動装置および画像表示装置 |

| KR101137844B1 (ko) * | 2005-06-30 | 2012-04-23 | 엘지디스플레이 주식회사 | 액정표시장치 |

| JP4362139B2 (ja) * | 2007-03-28 | 2009-11-11 | Okiセミコンダクタ株式会社 | タイミング・コントローラ、液晶表示装置及び液晶表示パネル駆動方法 |

| CN100582902C (zh) * | 2007-04-25 | 2010-01-20 | 群康科技(深圳)有限公司 | 液晶显示装置及其驱动方法 |

| CN101359107B (zh) * | 2007-08-03 | 2010-05-26 | 群康科技(深圳)有限公司 | 液晶显示装置及其驱动方法 |

| KR101301312B1 (ko) * | 2008-04-08 | 2013-08-29 | 엘지디스플레이 주식회사 | 액정표시장치와 그 구동방법 |

| KR101303424B1 (ko) * | 2008-06-12 | 2013-09-05 | 엘지디스플레이 주식회사 | 액정표시장치와 그 구동방법 |

| KR101363204B1 (ko) * | 2008-12-26 | 2014-02-24 | 엘지디스플레이 주식회사 | 액정표시장치와 그 구동방법 |

| JP5382528B2 (ja) * | 2009-12-28 | 2014-01-08 | Nltテクノロジー株式会社 | 画像表示制御装置、画像表示装置、画像表示制御方法、及び画像表示制御プログラム |

| KR101695290B1 (ko) * | 2010-07-01 | 2017-01-16 | 엘지디스플레이 주식회사 | 액정 표시장치의 구동장치와 그 구동방법 |

| JP6081696B2 (ja) * | 2011-12-01 | 2017-02-15 | エルジー ディスプレイ カンパニー リミテッド | タッチパネルを備えた液晶表示装置およびその駆動方法 |

| KR101982830B1 (ko) * | 2012-07-12 | 2019-05-28 | 삼성디스플레이 주식회사 | 표시 장치 및 그 구동 방법 |

| KR20170059058A (ko) * | 2015-11-19 | 2017-05-30 | 삼성디스플레이 주식회사 | 표시 장치 및 이를 이용한 표시 패널의 구동 방법 |

| US10470264B1 (en) * | 2018-08-24 | 2019-11-05 | Monolithic Power Systems, Inc. | Smart communication interface for LED matrix control |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3349527B2 (ja) * | 1991-10-01 | 2002-11-25 | 株式会社日立製作所 | 液晶中間調表示装置 |

| JP4421722B2 (ja) * | 1999-12-14 | 2010-02-24 | シャープ株式会社 | 液晶表示装置、駆動方法及び駆動回路 |

| KR100381963B1 (ko) * | 2000-12-26 | 2003-04-26 | 삼성전자주식회사 | 감소된 플리커를 갖는 액정 표시 장치 및 그것의 플리커저감 방법 |

-

2001

- 2001-08-14 JP JP2001246050A patent/JP4230682B2/ja not_active Expired - Fee Related

-

2002

- 2002-08-06 US US10/212,208 patent/US7027025B2/en not_active Expired - Lifetime

-

2005

- 2005-12-28 US US11/318,583 patent/US20060097977A1/en not_active Abandoned

-

2009

- 2009-03-26 US US12/411,903 patent/US20090184909A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| US7027025B2 (en) | 2006-04-11 |

| US20030034943A1 (en) | 2003-02-20 |

| US20090184909A1 (en) | 2009-07-23 |

| JP2003058123A (ja) | 2003-02-28 |

| US20060097977A1 (en) | 2006-05-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4230682B2 (ja) | 液晶表示装置 | |

| US5841410A (en) | Active matrix liquid crystal display and method of driving the same | |

| JP3727873B2 (ja) | 液晶表示パネル駆動回路及び液晶表示器 | |

| KR100708241B1 (ko) | 액정 표시 장치 및 그 구동 회로 | |

| US6977636B2 (en) | Liquid crystal display device driving method | |

| US20110285759A1 (en) | Liquid crystal display device and method for driving same | |

| US7724228B2 (en) | Liquid crystal display device and driving method thereof | |

| US20090174642A1 (en) | Liquid crystal display device and driving method thereof | |

| JP2008009288A (ja) | 液晶表示装置および画像表示方法 | |

| US20080284706A1 (en) | Driving Liquid Crystal Display with a Polarity Inversion Pattern | |

| JP2007017863A (ja) | 液晶パネルの駆動方法および液晶表示装置 | |

| JP4566176B2 (ja) | 表示駆動回路 | |

| JP2007093660A (ja) | 表示装置 | |

| JP2007212591A (ja) | 表示装置 | |

| US7423627B2 (en) | Data holding display apparatus, driving method thereof, and television set | |

| KR100495934B1 (ko) | 표시구동장치 및 그 구동제어방법 | |

| WO2017173869A1 (zh) | 液晶显示面板驱动方法、时序控制器及液晶显示装置 | |

| US20060044250A1 (en) | Display panel driving circuit | |

| JP2007140217A (ja) | 表示装置 | |

| US8736640B2 (en) | Liquid crystal display apparatus and method for driving the same | |

| US20050068282A1 (en) | Display, driver device for same, and display method for same | |

| JP2007094008A (ja) | 表示装置 | |

| CN114822435A (zh) | 显示面板的驱动电路、显示器和公共电压调节方法 | |

| JP2001296554A (ja) | 液晶表示装置及び情報携帯機器 | |

| JP2009009151A (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050325 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050325 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080402 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080624 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080825 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20081202 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081204 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4230682 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111212 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111212 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111212 Year of fee payment: 3 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111212 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| S631 | Written request for registration of reclamation of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313631 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111212 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111212 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313115 Free format text: JAPANESE INTERMEDIATE CODE: R313121 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111212 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111212 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121212 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121212 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131212 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |