JP4144258B2 - 画像出力装置及び画像出力方法 - Google Patents

画像出力装置及び画像出力方法 Download PDFInfo

- Publication number

- JP4144258B2 JP4144258B2 JP2002156273A JP2002156273A JP4144258B2 JP 4144258 B2 JP4144258 B2 JP 4144258B2 JP 2002156273 A JP2002156273 A JP 2002156273A JP 2002156273 A JP2002156273 A JP 2002156273A JP 4144258 B2 JP4144258 B2 JP 4144258B2

- Authority

- JP

- Japan

- Prior art keywords

- image

- display

- unit

- image data

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/60—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding

- H04N19/61—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding in combination with predictive coding

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/02—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators characterised by the way in which colour is displayed

- G09G5/026—Control of mixing and/or overlay of colours in general

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Studio Circuits (AREA)

- Controls And Circuits For Display Device (AREA)

- Image Processing (AREA)

- Compression Or Coding Systems Of Tv Signals (AREA)

Description

【発明の属する技術分野】

PCアーキテクチャをベースとし、圧縮動画像と背景画像との合成を行う画像出力装置及び画像出力方法に関する。

【0002】

【従来の技術】

従来、PC(パーソナルコンピュータ)をベースとしたビデオ画像表示装置では、入力された圧縮動画像をビデオデコーダボードやグラフィックアクセラレータ等を利用してデコード処理し、デコード処理した動画像とそれ以外の画像とをグラフィック出力部で合成し、合成した画像を表示画像として表示装置に出力している。

【0003】

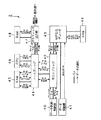

ここで、図6を用いて、上述のように画像を合成し、合成した画像を表示装置に出力する従来の装置(以下、画像出力装置2という。)について構成と動作を説明する。

【0004】

画像出力装置2は、図6に示すように、データ供給・格納部40と、データ供給部41と、サウスブリッジ42と、MPEGデコーダ43と、ノースブリッジ44と、RAM45と、CPU46と、グラフィック出力部47と、RAM48と、RAM49とを備えている。データ供給・格納部40は、サウスブリッジ42に接続されており、例えば、DVDドライブ、HDD、ネットワークモジュール、画像キャプチャーモジュール又はチューナーモジュール等の圧縮画像を含むデータを入出力する装置である。なお、複数台のデータ供給・格納部40がサウスブリッジ42に接続されていても良い。また、データ供給・格納部40は、例えばIEEE1394等のインターフェースを介してサウスブリッジ42に接続されていても良い。

【0005】

データ供給部41は、例えば、チューナーや外部入力モジュールであり、MPEGデコーダ43に接続されており、MPEGデコーダ43に圧縮画像を直接送信できるようになっている。サウスブリッジ42は、例えば、ICH(I/O Controller Hub)等のブリッジ又はハブであり、ノースブリッジ44及びMPEGデコーダ43が接続されている。サウスブリッジ42は、データ供給・格納部40から供給されてくるデータをノースブリッジ44及びMPEGデコーダ43に適合した所定の信号形式に変換し、変換後の信号をノースブリッジ44及びMPEGデコーダ43に出力する。MPEGデコーダ43は、サウスブリッジ42又はデータ供給装置から供給されたMPEGデータをデコードする。MPEGデコーダ43は、MPEGデコードデータをRAM49に出力する。RAM49は、MPEGデコーダ43から入力されたMPEGデコードデータを記憶する。RAM49に記憶されたMPEGデコードデータは、CPU46からの読み出し命令により読み出され、サウスブリッジ42に出力される。

【0006】

ノースブリッジ44は、例えば、MCH(Memory Controller Hub)等のブリッジ又はハブであり、RAM45と、CPU46と、グラフィック出力部47とに接続されている。ノースブリッジ44は、サウスブリッジ42から供給されてくるMPEGデータ、MPEGデコードデータ又はグラフィックデータ等を接続されている機器に適合した所定の信号形式に変換し出力する。CPU46は、画像出力装置2のメイン処理部として動作し、RAM45に記憶されているデータを読み出し、読み出したデータに所定の処理を行い、その処理結果をノースブリッジ44を介してグラフィック出力部47等に出力する。

【0007】

グラフィック出力部47は、ノースブリッジ44を介して入力されるデータに基づき表示部に適合した画像形式に変換して表示画像を生成し、表示部に出力する。なお、MPEGデコードデータに基づき生成される画像は、表示部の所定の場所に表示させるためにクロマキにより、キーカラーで塗りつぶした領域に表示される。

【0008】

【発明が解決しようとする課題】

上述したように、従来の画像出力装置2では、デコード処理したMPEGデータを表示画像に変換し、表示部に出力するために、MPEGデータをMPEGデコーダ43でデコード処理してからPCIバス等の接続線を介してサウスブリッジ42、ノースブリッジ44を経てグラフィック出力部47に供給する必要があった。

【0009】

したがって、デコード処理したMPEGデータがHDTV(High Definition Television)クラスの大容量データの場合には、MPEGデコーダ43サウスブリッジ42間のバスが帯域不足になる問題がある。

【0010】

また、上記問題点を解決するために、図7に示すように、データ供給部41から供給されたMPEGデータのデコード処理の一部をCPU46により行い、一部処理後のMPEGデータをMPEGデコード支援演算器を有したグラフィック出力部50に供給し、グラフィック出力部50で残りのデコード処理を行う構成にした場合には、一部のデコード処理をCPU46が行うことによるCPU46の負荷が増加し、かつ一部処理後のMPEGデータをノースブリッジ44からグラフィック出力部50へ供給する際に、ノースブリッジ44グラフィック出力部47間のバスの帯域を消費する問題がある。

【0011】

さらに、上述したように、MPEGデコードデータにより表される第1の表示画像を表示部に表示する際、上記第1の表示画像は、所定のキーカラーで塗りつぶした領域に表示されるため、第1の表示画像の上面にMPEGデータ以外の画像データにより表される第2の表示画像が重なった場合、図5(a)に示すように、上記キーカラーと第2の表示画像で使用されている色とが同一の部分において、後面の第1の表示画像が前面に表示される現象が起こる問題がある。

【0012】

そこで、本発明では、MPEGデコーダ−サウスブリッジ間及びサウスブリッジ−ノースブリッジ間及びノースブリッジ−グラフィック出力部間のバスにかかる負担を軽減し、かつ第1の表示画像と第2の表示画像とが重なり合う部分において、後面の第1の表示画像が前面の第2の表示画像に表示されてしまうという現象を起こすことなく表示画像の合成を行うことが可能な画像出力装置及び画像出力方法を提供することを目的とする。

【0013】

【課題を解決するための手段】

本発明に係る画像出力装置は、上述の問題を解決するために、入力された圧縮画像を含む符号化動画像データから第1の画像データを復号する復号手段、及び、上記第1の画像データと第2の画像データとを合成し、合成した表示画像を表示部に出力する合成出力手段を備える復号/合成部と、入力されたデータを一時記憶する記憶部と、上記復号/合成部に備えられた上記復号手段により復号された上記第1の画像データを上記表示部に表示する際、上記表示部の指定された場所に任意の大きさで上記第1の画像データにより表される第1の表示画像が表示される表示領域を示す第1の表示領域情報を生成する第1の表示領域情報生成手段、及び、上記表示部の指定された場所に任意の大きさで上記第2の画像データにより表される第2の表示画像が表示される表示領域を示す第2の表示領域情報を生成する第2の表示領域情報生成手段として機能する演算処理部と、上記記憶部により一時記憶されたデータに含まれている画像データに基づき上記表示部に適合した画像形式の上記第2の画像データを生成する表示画像生成手段、及び、上記第1の画像データと上記第2の画像データとを合成する際に、上記第1の表示画像と上記第2の表示画像が重なって表示される場合、上記第1の表示領域情報と上記第2の表示領域情報及び上記第1の画像データと上記第2の画像データの位置関係に基づき、合成パラメータを生成する合成パラメータ生成手段を備え、上記合成パラメータ生成手段は、上記第1の画像データによる第1の表示画像が前面で、上記第2の画像データによる第2の表示画像が後面の場合には、上記合成パラメータを透明に調整し、上記第2の画像データによる第2の表示画像が前面で、上記第1の画像データによる第1の表示画像が後面の場合には、上記合成パラメータを不透明に調整し、上記合成パラメータ生成手段により生成した合成パラメータを上記表示画像生成手段により生成した第2の画像データに付加して出力するグラフィック出力部とを備え、上記グラフィック出力部と上記復号/合成部との間がバスで接続され、上記グラフィック出力部から上記合成パラメータが付加された上記第2の表示画像を上記復号/合成部に供給し、上記復号/合成部において、上記記復号手段により復号された上記第1の表示画像と上記第2の表示画像とを上記合成出力手段により上記第2の表示画像に付加されている上記合成パラメータに基づき合成し、合成した表示画像を上記表示部に出力することを特徴とする。

また、本発明に係る画像出力方法は、入力された圧縮画像を含む符号化動画像データから復号された第1の画像データを表示部に表示する際、上記表示部の指定された場所に任意の大きさで上記第1の画像データにより表される第1の表示画像が表示される表示領域を示す第1の表示領域情報を生成し、入力されたデータに含まれている画像データに基づき上記表示部に適合した画像形式の第2の画像データを生成し、入力された第2の画像データを上記表示部に表示する際、上記第2の画像データを表示される表示領域を示す第2の表示領域情報を生成し、上記表示部の指定された場所に任意の大きさで上記第2の画像データにより表される第2の表示画像が表示される表示領域を示す第2の表示領域情報を生成し、上記第1の画像データと上記第2の画像データとを合成する際に、上記第1の表示画像と上記第2の表示画像が重なって表示される場合、上記第1の表示領域情報と上記第2の表示領域情報及び上記第1の画像データと上記第2の画像データの位置関係に基づき、合成パラメータを生成し、上記第1の画像データによる第1の表示画像が前面で、上記第2の画像データによる第2の表示画像が後面の場合には、上記合成パラメータを透明に調整し、上記第2の画像データによる第2の表示画像が前面で、上記第1の画像データによる第1の表示画像が後面の場合には、上記合成パラメータを不透明に調整して、上記合成パラメータを上記第2の画像データに付加し、上記第2の表示画像に付加されている上記合成パラメータに基づき、上記第1の画像データと上記第2の画像データとを合成し、合成した表示画像を上記表示部に出力することを特徴とする。

【0014】

【発明の実施の形態】

以下、本発明の実施の形態について図面を参照しながら詳細に説明する。

【0015】

本発明は、例えば図1に示すような画像出力装置1に適用される。画像出力装置1は、表示画像を表示部に出力する装置であり、データ供給部10と、データ格納部11と、サウスブリッジ12と、MPEGデコーダ/画像合成部13と、RAM14と、ノースブリッジ15と、RAM16と、CPU17と、グラフィック出力部18と、RAM19とを備える。画像出力装置1は、MPEGデコーダ/画像合成部13でデータ供給部10から供給されたMPEGデータをデコードし、CPU17で上記表示部の指定された場所に任意の大きさで上記デコード後のMPEGデータ(以下、MPEGデコードデータという。)により表される第1の表示画像を表示させる第1の表示領域情報を生成し、また、RAM16にグラフィックデータを含むデータを一時記憶し、グラフィック出力部18でRAM16から読み出したグラフィックデータに基づき上記表示部に適合した画像形式である第2の表示画像を生成し、CPU17で上記表示部の指定された場所に任意の大きさで第2の表示画像を表示させる第2の表示領域情報を生成し、かつ上記第1の表示画像と上記第2の表示画像とを合成する際に、上記第1の表示領域情報と上記第2の表示領域情報に基づき、合成状態を決定する合成パラメータ(以下、アルファプレーン情報という。)を生成し、グラフィック出力部18で上記第2の表示画像に上記アルファプレーン情報を付加する。また、画像出力装置1は、グラフィック出力部18とMPEGデコーダ/画像合成部13とが接続線で接続されており、上記接続線を介してグラフィック出力部18からMPEGデコーダ/画像合成部13にアルファプレーン情報付きの第2の表示画像が供給され、MPEGデコーダ/画像合成部13で上記アルファプレーン情報に基づき、上記第1の表示画像と上記第2の表示画像とを合成し、合成した表示画像を上記表示部に出力する。

【0016】

以下に、上述した画像出力装置1の構成と動作について詳述する。データ供給部10は、例えば、DVDドライブ、ネットワークモジュール、画像キャプチャーモジュール又はチューナーモジュール等の圧縮画像を含むデータを入出力する装置であり、サウスブリッジ12及びMPEGデコーダ/画像合成部13に接続されている。データ供給部10は、サウスブリッジ12を介してMPEGデコーダ/画像合成部13及びノースブリッジ15にMPEGデータ等を供給しても良いし、MPEGデコーダ/画像合成部13に直接、MPEGデータを供給しても良い。なお、複数台のデータ供給部10がサウスブリッジ12に接続されていても良い。また、データ供給部10は、例えばIEEE1394等のインターフェースを介してサウスブリッジ12に接続されていても良い。

【0017】

データ格納部11は、例えば、HDDやDVDレコーダ等であり、サウスブリッジ12に接続されている。データ格納部11は、サウスブリッジ12を介してMPEGデータを記録する。サウスブリッジ12は、例えば、ICH(I/O Controller Hub)等のブリッジ又はハブであり、データ格納部11、データ供給部10、ノースブリッジ15及びMPEGデコーダ/画像合成部13が接続されている。サウスブリッジ12は、データ供給部10から供給されるグラフィックデータ及びMPEGデータ等を所定の信号形式に変換し、ノースブリッジ15及びMPEGデコーダ/画像合成部13に供給する。

【0018】

MPEGデコーダ/画像合成部13は、例えば、DSPであり、データ供給部10、サウスブリッジ12、RAM14及びグラフィック出力部18が接続されており、データ供給部10から供給されたMPEGデータ又はサウスブリッジ12を介して供給されたMPEGデータをデコード処理する。また、MPEGデコーダ/画像合成部13は、グラフィック出力部18から第2の表示画像とともに供給されるアルファプレーン情報に基づき、MPEGデコードデータにより表される第1の表示画像と第2の表示画像とを合成処理し、合成した表示画像を表示部に出力する。また、MPEGデコーダ/画像合成部13は、MPEGデコードデータ及び合成処理した表示画像をRAM14に出力する。なお、表示部に表示される第1の表示画像及び第2の表示画像は、CPU17で生成された表示領域情報に基づき、指定された場所に任意の大きさで表示される。

【0019】

RAM14は、例えば、DRAMであり、MPEGデコーダ/画像合成部13でデコード処理されたMPEGデコードデータや、合成処理された合成画像を記憶保持する。RAM14に記憶された上記合成画像は、表示部に出力され表示される。なお、RAM14は、MPEGデコーダ/画像合成部13により使用されるデータを記憶保持することができるものであればSDRAM等でも良い。

【0020】

ノースブリッジ15は、例えば、MCH(Memory Controller Hub)等のブリッジ又はハブであり、サウスブリッジ12、RAM16、CPU17及びグラフィック出力部18に接続されている。ノースブリッジ15は、サウスブリッジ12から供給されるグラフィックデータ及びMPEGデータ等を所定の信号形式に変換し、RAM16及びCPU17に供給する。RAM16は、例えば、SDRAMであり、ノースブリッジ15に接続されており、画像出力装置1のメインメモリとして動作し、画像出力装置1で利用されるさまざまなデータの記憶保持を行う。なお、RAM16は、画像出力装置1のメインメモリとして利用できるモジュールであればRDRAM等でも良い。CPU17は、ノースブリッジ15に接続されており、画像出力装置1のメイン処理部として動作し、RAM16に記憶されているデータを読み出し、読み出したデータに所定の処理を行い、その処理結果をノースブリッジ15を介してグラフィック出力部18等に出力する。また、CPU17は、グラフィック出力部18で表示画像の合成を行う際に用いるアルファプレーン情報を生成し、生成したアルファプレーン情報をグラフィック出力部18に出力する。なお、アルファプレーン情報の生成の方法については後述する。

【0021】

グラフィック出力部18は、例えば、グラフィック・アクセラレータであり、ノースブリッジ15、RAM19及びMPEGデコーダ/画像合成部13に接続されており、ノースブリッジ15を介して供給されたグラフィックデータに基づき、所定の画像形式である表示画像を生成し、生成した上記表示画像とアルファプレーン情報を混合し、アルファプレーン情報付の表示画像をMPEGデコーダ/画像合成部13に供給する。また、グラフィック出力部18は、アルファプレーン情報付の表示画像の処理や保持のためにRAM19を利用する。なお、グラフィック出力部18は、グラフィックデータに基づき所定の画像形式である表示画像を生成でき、生成した表示画像とアルファプレーン情報を混合でき、かつMPEGデコーダ/画像合成部13に出力できる構成のものであればグラフィック・アクセラレータ以外でも良い。

【0022】

RAM19は、例えば、DDRであり、グラフィック出力部18に接続されており、グラフィック出力部18で使用されるデータの記憶保持を行う。なお、RAM19は、グラフィック出力部18が使用するデータの記憶保持ができるモジュールであればSDRAM等でも良く、また、RAM16を代用しても良い。この場合、RAM19の分のコストが抑えられ、装置全体のコストダウンとなる。

【0023】

ここで、MPEGデコーダ/画像合成部13の画像合成動作について説明する。MPEGデコーダ/画像合成部13は、上述したようにサウスブリッジ12又はデータ供給部10から供給されたMPEGデータをデコード処理し、MPEGデコードデータを生成し、MPEGデコードデータに基づき表示部に適合した画像形式である第1の表示画像を生成する。一方、グラフィック出力部18は、上述したようにノースブリッジ15からグラフィックデータが供給され、上記グラフィックデータに基づき表示部に適合した画像形式である第2の表示画像を生成する。CPU17は、上記MPEGデコードデータにより表される第1の表示画像及び上記グラフィックデータにより表される第2の表示画像をそれぞれ表示部の指定された場所に任意の大きさで表示させるための表示領域情報を生成し、生成した表示領域情報をMPEGデコーダ/画像合成部13に供給する。また、CPU17は、所定の階調値を有するアルファプレーン情報を1画面分生成し、上記アルファプレーン情報をグラフィック出力部18に供給する。グラフィック出力部18は、上記アルファプレーン情報と上記第2の表示画像とを合成し、アルファプレーン情報付きの第2の表示画像をMPEGデコーダ/画像合成部13に供給する。

【0024】

MPEGデコーダ/画像合成部13は、アルファプレーン情報に基づき第1の表示画像と第2の表示画像とを合成し、合成した表示画像を表示領域情報に応じて表示部に出力する。

【0025】

この例で説明しているアルファプレーン情報は、第2の表示画像に付属する情報であり、例えば、第2の表示画像に付属するアルファプレーン情報において透明度を「α」とすると、表示部に表示される色の情報「C」は、第1の表示画像の色情報「C1」と、第2の表示画像の色情報「C2」とを用いて、

C=C1×(1−α)+C2×α

で表すことができる。なお、αは、0≦α≦1であり、例えば、α=0の時、アルファプレーン情報が付属する画像(第2の表示画像)の中でα=0となっているピクセル部分が完全に透明であると仮定し、α=1で完全に不透明であると仮定する。

【0026】

上記では、式を簡単にするため、色情報「C」を用いたが、実際にはR、G、Bや輝度、クロマ等といったピクセル情報が用いられる。また、アルファプレーン情報は、画面の3次元座標上での前後関係(Z軸方向)とは別に独立して考えることができ、例えば、図2(a)の「T」で示した領域のアルファプレーン情報が「α=0(透明)」となっていた場合、「T」の領域には背後の情報である第1の表示画像が合成され出力される。なお、より高度な画面表示を行うために、第1の表示画像もアルファプレーン情報を持っていても良い。

【0027】

CPU17は、図2(b)に示すように、第1の表示画像と第2の表示画像とが重なり合う部分において、最終的に表示部に表示される画像で、表示されている画像が「前面」であると定義した場合(前述したように、実際の画面の前後関係はアルファプレーン情報とは独立して与えることが出来るが、表示部に表示される2次元の画像の見え方はアルファプレーン情報によって変化するので、見かけ上前面に見える部分を「前面」と表現する)、第1の表示画像が前面となり、第2の表示画像が後面となる場合には、例えば、アルファプレーン情報の第1の表示画像領域を「透明」に調整する。また、図2(c)第2の表示画像が前面となり、第1の表示画像が後面となる場合には、例えば、アルファプレーン情報の第2の表示画像領域を「不透明」に調整する。

【0028】

また、MPEGデコーダ/画像合成部13は、例えば、図3に示すような、第1のウィンドウ拡縮制御部30と、アルファプレーン情報抽出部31と、第1の制御回路部32と、ビデオデコーダ部33と、第2のウィンドウ拡縮制御部34と、第2の制御回路部35と、表示画像合成部36とを備える構成であっても良い。

【0029】

アルファプレーン情報付きの第2の表示画像が第1のウィンドウ拡縮制御部30に入力される。第1のウィンドウ拡縮制御部30は、第2の表示画像が表示部に表示される際の大きさ及び位置を制御し、アルファプレーン情報抽出部31に出力する。アルファプレーン情報抽出部31は、第2の表示画像からアルファプレーン情報を抽出する。抽出されたアルファプレーン情報は、第1の制御回路部32と第2の制御回路部35とに供給される。第1の制御回路部32は、第2の表示画像に所定の制御を行い、制御後の第2の表示画像を表示画像合成部36に出力する。

【0030】

ビデオデコーダ部33は、入力されるMPEGデータをデコード処理し、第1の表示画像を生成し、上記第1の表示画像を第2のウィンドウ拡縮制御部34に出力する。第2のウィンドウ拡縮制御部34は、第1の表示画像が表示部に表示される際の大きさ及び位置を制御し、制御後の第1の表示画像を第2の制御回路部35に出力する。第2の制御回路部35は、第1の表示画像に所定の制御を行い、制御後の第1の表示画像を表示画像合成部36に出力する。表示画像合成部36は、第1の表示画像と第2の表示画像を合成し、表示部に出力する。

【0031】

なお、上記のように、第1の表示画像および第2の表示画像を処理するウィンドウ拡縮制御部34が存在するため、第1の表示画像の領域サイズと第2の表示画像の領域サイズは、表示部で最終的に表示に用いられる領域サイズと一致していなくても良い。

【0032】

また、第1の制御回路部32は第2の表示画像とこれに付属するアルファプレーン情報である係数「α」とから第2の表示画像を制御し、第2の制御回路部35は、第1の表示画像と、係数「1−α」とによって第1の表示画像を制御する。

【0033】

つぎに、アルファプレーン情報の生成について図4に示すフローチャートを用いて説明する。

【0034】

ステップST1において、CPU17は、アルファプレーン情報の生成処理を継続するかどうかの判定を行う。CPU17は、MPEGデコーダ/画像合成部13が合成画像の出力を表示部に対して行わない場合には、アルファプレーン情報の生成処理を終了し、MPEGデコーダ/画像合成部13が合成画像の出力を表示部に対して継続する場合にはステップST2に進む。

【0035】

ステップST2において、CPU17は、第1の表示画像と第2の表示画像との前面/後面の順位等の位置関係が前回処理した後に更新されているかどうかを判断する。

【0036】

ステップST3において、CPU17は、上記ステップST2の判断により、第1の表示画像と第2の表示画像との前面/後面の順位等の位置関係が前回と変わらない(更新されていない)場合にはステップST1に戻り、第1の表示画像と第2の表示画像との前面/後面の順位等の位置関係が前回の処理から変化している(更新されている)場合にはステップST4に進む。なお、初めて処理を開始した場合には、ステップST4に進むこととする。また、ステップST2〜ステップST3の処理を行うことにより、それぞれの領域が移動していない場合に、CPU17で処理されるデータ量を減少させることができ、また、負荷を減らすことができる。

【0037】

ステップST4において、CPU17は、出力する1画面分のアルファプレーン情報が生成されたかどうかを判断する。1画面分のアルファプレーン情報が生成されたと判断した場合には、ステップST1に戻り、1画面分のアルファプレーン情報が生成されていないと判断した場合には、未処理のピクセルについてアルファプレーン情報の生成を継続するため、ステップST5に進む。

【0038】

ステップST5において、CPU17は、第1の表示画像と第2の表示画像との前面/後面の順位を計算する。この前面/後面というのは、前述したように、3次元上での画面の位置関係ではなく、表示部での見え方である。現在判定しているピクセルに図1に示したMPEGデコーダ/画像合成部13で得られる画像を表示部に表示する場合、処理しているピクセルのアルファプレーン情報の値を階調値0(透明)に調整する。また、グラフィック出力部18から得られる画像を表示部に表示したい場合は、255(不透明)に調整する。なお、この例でのアルファプレーン情報は、0(透明)〜255(不透明)の256階調とし、表示したい透明度に応じてこの中間値をとることができる。この処理の終了後、ステップST4に戻る。

【0039】

上述のような処理を行うことでアルファプレーン情報の生成が行われる。MPEGデコーダ/画像合成部13では、上記アルファプレーン情報の階調値に基づき第1の表示画像と第2の表示画像との合成を行い、合成画像を表示部に出力する。

【0040】

したがって、本発明に係る画像出力装置1に備えられているグラフィック出力部18は、MPEGデータ以外のグラフィックデータや、上記グラフィックデータにより表される第2の表示画像を表示部に表示するための各種のコマンドや、上述したアルファプレーン情報等のデータを処理し、アルファプレーン情報付きの表示画像を生成し、生成したアルファプレーン情報付きの表示画像をMPEGデコーダ/画像合成部13に供給する。従来の画像出力装置の場合、グラフィック出力部18と表示部とが接続線で接続され、上記接続線を介してグラフィック出力部18から表示部に表示画像を出力していたが、本発明では、グラフィック出力部18とMPEGデコーダ/画像合成部13とが接続線で接続され、上記接続線を介してグラフィック出力部18からMPEGデコーダ/画像合成部13にアルファプレーン情報付きの表示画像を供給し、MPEGデコーダ/画像合成部13から表示画像を表示部に出力する。

【0041】

ここで、従来の画像出力装置による表示画像の合成処理と本発明に係る画像出力装置1による表示画像の合成処理とを図5を用いて比較する。従来の画像出力装置では、図5(a)に示すように、第1の表示画像が後面で第2の表示画像が前面の場合において、第1の表示画像と第2の表示画像の合成時に、比較回路により第2の表示画像に使用されている色とキーカラーとの差分を与えるので、第1の表示画像のキーカラーと第2の表示画像のA領域に使用されている色とが同一のときには、第1の表示画像が第2の表示画像のA領域の部分に表示されてしまう。一方、本発明に係る画像出力装置では、図5(b)に示すように、上記図3に示した構成となっているので、後面である第1の表示画像が前面である第2の表示画像上に表示されることはない。

【0042】

このように構成された画像出力装置1では、グラフィック出力部18とMPEGデコード間をバスで接続し、グラフィック出力部18からグラフィックデータにより表されるアルファプレーン情報付きの第2の表示画像をMPEGデコーダ/画像合成部13に供給し、MPEGデコーダ/画像合成部13によりMPEGデコードデータにより表される第1の表示画像と上記第2の表示画像とをアルファプレーン情報に基づき合成し、合成した表示画像を表示部に出力するので、MPEGデコード−サウスブリッジ12間又はノースブリッジ15グラフィック出力部18間の接続線にかかる負担が軽減され、かつ第1の表示画像と第2の表示画像とが重なり合う部分において、後面の第1の表示画像が前面の第2の表示画像上に表示される現象を起こすことなく表示画像の合成を行うことができる。さらに、画像出力装置1では、MPEGデータのデコード処理をMPEGデコーダ/画像合成部13のみで行うため、CPU17の負荷を軽減することが可能である。

【0043】

なお、本発明に係る画像出力装置1では、グラフィックデータ及びMPEGデータに加えて、プログラムやプログラムが扱うデータの他、様々な制御信号が接続線を介して各機器間で送受信される。また、上述した第1の表示画像及び第2の表示画像は、RGB信号又はYUV信号その他の表色系で表示部に出力される。さらに、本発明に係る画像出力装置1は、例えば、パーソナルコンピュータ(PC、Personal Computer)、携帯情報端末、パーソナルビデオレコーダ(PVR、Personal Video Recorder)又はセットトップボックス(STB、Set Top Box)等に適用される。

【0044】

【発明の効果】

以上詳細に説明したように、本発明によれば、入力された圧縮画像を含む符号化動画像データから第1の画像データを復号する復号手段、及び、上記第1の画像データと第2の画像データとを合成し、合成した表示画像を表示部に出力する合成出力手段を備える復号/合成部とバスで接続されたグラフィック出力部において、記憶部により一時記憶された入力されたデータに含まれている画像データに基づき上記表示部に適合した画像形式の第2の画像データを表示画像生成手段により生成し、第1の表示領域情報生成手段、及び、第2の表示領域情報生成手段として機能する演算処理部により生成される表示部の指定された場所に任意の大きさで第1の画像データにより表される第1の表示画像が表示される表示領域を示す第1の表示領域情報と上記表示部の指定された場所に任意の大きさで第2の画像データにより表される第2の表示画像が表示される表示領域を示す第2の表示領域情報及び上記第1の画像データと上記第2の画像データの位置関係に基づき、合成パラメータ生成手段により合成パラメータを生成し、上記第1の画像データによる表示画像が前面で、上記第2の画像データによる表示画像が後面の場合には、上記合成パラメータを透明に調整し、上記第2の画像データによる表示画像が前面で、上記第1の画像データによる表示画像が後面の場合には、上記合成パラメータを不透明に調整し、上記合成パラメータ生成手段により生成した合成パラメータを上記表示画像生成手段により生成した第2の画像データに付加し、上記合成パラメータを付加した上記第2の画像データが供給される上記復号/合成部において、上記記復号手段により復号された上記第1の画像データと上記第2の画像データとを上記合成出力手段により上記第2の画像データに付加されている上記合成パラメータに基づき合成し、合成した表示画像を上記表示部に出力するので、大容量の第1の画像データを当該画像出力装置内の接続線以外の接続線に負担をかけて移動させることがないため、接続線の負担を軽減することができ、しかも、合成パラメータに基づき第1の画像データと上記第2の画像データとを合成するので、第1の画像データによる表示画像と第2の画像データによる表示画像とが重なり合う部分において、後面の第1の画像データによる表示画像が前面の第2の画像データによる表示画像上に表示される現象を起こすことなく表示画像の合成を行うことができる。

【図面の簡単な説明】

【図1】本発明を適用した画像出力装置の構成を示すブロック図である。

【図2】第1の表示画像と第2の表示画像とを合成し(a)、第1の表示画像が前面で第2の表示画像が後面の場合(b)と、第2の表示画像が前面で第1の表示画像が後面の場合(c)の合成画像を示す模式図である。

【図3】本発明を適用した画像出力装置が備えているMPEGデコーダ/画像合成部の構成を示すブロック図である。

【図4】本発明を適用した画像出力装置が備えているCPUによりアルファプレーン情報を生成する動作を示すフローチャートである。

【図5】従来の画像出力装置による合成処理(a)と、本発明に係る画像出力装置による合成処理(b)とを比較した図である。

【図6】従来の画像出力装置の第1の構成例を示すブロック図である。

【図7】従来の画像出力装置の第2の構成例を示すブロック図である。

【符号の説明】

1 画像出力装置、10 データ供給部、11 データ格納部、12 サウスブリッジ、13 MPEGデコーダ/画像合成部、14,16,19 RAM、15 ノースブリッジ、17 CPU、18 グラフィック出力部、30 第1のウィンドウ拡縮制御部、31 アルファプレーン情報抽出部、32 第1の制御回路部、33 ビデオデコーダ部、34 第2のウィンドウ拡縮制御部、35第2の制御回路部、36 表示画像合成部

Claims (2)

- 入力された圧縮画像を含む符号化動画像データから第1の画像データを復号する復号手段、及び、上記第1の画像データと第2の画像データとを合成し、合成した表示画像を表示部に出力する合成出力手段を備える復号/合成部と、

入力されたデータを一時記憶する記憶部と、

上記復号/合成部に備えられた上記復号手段により復号された上記第1の画像データを上記表示部に表示する際、上記表示部の指定された場所に任意の大きさで上記第1の画像データにより表される第1の表示画像が表示される表示領域を示す第1の表示領域情報を生成する第1の表示領域情報生成手段、及び、上記表示部の指定された場所に任意の大きさで上記第2の画像データにより表される第2の表示画像が表示される表示領域を示す第2の表示領域情報を生成する第2の表示領域情報生成手段として機能する演算処理部と、

上記記憶部により一時記憶されたデータに含まれている画像データに基づき上記表示部に適合した画像形式の上記第2の画像データを生成する表示画像生成手段、及び、上記第1の画像データと上記第2の画像データとを合成する際に、上記第1の表示画像と上記第2の表示画像が重なって表示される場合、上記第1の表示領域情報と上記第2の表示領域情報及び上記第1の画像データと上記第2の画像データの位置関係に基づき、合成パラメータを生成する合成パラメータ生成手段を備え、上記合成パラメータ生成手段は、上記第1の画像データによる第1の表示画像が前面で、上記第2の画像データによる第2の表示画像が後面の場合には、上記合成パラメータを透明に調整し、上記第2の画像データによる第2の表示画像が前面で、上記第1の画像データによる第1の表示画像が後面の場合には、上記合成パラメータを不透明に調整し、上記合成パラメータ生成手段により生成した合成パラメータを上記表示画像生成手段により生成した第2の画像データに付加して出力するグラフィック出力部と

を備え、

上記グラフィック出力部と上記復号/合成部との間がバスで接続され、

上記グラフィック出力部から上記合成パラメータが付加された上記第2の表示画像を上記復号/合成部に供給し、上記復号/合成部において、上記記復号手段により復号された上記第1の表示画像と上記第2の表示画像とを上記合成出力手段により上記第2の表示画像に付加されている上記合成パラメータに基づき合成し、合成した表示画像を上記表示部に出力する画像出力装置。 - 入力された圧縮画像を含む符号化動画像データから復号された第1の画像データを表示部に表示する際、上記表示部の指定された場所に任意の大きさで上記第1の画像データにより表される第1の表示画像が表示される表示領域を示す第1の表示領域情報を生成し、

入力されたデータに含まれている画像データに基づき上記表示部に適合した画像形式の第2の画像データを生成し、

入力された第2の画像データを上記表示部に表示する際、上記第2の画像データを表示される表示領域を示す第2の表示領域情報を生成し、

上記表示部の指定された場所に任意の大きさで上記第2の画像データにより表される第2の表示画像が表示される表示領域を示す第2の表示領域情報を生成し、

上記第1の画像データと上記第2の画像データとを合成する際に、上記第1の表示画像と上記第2の表示画像が重なって表示される場合、上記第1の表示領域情報と上記第2の表示領域情報及び上記第1の画像データと上記第2の画像データの位置関係に基づき、合成パラメータを生成し、

上記第1の画像データによる第1の表示画像が前面で、上記第2の画像データによる第2の表示画像が後面の場合には、上記合成パラメータを透明に調整し、上記第2の画像データによる第2の表示画像が前面で、上記第1の画像データによる第1の表示画像が後面の場合には、上記合成パラメータを不透明に調整して、上記合成パラメータを上記第2の画像データに付加し、

上記第2の表示画像に付加されている上記合成パラメータに基づき、上記第1の画像データと上記第2の画像データとを合成し、

合成した表示画像を上記表示部に出力する画像出力方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002156273A JP4144258B2 (ja) | 2002-05-29 | 2002-05-29 | 画像出力装置及び画像出力方法 |

| TW92113110A TWI229285B (en) | 2002-05-29 | 2003-05-14 | Picture outputting apparatus |

| US10/447,628 US6967665B2 (en) | 2002-05-29 | 2003-05-28 | Picture outputting apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002156273A JP4144258B2 (ja) | 2002-05-29 | 2002-05-29 | 画像出力装置及び画像出力方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003348447A JP2003348447A (ja) | 2003-12-05 |

| JP2003348447A5 JP2003348447A5 (ja) | 2005-04-07 |

| JP4144258B2 true JP4144258B2 (ja) | 2008-09-03 |

Family

ID=29772564

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002156273A Expired - Fee Related JP4144258B2 (ja) | 2002-05-29 | 2002-05-29 | 画像出力装置及び画像出力方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6967665B2 (ja) |

| JP (1) | JP4144258B2 (ja) |

| TW (1) | TWI229285B (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101120589A (zh) * | 2005-01-18 | 2008-02-06 | 松下电器产业株式会社 | 图像合成装置 |

| US8659704B2 (en) * | 2005-12-20 | 2014-02-25 | Savant Systems, Llc | Apparatus and method for mixing graphics with video images |

| JP2009109742A (ja) * | 2007-10-30 | 2009-05-21 | Sharp Corp | 表示装置及び表示方法 |

| US8072392B2 (en) * | 2007-12-07 | 2011-12-06 | Scenera Technologies, Llc | Integrated display system for a computer and a portable device |

| JP2010287983A (ja) * | 2009-06-10 | 2010-12-24 | Casio Computer Co Ltd | 撮像装置、画像処理方法及びプログラム |

| CN101742221B (zh) * | 2009-11-09 | 2012-06-13 | 中兴通讯股份有限公司 | 一种会议电视系统中的多画面合成方法及装置 |

| CN107094258B (zh) | 2011-02-22 | 2020-02-14 | 太阳专利托管公司 | 图像解码方法及图像解码装置 |

| HUE038308T2 (hu) | 2011-02-22 | 2018-10-29 | Tagivan Ii Llc | Szûrési eljárás, dinamikus képkódoló berendezés, dinamikus képdekódoló berendezés, dinamikus kép kódoló/dekódoló berendezés |

| HUE049204T2 (hu) | 2011-07-19 | 2020-09-28 | Tagivan Ii Llc | Szûrési eljárás, mozgókép dekódoló eljárás, mozgókép kódoló eljárás, mozgókép dekódoló berendezés, mozgókép kódoló berendezés, mozgókép kódoló/dekódoló berendezés |

| JP5968533B2 (ja) * | 2013-05-31 | 2016-08-10 | 三菱電機株式会社 | 画像処理装置、画像処理システム及び画像処理方法 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6567091B2 (en) * | 2000-02-01 | 2003-05-20 | Interactive Silicon, Inc. | Video controller system with object display lists |

-

2002

- 2002-05-29 JP JP2002156273A patent/JP4144258B2/ja not_active Expired - Fee Related

-

2003

- 2003-05-14 TW TW92113110A patent/TWI229285B/zh not_active IP Right Cessation

- 2003-05-28 US US10/447,628 patent/US6967665B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003348447A (ja) | 2003-12-05 |

| TW200400461A (en) | 2004-01-01 |

| US20040032416A1 (en) | 2004-02-19 |

| US6967665B2 (en) | 2005-11-22 |

| TWI229285B (en) | 2005-03-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8698840B2 (en) | Method and apparatus for processing video and graphics data to create a composite output image having independent and separate layers of video and graphics display planes | |

| US6763175B1 (en) | Flexible video editing architecture with software video effect filter components | |

| US8306399B1 (en) | Real-time video editing architecture | |

| EP2300991B1 (en) | Image processing device, method, and system | |

| US8922622B2 (en) | Image processing device, image processing method, and program | |

| JP2000330507A (ja) | 投射型表示装置 | |

| US6763176B1 (en) | Method and apparatus for real-time video editing using a graphics processor | |

| EP1872358A2 (en) | Display specific image processing in an integrated circuit | |

| US7623140B1 (en) | Method and apparatus for processing video and graphics data to create a composite output image having independent and separate layers of video and graphics | |

| JP4144258B2 (ja) | 画像出力装置及び画像出力方法 | |

| JP2007214659A (ja) | Osd装置 | |

| JPH1042204A (ja) | 映像信号処理装置 | |

| US7876996B1 (en) | Method and system for time-shifting video | |

| JP2010152518A (ja) | 画像処理装置及び画像処理方法 | |

| JP2006303631A (ja) | オンスクリーン表示装置及びオンスクリーンディスプレイ生成方法 | |

| JP2006301029A (ja) | オンスクリーン表示装置及びオンスクリーンディスプレイ生成方法 | |

| JP2003283925A (ja) | 画像合成装置及び方法 | |

| US20050057565A1 (en) | Information processing apparatus, semiconductor device for display control and video stream data display control method | |

| WO2020213366A1 (ja) | 画像生成装置および画像生成方法 | |

| JP3420151B2 (ja) | 画像処理装置 | |

| JP2005086822A (ja) | ビデオ・データおよびグラフィックス・データ処理用装置 | |

| KR20240123645A (ko) | 외부 장치에 표시하기 위한 비디오를 처리하는 전자 장치, 그 제어 방법, 및 그 기록 매체 | |

| KR100744519B1 (ko) | 온 스크린 디스플레이 스케일링 장치 및 그 방법 | |

| JP2004355013A (ja) | 映像表示装置 | |

| JPH05134640A (ja) | マルチメデイア用フレームバツフア |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040428 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040428 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060825 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060905 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061102 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061205 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070205 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080428 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080527 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080609 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110627 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120627 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130627 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |