JP4071910B2 - 半導体集積回路 - Google Patents

半導体集積回路 Download PDFInfo

- Publication number

- JP4071910B2 JP4071910B2 JP35054199A JP35054199A JP4071910B2 JP 4071910 B2 JP4071910 B2 JP 4071910B2 JP 35054199 A JP35054199 A JP 35054199A JP 35054199 A JP35054199 A JP 35054199A JP 4071910 B2 JP4071910 B2 JP 4071910B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- semiconductor integrated

- integrated circuit

- data

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4093—Input/output [I/O] data interface arrangements, e.g. data buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1072—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers for memories with random access ports synchronised on clock signal pulse trains, e.g. synchronous memories, self timed memories

Description

【発明の属する技術分野】

本発明は、外部とのデータの受け渡しを直列データで行い、メモリセルへのデータの読み書きを並列データで行う半導体集積回路に関し、特に、データ変換を高速に行う技術に関する。

【0002】

【従来の技術】

クロック信号等に同期して入出力インタフェースを高速に動作させ、データ信号の入出力を高速にした半導体集積回路として、SDRAM(synchronous DRAM)等が知られている。SDRAMは、外部とのデータの受け渡しを直列に行い、メモリセルへのデータの読み書きを並列に行うことで、データ転送速度を向上している。

【0003】

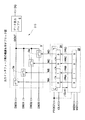

図7は、この種のSDRAMの出力インタフェース部の概要を示している。

出力インタフェース部1は、データセレクタ2、並列直列変換器3、シフトレジスタ4、およびデータ出力バッファ5を有している。この出力インタフェース部1は、シフトレジスタ4を除き、複数のデータ入出力端子DQ毎にそれぞれ形成されている。

【0004】

データセレクタ2は、CMOS伝達ゲート等からなる4つのスイッチ2aで構成されている。各スイッチ2aは、図示しないメモリセルから読み出されるデータ信号DB0-DB3を受け、受けた信号のいずれかを、アドレス信号AD0、AD1に応じてデータ信号DBS0(またはDBS1、DBS2、DBS3)として伝達する。この図のデータセレクタ2では、アドレス信号AD0、AD1が2進数の“10”のときのスイッチの接続状態を示している。

【0005】

並列直列変換回路3は、CMOS伝達ゲート等からなる4つのスイッチ3aで構成されている。各スイッチ3aは、接続信号NA、NB、NC、NDの活性化に応じてオンし、データ信号DBS0-DBS3をそれぞれデータ出力信号DOUTとして伝達する。

シフトレジスタ4は、クロック信号CLKに同期してシフト動作し、接続信号NA、NB、NC、NDを、この順序で活性化する。

【0006】

データ出力バッファ5は、データ出力信号DOUTに伝達される直列の読み出しデータをデータ入出力端子DQに出力する。

このSDRAMでは、読み出し動作時に、外部から供給される下位のアドレス信号AD0、AD1に応じて、データ信号DBS0-DBS3の出力順序が決められる。このようにメモリセルから並列に読み出されるデータを連続して出力する動作モードは、一般にバースト出力モードと称されている。

【0007】

図8は、上述したSDRAMの読み出し動作の一例を示している。

まず、SDRAMは、サイクル1のクロック信号CLKに同期して読み出しコマンドREAD1およびアドレス信号を取り込み、読み出し動作を開始する。この例では、読み出しコマンドREAD1とともに供給されるアドレス信号AD0、AD1は、2進数の“10”にされている。

【0008】

図7に示したデータセレクタ2は、アドレス信号AD0、AD1を受け、各スイッチ2aを接続する。メモリセルから読み出されたデータ信号DB0、DB1、DB2、DB3は、データセレクタ2を介して、それぞれデータ信号DBS2、DBS3、DBS0、DBS1として伝達される。

シフトレジスタ4は、サイクル3、4、5、6のクロック信号CLKに同期して、接続信号NA、NB、NC、NDをそれぞれ活性化する。

【0009】

並列直列変換回路3のスイッチ3aは、接続信号NA、NB、NC、NDを受けて、データ信号DBS2、DBS3、DBS0、DBS1を順次にデータ出力信号DOUTとして出力する。そして、直列のデータ出力信号DOUTが、データ出力バッファ5を介してデータ入出力端子DQに出力される。すなわち、アドレス信号AD0、AD1が“10”の場合、データ信号DB2、DB3、DB0、DB1の順で出力される(4ビットバースト出力)。

【0010】

また、SDRAMは、サイクル5のクロック信号CLKに同期して、次の読み出しコマンドREAD2およびアドレス信号AD0、AD1(2進数の“00”)を取り込む。

データセレクタ2は、アドレス信号AD0、AD1に応じて各スイッチ2aを切り替える。そして、メモリセルから読み出されたデータ信号DB0、DB1、DB2、DB3は、データセレクタ2を介して、それぞれデータ信号DBS0、DBS1、DBS2、DBS3として伝達される。並列直列変換回路3は、順次に活性化される接続信号NA、NB、NC、NDに同期して、データ信号DBS0、DBS1、DBS2、DBS3を直列のデータ出力信号DOUTとして出力する。

【0011】

そして、直列のデータ出力信号DOUTが、データ出力バッファ5を介してデータ入出力端子DQに出力される。すなわち、アドレス信号AD0、AD1が“00”の場合、データ信号DB0、DB1、DB2、DB3の順に出力される。

さらに、次の読み出しコマンドREAD3では、アドレス信号AD0、AD1(2進数の“11”)に応じて、読み出しデータは、データ信号DB3、DB0、DB1、DB2の順でデータ入出力端子DQに出力される。

【0012】

【発明が解決しようとする課題】

ところで、上述した出力インタフェース部1では、データ信号DB0-DB3は、データセレクタ2および並列直列変換回路3の両方で制御された後、外部に出力される。このため、SDRAMのタイミング設計時に、データセレクタ2および並列直列変換回路3の両方のタイミングマージンを考慮する必要があった。

【0013】

また、データ信号DB0-DB3は、2つのスイッチ2a、3aを介して外部に出力される。このため、これ等スイッチ2a、3aの伝搬遅延時間だけデータ信号を出力が遅れてしまう。

このように、従来のSDRAMでは、出力インタフェース部1が、メモリセルから読み出された読み出しデータのデータ転送速度を低下させる要因の一つになっていた。本来、SDRAMは、入出力インタフェースを高速に動作させることを特徴としている。このため、出力インタフェース部1は、メモリセルから読み出される読み出しデータを、できる限り高速に伝達する必要がある。

【0014】

本発明の目的は、メモリセルから読み出されるデータを高速に伝達することにある。

本発明の別の目的は、メモリセルを有する半導体集積回路の読み出し動作を高速に実行することにある。

本発明の別の目的は、メモリセルを有するクロック同期式の半導体集積回路の読み出し動作を高速に実行することにある。

【0015】

本発明の別の目的は、並列の読み出しデータの直列への変換を簡易な回路で制御することにある。

本発明の別の目的は、メモリセルを有する半導体集積回路の書き込み動作を高速に実行することにある。

【0016】

【課題を解決するための手段】

本発明の半導体集積回路は、メモリセルから読み出される並列データを直列データに変換する並列直列変換器と、アドレス信号を受け、並列直列変換器を制御するスイッチ制御回路とを備えている。並列直列変換器は、所定の順序で接続する複数のスイッチを有している。スイッチ制御回路は、アドレス信号に応じてスイッチの接続順序を制御し、並列データは、所定の順序で直列データに変換される。具体的には、スイッチ制御回路は、各記憶段の出力がスイッチに接続されたシフトレジスタを備えている。シフトレジスタの初期値は、アドレス信号に応じて設定される。そして、シフトレジスタをシフト動作することで、各スイッチが所定の順序で接続される。

【0017】

このため、並列データの伝送経路上に形成される遅延要素を最小限にできる。具体的には、例えば、並列データを並び替えるための変換回路が不要になる。すなわち、簡単な回路で直列データの並び順を制御できる。この結果、メモリセルからのデータの読み出し動作が高速になる。また、回路が簡単なため、タイミング設計、レイアウト設計が容易になる。また、アドレス信号は、メモリセルの読み出しコマンドに対応して外部から供給される。このため、直列データの並び順を読み出し動作毎にリアルタイムで変更することができる。

【0018】

本発明の半導体集積回路では、並列直列変換器が変換した直列データは、出力回路を介して外部に出力される。このため、例えば、バースト出力機能を有する半導体集積回路において、読み出し動作をさらに高速にできる。

本発明の半導体集積回路では、並列直列変換器の各スイッチは、外部から供給されるクロック信号に同期して動作する。このため、例えば、メモリセルを有するクロック同期式の半導体集積回路において、読み出し動作を高速にできる。

【0019】

本発明の半導体集積回路では、所定のメモリセルを選択するアドレス信号により、直列データの並び順が変更される。例えば、1ビットのアドレス信号を使用することで、2ビットの並列データを所定の並び順の直列データに変換できる。2ビットのアドレス信号を使用することで、4ビットの並列データを所定の並び順の直列データに変換できる。すなわち、バースト出力機能を有する半導体集積回路において、アクセス時間を遅らせることなく出力データを所定の並び順に変換できる。

【0022】

本発明の半導体集積回路では、シフトレジスタは、反転信号を受けてシフト方向を反転する。このため、同じシフトレジスタを使用して、異なる並び順の直列データを生成することができる。例えば、シフト方向を反転することでインタリーブモードを容易に適用できる。

【0023】

このため、並列データの伝送経路上に形成される遅延要素を最小限にできる。具体的には、例えば、並列データを並び替えるための変換回路が不要になる。この結果、メモリセルからのデータの書き込み動作が高速になる。

【0024】

【発明の実施の形態】

以下、本発明の実施形態を図面を用いて説明する。

【0025】

図1は、本発明の半導体記憶装置の第1の実施形態を示している。なお、従来技術で説明した回路と同一の回路については、同一の符号を付し、これ等回路については、詳細な説明を省略する。また、以降の説明では、“アドレス信号AD”を“AD信号”のように、信号名を略して称する場合がある。信号名に“/”が付く信号は、負論理の信号である。各図面において太線で示した信号線は、複数本で構成されていることを示している。また、太線が接続されたブロックの一部は、複数の回路で構成されている。

【0026】

この実施形態の半導体集積回路は、シリコン基板上に、CMOSプロセス技術を使用して、SDRAMとして形成されている。SDRAMは、入出力制御部10、メモリ制御部12、メモリコア14を有している。

入出力制御部10は、クロックバッファ16、入力バッファ18a、18b、コマンドデコーダ20、アドレスデコーダ22、シフトレジスタ24、データ出力バッファ5、データ入力バッファ26、並列直列変換器3、および直列並列変換器28を有している。ここで、アドレスデコーダ22、シフトレジスタ24、データ出力バッファ5、および並列直列変換器3は、出力インタフェース部30として構成されている。並列直列変換回路3およびデータ出力バッファ5は、図7と同一の回路である。

【0027】

図2は、本発明の要部である出力インタフェース部30の概要を示している。

並列直列変換回路3は、複数のスイッチ3aを有している。アドレスデコーダ22およびシフトレジスタ24は、並列直列変換回路3の制御回路として動作する。

アドレスデコーダ22は、読み出し制御信号PTOEZのLレベル時に活性化され、内部クロック信号/CLK1のLレベルを受けて非活性化される。アドレスデコーダ22は、内部アドレス信号IAD1、IAD0をデコードし、プリセット信号/PRA、/PRB、/PRC、/PRDのいずれかをLレベルにする。

【0028】

シフトレジスタ24は、内部クロック信号ICLKに同期してシフト動作する4ビットの記憶段24aを有している。最終段の情報は、初段に帰還されている。シフトレジスタ24の各記憶段24aは、各スイッチ3aを制御する接続信号NA、NB、NC、NDを出力している。また、各記憶段24aは、プリセット信号/PRA 、 /PRB 、 /PRC 、 /PRDでプリセットされる。すなわち、シフトレジスタ24は、外部から供給されるアドレス信号に応じて初期化される。シフトレジスタ24は、シフト動作毎に、接続信号NA、NB、NC、NDを順次に活性化する。

【0029】

そして、並列直列変換回路3は、CLK信号に同期した接続信号NA、NB、NC、NDを各スイッチ3aでそれぞれ受け、メモリセルMCから読み出される並列のデータ出力信号DBO0-DBO3を直列のデータ出力信号DOUTに変換する。

また、図1に示したように、クロックバッファ16は、外部からCLK信号を受け、内部クロック信号ICLKを出力している。ICLK信号は、図示した以外にも主要な回路に供給されている。入力バッファ18aは、ICLK信号に同期してコマンド信号CMDを取り込み、取り込んだ信号を、内部コマンド信号ICMDとして出力している。

【0030】

入力バッファ18bは、ICLK信号に同期してアドレス信号ADを取り込み、取り込んだ信号を内部アドレス信号IADとして出力している。

コマンドデコーダ20は、内部コマンド信号ICMDを受けてコマンドを解読し、チップの基本動作を制御する制御信号を出力している。ここで、読み出し制御信号PTOEZは、読み出し動作に対応するコマンド信号CMDが供給されたときに、所定の期間活性化(Hレベル)される。

【0031】

アドレスデコーダ22は、上述したように、/CLK1信号、PTOEZ信号、IAD0、IAD1信号を受け、プリセット信号/PRA、/PRB、/PRC、/PRDを出力している。

シフトレジスタ24は、ICLK信号、PTOEZ信号、およびプリセット信号/PRA、/PRB、/PRC、/PRDを受け、/CLK1信号および接続信号NA、NB、NC、NDを出力している。

【0032】

データ出力バッファ5は、読み出し動作時に、並列直列変換回路3から直列のデータ出力信号DOUTを受け、受けたデータをデータ入出力端子DQに出力している。データ入力バッファ26は、書き込み動作時に、データ入出力端子DQを介して書き込みデータを受け、受けたデータをデータ入力信号DINとして直列並列変換回路28に出力している。

【0033】

並列直列変換回路3は、メモリ制御部12から伝達される並列のデータ出力信号DBOを、直列のDOUT信号として出力している。直列並列変換器28は、データ入力バッファ26から伝達される直列のデータ入力信号DINを並列データに変換し、データ入力信号DBIとして出力している。

【0034】

なお、この実施形態では、16個のデータ入出力端子DQを有している。このため、データ出力バッファ5、データ入力バッファ26、並列直列変換回路3、直列並列変換回路28は、各端子DQ毎にそれぞれ形成されている。

メモリ制御部12は、入出力制御回路32を有している。メモリ制御部12は、その他にタイミング信号生成器34、アドレスデコーダ36等の制御回路を有している。

【0035】

メモリコア14は、複数のメモリセルMCが縦横に配置されたメモリセルアレイ38を有している。各メモリセルMCは、ワード線WLおよびビット線BL(/BL)に接続されている。メモリコア14は、その他にセンスアンプ40、ビット線用のプリチャージ回路42等の制御回路を有している。

図3は、アドレスデコーダ22およびシフトレジスタ24の詳細を示している。

【0036】

アドレスデコーダ22は、デコード回路22aと、このデコード回路22aを制御する制御回路22bとで構成されている。

デコード回路22aは、4つのNANDゲートおよび2つのインバータで構成されている。デコード回路22aは、制御回路22bの出力OUT1がHレベルのとき活性化され、IAD1、IAD0信号が“00”のときプリセット信号/PRAのみをLレベルに変化する。同様に、IAD1、IAD信号0が“01”、“10”、“11”のとき、プリセット信号/PRB、/PRC、/PRDのみが、それぞれLレベルに変化される。

【0037】

制御回路22bは、RSフリップフロップと、このフリップフロップの出力を受けるバッファとで構成されている。制御回路は22bの出力OUT1は、PTOEZ信号のLレベル時にHレベルになり、その後、/ICLK信号のLレベルを受けてLレベルになる。

シフトレジスタ24は、上述した4つの記憶段24aと、PTOEZ信号のHレベル時に、ICLK信号から/CLK1信号、CLK1信号を生成するNANDゲートおよびインバータとで構成されている。

【0038】

各記憶段24aは、内部クロック端子CLK1、/CLK1、読み出し制御端子OE、入力端子RIN、プリセット端子/PR、出力端子ROUT、データ出力端子DNを有している。各入力端子は、それぞれCLK1信号、/CLK1信号、PTOEZ信号、前段の出力信号、プリセット信号/PRB(または/PRC、/PRD、/PRA)を受け、各出力端子は、後段への出力信号および接続信号NA(またはNB、NC、ND)を出力している。換言すれば、/PRA信号は最終段に、/PRB信号は初段に、/PRC信号は第2段に、/PRD信号は第3段に供給されている。

【0039】

図4は、記憶段24aの詳細を示している。

記憶段24aは、入力端子RINおよびプリセット端子/PRを受けるNANDゲート24bと、NANDゲート24bの出力を帰還するクロックドインバータ24cと、クロックドインバータ24cの出力をデータ出力端子DNに伝達するインバータ24dと、インバータ24dの入力ノードにドレインを接続したpMOSトランジスタ24eと、NANDゲート24bの出力信号を出力端子ROUTに伝達するCMOS伝達ゲート24f、ラッチ24g、CMOS伝達ゲート24hとで構成されている。

【0040】

クロックドインバータ24cは、CLK1信号がLレベル、/CLK1信号がHレベル、PTOEZ信号がHレベルのとき活性化される。pMOSトランジスタ24eは、ゲートにPTOEZ信号を受け、ソースに電源電圧VIIを受けている。CMOS伝達ゲート24f、24hは、それぞれCLK1信号がLレベル、Hレベルのときオンする。ラッチ24gは、2つのインバータの入力と出力とを互いに接続して形成されている。

【0041】

図5は、上述したSDRAMの読み出し動作の例を示している。

まず、SDRAMは、サイクル1のCLK信号の立ち上がりエッジに同期して読み出しコマンドREADおよびアドレス信号を取り込み、読み出し動作を開始する。この例では、読み出しコマンドREADとともに供給されるAD0、AD信号1は、2進数の“01”にされている(図5(a))。

【0042】

図3に示したアドレスデコーダ22は、PTOEZ信号のLレベルを受けてデコード回路22aを活性化する。そして、デコード結果を/PRA信号、/PRB信号、/PRC信号、/PRD信号として出力する(図5(b))。この例では、/PRB信号のみがLレベルになる。/PRA信号、/PRB信号、/PRC信号、/PRD信号は、シフトレジスタ24の各記憶段24aのプリセット端子/PRにそれぞれ供給される。

【0043】

各記憶段24a(図4)のCMOS伝達ゲート24fは、CLK1信号、/CLK1信号のLレベル、Hレベルを受けてオンし、ラッチ24gに/PRB信号、/PRC信号、/PRD信号、/PRA信号をそれぞれ保持する。この例では、シフトレジスタ24の各記憶段24aのうち、初段のラッチ24gの出力のみLレベルを出力する。

また、各記憶段24aは、CMOS伝達ゲート24hをオフしている。各記憶段24aは、PTOEZ信号のLレベルを受けてpMOSトランジスタ24eをオンし、LレベルのNA、NB、NC、ND信号を出力している(図5(c))。記憶段24aのクロックドインバータ24cは、CLK1信号のLレベルおよび/CLK1信号のHレベルを受けて非活性化されている。

【0044】

次に、図1に示したコマンドデコーダ20は、CMD信号を解読し、PTOEZ信号を活性化(Hレベル)する(図5(d))。シフトレジスタ24の各記憶段24aは、PTOEZ信号のHレベルを受け、pMOSトランジスタ24eをオフする。

図3に示したシフトレジスタ24は、PTOEZ信号の活性化を受け、/CLK1信号、CLK1信号の生成を開始する(図5(e))。

【0045】

CMOS伝達ゲート24fは、CLK1信号、/CLK1信号のHレベル、Lレベルを受けオフする。同時に、CMOS伝達ゲート24fはオンする。そして、シフトレジスタの各記憶段24aは、前段のラッチ24gに保持されているデータを受けて、その反転データをNA、NB、NC、ND信号として出力する。この結果、サイクル3では、NB信号のみがHレベルに変化する(図5(f))。

【0046】

そして、図2に示した並列直列変換回路3のNB信号に対応するスイッチ3aがオンし、メモリセルから読み出されたDBO1信号は、DOUT信号として出力される(図5(g))。DBO1信号は1つのスイッチ3aのみを介して伝達されるため、その伝達速度は従来に比べ向上する。また、DBO1信号の伝達経路に形成される制御回路は、少ないため、タイミング設計が容易になり、タイミングマージンが向上する。

【0047】

アドレスデコーダ22は、/CLK1信号の立ち下がりエッジを受け、デコード回路22aを非活性化し、/PRA信号、/PRB信号、/PRC信号、/PRD信号を全てHレベルに変化する(図5(h))。

この後、サイクル3において、CLK1信号が立ち下がり、/CLK1信号が立ち上がる。図4に示した記憶段24aは、CMOS伝達ゲート24fをオンし、CMOS伝達ゲート24hをオフする。同時に、クロックドインバータ24cがオンし、インバータ24dを介してNA信号(または、NB、NC、ND信号)を出力する。

【0048】

次に、サイクル4において、CLK1信号が立ち上がり、/CLK1信号が立ち下がる。シフトレジスタ24の各記憶段24aは、前段からのデータを反転し、NA信号、NB信号、NC信号、ND信号として出力する。(図5(i))このとき、クロックドインバータ24cはオフしている。

そして、サイクル3と同様にして、DBO2信号は、DOUT信号として出力される(図5(j))。この後、サイクル5およびサイクル6において、上述と同様にシフトレジスタ24が動作し、DOUT信号が出力される(図5(k))。

【0049】

SDRAMは、連続する4ビットのデータを読み出した後、PTOEZ信号を非活性化(Lレベル)する(図5(l))。シフトレジスタ24は、PTOEZ信号の非活性化を受け、/CLK1信号、CLK1信号の生成を停止する(図5(m))。アドレスデコーダ22はPTOEZ信号のLレベルを受けてデコード回路22aを活性化し、次の読み出しコマンドのAD0信号、AD1信号が供給されるのを待つ(図5(n))。

【0050】

以上、本発明の半導体記憶装置では、シフトレジスタ24のシフト動作により、並列直列変換器3の各スイッチ3aの接続を制御した。このため、並列のデータ出力信号DBO0-DBO3の伝送経路上に形成される遅延要素を最小限にして、この並列データを所定の並び順の直列データに変換できる。この結果、メモリセルMCからのデータの読み出し動作が高速になる。

【0051】

並列直列変換器3が変換した直列のDOUT信号を、データ出力バッファ5を介して外部に出力した。このため、SDRAMのバースト出力モード時に、読み出しデータの伝達をさらに高速にできる。

並列直列変換器3の各記憶段3aを、外部から供給されるCLK信号に同期して動作させた。このため、クロック同期式のSDRAMの読み出し動作を高速にできる。

【0052】

外部から供給されるAD1、AD0信号に応じて、シフトレジスタ24の初期値を設定した。このため、直列データの並び順を読み出し動作毎にリアルタイムで設定することができる。

また、直列データの並び順をAD1、AD0信号に応じて設定した。このため、4ビットの並列データを所定の並び順の直列データに変換できる。すなわち、SDRAMのバースト出力モード時に、アクセス時間を遅らせることなく出力データを所定の並び順に変換できる。

【0053】

各記憶段24aの出力をスイッチ3aに接続したシフトレジスタ24と、このシフトレジスタ24をプリセット(初期値を設定)するアドレスデコーダ22とを形成した。このため、簡単な回路で直列データの並び順を制御できる。また、回路が簡単なため、タイミング設計、レイアウト設計が容易になる。

図6は、本発明の半導体記憶装置の第2の実施形態における出力インタフェース部を示している。なお、第1の実施形態で説明した回路と同一の回路については、同一の符号を付し、これ等回路については、詳細な説明を省略する。

【0054】

この実施形態の出力インタフェース部は、シフトレジスタ44が第1の実施形態のシフトレジスタ24と相違している。その他の構成は、第1の実施形態と同一である。

シフトレジスタ44は、反転信号REVにより、シフト方向を変える機能を有している。このシフトレジスタ44により、一般に、インタリーブモードと称する仕様に合わせて、バースト読み出し時に読み出しデータの出力順序を変えることが可能になる。なお、反転信号REVのレベルは、図示しないモードレジスタ等で設定される。

【0055】

この実施形態のSDRAMでは、REV信号がLレベルのとき、第1の実施形態と同一に動作する。REV信号がHレベルのとき、シフトレジスタ44は、図の右から左側にシフト動作する。この結果、読み出し動作において、A1、A0信号に例えば“01”が供給された場合、入出力端子DQには、データ出力信号DBO1、DBO0、DBO3、DBO2の順で読み出しデータが出力される。すなわち、シフトレジスタ44のシフト方向を反転するだけで、インタリーブモードに対応可能なる。

【0056】

この実施形態においても、上述した第1の実施形態と同様の効果を得ることができる。さらに、この実施形態では、インタリーブモードに対応して読み出しデータを出力することができる。従来、インタリーブモードでは、図1に示した入出力制御回路32を複雑なスイッチ制御をしてデータを変換していた。本実施形態では、シフトレジスタ44のシフト方向を反転するだけで、容易にインタリーブモードに対応できる。

【0057】

なお、上述した第1の実施形態では、本発明をメモリセルMCからの読み出しデータを外部に出力するための出力インタフェース部30に適用した例を示した。これに限定されず、本発明を入力インタフェース部に適用してもよい。具体的には、アドレスデコーダおよびシフトレジスタにより直列並列変換器28の変換順序を変えることで、容易に直列の書き込みデータを所定の並列データに変換することができる。すなわち、バースト書き込み動作を高速に実行できる。

【0058】

また、上述した第1の実施形態では、本発明をSDRAMに適用した例について述べた。これに限定されず、本発明をDRAM、SRAM等の半導体メモリに適用してもよい。あるいは、DRAMのメモリコアを内蔵したシステムLSIに適用してもよい。

本発明が適用される半導体製造プロセスは、CMOSプロセスに限定されず、Bi-CMOSプロセスでもよい。

【0059】

以上、本発明について詳細に説明してきたが、上記の実施形態およびその変形例は発明の一例に過ぎず、本発明はこれに限定されるものではない。本発明を逸脱しない範囲で変形可能であることは明らかである。

【0060】

【発明の効果】

本発明の半導体集積回路では、並列データの伝送経路上に形成される遅延要素を最小限にできる。この結果、メモリセルからのデータを高速に伝達でき、読み出し時のアクセス時間を向上することができる。

簡単な回路で直列データの並び順を制御できる。また、回路が簡単なため、タイミング設計、レイアウト設計が容易になる。さらに、直列データの並び順を、読み出し動作毎にリアルタイムで変更することができる。

【0061】

本発明の半導体集積回路では、バースト出力機能を有する半導体集積回路において、読み出し動作をさらに高速にできる。

本発明の半導体集積回路では、メモリセルを有するクロック同期式の半導体集積回路において、読み出し動作を高速にできる。

【0062】

本発明の半導体集積回路では、バースト出力機能を有する半導体集積回路において、アクセス時間を遅らせることなく出力データを所定の並び順に変換できる。

【0063】

本発明の半導体集積回路では、同じシフトレジスタを使用して、異なる並び順の直列データを容易に生成することができる。

【図面の簡単な説明】

【図1】本発明の半導体集積回路の第1の実施形態を示すブロック図である。

【図2】図1の出力インタフェース部の概要を示すブロック図である。

【図3】図1のアドレスデコーダおよびシフトレジスタの詳細を示す回路図である。

【図4】図3の記憶段の詳細を示す回路図である。

【図5】第1の実施形態の読み出し動作を示すタイミング図である。

【図6】本発明の半導体集積回路の第2の実施形態の出力インタフェース部を示すブロック図である。

【図7】従来の出力インタフェース部の概要を示すブロック図である。

【図8】従来の読み出し動作を示すタイミング図である。

【符号の説明】

3 並列直列変換器

5 データ出力バッファ

10 入出力制御部

12 メモリ制御部

14 メモリコア

16 クロックバッファ

18a、18b 入力バッファ部

20 コマンドデコーダ

22 アドレスデコーダ

22a デコード回路

22b 制御回路

24 シフトレジスタ

24a 記憶段

26 データ入力バッファ

28 直列並列変換器

30 出力インタフェース部

32 入出力制御回路

34 タイミング信号生成器

36 アドレスデコーダ

38 メモリセルアレイ

40 センスアンプ

42 プリチャージ回路

44 シフトレジスタ

AD アドレス信号

BL、/BL ビット線

CLK クロック信号

CLK1、/CLK1 内部クロック信号

CMD コマンド信号

DBI データ入力信号

DBO データ出力信号

DIN データ入力信号

DOUT データ出力信号

DQ データ入出力端子

IAD 内部アドレス信号

ICLK 内部クロック信号

ICMD 内部コマンド信号

MC メモリセル

NA、NB、NC、ND 接続信号

PRA、PRB、PRC、PRD プリセット信号

PTOEZ 読み出し制御信号

WL ワード線

Claims (10)

- メモリセルから読み出される並列データを複数のスイッチでそれぞれ受け、該スイッチを順次に接続して該並列データを直列データに変換する並列直列変換器と、

複数の記憶段を有し、前記各記憶段の出力が前記各スイッチにそれぞれ接続されるシフトレジスタと、アドレス信号に応じて前記シフトレジスタの記憶段の一つにプリセット信号を出力する設定回路とを有するスイッチ制御回路とを備え、

前記設定回路は、前記直列データが出力されている期間に非活性化されることを特徴とする半導体集積回路。 - 請求項1記載の半導体集積回路において、

コマンド信号をデコードするコマンドデコーダを備え、

前記設定回路は、前記コマンドデコーダから供給される制御信号により非活性化されることを特徴とする半導体集積回路。 - 請求項2記載の半導体集積回路において、

前記コマンドデコーダは、前記コマンド信号をデコードした後に前記制御信号を出力することを特徴とする半導体集積回路。 - 請求項1乃至請求項3のいずれか1項記載の半導体集積回路において、

前記シフトレジスタの初期値は、前記アドレス信号に応じて設定されることを特徴とする半導体集積回路。 - 請求項1乃至請求項4のいずれか1項記載の半導体集積回路において、

前記アドレス信号は、前記メモリセルの読み出し動作に対応して外部から供給されることを特徴とする半導体集積回路。 - 請求項1乃至請求項5のいずれか1項記載の半導体集積回路において、

前記アドレス信号の所定のビットに基づいて前記並列データの出力順序が決定されることを特徴とする半導体集積回路。 - 請求項1乃至請求項6のいずれか1項記載の半導体集積回路において、

前記並列直列変換器が出力する前記直列データを外部に出力する出力回路を備えたことを特徴とする半導体集積回路。 - 請求項1乃至請求項7のいずれか1項記載の半導体集積回路において、

前記各スイッチは、外部から供給されるクロック信号に同期して動作することを特徴とする半導体集積回路。 - 請求項1乃至請求項8のいずれか1項記載の半導体集積回路において、

前記アドレス信号は、所定の前記メモリセルを選択するために供給されることを特徴とする半導体集積回路。 - 請求項1乃至請求項9のいずれか1項記載の半導体集積回路において、

前記シフトレジスタは、反転信号を受けてシフト方向を反転することを特徴とする半導体集積回路。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP35054199A JP4071910B2 (ja) | 1999-12-09 | 1999-12-09 | 半導体集積回路 |

| TW089116100A TW456031B (en) | 1999-12-09 | 2000-08-10 | Semiconductor integrated circuit |

| US09/635,868 US6343041B1 (en) | 1999-12-09 | 2000-08-10 | Semiconductor integrated circuit |

| US10/028,428 US6438054B1 (en) | 1999-12-09 | 2001-12-28 | Semiconductor integrated circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP35054199A JP4071910B2 (ja) | 1999-12-09 | 1999-12-09 | 半導体集積回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001167575A JP2001167575A (ja) | 2001-06-22 |

| JP2001167575A5 JP2001167575A5 (ja) | 2004-12-02 |

| JP4071910B2 true JP4071910B2 (ja) | 2008-04-02 |

Family

ID=18411196

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP35054199A Expired - Lifetime JP4071910B2 (ja) | 1999-12-09 | 1999-12-09 | 半導体集積回路 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US6343041B1 (ja) |

| JP (1) | JP4071910B2 (ja) |

| TW (1) | TW456031B (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6825698B2 (en) | 2001-08-29 | 2004-11-30 | Altera Corporation | Programmable high speed I/O interface |

| WO1996024138A1 (fr) * | 1995-01-31 | 1996-08-08 | Hitachi, Ltd. | Dispositif de memoire remanente et procede de regeneration |

| JP4071910B2 (ja) * | 1999-12-09 | 2008-04-02 | 富士通株式会社 | 半導体集積回路 |

| JP3848038B2 (ja) * | 2000-01-12 | 2006-11-22 | 株式会社日立製作所 | 半導体集積回路 |

| JP4612139B2 (ja) * | 2000-02-08 | 2011-01-12 | 富士通セミコンダクター株式会社 | 入力回路及びその入力回路を利用する半導体装置 |

| US7120761B2 (en) | 2000-12-20 | 2006-10-10 | Fujitsu Limited | Multi-port memory based on DRAM core |

| US6549444B2 (en) * | 2001-04-12 | 2003-04-15 | Samsung Electronics Co., Ltd. | Memory device with prefetched data ordering distributed in prefetched data path logic, circuit, and method of ordering prefetched data |

| JP3717912B2 (ja) * | 2003-11-06 | 2005-11-16 | 沖電気工業株式会社 | インタリーブ装置 |

| DE102004014973B3 (de) * | 2004-03-26 | 2005-11-03 | Infineon Technologies Ag | Parallel-Seriell-Umsetzer |

| JP2005326203A (ja) * | 2004-05-13 | 2005-11-24 | Matsushita Electric Ind Co Ltd | 半導体集積回路の実速度検査方法 |

| JP2006277872A (ja) * | 2005-03-30 | 2006-10-12 | Elpida Memory Inc | 半導体記憶装置及びそのテスト方法 |

| US7444453B2 (en) * | 2006-01-03 | 2008-10-28 | International Business Machines Corporation | Address translation device |

| US20080288684A1 (en) * | 2006-01-03 | 2008-11-20 | Ellison Brandon J | Design structure for an address translation device |

| JP5410075B2 (ja) * | 2008-11-11 | 2014-02-05 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置および遅延路の制御方法 |

| JP2011108300A (ja) * | 2009-11-13 | 2011-06-02 | Elpida Memory Inc | 半導体装置及びその制御方法並びに半導体装置を備えたデータ処理システム |

| KR101326628B1 (ko) * | 2010-12-02 | 2013-11-07 | 주식회사 엘지화학 | 신규한 노칭 장치 및 이를 사용하여 생산되는 이차전지 |

| JP6170596B1 (ja) * | 2016-06-15 | 2017-07-26 | ウィンボンド エレクトロニクス コーポレーション | 半導体装置 |

| US10170166B1 (en) * | 2017-09-08 | 2019-01-01 | Winbond Electronics Corp. | Data transmission apparatus for memory and data transmission method thereof |

| US10366742B1 (en) | 2018-02-07 | 2019-07-30 | Micron Technology, Inc. | Memory device parallelizer |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2376572A1 (fr) * | 1976-12-30 | 1978-07-28 | Roche Alain | Circuits de conversion serie-parallele et de multiplexage ou de conversion parallele-serie et de demultiplexage pour des multiplex numeriques |

| JPS59221741A (ja) | 1983-05-31 | 1984-12-13 | Sanyo Electric Co Ltd | 記憶用半導体装置 |

| JPS6282417A (ja) | 1985-10-07 | 1987-04-15 | Casio Comput Co Ltd | スイツチ検出回路 |

| JP2000067577A (ja) * | 1998-06-10 | 2000-03-03 | Mitsubishi Electric Corp | 同期型半導体記憶装置 |

| JP2000163965A (ja) * | 1998-11-27 | 2000-06-16 | Mitsubishi Electric Corp | 同期型半導体記憶装置 |

| JP4071910B2 (ja) * | 1999-12-09 | 2008-04-02 | 富士通株式会社 | 半導体集積回路 |

-

1999

- 1999-12-09 JP JP35054199A patent/JP4071910B2/ja not_active Expired - Lifetime

-

2000

- 2000-08-10 US US09/635,868 patent/US6343041B1/en not_active Expired - Lifetime

- 2000-08-10 TW TW089116100A patent/TW456031B/zh not_active IP Right Cessation

-

2001

- 2001-12-28 US US10/028,428 patent/US6438054B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001167575A (ja) | 2001-06-22 |

| TW456031B (en) | 2001-09-21 |

| US6438054B1 (en) | 2002-08-20 |

| US6343041B1 (en) | 2002-01-29 |

| US20020057614A1 (en) | 2002-05-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4071910B2 (ja) | 半導体集積回路 | |

| US6510095B1 (en) | Semiconductor memory device for operating in synchronization with edge of clock signal | |

| US7355899B2 (en) | Pipe latch circuit of multi-bit prefetch-type semiconductor memory device with improved structure | |

| JP3183321B2 (ja) | 半導体記憶装置 | |

| JP4370507B2 (ja) | 半導体集積回路装置 | |

| US7613069B2 (en) | Address latch circuit of semiconductor memory device | |

| JP2000173264A (ja) | ウェ―ブパイプラインスキムを備える同期型半導体メモリ装置及びそれのデ―タパス制御方法 | |

| US6252804B1 (en) | Semiconductor integrated circuit, and method of controlling same | |

| JP4439033B2 (ja) | 半導体記憶装置 | |

| US11467965B2 (en) | Processing-in-memory (PIM) device | |

| JP2001035154A (ja) | パイプラッチ回路を有するメモリ素子におけるデータ出力装置 | |

| JP4145984B2 (ja) | 半導体記憶装置 | |

| US6292430B1 (en) | Synchronous semiconductor memory device | |

| US8068383B2 (en) | Semiconductor integrated circuit having address control circuit | |

| US7835218B2 (en) | Semiconductor integrated circuit including bank selection control block | |

| US6504767B1 (en) | Double data rate memory device having output data path with different number of latches | |

| US20030026152A1 (en) | Semiconductor memory | |

| US7643355B2 (en) | Semiconductor memory device and method of inputting/outputting data | |

| JP4594470B2 (ja) | 半導体集積回路 | |

| JPH09180443A (ja) | 半導体メモリ回路 | |

| JP2011019189A (ja) | 半導体集積回路 | |

| JPH06267279A (ja) | 半導体記憶装置 | |

| JPH07326189A (ja) | 半導体記憶装置 | |

| JP2003115190A (ja) | 半導体メモリ | |

| JP2011146944A (ja) | プログラマブルデバイス回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20031216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20031216 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20061018 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061031 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071009 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071207 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080115 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080118 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4071910 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110125 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110125 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110125 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120125 Year of fee payment: 4 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120125 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130125 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140125 Year of fee payment: 6 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |