JP4035519B2 - 半導体圧力センサおよびその製造方法 - Google Patents

半導体圧力センサおよびその製造方法 Download PDFInfo

- Publication number

- JP4035519B2 JP4035519B2 JP2004176853A JP2004176853A JP4035519B2 JP 4035519 B2 JP4035519 B2 JP 4035519B2 JP 2004176853 A JP2004176853 A JP 2004176853A JP 2004176853 A JP2004176853 A JP 2004176853A JP 4035519 B2 JP4035519 B2 JP 4035519B2

- Authority

- JP

- Japan

- Prior art keywords

- diaphragm

- pressure sensor

- semiconductor pressure

- semiconductor

- piezoresistive elements

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

前記歪み検出素子の少なくとも1つは、前記ダイヤフラム部に第1の端部を有し、該第1の端部と前記ダイヤフラム部のエッジ間の距離をLXとしたとき、LX≦20μmとなるように、前記ダイヤフラム部の内側と外側とに跨って配置されていることを特徴とする。

前記半導体基板に前記歪み検出素子を形成する工程と、

前記半導体基板に前記ダイヤフラム部を形成する工程とを有し、

前記歪み検出素子の少なくとも1つを、前記ダイヤフラム部1に第1の端部を有し、該第1の端部と前記ダイヤフラム部のエッジ間の距離をLXとしたとき、LX≦20μmとなるように、前記ダイヤフラム部の内側と外側とに跨って配置することを特徴とする。

R(L)=R(Leff)+R(L−Leff)・・・(1)

で表される。

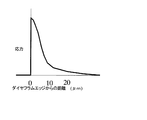

ΔR/R=Aπρ・・・(2)

と表すことができる。ここで、ΔRは抵抗変化分、Rは応力がかかる前の抵抗値、Aは定

数、ρは圧力である。応力分布がダイヤフラム3内の実効長さLeff部分のみにある場合は、全長Lの抵抗体の抵抗変化率は、

ΔR(Leff)/R(Leff)=A∫πρ(X,Y,Z)dxdydz・・・(3)

となる。

ΔR/R=R(Leff)A∫πρ(X,Y,Z)dxdydz/R(L)・・・(4)

となる。式(4)から、Leffが大きいほど抵抗変化が大きくなり、感度が高くなる。このことから、感度を高くするためには、この応力集中した位置にピエゾ抵抗素子R1,R3を配置することが重要である。

0.5<Leff/L<1・・・(5)

なる関係を満たす位置に配置すると、高感度化が促進される。

L=2L0+L1…(6)

で表される。また、実効長さLeffは、折り返し部が形成されているためダイヤフラム13のエッジを跨ぐ方向成分を有する箇所は2箇所あり、その和として、

Leff=2LX…(7)

で表される。

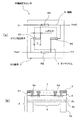

本実施例では、図1に示した直線型のピエゾ抵抗素子R1〜R4を有する半導体圧力センサ1を作製した。半導体基板はSOI基板2であり、n型で1×1016/cm3のリンが注入されている厚さが3μmの表面層2cと、厚さが300nmの埋め込み絶縁膜2bとを有する。ピエゾ抵抗素子R1〜R4は、表面層2cの、ピエゾ抵抗素子R1〜R4とする領域にボロンをイオン注入して得られたp型の拡散領域によって形成されたもので、シート抵抗値として2.5kΩの値を示した。ピエゾ抵抗素子R1〜R4の形成は、SOI基板2の表面に熱酸化膜を30nmの膜厚で形成し、その上にレジストを塗布してピエゾ抵抗素子R1〜R4を形成する領域をパターニングし、その後、加速電圧60kV、ドーズ量5×1013/cm2でBF2をイオン注入し、さらに、レジストを剥離し洗浄した後、窒素雰囲気中での、1000℃、30分の熱処理によりSOI基板2の表面層2cを活性化させて行った。ピエゾ抵抗素子R1〜R4の全長Lは20μmとした。

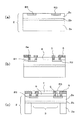

本実施例では、図5に示した折り返し型のピエゾ抵抗素子R11〜R14を有する半導体圧力センサ11を作製した。以下に、本実施例の半導体圧力センサ11の製造工程について図5を参照して説明する。

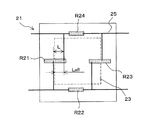

図9に、本発明の実施例3による半導体圧力センサ21の概略平面図を示す。本実施例の半導体圧力センサ21は、実施例1と同様に、直線型のピエゾ抵抗素子R21〜R24を有している。ただし、ダイヤフラム23を跨いで配置されるピエゾ抵抗素子R21,R23の長さが実施例1と比較して長く、かつ、ピエゾ抵抗素子R21,R23への配線25の接続位置(コンタクトホールの位置)が、実施例1と比較してピエゾ抵抗素子R21,R23の長手方向中央寄りである点が、実施例1と異なっている。

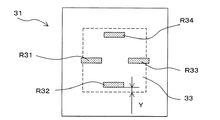

図11に、本発明の実施例4による半導体圧力センサ31の概略平面図を示す。なお図11では配線を省略している。本実施例の半導体圧力センサ31は、ダイヤフラム33のエッジを跨いで配置されるピエゾ抵抗素子R31,R33の対向方向と直交する方向で対向している、ダイヤフラム33のエッジに平行に配置された2つのピエゾ抵抗素子R32,R34が、ダイヤフラム33の内側に配置されていることと、ピエゾ抵抗素子R31〜R34の幅が5μmであることが、実施例3との構造上の相違点である。その他の点、例えば、ダイヤフラム33を1辺の長さが100μmの正方形としたことや、ダイヤフラム33を跨いで配置されるピエゾ抵抗素子R31,R33は、全長L=10μmで、かつLX=9μmとなるように配置されていること等は実施例3と同様である。

図15に本発明の実施例5による半導体圧力センサ41の概略平面図を示す。本実施例ではSOI基板42の表面の全域が拡散領域となっており、周溝44によって他の拡散領域と分離されることによってピエゾ抵抗素子R41〜R44が形成された構成となっている。その他の構成は実施例4と同様である。

2 SOI基板

3 ダイヤフラム

5 配線

R1〜R4 ピエゾ抵抗素子

Claims (12)

- ダイヤフラム部を有する半導体基板に1つ以上の歪み検出素子が設けられた半導体圧力センサにおいて、

前記歪み検出素子の少なくとも1つは、前記ダイヤフラム部に第1の端部を有し、該第1の端部と前記ダイヤフラム部のエッジ間の距離をLXとしたとき、LX≦20μmとなるように、前記ダイヤフラム部の内側と外側とに跨って配置されていることを特徴とする半導体圧力センサ。 - 前記歪み検出素子は、前記ダイヤフラム部に折り返し部を有し、該折り返し部は、前記第1の端部と接して形成されている請求項1に記載の半導体圧力センサ。

- 4つの前記歪み検出素子が、ホイートストンブリッジ回路を構成するように電気的に接続され、そのうち対向する2つの歪み検出素子が、LX≦20μmとなるように配置されている請求項1または2に記載の半導体圧力センサ。

- LX≦10μmである請求項1ないし3のいずれか1項に記載の半導体圧力センサ。

- 前記半導体基板は、半導体材料からなる支持層および表面層の間に絶縁層を介在させたSOI基板であり、前記表面層に前記歪み検出素子が形成されるとともに、前記支持層の一部の領域が除去されることによって、前記ダイヤフラムが形成されている請求項1ないし4のいずれか1項に記載の半導体圧力センサ。

- 前記歪み検出素子は、前記第1の端部が前記ダイヤフラム部の領域内に配置され、他端部が前記支持層の領域内に配置されている請求項5に記載の半導体圧力センサ。

- 前記歪み検出素子は、第一導電型の半導体層に形成された第二導電型の拡散領域で形成されている請求項1ないし6のいずれか1項に記載の半導体圧力センサ。

- 前記歪み検出素子は、第一導電型の半導体層の全域に形成された第二導電型の拡散領域の一部を、溝によって他の部分と電気的に分離することによって形成されている請求項1ないし6のいずれか1項に記載の半導体圧力センサ。

- 前記少なくとも1つの歪み検出素子は、前記歪み検出素子の全長をL、前記歪み検出素子の全長Lのうち、前記ダイヤフラム部の内側での前記ダイヤフラム部のエッジから中心へ向かう方向と平行なの部分の長さをLeffとしたとき、

0.5<Leff/L<1

なる関係を満たすように配置されている請求項1ないし8のいずれか1項に記載の半導体圧力センサ。 - 前記歪み検出素子の全長Lは、前記歪み検出素子と接続される配線の接続位置によって規定される請求項9に記載の半導体圧力センサ。

- 前記ダイヤフラム部の平面形状は、1辺の長さが400μm以下の正方形である請求項1ないし10のいずれか1項に記載の半導体圧力センサ。

- ダイヤフラム部を有する半導体基板に1つ以上の歪み検出素子が設けられた半導体圧力センサの製造方法において、

前記半導体基板に前記歪み検出素子を形成する工程と、

前記半導体基板に前記ダイヤフラム部を形成する工程とを有し、

前記歪み検出素子の少なくとも1つを、前記ダイヤフラム部に第1の端部を有し、該第1の端部と前記ダイヤフラム部のエッジ間の距離をLXとしたとき、LX≦20μmとなるように、前記ダイヤフラム部の内側と外側とに跨って配置することを特徴とする半導体圧力センサの製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004176853A JP4035519B2 (ja) | 2004-06-15 | 2004-06-15 | 半導体圧力センサおよびその製造方法 |

| US11/597,501 US7540198B2 (en) | 2004-06-15 | 2005-06-13 | Semiconductor device |

| PCT/JP2005/011191 WO2005124306A1 (en) | 2004-06-15 | 2005-06-13 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004176853A JP4035519B2 (ja) | 2004-06-15 | 2004-06-15 | 半導体圧力センサおよびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006003099A JP2006003099A (ja) | 2006-01-05 |

| JP2006003099A5 JP2006003099A5 (ja) | 2007-07-19 |

| JP4035519B2 true JP4035519B2 (ja) | 2008-01-23 |

Family

ID=35771622

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004176853A Expired - Fee Related JP4035519B2 (ja) | 2004-06-15 | 2004-06-15 | 半導体圧力センサおよびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4035519B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007292559A (ja) * | 2006-04-24 | 2007-11-08 | Mitsumi Electric Co Ltd | 半導体圧力センサーの製造方法 |

| JP4739164B2 (ja) | 2006-10-20 | 2011-08-03 | 三菱電機株式会社 | 車両用エンジンの吸入空気圧力測定用の半導体感歪センサ |

| JP5139759B2 (ja) * | 2007-09-25 | 2013-02-06 | アルプス電気株式会社 | 半導体圧力センサ |

| WO2010055734A1 (ja) * | 2008-11-17 | 2010-05-20 | アルプス電気株式会社 | 半導体圧力センサ |

| JP2015184046A (ja) | 2014-03-20 | 2015-10-22 | セイコーエプソン株式会社 | 物理量センサー、圧力センサー、高度計、電子機器および移動体 |

| JP6318760B2 (ja) | 2014-03-25 | 2018-05-09 | セイコーエプソン株式会社 | 物理量センサー、高度計、電子機器および移動体 |

| CN113348348B (zh) * | 2019-02-28 | 2023-11-17 | 阿尔卑斯阿尔派株式会社 | 压力传感器 |

-

2004

- 2004-06-15 JP JP2004176853A patent/JP4035519B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006003099A (ja) | 2006-01-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7540198B2 (en) | Semiconductor device | |

| US10775248B2 (en) | MEMS strain gauge sensor and manufacturing method | |

| US7926354B2 (en) | Semiconductor pressure sensor and method of producing the same | |

| JP2006030159A (ja) | ピエゾ抵抗型半導体装置及びその製造方法 | |

| KR100580440B1 (ko) | 도핑된 반도체층을 배선으로 사용한 반도체 가속도 센서 | |

| JP4035519B2 (ja) | 半導体圧力センサおよびその製造方法 | |

| JP4589605B2 (ja) | 半導体多軸加速度センサ | |

| US10386255B2 (en) | Pressure sensor device and manufacturing method | |

| US7192819B1 (en) | Semiconductor sensor device using MEMS technology | |

| KR20030026872A (ko) | 가속도 센서 | |

| JP3985214B2 (ja) | 半導体加速度センサー | |

| JP2006030158A (ja) | 半導体装置およびその製造方法 | |

| US7666699B2 (en) | Semiconductor strain gauge and the manufacturing method | |

| US7838320B2 (en) | Semiconductor physical quantity sensor and method for manufacturing the same | |

| KR101752875B1 (ko) | 반도체 압력센서 및 이의 제조방법 | |

| JP5191030B2 (ja) | 半導体歪みゲージ | |

| JP2011082195A (ja) | 半導体装置及びその製造方法 | |

| JP2010032389A (ja) | 物理量センサ及びその製造方法 | |

| JP4179070B2 (ja) | 半導体加速度センサおよびその製造方法 | |

| JP3187754B2 (ja) | 半導体センサおよびその製造方法 | |

| JPH06163934A (ja) | 半導体加速度センサ及びその製造方法 | |

| US20170233248A1 (en) | Micro sensor and manufacturing method thereof | |

| JP2011102775A (ja) | 半導体圧力センサおよびその製造方法 | |

| US11573143B2 (en) | Mems pressure sensing element with stress adjustors to minimize thermal hysteresis induced by electrical field | |

| JP5067295B2 (ja) | センサ及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070605 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070605 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070711 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070907 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071003 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071029 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101102 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101102 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111102 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121102 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131102 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |