JP3873003B2 - 液晶表示装置及びtft基板 - Google Patents

液晶表示装置及びtft基板 Download PDFInfo

- Publication number

- JP3873003B2 JP3873003B2 JP2002121634A JP2002121634A JP3873003B2 JP 3873003 B2 JP3873003 B2 JP 3873003B2 JP 2002121634 A JP2002121634 A JP 2002121634A JP 2002121634 A JP2002121634 A JP 2002121634A JP 3873003 B2 JP3873003 B2 JP 3873003B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- circuit

- liquid crystal

- crystal display

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3696—Generation of voltages supplied to electrode drivers

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0408—Integration of the drivers onto the display substrate

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0421—Structural details of the set of electrodes

- G09G2300/0426—Layout of electrodes and connections

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0876—Supplementary capacities in pixels having special driving circuits and electrodes instead of being connected to common electrode or ground; Use of additional capacitively coupled compensation electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0281—Arrangement of scan or data electrode driver circuits at the periphery of a panel not inherent to a split matrix structure

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0297—Special arrangements with multiplexing or demultiplexing of display data in the drivers for data electrodes, in a pre-processing circuitry delivering display data to said drivers or in the matrix panel, e.g. multiplexing plural data signals to one D/A converter or demultiplexing the D/A converter output to multiple columns

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

- G09G2310/061—Details of flat display driving waveforms for resetting or blanking

- G09G2310/063—Waveforms for resetting the whole screen at once

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

Description

【発明の属する技術分野】

本発明は、液晶表示装置に係わり、特に、携帯型表示装置に用いられる液晶表示装置の駆動回路に適用して有効な技術に関する。

【0002】

【従来の技術】

STN(Super Twisted Nematic)方式、あるいはTFT(Thin Film Transistor)方式の液晶表示装置は、ノート型パソコン等の表示装置として広く使用されている。これらの液晶表示装置は、液晶表示パネルと、液晶表示パネルを駆動する駆動回路を備えている。

【0003】

このような液晶表示装置において、携帯電話機等の携帯用端末装置の表示装置として利用されるものが増加している。液晶表示装置を携帯用端末装置の表示装置として用いる場合には、従来の液晶表示装置に比べて、さらに小型、高精細、のものが望まれる。

【0004】

小型化、高精細化が可能な液晶表示装置では、スイッチング素子としてポリシリコンTFTを用い、画素電極を形成する基板と同一の基板上に、駆動回路を形成する液晶表示装置(以下駆動回路一体型液晶表示装置と呼ぶ)が知られている。

【0005】

【発明が解決しようとする課題】

携帯電話機等の携帯用端末装置の表示装置は、画像付きメール等の普及に伴い、高画質、高精細化等、画像表示機能のさらなる向上が望まれている。また、携帯端末であることから低消費電力化が求められており、さらには、コスト競争力の強化も重要な課題である。

【0006】

携帯端末装置の小型化に伴う問題点として、液晶表示装置の駆動回路を実装するスペースが減少することがあげられる。さらに、実装方法に関して、携帯端末装置では、装置の中心線と表示画面の中心とが重なる配置方法である所謂画面センター化の要望があり、駆動回路を実装する位置が制限され、配置に考慮が必要である。さらには、従来の液晶表示装置では、表示画面の隣合う2辺に駆動回路が設けられていたが、1辺にのみ駆動回路を実装する所謂3辺フリー化の要望もある。また、実装面積の縮小及び、低コスト化のために、実装部品の削減の必要もある。

【0007】

また、小型の表示装置に高精細化を求めると、1画素あたりのピッチが小さく、画素の開口率が減少する問題がある。さらには、画面サイズの増大に伴い画素数が増加すると、駆動速度に対して駆動回路の性能が追従できなくなる問題や、回路規模が増大し信号及び電源用の配線の引き回しが長くなり、信号波形の歪みや、ノイズの影響が無視できなくなるという問題が生じる。

【0008】

本発明は、前記従来技術の問題点を解決するためになされたものであり、本発明の目的は、小型の液晶表示装置において、最適な駆動回路を実現する技術を提供することにある。

【0009】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

【0010】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

【0011】

【課題を解決するための手段】

液晶表示装置が有する第1の基板には保持容量素子が設けられており、前記保持容量素子はMOSにより形成されており、前記MOSのソース領域とドレイン領域とは画素電極に電気的に接続しており、前記MOSのゲート電極には走査信号の高電位側よりも高い電圧で変動する電圧が供給されている。また、液晶表示装置には駆動回路が設けられており、前記駆動回路は、走査信号の高電位側の電圧と、前記走査信号の低電位側の電圧と、前記走査信号の高電位側の電圧よりも高い電圧とを生成する昇圧回路を有しており、前記昇圧回路には、時分割で駆動される第1の昇圧容量と第2の昇圧容量と第3の昇圧容量とが接続されている。また、液晶表示装置には駆動回路が設けられており、前記駆動回路には、走査信号の高電位側の電圧と、前記走査信号の低電位側の電圧と、前記走査信号の高電位側の電圧よりも高い電圧とを生成する昇圧回路を有しており、液晶表示装置の電源オフ時に、前記高い電圧を、定電流素子を用いることで、徐々にGND電位に近づける。

【0012】

TFT基板が有する基板には保持容量素子が設けられており、前記保持容量素子はMOSにより形成されており、前記MOSのソース領域とドレイン領域とは画素電極に電気的に接続しており、前記MOSのゲート電極には走査信号の高電位側よりも高い電圧で変動する電圧が供給されている。また、TFT基板が有する基板には駆動回路が電気的に接続されており、前記駆動回路は、走査信号の高電位側の電圧と、前記走査信号の低電位側の電圧と、前記走査信号の高電位側の電圧よりも高い電圧とを生成する昇圧回路を有しており、前記昇圧回路には、時分割で駆動される第1の昇圧容量と第2の昇圧容量と第3の昇圧容量とが接続されている。また、TFT基板が有する基板には駆動回路が電気的に接続されており、前記駆動回路は、走査信号の高電位側の電圧と、前記走査信号の低電位側の電圧と、前記走査信号の高電位側の電圧よりも高い電圧とを生成する昇圧回路を有しており、電源オフ時に、前記高い電圧を、定電流素子を用いることで、徐々にGND電位に近づける。

【0013】

【発明の実施の形態】

以下、図面を参照して本発明の実施の形態を詳細に説明する。なお、実施の形態を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

【0014】

図1は、本発明の実施の形態の液晶表示装置の基本構成を示すブロック図である。同図に示すように、本実施の形態の液晶表示装置100は、液晶表示パネル1と、コントローラ3と、電源回路4と、駆動回路50とから構成される。

【0015】

液晶表示パネル1は、画素電極12、薄膜トランジスタ10、保持容量素子13等が形成されるTFT基板2と、カラーフィルタ等が形成されるフィルタ基板(図示せず)とを、所定の間隙を隔てて重ね合わせ、該両基板間の周縁部近傍に枠状に設けたシール材により、両基板を貼り合わせると共に、シール材の一部に設けた液晶封入口から両基板間のシール材の内側に液晶を封入、封止し、さらに、両基板の外側に偏光板を貼り付けて構成される。なお、本実施の形態は対向電極15がTFT基板2に設けられる所謂横電界方式の液晶表示パネルにも、対向電極15がフィルタ基板に設けられる所謂縦電界方式の液晶表示パネルにも同様に適用される。

【0016】

各画素は、画素電極12と薄膜トランジスタ10から成り、複数の走査信号線(またはゲート信号線)GLと映像信号線(またはドレイン信号線)DLとの交差する部分に対応して設けられる。

【0017】

各画素の薄膜トランジスタ10は、ソースが画素電極12に接続され、ドレインが映像信号線DLに接続され、ゲートが走査信号線GLに接続される。この薄膜トランジスタ10は、画素電極12に表示電圧(階調電圧)を供給するためのスイッチとして機能する。また、画素電極12には保持容量素子13が接続されている。保持容量素子13は画素電極に書き込まれた電圧を保持するための素子である。

【0018】

なお、ソース、ドレインの呼び方は、バイアスの関係で逆になることもあるが、ここでは、映像信号線DLに接続される方をドレインと称する。

【0019】

コントローラ3と、電源回路4、駆動回路50とは、液晶表示パネル1のTFT基板2を構成する透明性の絶縁基板(ガラス基板、樹脂基板等)に、それぞれ電気的に接続される。コントローラ3から送出されたディジタル信号(表示データ、クロック信号等)、および電源回路4から供給される電源電圧は、駆動回路50に入力される。

【0020】

コントローラ3は、半導体集積回路(LSI)から構成され、外部から送信されてくるクロック信号、ディスプレイタイミング信号、水平同期信号、垂直同期信号の各表示制御信号および表示用デ−タ(R・G・B)を基に、駆動回路50を制御・駆動する。

【0021】

駆動回路50は、TFT基板2とは別の基板に形成された半導体集積回路(LSI)又は、TFT基板2と同じ基板に形成された半導体回路から構成され、走査信号線GLの駆動と、映像信号線DLの駆動と、保持容量素子13に保持容量信号線14を介して、信号を供給している。

【0022】

駆動回路50は、コントローラ3から送出されるフレーム開始指示信号(FLM、以下スタート信号とも呼ぶ)およびシフトクロック(CL1)に基づき、1水平走査時間(以下1Hとも呼ぶ)毎に、順次液晶表示パネル1の各走査信号線GLにHighレベルの選択走査電圧(走査信号)を供給する。これにより、液晶表示パネル1の各走査信号線GLに接続された複数の薄膜トランジスタ10が、1水平走査時間1Hの間導通する。

【0023】

また、駆動回路50は画素が表示すべき階調に対応する階調電圧を映像信号線DLに出力する。薄膜トランジスタ10がオン状態になると、映像信号線DLがから階調電圧(映像信号)が画素電極12に供給される。その後、薄膜トランジスタ10がオフ状態となることで画素が表示すべき映像に基づく階調電圧が画素電極12に保持される。

【0024】

保持容量素子13は画素電極12に接続された電極と、保持容量信号線14に接続した電極との間で容量を形成しており、該容量により画素電極12に入力した階調電圧を保持する。従来、保持容量信号線14で供給される信号には、対向電極15に供給される共通電圧(VCOM)と同等な電圧が供給されるが、本実施の形態では、保持容量信号線14で供給される信号は、画素電極に供給される階調電圧よりも高い電圧が供給される。

【0025】

図2は、図1に示す駆動回路を2つに分けた実施例を示す。図2では、駆動回路はTFT基板2に形成された第1駆動回路5と、TFT基板2とは別基板に形成され、液晶表示パネル1に接続された第2駆動回路6とで構成される。第1駆動回路5は走査信号線GLに走査信号を出力する第1駆動回路5A、5Bとが、TFT基板2の図中左右に分離して設けられている。また、第2駆動回路は映像信号線DLに階調電圧を供給する回路であり、図中下方に設けられている。

【0026】

なお、第1の駆動回路はTFT基板2と同様の工程で形成される回路であり、第2駆動回路6はシリコン基板等に形成された集積回路で、TFT基板2とは別工程で形成され、液晶表示パネル1完成後に異方性導電膜等により接続される回路である。

【0027】

なお、図2では走査信号線GLに走査信号を出力する第1駆動回路5A、5Bとを、分離してTFT基板2の図中左右に設けたが、走査信号線GLに走査信号を出力する第1駆動回路を一つにして、TFT基板2の左右どちらか片側に設けることも可能である。また、TFT基板2の図中下側に設けてもよい。

【0028】

図2に示す構成では、走査信号線GLを駆動する駆動回路は走査信号線GLの延長線上(図中では液晶表示パネル1の左右)に設けられている。しかしながら、携帯電話機等の携帯電子機器では、表示画面部分の横幅が狭いことと、利用者に好まれる機器デザインの理由より、機器の中心線上に表示画面の中心が位置する所謂画面センター化の要望がある。よって、表示画面の両横側には第2駆動回路5A、5Bを配置する充分な領域が無いことから、第2駆動回路5A、5Bは液晶表示パネル1に設けたスイッチング素子等と同様の半導体製造工程により形成する方法が用いられる。

【0029】

すなわち、液晶表示パネル1を形成する際に、駆動回路も作り込んでおけば、比較的狭い領域に駆動回路を形成することが可能で、さらには外部接続端子等の構成を省略することができる。なお、絶縁基板上に駆動回路を形成可能な半導体層としてはポリシリコン半導体層等の結晶構造が単結晶に近い半導体層が利用可能である。

【0030】

図2では、保持容量素子13としてスイッチング素子10と同様の構成を用いている(MOSキャップ容量)。すなわち、画素に設けられたスイッチング素子10では、ゲート電極が半導体層及び、絶縁膜を介して、ソース・ドレイン領域と重なっており容量(ゲート寄生容量)を形成する。保持容量素子13もスイッチング素子10と同様の構成をしており、ゲート電極は半導体層及び、絶縁膜を介して、ソース・ドレイン領域と重なっており容量素子を形成する。図2に示すように、保持容量素子13を構成する1方の電極(以下SD側対向電極とも呼ぶ)は、ドレイン領域とソース領域とが短絡され、画素電極に電気的に接続している。また、保持容量素子13を構成する他方の電極(G側対向電極)はゲート電極で形成されている。

【0031】

本実施の形態では、スイッチング素子10はn型トランジスタであり、保持容量素子13のゲート電極には、画素電極に印加された電圧よりも高い電圧が印加される。保持容量素子13のゲート電極に保持容量信号線14を介して高電圧が印加されると、保持容量素子13を構成する半導体層(チャネル部)の電気抵抗が低下し、半導体層も容量素子の電極として機能する。特に、ゲート電極と半導体層との間の絶縁膜(例えばゲート酸化膜)は、膜厚が薄いため保持容量素子13の各電極の面積が、従来に比較して小さくても充分な容量を得ることができる。

【0032】

従来、保持容量信号線14で供給される信号には、対向電極15に供給される共通電圧と同等な電圧が供給されたが、本実施の形態では、画素電圧に供給される階調電圧よりも高い電圧が供給され、さらには、走査信号よりも高い電圧が供給される。スイッチング素子10がn型トランジスタの場合に、保持容量素子13をオンするためにゲート電極に印加される電圧(Vth)は、画素電極に印加された電圧よりも充分に高い電圧とする必要がある。すなわち、スイッチング素子10をオンにする走査信号は、画素電極に印加された電圧よりも高い電圧である。

【0033】

さらに、保持容量素子13が容量素子として機能するように、チャネル部に充分な反転層が発生するためには、保持容量素子13のG側対向電極に印加される電圧(Vsg)は、Vsg>Vthである必要がある。すなわち、保持容量素子13に印加される電圧(G側対向電極電圧)は走査信号の高電位側電圧よりも高い電圧である必要がある。そのため、電源回路4は走査信号よりも高電圧の電源電圧を形成する必要が生じることとなる。なお、電源回路4で高電圧を形成する昇圧回路の詳細については後述する。

【0034】

次に図2に示す各回路の配置の問題点について説明する。図2においては、第2駆動回路6とコントローラ3と電源回路4とが、別々に設けられることから、各回路に接続される配線のレイアウトに問題が生じる。図2では、コントローラ3が右側で、電源回路4が左側に位置しており、コントローラ3から左側の第1駆動回路5Aまでの配線は、電源回路4から出力する配線を避けて設ける必要がある。例えば、配線をフレキシブル基板等に形成する場合では、高価な多層基板を用いる必要がある。そのため、各回路を同一チップで形成したり、出力端子位置を工夫することとした。

【0035】

図3にコントローラ3と映像信号線出力回路とを1つの基板上にまとめて第2駆動回路6として形成し、フレキシブル基板30に搭載した構成を示す。

【0036】

符号31は入力配線で、外部からの信号が第2駆動回路6や電源回路4に入力する。配線32は電源回路4から第2駆動回路に電圧を供給する配線で、配線33は第2駆動回路6から第1駆動回路5に接続する配線である。符号34は、コンデンサ等の外付け部品であり、第2駆動回路6に必要な外付け部品34がフレキシブルプリント基板30に搭載されている。電源回路4には昇圧回路が内蔵されており、昇圧回路に用いられるコンデンサが電源回路4に接続されている。

【0037】

図3に示すように、コントローラ3と映像信号線出力回路とを1つのチップにまとめて形成すると、フレキシブル基板30上の配線が省略できる。ただし、高精細表示になり画素数が増加すると、第2駆動回路6を小型に形成することが困難となる。

【0038】

次に図4に、映像信号線DLに階調電圧を供給する回路を分配回路60としてTFT基板2上に形成した概略ブロック図を示す。

【0039】

図4に示す第2駆動回路6からは1走査期間1Hの間、時系列に3本の映像信号線に信号が出力する。分配回路60は3つの分配スイッチング素子61が1つの第2駆動回路6の出力に接続されており、順番に分配スイッチング素子61が導通することで、1走査期間1Hの間、3本の映像信号線に信号が分配供給されることになる。符号62は分配制御信号線で分配スイッチング素子61を導通状態とする信号が、電源回路4から供給される。

【0040】

分配回路60を液晶表示パネル1に設けることで、第2駆動回路6からの出力数を減少することが可能であり、第2駆動回路6の回路規模を縮小することから、チップ面積が小さくなり、低コスト化が可能である。また、出力数が減少することで、フレキシブル基板30と液晶表示パネル1との接続箇所数も減少し接続信頼性も向上する。

【0041】

ただし、分配スイッチング素子61を制御する信号を供給する必要がある。分配スイッチング素子61は画素部のスイッチング素子10と同様の構成をしている。すなわち、分配スイッチング素子61を制御するためには、走査信号同様の電圧が必要となる。

【0042】

図4では、電源回路4から分配制御信号線62が出力しており、分配制御信号は電源回路4が供給している。電源回路4では第2駆動回路6から供給される信号の電圧を変換(レベルシフト)して、分配制御信号を形成する。電源回路4からは第1駆動回路5、保持容量素子13にも高電圧が供給されている。なお、電源回路4から出力する高電圧の制御信号は、第2駆動回路6からの信号をレベルシフトして出力している。

【0043】

図5に電源回路4を第2駆動回路6に設けた場合の概略ブロック図を示す。図5では、映像信号線DLに階調電圧を出力する回路と、コントローラと、電源回路4とが1チップ化されている。すなわち、図5に示す第2駆動回路6は、高電圧を発生させる回路を内蔵している。また、レベルシフト回路も内蔵されており、第2駆動回路6が分配スイッチング素子61、第1駆動回路5、保持容量素子13を制御する高電圧の信号を出力している。

【0044】

次に図6にTFT基板2上に、電源回路4を構成するチップを搭載した液晶表示装置100の概略ブロック図を示す。第1駆動回路5はTFT基板2に形成されており、絶縁膜等を介して第1駆動回路5上に半導体基板を搭載することが可能である。符号40は第1駆動回路5と電源回路4とが重なって設けられる領域で、第1駆動回路5と電源回路4との接続部が設けられる。また、外付け部品34とはフレキシブル基板30に形成された配線を介して電気的に接続されている。

【0045】

次に、電源回路4に用いられる昇圧回路について説明する。携帯電話機等の小型携帯機器では、電源として電池の利用が一般的である。また、流通量の多さから電池は出力電圧が1.5V程度から4V程度のものが利用される。

【0046】

そのため、昇圧回路を用いて液晶表示装置用に電源電圧を作成している。図7に薄膜トランジスタ方式の液晶表示装置に必要な電源電圧を示す。なお、図7では図1から図6に示す液晶表示装置100の対向電極15に供給する電圧VCOMを一定周期で反転させる、所謂VCOM反転駆動方式を用いている場合の各駆動電圧を示している。

【0047】

図7においてVGONは画素部の薄膜トランジスタ(TFT)をオンするための走査信号VGのハイ電圧で、約7.5V程度が必要となる。また、VGOFFは薄膜トランジスタをオフするための電圧であり、走査信号VGのロウ電圧で、約−5.5V程度必要となる。VGHは走査信号VGを出力する第1駆動回路5(ゲートドライバ)用ハイ電源で、VGLは第1駆動回路5用ロウ電源である。走査信号のハイ電圧VGONが約7.5Vなので、VGHは8V、走査信号のロウ電圧VGOFFが約−5.5Vなので、VGLは−6V程度必要となる。

【0048】

次に、VDHは階調基準電圧である。階調基準電圧VDHを基準に第2駆動回路で階調電圧を生成する。液晶材の特性から5.0V程度が必要である。DDVDHは図4乃至図6に示す第2駆動回路(ソースドライバ)6用の電源電圧である。第2駆動回路6が出力する階調電圧の基準電圧VDHが5.0Vで、第2駆動回路6の最大定格が6.0Vであるため、5.5V程度が必要となる。

【0049】

VCOMHは対向電極用ハイ電圧で、VCOMLは対向電極用ロウ電圧である。VCOMHは5.0V以下が必要となり、VCOMLは−2.5V程度の電圧が必要となる。VCLは対向電極用電圧生成電源で、対向電極用ロウ電圧VCOMLを生成するための電源電圧である。VCOML生成回路の動作マージンを考慮し−3V程度が必要となる。

【0050】

さらに、VSTGHとVSTGLは保持容量素子13のG側対向電極に供給される電圧で、電圧VSTGから形成される。前述したように、VCOM反転駆動方式を用いるため、保持容量素子13のG側対向電極に供給される電圧もハイ側とロウ側が必要であり、VSTGHがG側対向電極ハイ電圧で、VSTGLがG側対向電極ロウ電圧である。G側対向電極電圧は保持容量素子13が機能するように、走査信号よりも充分に高い電圧が印加される。そのため、電圧VSTGは16.5V程度必要である。

【0051】

以上液晶表示装置に必要な電源の中で、第2駆動回路6用の電源電圧DDVDHと、第1駆動回路5用ハイ電源VGHと、第1駆動回路5用ロウ電源VGLと、対向電極用電圧生成電源VCLと、保持容量素子13用の電圧VSTGをチャージポンプ方式の昇圧回路を用いて作成することとし、他の電圧は昇圧回路で形成した電圧を分圧等して形成することとした。

【0052】

チャージポンプ方式の昇圧回路の動作原理について図8を用いて、2倍昇圧を例に取り説明する。昇圧回路は入力電源Vin、昇圧容量C11、保持容量Cout1、切り替えスイッチSW1、SW2で構成され,切り替えスイッチにより図8(a)の充電状態と、図8(b)の放電状態を実現している。まず図8(a)の充電状態では切り替えスイッチSW1により、昇圧容量C11の一方の電極をGND電位に接続し、スイッチSW2により昇圧容量C11の他方の電極を入力電源Vinに接続して、昇圧容量C11を入力電源Vinに対し並列に接続する。これにより入力電源Vin分の電荷が昇圧容量C11に充電される。

【0053】

次に図8(b)では、切り替えスイッチSW3により、図8(a)において昇圧容量C11のGND電位に接続された電極に、入力電源Vinを印加するよう直列に接続する。この時、昇圧容量C11の他方の電極は、入力電源Vinの2倍の電圧である2×Vinとなる。スイッチSW4により昇圧容量C11、入力電源Vinに対し並列にCout1を接続する。これにより保持容量Cout1には2×Vinの電圧が保持される。

【0054】

次に、図8に示す昇圧回路で、前述の第2駆動回路6用の電源電圧DDVDH(約5.5V)と、第1駆動回路5用ハイ電源VGH(約7.5V)と、第1駆動回路5用ロウ電源VGL(約−6V)と、対向電極用電圧生成電源VCL(約−3V)と、保持容量素子13用の電圧VSTG(約16.5V)とを作成する場合を検討する。

【0055】

入力電源Vinを3Vとすると、第2駆動回路6用の電源電圧DDVDH(約5.5V)は約2倍なので、入力電源Vinを2倍とする昇圧回路が必要である。第1駆動回路5B用ハイ電源VGH(約7.5V)は2倍では不足なので、入力電源Vinを3倍とする昇圧回路が必要である。、第1駆動回路5用ロウ電源VGLは約−6Vなので、入力電源Vinを−2倍とする昇圧回路が必要で、対向電極用電圧生成電源VCLは約−3Vなので、入力電源Vinを−1倍とする昇圧回路が必要となる。また、保持容量素子13用の電圧VSTG(約16.5V)用には入力電源Vinを3Vを6倍とする昇圧回路を用いることとした。

【0056】

図9に入力電源Vinを2倍、3倍、6倍、−2倍、−1倍とする昇圧回路55の構成を示す。なお、−2倍、−1倍とする場合では、厳密には昇圧ではないが、ここでは、昇圧回路を入力電圧から異なる電圧を形成する回路の意味で用いる。図9に示す回路では、回路の外付部品としてコンデンサ51を多数使用しており、実装部品点数が多くなり、実装面積が広くなってしまうといった問題がある。なお、図中の符号Cout1からCout5は出力電圧を保持する保持容量である。

【0057】

次に、図10に昇圧回路55の出力を入力電源として利用することで、外付けコンデンサ51の数を減らす回路の概念ブロック図を示す。昇圧回路52では入力電源Vinを2倍にしているので、昇圧回路52の出力電圧を利用し、さらに昇圧回路53で3倍にすることで、入力電源Vinを3Vとすると、6倍の電圧18Vを形成することが可能である。図10に示す回路では、外付けコンデンサとして、昇圧回路52に接続しているC11と、昇圧回路53に接続している外付けコンデンサC12、C21,C22の4個となり、図9に示す回路に対して外付けコンデンサの数を11個から4個に減少することができる。なお、外付けコンデンサC11は2倍用で、外付けコンデンサC12は1倍用(−1倍用)で、外付けコンデンサC21、C22は2倍用(−2倍用)である。

【0058】

図11を用いて昇圧回路53の入力電源Vinを3倍にする動作を説明する。図11(a)では、入力電源電圧Vinを用い、昇圧容量(外付けコンデンサ)C12を充電している。また、図11(b)では、図8で説明したような入力電源電圧Vinを2倍とする昇圧回路で、電圧DDVDHが作成されている。その後、図11(c)に示すように、保持容量Cout1の出力である電圧DDVDHを用い、保持容量Cout1と昇圧容量C12とを直列につなぐことで、入力電源Vinの3倍の電圧が作成される。

【0059】

次に、図12を用いて昇圧回路53の入力電源Vinを6倍にする動作を説明する。図12(a)では、昇圧回路52の保持容量Cout1の出力である電圧DDVDHを用い、昇圧容量C21とC22とを電圧DDVDHに充電する。その後、図12(b)では、昇圧容量C21、C22と保持容量Cout1とを直列につなぐことで、電圧DDVDHの3倍で、入力電源Vinの6倍の電圧を作成している。

【0060】

次に、図13を用いて昇圧回路55の動作を説明する。図13(a)では、入力電源Vinを用いて、昇圧容量C12を電圧Vinに充電する。その後、図13(b)では、昇圧容量C12の正極性側の電極をGND電位に接続することで、入力電源Vinと極性が反転した電圧VCLを作成している。そして昇圧容量C12と保持容量Cout4を並列につなぐことで、保持容量Cout4に電圧VCLが保持される。

【0061】

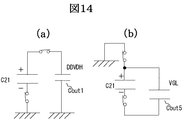

次に、図14を用いて昇圧回路53の動作を説明する。図14(a)では、昇圧回路52の保持容量Cout1の出力である電圧DDVDHを用いて、昇圧容量C21を電圧DDVDHに充電する。その後、図14(b)では、昇圧容量C21の正極性側の電極をGND電位に接続することで、電圧DDVDHと極性が反転した電圧VGLを作成している。そして昇圧容量C21と保持容量Cout3を並列につなぐことで、保持容量Cout3に電圧VGLが保持される。

【0062】

なお、図9に示す昇圧回路では、例えば5倍の電圧を作成するのにコンデンサが5個と電源電圧に対して昇圧する電圧の倍数分のコンデンサが必要である。対して図10に示す昇圧回路では、保持容量Cout1で保持されている昇圧した電圧を利用することで、コンデンサを省略し部品数を減少させている。さらに、図13、図14に示す回路では、負極性側の電圧をコンデンサの接続を逆転することと、保持容量の昇圧された電圧に加えて入力電源Vinを利用することで、コンデンサを兼用可能として部品数を減少させている。このコンデンサの数を省略可能としたり、兼用可能としているのは、液晶表示装置特有の電源が第1駆動回路5A用の電源電圧DDVDHと、第2駆動回路5B用ハイ電源VGHと、第2駆動回路5B用ロウ電源VGLと、対向電極用電圧生成電源VCLのように複数あり、また、負極性側の電圧があるためである。そのため昇圧容量C12、C21、C22を時分割で、複数の昇圧回路の間で兼用することや、昇圧した電圧を利用することが可能となっている。

【0063】

図15に図10に示す昇圧回路53のより具体的な構成を示し、以下図16に示すタイミングチャートを用いて動作を説明する。まず、電圧VGHを作成するために、図11に示した動作を実現する方法について説明する。図11(a)に示す回路とするには、図15のスイッチSW1とスイッチSW3をオンにする。スイッチSW1とスイッチSW3をオンにすると、昇圧容量C12には入力電源Vinの電圧が充電される。この時、図11(b)に示す回路のように、昇圧回路52からは電圧DDVDHが出力している。次に、図11(c)に示す回路となるように、図15のスイッチ1、スイッチ3をオフとし、スイッチ4をオンにして、昇圧容量C12とCout1とを直列に接続すると同時に、スイッチ13をオンにして、保持容量Cout2を充電する。

【0064】

次に、図12に示した回路の動作について説明する。図12(a)に示す回路となるように、図15のスイッチ5、スイッチ7、スイッチ9、スイッチ10をオンにして、昇圧容量C21、C22を電圧DDVDHで充電する。次に、図12(b)に示す回路となるように、スイッチ5、スイッチ7、スイッチ9、スイッチ10をオフにし、スイッチ11、スイッチ8をオンにして、昇圧容量C21とC22と、保持容量Cout1とを直列に接続すると同時に、スイッチSW12をオンにして、保持容量Cout3を充電する。

【0065】

次に、図13に示した回路の動作について説明する。図13(a)に示す回路となるように、図15のスイッチ1、スイッチ3をオンにして、昇圧容量C12を入力電源Vinで充電する。次に、スイッチ1、スイッチ3をオフにし、スイッチ2をオンにして極性を反転させ、さらにスイッチ14をオンにして保持容量Cout4を充電する。

【0066】

次に、図14に示した回路の動作について説明する。図14(a)に示す回路となるように、図15のスイッチ5、スイッチ7をオンにして、昇圧容量C21を電圧DDVDHで充電する。次に、スイッチ5、スイッチ7をオフにし、スイッチ6をオンにして極性を反転させ、さらにスイッチ15をオンにして保持容量Cout5を充電する。

【0067】

以上述べたように、図15に示す回路は、昇圧容量C12、C21、C22を時分割で兼用している。また、図16に示すように、昇圧容量C12、C21、C22は、スイッチSW1、SW3、SW5、SW7、SW9、SW10により繰り返し充電され、スイッチSW4、SW13、SW11、SW12により昇圧動作に使用されると共に、スイッチSW2、SW14、SW6、SW15により反転(昇圧)動作にも使用される。このように昇圧容量C12、C21、C22を時分割で兼用することで、外付けコンデンサの数が減少し、液晶表示装置の部品点数が削減される。

【0068】

次に、交流化駆動のための回路について説明する。図17は電源回路4に交流化駆動用回路を加えた構成を示す概略ブロック図である。符号81は対向電極電圧出力回路で、82は振幅調整回路で、83は保持容量信号出力回路で、84は第1レギュレータで、85は第2レギュレータで、86は内部基準電圧生成回路で、87は基準電圧出力回路で、Mは交流化信号入力端子である。

【0069】

交流化駆動を行う目的は、直流電圧が液晶に印加されることによる劣化を防止するためである。画素電極と対向電極との間に電圧を印加するアクティブマトリクス型液晶表示装置において、交流化駆動を行う一つの方法として、対向電極に一定周期毎に高電圧と低電圧とに変化する電圧を印加し、画素電極には対向電極に対して正極性、負極性の信号電圧を印加する、いわゆるコモン反転駆動方法が知られている。

【0070】

図17に示す回路では、コモン反転駆動が可能なように、対向電極電圧出力回路81は、一定周期で反転する電圧が出力可能に構成されている。対向電極電圧出力回路81には交流化信号線42により交流化信号が伝えられており、交流化信号により対向電極高レベル電圧VCOMHと対向電極低レベル電圧VCOMLが出力する。図18に対向電極高レベル電圧VCOMHと対向電極低レベル電圧VCOMLを有する対向電極電圧の出力波形を示す。

【0071】

対向電極が反転することに合わせて、保持容量信号の電圧も変動する必要がある。すなわち画素電極と対向電極との電位差により、表示階調が定まるために、対向電極の電圧が変動するタイミングと電圧幅に合わせて、保持容量信号の電圧も変動する必要がある。そこで、保持容量信号出力回路83にも交流化信号が伝えられ、変動する電圧幅は振幅調整回路82により定められ、基準電圧幅を示す電圧が、保持容量信号出力回路83に伝えられる。

【0072】

なお、振幅調整回路82で基準電圧幅を定め、対向電極電圧出力回路81と保持容量信号出力回路83とに伝えることで、図18に示す波形のように、保持容量信号出力回路83からの電圧振幅を対向電極電圧出力回路81からの電圧振幅に合わせることが可能になる。

【0073】

図17に示す回路では、第1レギュレータ84から、対向電極高レベル電圧VCOMHとして振幅調整回路82と対向電極電圧出力回路81の高レベル出力部81aに基準電圧が供給されている。振幅調整回路82では対向電極電圧として必要な振幅となるように、振幅基準電圧を作成し、対向電極高レベル電圧VCOMHから振幅基準電圧を減算することで、対向電極低レベル電圧VCOMLを作成し低レベル出力部81bに出力している。対向電極電圧出力回路81は交流化信号に従い、高レベル出力部81aと低レベル出力部81bとの接続を切換て、対向電極高レベル電圧VCOMHと対向電極低レベル電圧VCOMLを出力する。

【0074】

なお、対向電極電圧出力回路81と振幅調整回路82では、コントローラからの制御により、対向電極の基準電圧と振幅基準電圧の電圧値を変更可能になっている。また、調整用抵抗88が設けられており、液晶表示パネル毎の微調整が可能になっている。

【0075】

第2レギュレータ85からは、保持容量信号用に基準電圧が、保持容量信号低レベル電圧VSTGLとして振幅調整回路82と、保持容量信号出力回路83の低レベル出力部83bに供給されている。振幅調整回路82では振幅基準電圧を作成し、保持容量信号低レベル電圧VSTGLに振幅基準電圧を加算することで、保持容量信号高レベル電圧VSTGHを作成し高レベル出力部83aに出力している。保持容量信号出力回路83は交流化信号に従い、高レベル出力部83aと低レベル出力部83bとの接続を切換て、保持容量信号高レベル電圧VSTGHと保持容量信号低レベル電圧VSTGLを出力する。保持容量信号出力回路83の出力に接続している定電流素子89は電源オフ時の不要な表示を防止する回路である。定電流素子89の詳細については後述する。

【0076】

内部基準電圧生成回路86は、電池等から供給される外部電源電圧から入力電源Vinの電圧値を作成している。昇圧回路52、53では入力電源Vinをn倍しているが、内部基準電圧生成回路86では昇圧回路52、53から出力する電圧値に対して、入力電源Vinが最適な電圧となるように微調整が行われる。内部基準電圧生成回路86から出力する入力電源Vinは、基準電圧出力回路87で電流増幅され他の回路へ出力される。

【0077】

次に図19に、電源回路4に分配回路60の3つの分配スイッチング素子61を駆動するためのレベルシフト回路91とミラー用液晶パネル駆動回路93を設けた構成を示す。

【0078】

分配スイッチング素子61を駆動する信号は、例えばコントローラから信号が出力しているが、コントローラ等は比較的低電圧の信号で駆動しており、分配スイッチング素子61を駆動するためには、電圧レベルを変換する必要がある。そのため、電源回路4は外部から分配スイッチング素子61を駆動するタイミングを示す信号R、G、Bを入力し、第1のレベルシフト回路91で電圧レベルを変換して制御信号ROUT、GOUT、BOUTとして出力している。また、第2のレベルシフト回路92では走査信号線を駆動する駆動回路用にフレーム信号FLMとシフトクロックSFTCLKの電圧レベルを変換して、フレーム信号FLMOUTとシフトクロックSFTOUTとして出力している。

【0079】

なお、図19において符号94はレジスタ回路で、95はシリアルインターフェースである。シリアルインターフェース95はコントローラ等の外部から制御データを入力し、レジスタ94に保持する。レジスタ94に保持された制御データにより、第1レギュレータ84、第2レギュレータ85、振幅調整回路82等の制御が可能である。

【0080】

次に図20を用いて、ミラー用液晶について説明する。図20において符号1は液晶表示パネルで、表示に用いられる。液晶表示パネル1を観察する側には、ミラー用液晶パネル400が設けられている。ミラー用液晶パネル400は、透過偏光軸可変部410と、反射型偏光部420と、吸収型偏光部415とを有している。

【0081】

透過偏光軸可変部410は、入射した直線偏光の光が透過する際にその偏光軸を変化させる状態と、変化させない状態に制御が可能である。図20(a)のように、1対の基板411と基板412に形成した電極間に、電源416から電圧を印加していない場合では、入射した直線偏光の光はその偏光軸が変化し、反射型偏光部420を透過して液晶表示パネル1に到達する。逆に液晶表示パネル1から出射する光が、反射型偏光部420を透過する直線偏光であれば、液晶表示パネル1から出射する光は、ミラー用液晶パネル400を透過して観察者まで到達する。

【0082】

対して、図20(b)の基板411と基板412に形成した電極間に、電圧を印加した場合では、透過偏光軸可変部410に入射した直線偏光の光はその偏光軸が変化しないため、反射型偏光部420で反射する。また、液晶表示パネル1から出射した光は、反射型偏光部420を透過する直線偏光であれば、吸収型偏光部415で吸収され、観察者まで到達しない。

【0083】

なお、ミラー用液晶パネル400に印加する電圧は、液晶表示パネル1と同様に交流化駆動する。そのために、電源回路4にはミラー用液晶パネル駆動回路93が設けられ、ミラー用液晶パネル駆動信号MCLKが出力している。ミラー用液晶パネルは液晶に問題が発生しない程度に遅い周波数で駆動することが可能で、ミラー用液晶パネル駆動回路93は省電力のために、低周波駆動される。ただし、コントローラ等から送られてくる信号OSCは高周波のためミラー用液晶パネル駆動回路93は分周回路を備えている。

【0084】

次に電源回路4に設ける表示オフ時の発光を防止する回路について説明する。反射型の液晶表示パネルの場合に、保持容量に残っている電荷により、電源オフ時に一瞬発光する問題がある。透過型の液晶表示パネルの場合は、バックライトをオフとすることで発光を目立たなくすることが可能であるが、半透過型や反射型の液晶表示パネルでは発光が観察される。

【0085】

発光の原因は、画素部の薄膜トランジスタ10がオフ状態のため、画素電極12に溜まった電荷の行き場がなく、保持容量素子に印加された電圧が急に変化すると、画素電極と対向電極間の電圧が変化し、それが表示の変化として観察されるためである。特にノマリーブラックモードでは画素電極と対向電極間に電圧が印加すると、白表示となり目立つことになる。

【0086】

上記問題を解決するためには、保持容量に残っている電荷をゆっくりと放電する必要がある。図21に電荷をゆっくりと放電する場合の各電圧の変化の様子を示す。図21(a)は保持容量素子に高電圧の保持容量信号を供給する場合を示し、図21(b)は保持容量素子に走査信号を供給する場合を示す。

【0087】

図中符号Cで示すタイミングで、対向電極に出力する電圧を対向電極低レベル電圧VCOMLで出力停止し、保持容量素子に出力する電圧を図21(a)では保持容量信号低レベル電圧VSTGLで出力停止し、図21(b)では走査信号OFF低レベル電圧VGOFFLで出力を停止する。その後、図中符号A及びBに示すように保持容量素子に溜まった電荷を放電して、電圧を徐々にGND電位に近づける。

【0088】

このとき、保持容量素子の電圧の変化の割合は、変化率<(液晶閾値電圧/フレーム周期)の関係を満たす必要がある。フレーム周波数が60Hzの場合に、フレーム周期は17msで、液晶の閾値を0.5Vとすると、9Vの保持容量信号低レベル電圧VSTGLを306msで下げなくてはならない。電荷を徐々に放電するためには、保持容量信号線に定電流素子を接続することで可能である。前述したように、図17の保持容量信号出力回路83の出力には定電流素子89が接続されており、保持容量信号線の電圧を徐々に放電している。

【0089】

次に、図22に電源回路4の端子配置を示す。符号451は入力端子領域で、452は出力端子領域で、453は昇圧回路用端子領域である。出力端子領域452は駆動回路50側に設けられている。対して、接地電位線GNDは出力端子領域452と駆動回路50とを接続する配線32となるべく交差しないように配置されており、昇圧回路用端子領域453は接地電位線GNDとの間に、昇圧回路用コンデンサCout等を接続するため、接地電位線GND側に設けられている。

【0090】

【発明の効果】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

(1)本発明の液晶表示装置によれば、駆動回路の実装面積が小さく、駆動回路の配置が自由に選ぶことが可能となる。

(2)本発明の液晶表示装置によれば、外付け部品点数を少なくし、携帯に便利な電池を用いて駆動される液晶表示装置が実現可能となる。

【図面の簡単な説明】

【図1】本発明の実施の形態の液晶表示装置を示す概略ブロック図である。

【図2】本発明の実施の形態の液晶表示装置を示す概略ブロック図である。

【図3】本発明の実施の形態の液晶表示装置を示す概略ブロック図である。

【図4】本発明の実施の形態の液晶表示装置を示す概略ブロック図である。

【図5】本発明の実施の形態の液晶表示装置を示す概略ブロック図である。

【図6】本発明の実施の形態の液晶表示装置を示す概略ブロック図である。

【図7】本発明の実施の形態の液晶表示装置に用いられる駆動波形を示すタイミング図である。

【図8】本発明の実施の形態の液晶表示装置に用いられる昇圧回路を説明する概略回路図である。

【図9】本発明の実施の形態の液晶表示装置に用いられる昇圧回路を説明する概略回路図である。

【図10】本発明の実施の形態の液晶表示装置に用いられる昇圧回路を説明する概略回路図である。

【図11】本発明の実施の形態の液晶表示装置に用いられる昇圧回路を説明する概略回路図である。

【図12】本発明の実施の形態の液晶表示装置に用いられる昇圧回路を説明する概略回路図である。

【図13】本発明の実施の形態の液晶表示装置に用いられる昇圧回路を説明する概略回路図である。

【図14】本発明の実施の形態の液晶表示装置に用いられる昇圧回路を説明する概略回路図である。

【図15】本発明の実施の形態の液晶表示装置に用いられる昇圧回路を説明する概略回路図である。

【図16】本発明の実施の形態の液晶表示装置に用いられる昇圧回路の動作を説明するタイミング図である。

【図17】本発明の実施の形態の液晶表示装置に用いられる電源回路を説明する概略ブロック図である。

【図18】本発明の実施の形態の液晶表示装置に用いられる電源回路から出力する信号波形を説明するタイミング図である。

【図19】本発明の実施の形態の液晶表示装置に用いられる電源回路を説明する概略ブロック図である。

【図20】本発明の実施の形態の液晶表示装置に用いられるミラー用液晶パネルを説明する概略ブロック図である。

【図21】本発明の実施の形態の液晶表示装置に用いられる電源回路の動作を説明するタイミング図である。

【図22】本発明の実施の形態の液晶表示装置に用いられる電源回路の端子配置を説明する概略ブロック図である。

【符号の説明】

1…液晶表示パネル、2…TFT基板、3…コントローラ、4…電源回路、5…第1駆動回路、6…第2駆動回路、10…スイッチング素子(薄膜トランジスタ)、12…画素電極、13…保持容量素子、14…保持容量信号線、15…対向電極、30…フレキシブル基板、31…入力配線、32、33…配線、40…重なる領域、42…交流化信号線、50…駆動回路、51、52、53、54、55…昇圧回路、60…分配回路、61…分配スイッチング素子、62…分配制御信号、81…対向電極電圧出力回路、82…振幅調整回路、83…保持容量信号出力回路、84…第1レギュレータ、85…第2レギュレータ、86…内部基準電圧生成回路、87…基準電圧出力回路、91、92…レベルシフト回路、94…レジスタ回路、95…シリアルインターフェース、100…液晶表示パネル、400…ミラー用液晶パネル、410…透過偏光軸可変部、411、412…基板、415…吸収型偏光部、416…電源、420…反射型偏光部。

Claims (4)

- 第1の基板と、第2の基板と、

前記第1の基板と第2の基板の間に挟まれた液晶組成物と、

前記第1の基板に設けられた画素電極と、

前記画素電極に映像信号を供給するスイッチング素子と、

前記スイッチング素子に映像信号を供給する映像信号線と、

前記スイッチング素子を制御する走査信号を供給する走査信号線と、

前記第1の基板に電気的に接続された駆動回路とを有する液晶表示装置であって、

前記駆動回路は、前記走査信号の高電位側の電圧と、前記走査信号の低電位側の電圧と、

前記走査信号の高電位側の電圧よりも高い電圧とを生成する昇圧回路を有しており、

前記液晶表示装置の電源オフ時に、前記高い電圧を、定電流素子を用いることで、徐々にGND電位に近づけることを特徴とする液晶表示装置。 - 請求項1に記載の液晶表示装置において、

前記高い電圧は、前記第1の基板に設けられ、ソース領域とドレイン領域とが前記画素電極に電気的に接続されたMOSよりなる保持容量素子のゲート電極に供給されていることを特徴とする液晶表示装置。 - 第1の基板と、

前記第1の基板に設けられた複数の画素電極と、

前記スイッチング素子に映像信号を供給する映像信号線と、

前記スイッチング素子を制御する走査信号を供給する走査信号線と、

前記映像信号線と前記走査信号線とに接続されたスイッチング素子と、

前記第1の基板に電気的に接続された駆動回路とを有するTFT基板であって、

前記駆動回路は、前記走査信号の高電位側の電圧と、前記走査信号の低電位側の電圧と、

前記走査信号の高電位側の電圧よりも高い電圧とを生成する昇圧回路を有しており、

前記駆動回路の電源をオフにする際に、前記高い電圧を、定電流素子を用いることで、徐々にGND電位に近づけることを特徴とするTFT基板。 - 前記高い電圧は、前記第1の基板に設けられ、ソース領域とドレイン領域とが前記画素電極に電気的に接続されたMOSよりなる保持容量素子のゲート電極に供給されていることを特徴とする請求項3に記載のTFT基板。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002121634A JP3873003B2 (ja) | 2002-04-24 | 2002-04-24 | 液晶表示装置及びtft基板 |

| US10/411,110 US7307612B2 (en) | 2002-04-24 | 2003-04-11 | Liquid crystal display device having drive circuit |

| US11/889,747 US7999803B2 (en) | 2002-04-24 | 2007-08-16 | Liquid crystal display device having drive circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002121634A JP3873003B2 (ja) | 2002-04-24 | 2002-04-24 | 液晶表示装置及びtft基板 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003316328A JP2003316328A (ja) | 2003-11-07 |

| JP2003316328A5 JP2003316328A5 (ja) | 2005-02-03 |

| JP3873003B2 true JP3873003B2 (ja) | 2007-01-24 |

Family

ID=29243595

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002121634A Expired - Fee Related JP3873003B2 (ja) | 2002-04-24 | 2002-04-24 | 液晶表示装置及びtft基板 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7307612B2 (ja) |

| JP (1) | JP3873003B2 (ja) |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4027691B2 (ja) * | 2002-03-18 | 2007-12-26 | 株式会社日立製作所 | 液晶表示装置 |

| JP4744075B2 (ja) * | 2003-12-04 | 2011-08-10 | ルネサスエレクトロニクス株式会社 | 表示装置、その駆動回路およびその駆動方法 |

| TWI331743B (en) * | 2005-03-11 | 2010-10-11 | Chimei Innolux Corp | Driving system in a liquid crystal display |

| KR101119186B1 (ko) * | 2005-04-06 | 2012-03-20 | 삼성전자주식회사 | 표시패널, 이를 갖는 표시장치 및 이의 제조 방법 |

| US20070063952A1 (en) * | 2005-09-19 | 2007-03-22 | Toppoly Optoelectronics Corp. | Driving methods and devices using the same |

| KR101324756B1 (ko) | 2005-10-18 | 2013-11-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치 및 그의 구동방법 |

| JP5656321B2 (ja) * | 2005-10-18 | 2015-01-21 | 株式会社半導体エネルギー研究所 | 半導体装置、表示装置、表示モジュール及び電子機器 |

| JP2007219155A (ja) * | 2006-02-16 | 2007-08-30 | Seiko Epson Corp | 半導体集積回路 |

| JP2007333865A (ja) * | 2006-06-13 | 2007-12-27 | Epson Imaging Devices Corp | 液晶表示装置及び液晶表示装置のガンマ特性補正方法 |

| KR101281926B1 (ko) * | 2006-06-29 | 2013-07-03 | 엘지디스플레이 주식회사 | 액정표시장치 |

| TWI312219B (en) * | 2006-07-20 | 2009-07-11 | Holtek Semiconductor Inc | Power supply apparatus for field emission display |

| US8120261B2 (en) * | 2007-12-04 | 2012-02-21 | Samsung Mobile Display Co., Ltd. | Organic electroluminescence display and driving method thereof |

| KR100983392B1 (ko) * | 2008-08-19 | 2010-09-20 | 매그나칩 반도체 유한회사 | 칼럼 데이터 구동회로, 이를 구비한 표시장치 및 그의 구동방법 |

| KR101716781B1 (ko) * | 2010-08-20 | 2017-03-16 | 삼성디스플레이 주식회사 | 표시 장치 및 표시 장치의 전원 공급 방법 |

| JP2015069019A (ja) * | 2013-09-30 | 2015-04-13 | シナプティクス・ディスプレイ・デバイス株式会社 | 半導体装置 |

| JP6642595B2 (ja) | 2018-01-25 | 2020-02-05 | セイコーエプソン株式会社 | 電気光学装置、および電子機器 |

| TWI698846B (zh) * | 2019-03-22 | 2020-07-11 | 大陸商北京集創北方科技股份有限公司 | 具led開路檢測功能的led顯示驅動電路、led開路檢測方法及led顯示裝置 |

| JP7269139B2 (ja) * | 2019-08-30 | 2023-05-08 | 株式会社ジャパンディスプレイ | 表示装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09127556A (ja) | 1995-10-31 | 1997-05-16 | Sony Corp | 表示装置及びその駆動方法 |

| KR100280874B1 (ko) * | 1997-09-12 | 2001-02-01 | 구본준 | 액정패널 |

| JP2001051292A (ja) * | 1998-06-12 | 2001-02-23 | Semiconductor Energy Lab Co Ltd | 半導体装置および半導体表示装置 |

| JP2001109435A (ja) | 1999-10-05 | 2001-04-20 | Toshiba Corp | 表示装置 |

| ATE378669T1 (de) * | 2000-02-02 | 2007-11-15 | Seiko Epson Corp | Anzeigesteuergerät und anzeigevorrichtung zu dessen verwendung |

| TWI238375B (en) * | 2000-05-31 | 2005-08-21 | Toshiba Corp | Pumping circuit and flat panel display device |

| JP3630116B2 (ja) * | 2000-08-10 | 2005-03-16 | セイコーエプソン株式会社 | 電気光学ユニットおよび電子機器 |

| CN1394320A (zh) * | 2000-10-27 | 2003-01-29 | 松下电器产业株式会社 | 显示器件 |

-

2002

- 2002-04-24 JP JP2002121634A patent/JP3873003B2/ja not_active Expired - Fee Related

-

2003

- 2003-04-11 US US10/411,110 patent/US7307612B2/en not_active Expired - Fee Related

-

2007

- 2007-08-16 US US11/889,747 patent/US7999803B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003316328A (ja) | 2003-11-07 |

| US20080252577A1 (en) | 2008-10-16 |

| US7307612B2 (en) | 2007-12-11 |

| US20030201991A1 (en) | 2003-10-30 |

| US7999803B2 (en) | 2011-08-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3854905B2 (ja) | 液晶表示装置 | |

| US7999803B2 (en) | Liquid crystal display device having drive circuit | |

| JP3959253B2 (ja) | 液晶表示装置及び携帯型表示装置 | |

| US7646369B2 (en) | Method of driving liquid crystal display device, liquid crystal display device,and electronic apparatus | |

| US7847759B2 (en) | Semiconductor circuit, driving circuit of electro-optical device, and electronic apparatus | |

| US20090027321A1 (en) | Method of driving liquid crystal display device, liquid crystal display device, and portable electronic apparatus | |

| US7839371B2 (en) | Liquid crystal display device, method of driving the same, and method of manufacturing the same | |

| JP2012088736A (ja) | 表示装置 | |

| JP2009122561A (ja) | 液晶表示装置 | |

| US8054393B2 (en) | Liquid crystal display device | |

| JP4204204B2 (ja) | アクティブマトリクス型表示装置 | |

| TW493157B (en) | Method for driving electro-optical panel, data line driving circuit thereof, electro-optical apparatus, and electronic equipment | |

| US8164551B2 (en) | Liquid crystal display device | |

| US20060262063A1 (en) | Display device | |

| JP5004386B2 (ja) | 表示装置及びその駆動方法 | |

| JP2010107739A (ja) | 液晶表示装置 | |

| JP2010113247A (ja) | 液晶表示装置 | |

| KR20080004851A (ko) | 액정 표시 장치 | |

| EP1239444A1 (en) | Liquid crystal display device and method for driving the same | |

| JP4278314B2 (ja) | アクティブマトリクス型表示装置 | |

| JP4419394B2 (ja) | 電気光学パネルの駆動方法及び駆動回路、これを用いた電気光学パネル、並びに電子機器 | |

| JP4963761B2 (ja) | 表示装置 | |

| JP4197852B2 (ja) | アクティブマトリクス型表示装置 | |

| JP4297629B2 (ja) | アクティブマトリクス型表示装置 | |

| JP2005070337A (ja) | 電気光学装置、電子機器、及び電気光学装置の電源制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040219 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040219 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040223 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20051027 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20051101 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051219 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20060331 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20060510 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060510 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20060530 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060721 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060628 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20060808 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061010 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061023 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3873003 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091027 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101027 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101027 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313121 Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111027 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121027 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121027 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131027 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |