JP3860795B2 - ローレベルとハイレベルとの間の振幅の交互変化によって(ask)変調される電圧を復調するための回路配置 - Google Patents

ローレベルとハイレベルとの間の振幅の交互変化によって(ask)変調される電圧を復調するための回路配置 Download PDFInfo

- Publication number

- JP3860795B2 JP3860795B2 JP2002580477A JP2002580477A JP3860795B2 JP 3860795 B2 JP3860795 B2 JP 3860795B2 JP 2002580477 A JP2002580477 A JP 2002580477A JP 2002580477 A JP2002580477 A JP 2002580477A JP 3860795 B2 JP3860795 B2 JP 3860795B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- charging

- voltage

- circuit arrangement

- arrangement according

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/02—Amplitude-modulated carrier systems, e.g. using on-off keying; Single sideband or vestigial sideband modulation

- H04L27/06—Demodulator circuits; Receiver circuits

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Digital Transmission Methods That Use Modulated Carrier Waves (AREA)

- Transceivers (AREA)

- Near-Field Transmission Systems (AREA)

Description

V2 第2の入力ノード

C1 キャパシタ

C2 キャパシタ

I1 電流ソース

I2 電流ソース

D1 整流回路

D2 整流回路

Y 出力ノード

S1 分断デバイス(スイッチ)

Claims (7)

- ローレベルとハイレベルとの間の振幅の交互変化によって(ASK)変調された電圧を復調するための回路配置であって、

高周波数入力(LB、LA)の下流にある整流回路(D1、D2;N4、N5)と、

該整流回路(D1、D2;N4、N5)の出力(Y)と並列に接続される第1の充電回路(C1,il;C1、P1)および第2の充電回路(C2、i2;C2、P0)であって、各回路は、充電電圧(V1、V2)を生成する、第1の充電回路(C1,il;C1、P1)および第2の充電回路((C2、i2;C2、P0)と、

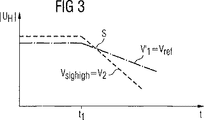

該充電電圧(V1、V2)と該整流回路(D1、D2;N4、N5)に対する入力電圧(UHF)との間に所定の割合が存在するときに、該充電電圧(V1、V2)を分断する分断デバイス(S1;N24、N25)と、

該充電電圧(V1、V2)の該割合から変調レベルを確かめるエバリュエーション回路と

を有する、回路配置。 - 前記充電回路は、フローティング電流ミラー回路(P1;P0)を有する、請求項1に記載の回路配置。

- 少なくとも1つの充電回路(C1、i1;C2、i2)の前記充電電圧(V1)は、変圧器(X%)を利用して変更される、請求項1に記載の回路配置。

- 前記第1および第2の充電回路(C1、i1;C2、i2)は、前記充電電圧(V1、V2)に対して所定の割合が存在するときに、ダイオード(D3;N11)を介して、互いに接続される、請求項1または2に記載の回路配置。

- 前記第2の充電回路は、該第2の充電回路によって提供される前記充電電圧(V2)を2つの異なる電圧(V2’、V2”)に変換する第1の分圧器(Y%)および第2の分圧器(Z%)を含む、請求項1〜4のいずれか一項に記載の回路配置。

- 前記第1および第2の充電回路は、異なる放電時間を有する、請求項1〜5のいずれか一項に記載の回路配置。

- 所定の程度の変調が識別された場合に充電電流増幅回路(P4、N1、N0、N2、P2)をオンにする転換装置(NA6)が設られている、請求項1〜6のいずれか一項に記載の回路配置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE2001116874 DE10116874A1 (de) | 2001-04-04 | 2001-04-04 | Schaltungsanordnung zur Demodulation in einer durch Wechsel der Amplitude zwischen einem niedrigen und einem hohen Pegel (ASK-) modulierten Spannung |

| DE2001116747 DE10116747B4 (de) | 2001-04-04 | 2001-04-04 | Schaltungsanordnung zur Demodulation einer durch Wechsel der Amplitude zwischen einem niedrigen und einem hohen Pegel (ASK-) modulierten Spannung |

| PCT/DE2002/000668 WO2002082634A2 (de) | 2001-04-04 | 2002-02-22 | Demoduliere für ämplitudenspungmodulierte (ask) signale |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004532564A JP2004532564A (ja) | 2004-10-21 |

| JP3860795B2 true JP3860795B2 (ja) | 2006-12-20 |

Family

ID=26009003

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002580477A Expired - Fee Related JP3860795B2 (ja) | 2001-04-04 | 2002-02-22 | ローレベルとハイレベルとの間の振幅の交互変化によって(ask)変調される電圧を復調するための回路配置 |

Country Status (12)

| Country | Link |

|---|---|

| US (1) | US6768373B2 (ja) |

| EP (1) | EP1374514B1 (ja) |

| JP (1) | JP3860795B2 (ja) |

| KR (1) | KR100556222B1 (ja) |

| CN (1) | CN1232085C (ja) |

| AT (1) | ATE463111T1 (ja) |

| BR (1) | BR0208564A (ja) |

| DE (1) | DE50214314D1 (ja) |

| MX (1) | MXPA03009074A (ja) |

| RU (1) | RU2252492C1 (ja) |

| TW (1) | TW569576B (ja) |

| WO (1) | WO2002082634A2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7545892B2 (en) | 2002-08-22 | 2009-06-09 | Infineon Technologies Ag | Method and circuit for controlling the input signal for a contactless transponder |

| WO2004021270A1 (de) * | 2002-08-22 | 2004-03-11 | Infineon Technologies Ag | Verfahren zum regeln des eingangssignals eines kontaktlos-transponders |

| TWI228895B (en) * | 2002-10-10 | 2005-03-01 | Infineon Technologies Ag | Circuit arrangement for analog/digital conversion of a voltage which is (ASK) modulated by alternating the amplitude between a low and a high level |

| FR2883434B1 (fr) * | 2005-03-21 | 2007-04-20 | Commissariat Energie Atomique | Methode et dispositif de demodulation a deux niveaux. |

| KR20220041367A (ko) | 2020-09-25 | 2022-04-01 | 삼성전자주식회사 | 정전기 보호 회로, 및 이를 포함하는 반도체 장치 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2751148B1 (fr) * | 1996-07-12 | 1998-09-18 | Inside Technologies | Demodulateur d'un signal alternatif module en amplitude recu dans une bobine par induction electromagnetique |

| ATE207224T1 (de) * | 1998-03-03 | 2001-11-15 | Infineon Technologies Ag | Datenträger zum kontaktlosen empfangen von amplitudenmodulierten signalen |

| UA54622C2 (uk) * | 1998-11-05 | 2003-03-17 | Інфінеон Текнолоджіз Аг | Спосіб демодуляції імодульованої шляхом зміни амплітуди між низьким і високим рівнями напруги і демодулятор для його здійснення |

-

2002

- 2002-02-22 CN CNB028077997A patent/CN1232085C/zh not_active Expired - Fee Related

- 2002-02-22 WO PCT/DE2002/000668 patent/WO2002082634A2/de active Application Filing

- 2002-02-22 AT AT02714060T patent/ATE463111T1/de active

- 2002-02-22 BR BR0208564-0A patent/BR0208564A/pt not_active IP Right Cessation

- 2002-02-22 JP JP2002580477A patent/JP3860795B2/ja not_active Expired - Fee Related

- 2002-02-22 EP EP02714060A patent/EP1374514B1/de not_active Expired - Lifetime

- 2002-02-22 RU RU2003132169/09A patent/RU2252492C1/ru not_active IP Right Cessation

- 2002-02-22 DE DE50214314T patent/DE50214314D1/de not_active Expired - Lifetime

- 2002-02-22 MX MXPA03009074A patent/MXPA03009074A/es active IP Right Grant

- 2002-02-22 KR KR1020037012809A patent/KR100556222B1/ko not_active IP Right Cessation

- 2002-03-06 TW TW091104119A patent/TW569576B/zh not_active IP Right Cessation

-

2003

- 2003-10-06 US US10/680,384 patent/US6768373B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| ATE463111T1 (de) | 2010-04-15 |

| CN1232085C (zh) | 2005-12-14 |

| US6768373B2 (en) | 2004-07-27 |

| US20040066227A1 (en) | 2004-04-08 |

| JP2004532564A (ja) | 2004-10-21 |

| BR0208564A (pt) | 2004-03-30 |

| CN1500332A (zh) | 2004-05-26 |

| MXPA03009074A (es) | 2004-02-27 |

| EP1374514A2 (de) | 2004-01-02 |

| EP1374514B1 (de) | 2010-03-31 |

| WO2002082634A3 (de) | 2003-04-10 |

| TW569576B (en) | 2004-01-01 |

| WO2002082634A2 (de) | 2002-10-17 |

| KR100556222B1 (ko) | 2006-03-03 |

| RU2252492C1 (ru) | 2005-05-20 |

| DE50214314D1 (de) | 2010-05-12 |

| KR20040008147A (ko) | 2004-01-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7853236B2 (en) | Rectifier circuit and RFID tag | |

| US7855595B2 (en) | High dynamic range ASK demodulator for use in an RFID transponder | |

| US11575305B2 (en) | Interface for passing control information over an isolation channel | |

| JP2003523147A (ja) | 分離バリアを通過して論理信号を送信するアイソレータ | |

| KR100411562B1 (ko) | Ask-복조 방법 및 ask-복조기 | |

| US11888658B2 (en) | Transmitter for dual communication over an isolation channel | |

| EP2280480A1 (en) | Low power regulated ampliflier in a transponder | |

| JP4263023B2 (ja) | 2線式データ通信方法、システム、コントロール装置およびデータ記憶装置 | |

| JP3860795B2 (ja) | ローレベルとハイレベルとの間の振幅の交互変化によって(ask)変調される電圧を復調するための回路配置 | |

| JP4721605B2 (ja) | 振幅変調された交流信号のための復調器 | |

| JP2006295319A (ja) | Ask復調回路 | |

| JP4062448B2 (ja) | ローレベルとハイレベルとの間の振幅を変更することによって(ask)変調される電圧のアナログ/デジタル変換のための回路構成物 | |

| JP3899388B2 (ja) | 半導体集積回路装置及びicカード | |

| US7400874B2 (en) | Integrated circuit comprising a clock-signal generator, smart card comprising an integrated circuit of this kind and associated method for the generation of clock signals | |

| JP7297453B2 (ja) | データスライサ及び受信装置 | |

| JP2009044774A (ja) | データ記憶装置 | |

| UA73652C2 (en) | Device for demodulating amplitude-shift keyed voltage signals | |

| JPH04319814A (ja) | パルス回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060119 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060124 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20060414 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20060510 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060724 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060824 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060922 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100929 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100929 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110929 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110929 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120929 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120929 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130929 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |