JP3829904B2 - 可変利得アンプ - Google Patents

可変利得アンプ Download PDFInfo

- Publication number

- JP3829904B2 JP3829904B2 JP20582699A JP20582699A JP3829904B2 JP 3829904 B2 JP3829904 B2 JP 3829904B2 JP 20582699 A JP20582699 A JP 20582699A JP 20582699 A JP20582699 A JP 20582699A JP 3829904 B2 JP3829904 B2 JP 3829904B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- attenuator

- parallel

- resistor

- circuits

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Control Of Amplification And Gain Control (AREA)

- Amplifiers (AREA)

- Circuits Of Receivers In General (AREA)

Description

【発明の属する技術分野】

この発明は可変利得アンプに関する。

【0002】

【従来の技術】

デジタル音声放送として、ヨーロッパではDAB(Eureka147規格にしたがったデジタル音声放送)が採用され、日本ではISDB−Tが提案されている。

【0003】

そして、ISDB−Tは、

伝送帯域幅:432 kHz(狭帯域ISDB−Tのとき)

変調方式 :OFDM

多重方式 :MPEG2

を採用することにより、複数チャンネルのデジタルオーディオデータやデジタルデータを同時に放送するものである。

【0004】

なお、放送に使用する周波数帯は、狭帯域ISDB−Tのとき、88MHz〜108 MHzおよび170 MHz〜222 MHzが予定されている。

【0005】

【発明が解決しようとする課題】

ところで、AM受信機にはAGC回路が設けられ、AM検波出力のレベルが受信電界強度にかかわらず一定となるように制御されている。すなわち、高周波信号あるいは中間周波信号の信号ラインに、可変利得アンプが設けられ、その利得が、AM検波出力に含まれる直流電圧(AGC電圧)によりフィードバック制御されている。

【0006】

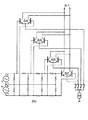

そして、可変利得アンプとして、例えば図4あるいは図5に示すような回路がある。すなわち、図4の回路は、高利得のアンプA11と、アッテネータ回路A12とを選択的に動作させることより、可変利得アンプを構成している。また、図5の回路は、抵抗ラダー回路A13の各段の出力を差動アンプA14〜A17により選択して取り出すようにして、可変利得アンプを構成している。

【0007】

ところが、図4の可変利得アンプの場合には、アンプA11およびアッテネータ回路A12により、利得を高低2段に切り換えられるだけであり、利得の変更やダイナミックレンジの拡大を円滑に行うことができない。

【0008】

その点、図5の可変利得アンプの場合には、利得を円滑に変更することができるが、差動アンプA14〜A17の入力容量の影響をなくすには、抵抗ラダー回路A13の抵抗器の値を、差動アンプA14〜A17の入力容量の示すインピーダンスに比べ、十分に小さく、例えば、50Ω〜200 Ω程度にする必要がある。しかし、そのようにすると、抵抗ラダー回路A13の抵抗器により発生するノイズが無視できなくなり、NF(ノイズフィギュア)が悪くなってしまう。

【0009】

さらに、可変利得アンプを上述したようなデジタル音声放送の受信機のAGC回路に使用する場合には、可変利得アンプは低歪みであることも要求される。すなわち、DABやISDB−Tでは、1つの放送波が複数のキャリア信号から構成されている。例えば、狭帯域ISDB−Tの場合、放送波は、モード1のときには、4kHzおきに分布する109 個のキャリア信号から構成され、モード2のときには、1kHzおきに分布する433 個のキャリア信号から構成されている。

【0010】

したがって、デジタル音声放送の受信機において、可変利得アンプの直線性が悪いと、その可変利得アンプを通過する受信信号や中間周波信号に歪みを生じてしまい、その歪み成分が本来のキャリア信号と区別のつかないことがある。したがって、デジタル音声放送の受信機のAGC回路に使用される可変利得アンプには、歪みの発生の少ないことも要求される。

【0011】

この発明は、以上のような問題点を解決しようとするものである。

【0012】

【課題を解決するための手段】

この発明においては、

入力信号に対して縦続接続された複数のアッテネータ回路と、

この複数のアッテネータ回路よりも1つ多い複数の差動アンプと、

この複数の差動アンプの出力端に共通に接続された取り出し回路と

を有し、

上記複数のアッテネータ回路のそれぞれは、

第1の抵抗器および第1のコンデンサが並列接続された第1の並列回路と、

第2の抵抗器および第2のコンデンサが並列接続された第2の並列回路と、

第3の抵抗器および第3のコンデンサが並列接続された第3の並列回路と、

第4の抵抗器および第4のコンデンサが並列接続された第4の並列回路と

が、この順に直列接続されるとともに、

上記第1〜第4の並列回路の直列接続の両端が入力端とされ、

上記第2および第3の並列回路の直列接続の両端が出力端とされて

バランス型に構成され、

上記複数のアッテネータ回路のうち、第1段目のアッテネータ回路の入力端に上記入力信号が供給されるとともに、

上記複数のアッテネータ回路のうち、第2段目以降のアッテネータ回路の入力端が、前段のアッテネータ回路の出力端にそれぞれ接続され、

上記複数の差動アンプのうち、第1の差動アンプの入力端が、上記第1段目のアッテネータ回路の入力端に接続され、

上記複数の差動アンプのうち、残る差動アンプの入力端が、上記複数のアッテネータ回路の出力端にそれぞれ接続され、

上記複数のアッテネータ回路のそれぞれにおける上記第2の並列回路と第3の並列回路との接続点が共通に接続されるとともに、

上記第2の並列回路と第3の並列回路とが共通に接続された接続点に上記複数の差動アンプのバイアス電圧が供給され、

上記複数のアッテネータ回路のそれぞれにおいて、

上記第1の抵抗器および上記第1のコンデンサのCR積と、上記第2の抵抗器および上記第2のコンデンサのCR積とが等しくされるとともに、

上記第3の抵抗器および上記第3のコンデンサのCR積と、上記第4の抵抗器および上記第4のコンデンサのCR積とが等しくされ、

制御電圧により上記複数の差動アンプを選択的に動作状態に制御して上記取り出し回路から上記動作状態に制御した差動アンプの出力信号を取り出す

ようにした可変利得アンプ

とするものである。

【0013】

【発明の実施の形態】

[ISDB−T受信機]

ISDB−T受信機は、例えば図1に示すように構成される。なお、図1は、狭帯域ISDB−T用の受信機の場合であり、ダイレクトコンバージョン方式に構成された場合である。

【0014】

すなわち、狭帯域ISDB−Tの放送波がアンテナ11により受信され、この受信信号が電子同調方式のアンテナ同調回路12に供給されて目的とする周波数の受信信号S12が取り出され、この信号S12がAGC用の可変利得アンプ13および電子同調方式の段間同調回路14を通じてミキサ回路15A、15Bに供給される。

【0015】

また、PLL21において受信信号S12のキャリア周波数(中心周波数)の2倍の周波数の発振信号が形成され、この発振信号が分周回路22に供給されて受信信号S12のキャリア周波数に等しく、かつ、位相が互いに90°異なる2つの信号に分周され、この分周信号がミキサ回路15A、15Bに局部発振信号として供給される。

【0016】

こうして、ミキサ回路15A、15Bにおいて、受信信号S12は位相が互いに90°異なるベースバンド信号S15A 、S15B 、すなわち、I軸およびQ軸のベースバンド信号S15A 、S15B に周波数変換される。

【0017】

なお、このとき、PLL21から、そのVCO(図示せず)の可変容量ダイオードに供給される制御電圧の一部が取り出され、この制御電圧が同調回路12、14に同調電圧として供給され、受信信号S12に対する同調が実現される。

【0018】

そして、ミキサ回路15A、15Bからの信号S15A 、S15B が、ローパスフィルタ16A、16B→AGC用の可変利得アンプ17A、17B→ローパスフィルタ18A、18Bの信号ラインを通じて復調回路19に供給される。この復調回路19は、図示はしないが、ISDB−Tの送信時の変調処理に対応して、複素フーリエ変換、周波数デインターリーブ、タイム・デインターリーブ、複数のチャンネルのうちの目的とするチャンネルのデジタルオーディオデータの選択、エラー訂正およびデータ伸長などの復調処理を行うものである。

【0019】

したがって、復調回路19からは、複数の番組(チャンネル)のうちの目的とする番組のオーディオ信号L、Rが取り出される。

【0020】

また、このとき、ローパスフィルタ18A、18Bからの信号S15A 、S15B がAGC検波回路25に供給されてAGC電圧V25が形成され、このAGC電圧V25が可変利得アンプ17A、17Bに利得の制御信号として供給される。

【0021】

さらに、ミキサ回路15A、15Bからの信号S15A 、S15B がAGC検波回路23に供給されて遅延AGC電圧V23が形成され、このAGC電圧V23が加算回路24に供給されるとともに、AGC電圧V25が加算回路24に供給される。そして、加算回路24からはAGC電圧V23、V25の加算電圧V24が取り出され、この電圧V24が可変利得アンプ13に利得の制御信号として供給される。

【0022】

したがって、AGC電圧V24により同調回路12からの受信信号S12に対してAGCが行われるとともに、AGC電圧V25によりローパスフィルタ16A、16Bからのベースバンド信号S15A 、S15B に対してAGCが行われる。そして、このとき、AGC電圧V24は、遅延AGC電圧V23とAGC電圧V25との加算電圧であるから、受信信号S12に対するAGC範囲を拡大することができる。

【0023】

また、この受信機は、同調回路12、14、PLL21のVCOの共振回路および復調回路19を除いて、1チップIC化することができる。

【0024】

[可変利得アンプ]

可変利得アンプ13は、例えば図2に示すように、縦続接続された例えば3つのアッテネータ回路31〜33と、その入力および各出力を選択的に取り出す差動アンプ41〜44と、カスコードアンプ51、52とから構成される。

【0025】

すなわち、図2の可変利得アンプ13においては、同調回路12の同調コイル(図示せず)の2次コイルL12に抵抗器R01〜R03の直列回路が接続され、同調回路12からは受信信号S12がバランス型に取り出される。また、このとき、同調回路12の出力インピーダンスは、例えば50Ωとされる。

【0026】

そして、アッテネータ回路31〜33は、バランス型のラダーアッテネータ回路30を構成しているものでもあり、同調回路12の出力端、すなわち、抵抗器R02の両端間に、抵抗器R11、R12、R14、R13の直列回路が接続されるとともに、これら抵抗器R11、R12、R14、R13にコンデンサC11、C12、C14、C13がそれぞれ並列接続される。こうして、素子R11〜R14、C11〜C14により第1段目のバランス型アッテネータ回路31が構成される。

【0027】

また、抵抗器R12、R14の直列回路の両端間に、抵抗器R21、R22、R24、R23の直列回路が接続されるとともに、これら抵抗器R21、R22、R24、R23にコンデンサC21、C22、C24、C23がそれぞれ並列接続される。こうして、素子R21〜R24、C21〜C24により第2段目のバランス型アッテネータ回路32が構成される。

【0028】

さらに、抵抗器R22、R24の直列回路の両端間に、抵抗器R31、R32、R34、R33の直列回路が接続されるとともに、これら抵抗器R31、R32、R34、R33にコンデンサC31、C32、C34、C33がそれぞれ並列接続される。こうして、素子R31〜R34、C31〜C34により第3段目のバランス型アッテネータ回路33が構成される。

【0029】

したがって、アッテネータ回路31〜33によりラダーアッテネータ回路30が構成されたことになるが、この場合、

C11・R11=C12・R12、C13・R13=C14・R14

C21・R21=C22・R22、C23・R23=C24・R24

C31・R31=C32・R32、C33・R33=C34・R34

とされる。

【0030】

また、各アッテネータ回路31〜33の減衰量を等しくする場合には、

R11=R13=R21=R23=R31=R33

R12=R14=R22=R24

R32=R34=R12/2

C11=C13=C21=C23=C31=C33

C12=C14=C22=C24

C32=C34=2・C12

とされる。

【0031】

さらに、各アッテネータ回路31〜33の減衰量を1/n〔倍〕(ただし、n>1)とすれば、

R12/R11=2/(n−1)

C11/C12=2/(n−1)

とされる。

【0032】

そして、トランジスタQ11、Q12のエミッタが、定電流源用のトランジスタQ13のコレクタに共通に接続され、そのエミッタが接地に接続されて差動アンプ41が構成される。そして、トランジスタQ11、Q12のベースが、抵抗器R02の両端にそれぞれ接続され、抵抗器R12、R14の接続中点と、抵抗器R22、R24の接続中点と、抵抗器R32、R34の接続中点とが互いに接続されるとともに、この接続中点と、接地との間に、直流バイアス電源VBBが接続される。

【0033】

また、トランジスタQ21、Q22のエミッタが、トランジスタQ23のコレクタに共通に接続され、そのエミッタが接地に接続されて差動アンプ42が構成され、トランジスタQ21、Q22のベースがアッテネータ回路31の出力端にそれぞれ接続される。

【0034】

さらに、トランジスタQ31、Q32、Q33およびQ41、Q42、Q43により同様に差動アンプ43および44が構成され、トランジスタQ31、Q32のベースがアッテネータ回路32の出力端に接続され、トランジスタQ41、Q42のベースがアッテネータ回路33の出力端に接続される。

【0035】

そして、制御電圧形成回路60において、AGC電圧V24から所定の制御電圧VB1〜VB4が形成され、これら制御電圧VB1〜VB4がトランジスタQ13、Q23、Q33、Q43のベースにそれぞれ供給される。

【0036】

この場合、これら制御電圧VB1〜VB4は、AGC電圧V24に対応して変化するものであり、所定の電圧レベルをVL 、VM 、VH (ただし、VL <VM <VH )とすると、

▲1▼ V24<VL のとき、トランジスタQ13だけをオンにする。

▲2▼ VL ≦V24<VM のとき、トランジスタQ23だけをオンにする。

▲3▼ VM ≦V24<VH のとき、トランジスタQ33だけをオンにする。

▲4▼ VH ≦V24 のとき、トランジスタQ43だけをオンにする。

のように変化するものである。

【0037】

そして、トランジスタQ11、Q21、Q31、Q41のコレクタが、ベース接地のトランジスタQ51のエミッタに接続されてカスコードアンプ51が構成され、トランジスタQ12、Q22、Q32、Q42のコレクタが、ベース接地のトランジスタQ52のエミッタに接続されてカスコードアンプ52が構成され、トランジスタQ51、Q52のコレクタ出力が次段の同調回路14に供給される。

【0038】

このような構成によれば、同調回路12から受信信号S12が出力されると、この信号S12はアッテネータ回路31〜33により所定量ずつ順に減衰され、したがって、アッテネータ回路31〜33からは順にレベルが小さくされた受信信号S12が出力される。

【0039】

そして、直流バイアス電源VBBからのバイアス電圧が、抵抗器R11〜R34を通じてトランジスタQ11〜Q42のベースに供給されるが、AGC電圧V24が▲1▼の場合には、制御電圧VB1によりトランジスタQ13だけがオンとなって定電流源として動作する。したがって、▲1▼の場合には、差動アンプ41〜44のうち、差動アンプ41だけが有効に動作することになり、トランジスタQ11、Q12と、トランジスタQ51、Q52とが、カスコードアンプ51、52を構成することになる。

【0040】

したがって、▲1▼の場合には、同調回路12から出力される受信信号S12が、差動アンプ41により選択されるとともに、カスコードアンプ51、52を通じて次段へと出力される。

【0041】

また、AGC電圧V24が▲2▼の場合には、制御電圧VB2によりトランジスタQ23だけがオンとなって定電流源として動作するので、差動アンプ41〜44のうち、差動アンプ42だけが有効に動作する。したがって、第1段目のアッテネータ回路31から出力される受信信号S12が、差動アンプ42により選択されるとともに、カスコードアンプ51、52を通じて次段へと出力される。

【0042】

さらに、AGC電圧V24が▲3▼の場合には、制御電圧VB3によりトランジスタQ33だけがオンとなり、差動アンプ43だけが有効に動作する。したがって、第2段目のアッテネータ回路32から出力される受信信号S12が、差動アンプ43により選択されるとともに、カスコードアンプ51、52を通じて出力される。

【0043】

そして、AGC電圧V24が▲4▼の場合には、制御電圧VB4により差動アンプ44だけが有効に動作するので、第3段目のアッテネータ回路33から出力される受信信号S12が、差動アンプ44により選択されるとともに、カスコードアンプ51、52を通じて出力される。

【0044】

こうして、図2の回路によれば、同調回路12および各アッテネータ回路31〜33の出力信号が、AGC電圧V24にしたがって差動アンプ41〜44により選択され、カスコードアンプ51、52を通じて取り出される。したがって、この図2の回路は利得が4ステップに切り換わる可変利得アンプ13として動作していることになる。また、このとき、AGCが行われることになる。

【0045】

そして、その場合、アッテネータ回路31〜33においては、コンデンサC11〜C34によっても信号の分圧ないし減衰が行われるので、抵抗器R11〜R34の値を、同調回路12の出力インピーダンス50Ωに比べて十分に高く、例えば1.25kΩと高くすることができ、したがって、抵抗器R11〜R34によりNFが悪化することがなく、ノイズの少ない可変利得アンプとすることができる。

【0046】

また、同調回路12およびアッテネータ回路31〜33の出力信号のうち適正なレベルの受信信号S12を差動アンプ41〜44により選択して取り出しているので、歪みの発生を抑えることができる。

【0047】

さらに、コンデンサC11〜C34の値に、トランジスタQ11〜Q42の入力容量を加味することにより、その入力容量を無視することができる。また、C11・R11=C12・R12、C13・R13=C14・R14(他のCR積も同様)とすることにより、周波数特性を平坦にすることもできる。したがって、周波数特性を広帯域化することができる。

【0048】

また、直流バイアス電源VBBからのバイアス電圧は、抵抗器R11〜R34を通じてトランジスタQ11〜Q42に供給されるので、トランジスタQ11〜Q42にバイアス電圧を供給するための回路を新たに設ける必要がない。

【0049】

さらに、IC化もできる。また、可変利得アンプ13の処理する受信信号S12の周波数を、使用する素子のCR積により決まる周波数よりも遥かに高くすることができ、その場合には、アッテネータ回路31〜33の減衰量はコンデンサC11〜C34の容量比だけで決まるので、トランジスタQ11〜Q42の入力容量を補正するだけでよい。

【0050】

[ISDB−T受信機の他の例]

図3は、狭帯域ISDB−T用の受信機がスーパーヘテロダイン方式に構成されている場合である。

【0051】

すなわち、狭帯域ISDB−Tの放送波がアンテナ11により受信され、この受信信号が電子同調方式のアンテナ同調回路12に供給されて目的とする周波数の受信信号S12が取り出され、この信号S12がAGC用の可変利得アンプ13および電子同調方式の段間同調回路14を通じてミキサ回路15A、15Bに供給される。

【0052】

また、PLL21において所定の周波数の発振信号が形成され、この発振信号が分周回路22に供給されて受信信号S12のキャリア周波数(中心周波数)よりも例えば500 kHzだけ高く、かつ、位相が互いに90°異なる2つの信号に分周され、この分周信号がミキサ回路15A、15Bに局部発振信号として供給される。

【0053】

こうして、ミキサ回路15A、15Bにおいて、受信信号S12は位相が互いに90°異なる2つの中間周波信号S15A 、S15B (中間周波数は500 kHz)に周波数変換される。

【0054】

なお、このとき、PLL21から、そのVCO(図示せず)の可変容量ダイオードに供給される制御電圧の一部が取り出され、この制御電圧が同調回路12、14に同調電圧として供給され、受信信号S12に対する同調が実現される。

【0055】

そして、ミキサ回路15A、15Bからの中間周波信号S15A 、S15B が、ローパスフィルタ16A、16BおよびAGC用の可変利得アンプ17A、17Bを通じて移相回路26A、26Bに供給され、この移相回路26A、26Bにおいて、例えば、中間周波信号S15A 、S15B に含まれる本来の信号成分が同相となり、かつ、イメージ成分が逆相となるように移相される。そして、この移相後の中間周波信号S15A 、S15B が加算回路27に供給され、加算回路27からは、イメージ成分が相殺され、本来の信号成分を有する中間周波信号S15が取り出される。

【0056】

続いて、この中間周波信号S15が、中間周波フィルタ用のバンドパスフィルタ28→AGC用の可変利得アンプ17→ローパスフィルタ18の信号ラインを通じて復調回路19に供給され、復調回路19からは、複数の番組のうちの目的とする番組のオーディオ信号L、Rが取り出される。

【0057】

また、このとき、ローパスフィルタ18からの中間周波信号S15がAGC検波回路25に供給されてAGC電圧V25が形成され、このAGC電圧V25が可変利得アンプ17に利得の制御信号として供給される。

【0058】

さらに、ローパスフィルタ16A、16Bからの中間周波信号S16A 、S16B がAGC検波回路23に供給されて遅延AGC電圧V23が形成され、このAGC電圧V23が加算回路24に供給されるとともに、AGC電圧V25が加算回路24に供給される。そして、加算回路24からはAGC電圧V23、V25の加算電圧V24が取り出され、この電圧V24が可変利得アンプ13に利得の制御信号として供給される。

【0059】

したがって、AGC電圧V24により同調回路12からの受信信号S12に対してAGCが行われるとともに、AGC電圧V25によりバンドパスフィルタ28からの中間周波信号S15に対してAGCが行われる。そして、このとき、AGC電圧V24は、遅延AGC電圧V23とAGC電圧V25との加算電圧であるから、受信信号S12に対するAGC範囲を拡大することができる。

【0060】

そして、この受信機においても、可変利得アンプ13を例えば図2に示すように構成することができるとともに、IC化ができる。

【0061】

【発明の効果】

この発明によれば、ノイズの少ない可変利得アンプとすることができる。また、直線性が良好であり、歪みの発生が少ない。さらに、出力信号を選択して取り出すためのアンプのバイアス回路を簡単化ないし省略することができる。

【0062】

また、その選択用のアンプのトランジスタの入力容量を無視することができるとともに、周波数特性を平坦にすることもでき、したがって、周波数特性を広帯域化することができる。

【図面の簡単な説明】

【図1】この発明の一形態を示す系統図である。

【図2】この発明の一形態を示す接続図である。

【図3】この発明の一形態を示す系統図である。

【図4】この発明を説明するための接続図である。

【図5】この発明を説明するための接続図である。

【符号の説明】

11…アンテナ、12…同調回路、13…可変利得アンプ、14…同調回路、15A、15B…ミキサ回路、16A、16B…ローパスフィルタ、17A、17B…可変利得アンプ、18A、18B…ローパスフィルタ、19…復調回路、21…PLL、22…分周回路、23…AGC検波回路、24…加算回路、25…AGC検波回路、26A、26B…移相回路、27…加算回路、28…バンドパスフィルタ、30…ラダーアッテネータ回路、31〜33…アッテネータ回路、40…取り出し回路、41〜44…差動アンプ、51、52…カスコードアンプ、60…制御電圧形成回路

Claims (1)

- 入力信号に対して縦続接続された複数のアッテネータ回路と、

この複数のアッテネータ回路よりも1つ多い複数の差動アンプと、

この複数の差動アンプの出力端に共通に接続された取り出し回路と

を有し、

上記複数のアッテネータ回路のそれぞれは、

第1の抵抗器および第1のコンデンサが並列接続された第1の並列回路と、

第2の抵抗器および第2のコンデンサが並列接続された第2の並列回路と、

第3の抵抗器および第3のコンデンサが並列接続された第3の並列回路と、

第4の抵抗器および第4のコンデンサが並列接続された第4の並列回路と

が、この順に直列接続されるとともに、

上記第1〜第4の並列回路の直列接続の両端が入力端とされ、

上記第2および第3の並列回路の直列接続の両端が出力端とされて

バランス型に構成され、

上記複数のアッテネータ回路のうち、第1段目のアッテネータ回路の入力端に上記入力信号が供給されるとともに、

上記複数のアッテネータ回路のうち、第2段目以降のアッテネータ回路の入力端が、前段のアッテネータ回路の出力端にそれぞれ接続され、

上記複数の差動アンプのうち、第1の差動アンプの入力端が、上記第1段目のアッテネータ回路の入力端に接続され、

上記複数の差動アンプのうち、残る差動アンプの入力端が、上記複数のアッテネータ回路の出力端にそれぞれ接続され、

上記複数のアッテネータ回路のそれぞれにおける上記第2の並列回路と第3の並列回路との接続点が共通に接続されるとともに、

上記第2の並列回路と第3の並列回路とが共通に接続された接続点に上記複数の差動アンプのバイアス電圧が供給され、

上記複数のアッテネータ回路のそれぞれにおいて、

上記第1の抵抗器および上記第1のコンデンサのCR積と、上記第2の抵抗器および上記第2のコンデンサのCR積とが等しくされるとともに、

上記第3の抵抗器および上記第3のコンデンサのCR積と、上記第4の抵抗器および上記第4のコンデンサのCR積とが等しくされ、

制御電圧により上記複数の差動アンプを選択的に動作状態に制御して上記取り出し回路から上記動作状態に制御した差動アンプの出力信号を取り出す

ようにした可変利得アンプ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP20582699A JP3829904B2 (ja) | 1999-07-21 | 1999-07-21 | 可変利得アンプ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP20582699A JP3829904B2 (ja) | 1999-07-21 | 1999-07-21 | 可変利得アンプ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001036367A JP2001036367A (ja) | 2001-02-09 |

| JP2001036367A5 JP2001036367A5 (ja) | 2005-06-16 |

| JP3829904B2 true JP3829904B2 (ja) | 2006-10-04 |

Family

ID=16513359

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP20582699A Expired - Fee Related JP3829904B2 (ja) | 1999-07-21 | 1999-07-21 | 可変利得アンプ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3829904B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3770819B2 (ja) | 2001-09-28 | 2006-04-26 | 株式会社ルネサステクノロジ | 無線通信受信装置 |

| US6687491B2 (en) * | 2002-01-18 | 2004-02-03 | Sony Corporation | Direct conversion of low power high linearity receiver |

| JP5252212B2 (ja) * | 2009-03-12 | 2013-07-31 | ルネサスエレクトロニクス株式会社 | 信号増幅用半導体装置 |

| CN110336579A (zh) * | 2019-07-16 | 2019-10-15 | 武汉磐索地勘科技有限公司 | 级联式无缆探杆通信方法及电路 |

-

1999

- 1999-07-21 JP JP20582699A patent/JP3829904B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001036367A (ja) | 2001-02-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3263395B2 (ja) | 利得制御増幅器 | |

| US6160572A (en) | Tuner for cable modem | |

| KR0151379B1 (ko) | 동조 가능한 공진 증폭기, 주파수 합성회로 및 슈퍼헤테로다인 fm 수신기 | |

| US20070140391A1 (en) | Rf complex bandpass-notch filter for rf receiver and tv tuner | |

| US8159619B2 (en) | Multi-standard integrated television receiver | |

| JPH0677853A (ja) | Fm受信機 | |

| JP2001077648A (ja) | ポリフェイズフィルタおよびこれを使用した受信機 | |

| US5122879A (en) | Television synchronous receiver with phase shifter for reducing interference from a lower adjacent channel | |

| US20040116096A1 (en) | Radio frequency receiver architecture with tracking image-reject polyphase filtering | |

| CA2129854C (en) | Parallel untuned video if amplifiers supplied signals from tv 1st detector via respective input filters | |

| JP3952114B2 (ja) | 可変利得アンプ | |

| JP2002027341A (ja) | テレビジョンチューナ | |

| KR0183114B1 (ko) | 모놀리식 집적회로내에서 구현되는 제2검파기 및 중간 주파수 증폭기 | |

| JP2008160672A (ja) | ミキサ回路の入力回路 | |

| JP3829904B2 (ja) | 可変利得アンプ | |

| JP2001502514A (ja) | 非対称側波帯を有する変調キャリヤの受信 | |

| US20070093228A1 (en) | Method and system for image rejection by using post mixer I/Q equalization | |

| JP2001053564A (ja) | 電流切り換え回路、可変利得アンプおよび受信機 | |

| US7233368B2 (en) | Down-converter | |

| JP3600075B2 (ja) | テレビジョンチューナ | |

| JP3955987B2 (ja) | 可変利得アンプおよび受信機 | |

| JP4820764B2 (ja) | 利得制御フィルタ装置、利得制御複素フィルタ装置および受信装置 | |

| JP4087684B2 (ja) | 通信用半導体集積回路およびアンプのオフセット補正方法 | |

| JPH07240663A (ja) | アクティブフィルタ回路 | |

| JP4248637B2 (ja) | ケーブルモデム用チューナ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040910 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040910 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20040910 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20050112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050126 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050328 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20051005 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051031 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060621 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060704 |

|

| LAPS | Cancellation because of no payment of annual fees |