JP3813614B2 - エラー補正回路およびa/dコンバータ - Google Patents

エラー補正回路およびa/dコンバータ Download PDFInfo

- Publication number

- JP3813614B2 JP3813614B2 JP2004020922A JP2004020922A JP3813614B2 JP 3813614 B2 JP3813614 B2 JP 3813614B2 JP 2004020922 A JP2004020922 A JP 2004020922A JP 2004020922 A JP2004020922 A JP 2004020922A JP 3813614 B2 JP3813614 B2 JP 3813614B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- folding

- output

- converter

- bits

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000006243 chemical reaction Methods 0.000 claims description 66

- 238000010586 diagram Methods 0.000 description 9

- 238000001514 detection method Methods 0.000 description 2

- 102100028918 Catenin alpha-3 Human genes 0.000 description 1

- 101000916179 Homo sapiens Catenin alpha-3 Proteins 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/06—Continuously compensating for, or preventing, undesired influence of physical parameters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/06—Continuously compensating for, or preventing, undesired influence of physical parameters

- H03M1/0617—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by the use of methods or means not specific to a particular type of detrimental influence

- H03M1/0634—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by the use of methods or means not specific to a particular type of detrimental influence by averaging out the errors, e.g. using sliding scale

- H03M1/0636—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by the use of methods or means not specific to a particular type of detrimental influence by averaging out the errors, e.g. using sliding scale in the amplitude domain

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/34—Analogue value compared with reference values

- H03M1/36—Analogue value compared with reference values simultaneously only, i.e. parallel type

- H03M1/368—Analogue value compared with reference values simultaneously only, i.e. parallel type having a single comparator per bit, e.g. of the folding type

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Analogue/Digital Conversion (AREA)

Description

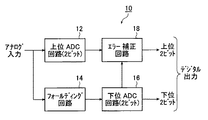

前記上位A/Dコンバータ回路への入力電圧範囲と前記下位A/Dコンバータ回路への入力電圧範囲とが、所定の電圧だけ高電位側または低電位側にシフトされており、

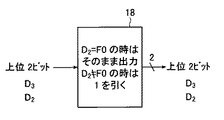

前記上位A/Dコンバータ回路から出力される上位ビットの変換結果のうちの最下位ビットと、前記下位A/Dコンバータ回路から出力され、前記フォールディング回路から出力される複数個のフォールディング信号のうちの1つのフォールディング信号について、その電圧レベルが、中心レベルよりも高電位の期間と低電位の期間とで異なる極性を持つ符号の極性に応じて、前記上位ビットの変換結果をそのまま出力する、もしくは前記上位ビットの変換結果から1を引くか1を加えるかのどちらかを行うことによって前記上位ビットの変換結果を補正することを特徴とするエラー補正回路を提供する。

前記上位A/Dコンバータ回路は、アナログ信号の入力電圧に対応するデジタル信号の上位ビットを出力し、

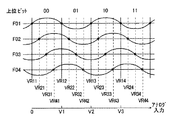

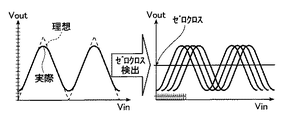

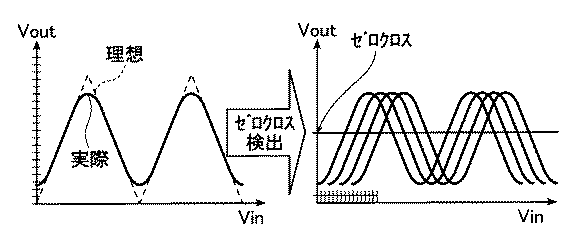

前記フォールディング回路は、その出力電圧が、前記アナログ信号の入力電圧に対して、前記上位A/Dコンバータ回路の各々の基準電圧で順次折り返される出力特性を持ち、かつ前記下位A/Dコンバータ回路の1ビットに相当するアナログ信号の電圧ずつシフトされた複数個のフォールディング信号を出力し、

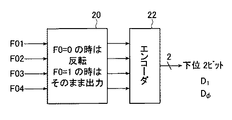

前記下位A/Dコンバータ回路は、前記フォールディング回路から出力される複数個のフォールディング信号に対応するデジタル信号の下位ビットを出力するとともに、前記フォールディング回路から出力される複数個のフォールディング信号のうちの1つのフォールディング信号の電圧レベルが、中心レベルよりも高電位の期間と低電位の期間とで異なる極性を持つ符号を出力し、

前記上位A/Dコンバータ回路への入力電圧範囲と前記下位A/Dコンバータ回路への入力電圧範囲とが、所定の電圧だけ高電位側または低電位側にシフトされており、

前記エラー補正回路は、前記上位A/Dコンバータ回路から出力される上位ビットの変換結果のうちの最下位ビットおよび前記下位A/Dコンバータ回路から出力されるフォールディング信号の符号の極性に応じて、前記上位ビットの変換結果をそのまま出力する、もしくは前記上位ビットの変換結果から1を引くか1を加えるかのどちらかを行うことによって前記上位ビットの変換結果を補正することを特徴とするA/Dコンバータを提供する。

以上、本発明のエラー補正回路およびA/Dコンバータについて詳細に説明したが、本発明は上記実施形態に限定されず、本発明の主旨を逸脱しない範囲において、種々の改良や変更をしてもよいのはもちろんである。

12,32 上位ADC回路

14,34 フォールディング回路

16,36 下位ADC回路

18 エラー補正回路

20 ビット反転回路

22 エンコーダ

Claims (2)

- 上位ビット変換用の上位A/Dコンバータ回路と、下位ビット変換用のフォールディング回路および下位A/Dコンバータ回路とを備えるフォールディング型のA/Dコンバータで用いられるエラー補正回路であって、

前記上位A/Dコンバータ回路への入力電圧範囲と前記下位A/Dコンバータ回路への入力電圧範囲とが、所定の電圧だけ高電位側または低電位側にシフトされており、

前記上位A/Dコンバータ回路から出力される上位ビットの変換結果のうちの最下位ビットと、前記下位A/Dコンバータ回路から出力され、前記フォールディング回路から出力される複数個のフォールディング信号のうちの1つのフォールディング信号について、その電圧レベルが、中心レベルよりも高電位の期間と低電位の期間とで異なる極性を持つ符号の極性に応じて、前記上位ビットの変換結果をそのまま出力する、もしくは前記上位ビットの変換結果から1を引くか1を加えるかのどちらかを行うことによって前記上位ビットの変換結果を補正することを特徴とするエラー補正回路。 - 上位ビット変換用の上位A/Dコンバータ回路と、下位ビット変換用のフォールディング回路および下位A/Dコンバータ回路と、エラー補正回路とを備えるフォールディング型のA/Dコンバータであって、

前記上位A/Dコンバータ回路は、アナログ信号の入力電圧に対応するデジタル信号の上位ビットを出力し、

前記フォールディング回路は、その出力電圧が、前記アナログ信号の入力電圧に対して、前記上位A/Dコンバータ回路の各々の基準電圧で順次折り返される出力特性を持ち、かつ前記下位A/Dコンバータ回路の1ビットに相当するアナログ信号の電圧ずつシフトされた複数個のフォールディング信号を出力し、

前記下位A/Dコンバータ回路は、前記フォールディング回路から出力される複数個のフォールディング信号に対応するデジタル信号の下位ビットを出力するとともに、前記フォールディング回路から出力される複数個のフォールディング信号のうちの1つのフォールディング信号の電圧レベルが、中心レベルよりも高電位の期間と低電位の期間とで異なる極性を持つ符号を出力し、

前記上位A/Dコンバータ回路への入力電圧範囲と前記下位A/Dコンバータ回路への入力電圧範囲とが、所定の電圧だけ高電位側または低電位側にシフトされており、

前記エラー補正回路は、前記上位A/Dコンバータ回路から出力される上位ビットの変換結果のうちの最下位ビットおよび前記下位A/Dコンバータ回路から出力されるフォールディング信号の符号の極性に応じて、前記上位ビットの変換結果をそのまま出力する、もしくは前記上位ビットの変換結果から1を引くか1を加えるかのどちらかを行うことによって前記上位ビットの変換結果を補正することを特徴とするA/Dコンバータ。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004020922A JP3813614B2 (ja) | 2004-01-29 | 2004-01-29 | エラー補正回路およびa/dコンバータ |

| US11/041,256 US6985097B2 (en) | 2004-01-29 | 2005-01-25 | Error correction circuit and A/D converter |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004020922A JP3813614B2 (ja) | 2004-01-29 | 2004-01-29 | エラー補正回路およびa/dコンバータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005217702A JP2005217702A (ja) | 2005-08-11 |

| JP3813614B2 true JP3813614B2 (ja) | 2006-08-23 |

Family

ID=34805595

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004020922A Expired - Lifetime JP3813614B2 (ja) | 2004-01-29 | 2004-01-29 | エラー補正回路およびa/dコンバータ |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6985097B2 (ja) |

| JP (1) | JP3813614B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8155611B2 (en) * | 2007-12-31 | 2012-04-10 | Synopsys, Inc. | GPS baseband architecture |

| KR101584785B1 (ko) * | 2009-01-21 | 2016-01-13 | 삼성전자주식회사 | 아날로그-디지털 컨버터 및 이를 포함하는 전자 시스템 |

| US8593315B2 (en) * | 2010-02-09 | 2013-11-26 | Nec Corporation | A/D conversion device and A/D conversion correcting method |

| US8547257B2 (en) * | 2011-10-26 | 2013-10-01 | Texas Instruments Incorporated | Digital error correction in an analog-to-digital converter |

| KR102174204B1 (ko) * | 2014-04-22 | 2020-11-05 | 에스케이하이닉스 주식회사 | Sar 및 ss 아날로그-디지털 변환 장치 및 그 방법과 그에 따른 씨모스 이미지 센서 |

| US9941906B2 (en) | 2016-02-18 | 2018-04-10 | Samsung Electronics Co., Ltd. | Sliced polar codes |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5568149A (en) * | 1995-08-24 | 1996-10-22 | Motorola, Inc. | A/D converter subsystem with half linear buffer amplifier |

| JP3920443B2 (ja) * | 1998-02-27 | 2007-05-30 | 株式会社ルネサステクノロジ | A/d変換回路 |

| JP3520233B2 (ja) * | 2000-01-21 | 2004-04-19 | 春夫 小林 | Ad変換回路 |

-

2004

- 2004-01-29 JP JP2004020922A patent/JP3813614B2/ja not_active Expired - Lifetime

-

2005

- 2005-01-25 US US11/041,256 patent/US6985097B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005217702A (ja) | 2005-08-11 |

| US6985097B2 (en) | 2006-01-10 |

| US20050168368A1 (en) | 2005-08-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101007063B1 (ko) | Sar 방식의 아날로그/디지털 변환기의 디지털 에러수정 방법 및 장치 | |

| JP5946443B2 (ja) | 積分非直線性補正を備えた逐次比較レジスタアナログ・デジタル・コンバータ | |

| US8599059B1 (en) | Successive approximation register analog-digital converter and method for operating the same | |

| US8416116B2 (en) | Successive approximation analog-to-digital converter having auxiliary prediction circuit and method thereof | |

| US8791845B2 (en) | Circuitry and method for reducing area and power of a pipelince ADC | |

| US9467161B1 (en) | Low-power, high-speed successive approximation register analog-to-digital converter and conversion method using the same | |

| US8570206B1 (en) | Multi-bit per cycle successive approximation register ADC | |

| JP3813614B2 (ja) | エラー補正回路およびa/dコンバータ | |

| JP4526919B2 (ja) | A/d変換装置 | |

| JP5059796B2 (ja) | ディジタル/アナログ変換器 | |

| KR20080042016A (ko) | 아날로그/디지털 변환기 | |

| JP4836574B2 (ja) | アナログデジタル変換器およびしきい値補正方法 | |

| TWI734560B (zh) | 時間交織數位類比轉換器及其轉換方法 | |

| JP2012151728A (ja) | ディジタル/アナログ変換器 | |

| KR101364987B1 (ko) | 아날로그 입력신호 범위 확장을 통한 데이터 변환이 가능한 파이프라인 아날로그-디지털 변환기 | |

| JP4648779B2 (ja) | ディジタル・アナログ変換器 | |

| JPWO2011099367A1 (ja) | A/d変換装置及びa/d変換補正方法 | |

| US7999718B2 (en) | Analog-to-digital converter and electronic system including the same | |

| JP5336638B2 (ja) | ディジタル/アナログ変換器 | |

| CN112825485B (zh) | 循续渐近式模拟至数字转换器及其参考涟波抑制电路 | |

| KR100587969B1 (ko) | 플래쉬 아날로그 디지털 컨버터 | |

| KR102242402B1 (ko) | 아날로그 신호를 복수의 비트의 디지털 정보로 변환하는 방법 | |

| JP2006019818A (ja) | 過渡応答特性を形成する方法および装置 | |

| US6965338B2 (en) | Cascade A/D converter | |

| CN108347246A (zh) | 流水线模拟数字转换器及其操作方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060501 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060516 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060531 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3813614 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090609 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100609 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110609 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110609 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120609 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120609 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130609 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130609 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140609 Year of fee payment: 8 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |