JP3667136B2 - 高周波電力増幅器モジュール - Google Patents

高周波電力増幅器モジュール Download PDFInfo

- Publication number

- JP3667136B2 JP3667136B2 JP04104599A JP4104599A JP3667136B2 JP 3667136 B2 JP3667136 B2 JP 3667136B2 JP 04104599 A JP04104599 A JP 04104599A JP 4104599 A JP4104599 A JP 4104599A JP 3667136 B2 JP3667136 B2 JP 3667136B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- input terminal

- power amplifier

- amplifier module

- output terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49175—Parallel arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01004—Beryllium [Be]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01014—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/095—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00 with a principal constituent of the material being a combination of two or more materials provided in the groups H01L2924/013 - H01L2924/0715

- H01L2924/097—Glass-ceramics, e.g. devitrified glass

- H01L2924/09701—Low temperature co-fired ceramic [LTCC]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19105—Disposition of discrete passive components in a side-by-side arrangement on a common die mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30107—Inductance

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3025—Electromagnetic shielding

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Wire Bonding (AREA)

Description

【発明の属する技術分野】

本発明はUHFからマイクロ波帯の信号の増幅を行う高周波電力増幅器モジュールに係り、特に小型化の必要な携帯電話機に用いられる高周波電力増幅器モジュールに関する。

【0002】

【従来の技術】

トランジスタを用いた高周波電力増幅器モジュールはPDC(Personal Digital Cellular)方式、GSM(Grobal System for Mobile communications)方式等の移動体通信の携帯電話機のキーデバイスであり、その需要は近年急激に伸びている。また、その仕様としては、移動体通信システムに対する高周波特性の他、小型、低価格であることが要求されている。

【0003】

この要求に応える一つの方法が特許公報第2755250号に記載されている。図11の平面図,図12の斜視図に示すように,1つの半導体チップ1上に2個のトランジスタ2,3を近接して配置することにより、小型、低価格化している。また、初段トランジスタ2のボンディング用入力電極2bと配線基板のボンディング用電極7dは入力ボンディングワイヤ9dで接続されている。2段目トランジスタ3のボンディング用出力電極3cと配線基板6のボンディング用電極7aは出力ボンディングワイヤ9aで接続されている。半導体チップ1上のボンディング用電極10aと配線基板6のボンディング用電極12aはシールド用ボンディングワイヤ13aで接続されている。シールド用ボンディングワイヤ13aは入力ボンディングワイヤ9dと出力ボンディングワイヤ9aとの間に設けられており、かつその両端のボンディング用電極10aと12aは各々半導体チップ1および配線基板に形成されたバイアホール(Via Hole(図示せず))を通して高周波的に接地されている。このシールド用ボンディングワイヤ13aを設けることにより、入力ボンディングワイヤ9dと出力ボンディングワイヤ9aとの間の相互インダクタンスによる結合が低減して高周波入出力端子間のアイソレーション劣化を改善することができ、高周波特性が向上する。

【0004】

入力ボンディングワイヤ9dと出力ボンディングワイヤ9aとの間の相互インダクタンスによる結合の問題は、初段トランジスタ2と2段目トランジスタ3とが、入出力の位置を逆にして並置されているため、両者が近接する結果生じる。この問題は特に、初段トランジスタ2の入力ボンディングワイヤ9dと、2段目トランジスタ3の出力ボンディングワイヤ9aの間で顕著である。これは初段トランジスタ2に入力される高周波信号電力に比べ、2段目トランジスタ3から出力される高周波信号電力の方が20dB〜30dB(100〜1000倍)大きく,出力から入力への正帰還が働くことによる。一方,初段トランジスタ2の出力ボンディングワイヤ9cと2段目トランジスタ3の入力ボンディングワイヤ9bも近接しているが,両者に流れる高周波信号電力の比は0dB(1倍)以下と小さく, 高周波特性劣化の問題は生じない。

【0005】

なお、図11,12において,2a,3aはトランジスタの本体部分,2d,3dはトランジスタのソース電極,2cは初段トランジスタ2のボンディング用出力電極,3bは2段目トランジスタ3のボンディング用入力電極,4は接地電極, 7 b ,7 c は配線基板6のボンディング用電極,8a〜8dはリード電極,104はキャビティである。

【0006】

【発明が解決しようとする課題】

上記従来技術のシールド用ボンディングワイヤ13aの効果を図5により説明する。図5は、増幅器の入出力ボンディングワイヤ間の結合係数(相互インダクタンス(単位: nH))を、長さ1mm(実物に近い長さ)の平行した2本の入出力ボンディングワイヤのボンディング部の間隔dに対し、算出したものである。ここで、結合係数0.12の個所を示す破線は、結合係数が0.12以下のとき増幅器が安定に動作することを示す。この0.12という値は、結合係数と増幅器の安定係数の関係を示す図6から求めた。安定係数が1以上で増幅器は安定に動作する。ここで、ボンディング部の間隔dは、最も近接した2つのボンディングワイヤのボンディング部の中心間の距離で定義される。

【0007】

図5に示されるように、シールド用ボンディングワイヤを設けるという対策を施している上記従来技術の場合は、そうでない場合(図中、「対策なし」と表示)に比べて、結合係数が小さくなっており、高周波数特性が向上している。また、結合係数が0.12以下のボンディング部の間隔dの範囲が広がり、設計の自由度が増している。さらには、ボンディング部の間隔dを0.55 mmまで小さくすることが可能となるため、チップ面積を小さくでき、モジュールの小型化、コストの低減が可能となる。

【0008】

しかし、現実には、シールド用ボンディングワイヤ13aの両端にバイアホールによるインダクタンスが直列に加わるため,上記従来技術では充分な高周波特性の向上が得られない。

【0009】

本発明の目的は, より高周波特性を向上させることができる高周波電力増幅器モジュールを提供することにある。

【0010】

【課題を解決するための手段】

上記目的は、 誘電体材料を基体とする配線基板上に半導体チップが設置された高周波電力増幅器モジュールにおいて、半導体チップに、2段以上の増幅段トランジスタ、これらの増幅段トランジスタへ高周波電力を入力するためのボンディング用入力電極、およびこれらの増幅段トランジスタから高周波電力を出力するためのボンディング用出力電極を設け、ある一つの増幅段トランジスタに対応するボンディング用入力電極と配線基板を接続する入力ボンディングワイヤの両端のボンディング部同士を結ぶ第1の補助線と、この一つの増幅段トランジスタの次段に位置する増幅段トランジスタに対応するボンディング用出力電極と配線基板を接続する出力ボンディングワイヤの両端のボンディング部(その中心部)同士を結ぶ第2の補助線のなす角度が、72〜180゜の範囲に入るように、かつボンディング用入力電極とボンディング用出力電極のボンディング部の間隔が0.3mm以上0.8mm未満の範囲に入るように高周波電力増幅器モジュールを設計することにより達成できる。

【0011】

ここで、0.3mm以上0.8mm未満というボンディング部間隔の条件にかかわらず、上記2つの増幅段トランジスタの安定係数が1以上となるように高周波電力増幅器モジュールを設計すれば上記目的を達成できる。

【0012】

【発明の実施の形態】

図5に示されるように、本発明の場合は上記従来技術の場合より更に結合係数が小さくなっており、高周波数特性が向上している。また、結合係数が0.12以下(安定係数が1以上)のボンディング部の間隔dの範囲も更に広がり、設計の自由度が増している。さらには、ボンディング部の間隔dを0.3 mmまで小さくすることが可能となるため、チップ面積を更に小さくでき、更なるモジュールの小型化、コストの低減が可能となる。

【0013】

また、図5は入出力ボンディングワイヤ間のなす角度φが90゜の場合であるが、図7に示されるように、この角度φは72〜180゜の範囲にあれば良い。また、角度φが140゜のとき結合係数が最小になっており、極小点が存在することが分かる。

【0014】

本発明の高周波電力増幅器モジュールの具体的設計に当たっては、以上のことを踏まえて、ボンディング部間隔dと角度φを選ぶことになる。

【0015】

さらには、以上の説明から明らかなように、本発明は角度φを従来のように0゜にしないことがその根底にある。したがって、角度φが72〜180゜の範囲にあり、入出力ボンディングワイヤに対応する2つの増幅段トランジスタの安定係数が1以上となるように高周波電力増幅器モジュールを設計しても良い。

【0016】

実施例1

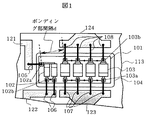

本発明の実施例1の2段電力増幅器モジュールを図1〜図4により説明する。図1は要部平面図,図2は等価回路図 ,図3は外観構成を示す平面図,図4は要部斜視図である。

【0017】

図1に示されるように,初段と2段目のMOSFETで構成されたトランジスタ102,103を一つのシリコンチップ101上に近接して形成する。初段トランジスタ102のゲート電極102aからドレイン電極102bへの高周波信号の流れの向きと、2段目トランジスタ103のゲート電極103aからドレイン電極103bへの高周波信号の流の向きが反対となるようにこれらのトランジスタは配置する。

【0018】

高周波入力端子であるゲート電極102aは,1本の入力ボンディングワイヤ105により、配線基板113上の入力整合回路125の端部121に接続されている。高周波出力端子であるドレイン電極103bは,4本の出力ボンディングワイヤ108により、配線基板113上の出力整合回路127の端部124に接続されている。ゲート電極102aはシリコンチップ101の左側の一辺に沿って配置し,ドレイン電極103bはシリコンチップ101の上側の一辺に沿って配置する。入力ボンディングワイヤ105と出力ボンディングワイヤ108のなす角度は約90゜にする。ボンディングワイヤ106,107は、ドレイン電極102b,ゲート電極103aを、配線基板113上の段間整合回路126の両端部122および123に各々接続されている。初段トランジスタ102のゲート電極102a(ボンディング用入力電極)と2段目トランジスタ103のドレイン電極103b(ボンディング用出力電極)のボンディング部の間隔dは約0.6mmにする。

【0019】

シリコンチップ101は,配線基板113に形成されたキャビティ104の中に搭載する。シリコンチップ101の裏面には,初段トランジスタ102のソース電極および2段目トランジスタ103のソース電極として金属膜を被着し,キャビティ104内の配線を介して接地電位に接続する。配線基板113の材料としては、ガラスセラミックスやアルミナなどの誘電体基板を用いる。また、その配線には銅や銀,銀白金などを用いる。

【0020】

図2および図3において,記号Pin,Pout,Vgg,Vddはそれぞれ高周波信号入力端子,高周波信号出力端子,ゲート電圧印加端子,ドレイン電圧印加端子であり,これらは電力増幅器モジュールの外部接続端子である。図3において、入力整合回路125、段間整合回路126および出力整合回路127の領域の境界を補助線で示す。また、図4にキャビティ104近辺の立体的様子を示す。

【0021】

本実施例において,入力ボンディングワイヤ105と出力ボンディングワイヤ108のなす角度を約90゜としたが,この角度は72゜〜180゜の範囲で選ぶことができる。

【0022】

実施例2

本発明の実施例2の3段電力増幅器モジュールを図8の要部平面図により説明する。初段,2段目,出力段のMOSFETで構成されたトランジスタ102,103,114を一つのシリコンチップ101上に近接して形成する。初段トランジスタ102のゲート電極102aからドレイン電極102bへの高周波信号の流れの向きと,2段目トランジスタ103のゲート電極103aからドレイン電極103bへの高周波信号の流れの向きが反対となるようにこれらのトランジスタは配置する。また,出力段トランジスタ114を、そのゲート電極114aからドレイン電極114bへの高周波信号の流れの向きが2段目トランジスタ103とは反対の向きとなるように配置する。

【0023】

実施例1との違いは,初段トランジスタ102の入力ボンディングワイヤ105と2段目トランジスタ103の出力ボンディングワイヤ108とのなす角度を約140゜とした点、および出力段トランジスタ114を同一チップ上に設け、このトランジスタの出力ボンディングワイヤ110と2段目トランジスタ103の入力ボンディングワイヤ107とのなす角度を約90゜、2段目トランジスタ103のゲート電極103a(ボンディング用入力電極)と出力段トランジスタ114のドレイン電極114b(ボンディング用出力電極)のボンディング部の間隔dを約0.7mmとし、ここにも本発明を適用した点にある。

【0024】

本実施例によれば,図7に示すように、初段と2段目の入出力ボンディングワイヤ間の結合係数を最小にでき,アイソレーションをさらに改善できる。また,本発明を適用したので、2段目と出力段の入出力ボンディングワイヤ間も十分なアイソレーションを確保できる。したがって、半導体チップ面積の縮小の為に同一チップ上に3段のトランジスタを形成した本実施例場合でも、これらトランジスタ間の距離が短くなるにもかかわらず、高周波特性を改善できる。

【0025】

実施例3

本発明の実施例3の3段電力増幅器モジュールを図9の要部平面図により説明する。実施例2との違いは,2段目トランジスタ103と出力段トランジスタ114との間に、従来技術であるシールド技術を応用して、シールド用ボンディングワイヤ201とシールド配線204を設け,これらの両端を配線基板上の電極202およびバイアホール203を介して接地電位に接続した点にある。

【0026】

本実施例では,初段と2段目の間に従来技術であるシールド技術を適用したが、これらのトランジスタ領域は元々面積が広く、高周波特性を改善できる。

【0027】

実施例4

本発明の実施例4の2段電力増幅器モジュールを図10の要部平面図により説明する。

【0028】

実施例1との違いは,初段トランジスタ102自体の方向を90゜回転した点にある。

【0029】

本実施例は,初段と2段目との入出力ボンディングワイヤのボンディング部の位置をチップの辺の中央部に移動できるので、ボンディング部間隔をさらに広げることが可能となり(実施例1で0.6mmだったものが0.75mmになる。)、入出力間のアイソレーションをさらに改善できる。

【0030】

以上,本発明を実施例を基に説明したが,本発明は上記実施例に限定されるものではなく,トランジスタの電極数,ボンディングワイヤの本数等はその主旨を逸脱しない範囲において種々変更可能である。また、トランジスタはMOSFETに限らず他の電界効果トランジスタ、ヘテロ接合バイポーラトランジスタ(HBT)等のトランジスタを用いても良い。

【0031】

【発明の効果】

本発明によれば,高周波電力増幅器モジュールの高周波特性をより向上させることができ、これに伴い電力増幅器モジュールの小型化,またこれを用いた携帯電話端末の小型・薄型化が可能となる。

【図面の簡単な説明】

【図1】本発明の実施例1の2段電力増幅器モジュールの要部平面図である。

【図2】本発明の実施例1の2段電力増幅器モジュールの等価回路図である。

【図3】本発明の実施例1の2段電力増幅器モジュールの外観構成を示す平面図である。

【図4】本発明の実施例1の2段電力増幅器モジュールの要部斜視図である。

【図5】本発明および従来技術の入出力ボンディングワイヤ間の結合係数とボンディング部間隔の関係を示す図である。

【図6】入出力ボンディングワイヤ間の結合係数と増幅器の安定係数の関係を示す図である。

【図7】本発明の入出力ボンディングワイヤ間の結合係数と角度の関係を示す図である。

【図8】本発明の実施例2の3段電力増幅器モジュールの要部平面図である。

【図9】本発明の実施例3の3段電力増幅器モジュールの要部平面図である。

【図10】本発明の実施例4の2段電力増幅器モジュールの要部平面図である。

【図11】従来技術の2段電力増幅器モジュールの平面図である。

【図12】従来技術の2段電力増幅器モジュールの斜視図である。

【符号の説明】

1…半導体チップ,2…初段トランジスタ,2a…トランジスタの本体部分,2b…ボンディング用入力電極,2c…ボンディング用出力電極,2d…ソース電極,3…2段目トランジスタ,3a…トランジスタの本体部分,3b…ボンディング用入力電極,3c…ボンディング用出力電極,3d…ソース電極,4…接地電極,6…配線基板,7a〜7d…配線基板6のボンディング用電極 ,8a〜8d…リード電極,9a…出力ボンディングワイヤ,9b…入力ボンディングワイヤ,9c…出力ボンディングワイヤ,9d…入力ボンディングワイヤ,10a,10b…ボンディング用電極,12a,12b…ボンディング用電極,13a,13b…シールド用ボンディングワイヤ,101…シリコンチップ,102…初段トランジスタ,102a…ゲート電極(入力電極),102b…ドレイン電極(出力電極),103…2段目トランジスタ,103a…ゲート電極(入力電極),103b…ドレイン電極(出力電極),104…キャビティ,105…入力ボンディングワイヤ,106…出力ボンディングワイヤ,107…入力ボンディングワイヤ,108…出力ボンディングワイヤ,109…入力ボンディングワイヤ,110…出力ボンディングワイヤ,113…配線基板,114…出力段トランジスタ,114a…ゲート電極(入力電極),114b…ドレイン電極(出力電極),121…入力整合回路の端部,122…段間整合回路の端部,123…段間整合回路の端部,124…出力整合回路の端部,125…入力整合回路,126…段間整合回路,127…出力整合回路,Pin…高周波信号入力端子,Pout…高周波信号出力端子,Vgg…ゲート電圧印加端子,Vdd…ドレイン電圧印加端子,201…シールド用ボンディングワイヤ,202…電極,203…バイアホール,204…シールド配線。

Claims (23)

- 基板と、

前記基板の1つの面に配置される第1および第2の電極と、

前記基板に搭載され、入力端子および出力端子を有する第1および第2のトランジスタを有して成る四辺形状の半導体チップと、

前記第1の電極と前記第1のトランジスタの前記入力端子とを電気的に接続する第1の接続導体と、

前記第2の電極と前記第2のトランジスタの前記出力端子とを電気的に接続する第2の接続導体とを具備して成り、

前記半導体チップは、前記第1のトランジスタの前記入力端子と前記第1の電極とが対向し、前記第2のトランジスタの前記出力端子と前記第2の電極とが対向するように配置され、

前記第1の接続導体は第1の方向に延在し、前記第2の接続導体は前記第1の方向とは異なる第2の方向に延在し、

前記第1の方向と前記第2の方向との成す角は、前記基板の前記1つの面を平面図として見た場合に72〜180度の範囲内であり、

前記第1のトランジスタの前記入力端子に入力された信号を電圧増幅し、前記第2のトランジスタの前記出力端子から、電圧増幅された前記信号を出力することを特徴とする高周波電力増幅器モジュール。 - 請求項1において、

前記第1のトランジスタの前記出力端子と前記第2のトランジスタの前記入力端子とは整合回路を介して互いに接続されていることを特徴とする高周波電力増幅器モジュール。 - 請求項1において、

前記第1および第2のトランジスタの各々は、ゲート、ソース、およびドレインを有する電界効果トランジスタを含んで成り、

前記第1のトランジスタの前記入力端子は、前記第1のトランジスタの前記電界効果トランジスタの前記ゲートであり、

前記第2のトランジスタの前記出力端子は、前記第2のトランジスタの前記電界効果トランジスタの前記ドレインであることを特徴とする高周波電力増幅器モジュール。 - 請求項1において、

前記第1および第2のトランジスタの各々は、バイポーラトランジスタであることを特徴とする高周波電力増幅器モジュール。 - 請求項1において、

前記第1のトランジスタの前記入力端子と前記第2のトランジスタの前記出力端子とのボンディング部間の距離は0.3mm以上であり、前記第1および第2のトランジスタの安定係数は1以上であることを特徴とする高周波電力増幅器モジュール。 - 基板と、

前記基板の1つの面に配置される第1および第2の電極と、

前記基板に搭載され、入力端子および出力端子を有する第1および第2のトランジスタを有して成る四辺形状の半導体チップと、

前記第1の電極と前記第1のトランジスタの前記入力端子とを電気的に接続する第1の接続導体と、

前記第2の電極と前記第2のトランジスタの前記出力端子とを電気的に接続する第2の接続導体とを具備して成り、

前記半導体チップは、前記第1のトランジスタの前記入力端子と前記第1の電極とが対向し、前記第2のトランジスタの前記出力端子と前記第2の電極とが対向するように配置され、

前記第1の接続導体の両端のボンディング部間を結ぶ第1の補助線で定義される第1の方向と、前記第2の接続導体の両端のボンディング部間を結ぶ第2の補助線で定義される第2の方向との成す角は、72〜180度の範囲内であり、

前記第1のトランジスタの前記入力端子に入力された信号を電圧増幅し、前記第2のトランジスタの前記出力端子から、電圧増幅された前記信号を出力することを特徴とする高周波電力増幅器モジュール。 - 請求項6において、

前記第1のトランジスタの前記出力端子と前記第2のトランジスタの前記入力端子とは整合回路を介して互いに接続されていることを特徴とする高周波電力増幅器モジュール。 - 請求項6において、

前記第1および第2のトランジスタの各々は、ゲート、ソース、およびドレインを有する電界効果トランジスタを含んで成り、

前記第1のトランジスタの前記入力端子は、前記第1のトランジスタの前記電界効果トランジスタの前記ゲートであり、

前記第2のトランジスタの前記出力端子は、前記第2のトランジスタの前記電界効果トランジスタの前記ドレインであることを特徴とする高周波電力増幅器モジュール。 - 請求項6において、

前記第1および第2のトランジスタの各々は、バイポーラトランジスタであることを特徴とする高周波電力増幅器モジュール。 - 請求項6において、

前記第1のトランジスタの前記入力端子と前記第2のトランジスタの前記出力端子とのボンディング部間の距離は0.3mm以上であり、前記第1および第2のトランジスタの安定係数は1以上であることを特徴とする高周波電力増幅器モジュール。 - 基板と、

前記基板の1つの面に配置される第1および第2の電極と、

前記基板に搭載され、入力端子および出力端子を有する第1および第2のトランジスタを有して成る四辺形状の半導体チップと、

前記第1の電極と前記第1のトランジスタの前記入力端子とを電気的に接続する第1の接続導体と、

前記第2の電極と前記第2のトランジスタの前記出力端子とを電気的に接続する第2の接続導体とを具備して成り、

前記半導体チップは、前記第1のトランジスタの前記入力端子と前記第1の電極とが対向し、前記第2のトランジスタの前記出力端子と前記第2の電極とが対向するように配置され、

前記第1の接続導体は第1の方向に延在し、前記第2の接続導体は前記第1の方向とは異なる第2の方向に延在し、

前記第1の方向と前記第2の方向との成す角が、前記基板の前記1つの面を平面図として見た場合に72〜180度の範囲内であることにより、前記第2のトランジスタの前記出力端子から出力される信号から前記第1のトランジスタの前記入力端子に入力される信号へ正帰還が働くことを防止し、

前記第1のトランジスタの前記入力端子に入力された信号を電圧増幅し、前記第2のトランジスタの前記出力端子から、電圧増幅された前記信号を出力することを特徴とする高周波電力増幅器モジュール。 - 請求項11において、

前記第1のトランジスタの前記出力端子と前記第2のトランジスタの前記入力端子とは整合回路を介して互いに接続されていることを特徴とする高周波電力増幅器モジュール。 - 請求項11において、

前記第1および第2のトランジスタの各々は、ゲート、ソース、およびドレインを有する電界効果トランジスタを含んで成り、

前記第1のトランジスタの前記入力端子は、前記第1のトランジスタの前記電界効果トランジスタの前記ゲートであり、

前記第2のトランジスタの前記出力端子は、前記第2のトランジスタの前記電界効果トランジスタの前記ドレインであることを特徴とする高周波電力増幅器モジュール。 - 請求項11において、

前記第1および第2のトランジスタの各々は、バイポーラトランジスタであることを特徴とする高周波電力増幅器モジュール。 - 請求項11において、

前記第1のトランジスタの前記入力端子と前記第2のトランジスタの前記出力端子とのボンディング部間の距離は0.3mm以上であり、前記第1および第2のトランジスタの安定係数は1以上であることを特徴とする高周波電力増幅器モジュール。 - 請求項1において、

前記第1の方向と前記第2の方向との成す角は、前記基板の前記1つの面を平面図として見た場合に略90度であることを特徴とする高周波電力増幅器モジュール。 - 請求項16において、

前記第1のトランジスタの前記出力端子と前記第2のトランジスタの前記入力端子とは整合回路を介して互いに接続されていることを特徴とする高周波電力増幅器モジュール。 - 請求項16において、

前記第1および第2のトランジスタの各々は、ゲート、ソース、およびドレインを有する電界効果トランジスタを含んで成り、

前記第1のトランジスタの前記入力端子は、前記第1のトランジスタの前記電界効果トランジスタの前記ゲートであり、

前記第2のトランジスタの前記出力端子は、前記第2のトランジスタの前記電界効果トランジスタの前記ドレインであることを特徴とする高周波電力増幅器モジュール。 - 請求項16において、

前記第1および第2のトランジスタの各々は、バイポーラトランジスタであることを特徴とする高周波電力増幅器モジュール。 - 請求項16において、

前記第1のトランジスタの前記入力端子と前記第2のトランジスタの前記出力端子とのボンディング部間の距離は0.3mm以上であり、前記第1および第2のトランジスタの安定係数は1以上であることを特徴とする高周波電力増幅器モジュール。 - 基板と、

前記基板の1つの面に配置される第1および第2の電極と、

前記基板に搭載され、入力端子および出力端子を有する第1および第2のトランジスタを有して成る四辺形状の半導体チップと、

前記第1の電極と前記第1のトランジスタの前記入力端子とを電気的に接続する第1の接続導体と、

前記第2の電極と前記第2のトランジスタの前記出力端子とを電気的に接続する第2の接続導体とを具備して成り、

前記半導体チップは、前記第1のトランジスタの前記入力端子と前記第1の電極とが対向し、前記第2のトランジスタの前記出力端子と前記第2の電極とが対向するように配置され、

前記第2のトランジスタは電界効果トランジスタであり、

前記第2のトランジスタの前記出力端子は、前記第1のトランジスタの前記入力端子に入力された信号を出力する前記第2のトランジスタのドレイン端子であり、

前記第1の接続導体は第1の方向に延在し、前記第2の接続導体は前記第1の方向とは異なる第2の方向に延在し、

前記第1の方向と前記第2の方向との成す角は、前記基板の前記1つの面を平面図として見た場合に72〜180度の範囲内であることを特徴とする高周波電力増幅器モジュール。 - 請求項21において、

前記第1のトランジスタの前記出力端子と前記第2のトランジスタの前記入力端子とは整合回路を介して互いに接続されていることを特徴とする高周波電力増幅器モジュール。 - 請求項21において、

前記第1のトランジスタの前記入力端子と前記第2のトランジスタの前記出力端子とのボンディング部間の距離は0.3mmであり、前記第1および第2のトランジスタの安定係数は1以上であることを特徴とする高周波電力増幅器モジュール。

Priority Applications (13)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP04104599A JP3667136B2 (ja) | 1999-02-19 | 1999-02-19 | 高周波電力増幅器モジュール |

| TW088110698A TW473882B (en) | 1998-07-06 | 1999-06-25 | Semiconductor device |

| EP99112588A EP0971411B1 (en) | 1998-07-06 | 1999-07-01 | Semiconductor device |

| DE69935182T DE69935182T2 (de) | 1998-07-06 | 1999-07-01 | Halbleiteranordnung |

| EP06027122A EP1770777A3 (en) | 1998-07-06 | 1999-07-01 | Semiconductor device with a shielding bond wire |

| US09/345,505 US6330165B1 (en) | 1998-07-06 | 1999-07-01 | Semiconductor device |

| US09/970,668 US6489680B2 (en) | 1998-07-06 | 2001-10-05 | Semiconductor device |

| US10/291,840 US6943441B2 (en) | 1998-07-06 | 2002-11-12 | Semiconductor device |

| US11/194,701 US7068521B2 (en) | 1998-07-06 | 2005-08-02 | Semiconductor device |

| US11/451,579 US20070001300A1 (en) | 1998-07-06 | 2006-06-13 | Semiconductor device |

| US11/905,421 US7525813B2 (en) | 1998-07-06 | 2007-10-01 | Semiconductor device |

| US12/394,421 US7817437B2 (en) | 1998-07-06 | 2009-02-27 | Semiconductor device |

| US12/787,154 US8295057B2 (en) | 1998-07-06 | 2010-05-25 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP04104599A JP3667136B2 (ja) | 1999-02-19 | 1999-02-19 | 高周波電力増幅器モジュール |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004150427A Division JP4153898B2 (ja) | 2004-05-20 | 2004-05-20 | 高周波電力増幅器モジュール |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000243779A JP2000243779A (ja) | 2000-09-08 |

| JP2000243779A5 JP2000243779A5 (ja) | 2005-04-07 |

| JP3667136B2 true JP3667136B2 (ja) | 2005-07-06 |

Family

ID=12597443

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP04104599A Expired - Fee Related JP3667136B2 (ja) | 1998-07-06 | 1999-02-19 | 高周波電力増幅器モジュール |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3667136B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006093419A (ja) * | 2004-09-24 | 2006-04-06 | Oki Electric Ind Co Ltd | 半導体装置及びその実装方法 |

-

1999

- 1999-02-19 JP JP04104599A patent/JP3667136B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000243779A (ja) | 2000-09-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6489680B2 (en) | Semiconductor device | |

| US8295057B2 (en) | Semiconductor device | |

| US7952434B2 (en) | Semiconductor device | |

| JP5589428B2 (ja) | 伝送線路、インピーダンス変換器、集積回路搭載装置および通信機モジュール | |

| CN210246699U (zh) | 功率放大模块 | |

| US6414387B1 (en) | Semiconductor device including a chip having high-frequency circuit blocks | |

| JP5812158B2 (ja) | 伝送線路、インピーダンス変換器、集積回路搭載装置および通信機モジュール | |

| JPH11238851A (ja) | 集積回路装置およびそれを用いた通信機 | |

| JP2755250B2 (ja) | 半導体集積回路 | |

| JP3667136B2 (ja) | 高周波電力増幅器モジュール | |

| JP2006528854A (ja) | 小型インピーダンス変換回路 | |

| JP4153898B2 (ja) | 高周波電力増幅器モジュール | |

| JP2008228347A (ja) | 高周波電力増幅器モジュール | |

| JPH11204728A (ja) | 高周波半導体装置 | |

| JPH07321130A (ja) | 半導体装置 | |

| JP2002171144A (ja) | 高周波増幅器 | |

| JPH04261206A (ja) | 増幅器 | |

| JP2005051062A (ja) | 半導体装置 | |

| KR20000011461A (ko) | 반도체장치 | |

| JPH08125198A (ja) | 半導体装置 | |

| JPH10125796A (ja) | ヘテロ接合バイポーラトランジスタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040520 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040520 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20040520 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20040520 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20040623 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040818 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040831 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041101 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050304 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050329 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050405 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080415 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090415 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090415 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100415 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100415 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110415 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110415 Year of fee payment: 6 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110415 Year of fee payment: 6 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120415 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120415 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130415 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140415 Year of fee payment: 9 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |