以下、本開示の例示的な実施例を、添付した図面を参照して詳細に説明する。以下の実施例は、本開示の思想を本開示の属する技術分野における当業者に十分に伝達するための例として提供される。したがって、本開示はここに開示された実施例に限定されず、他の形態で実現されてもよい。図面において、要素の幅、長さ、厚さなどは明瞭さと説明的な目的のために誇張されることがある。要素または層が他の要素または層の「上部に配置」されるか、「上に配置」されると言及されたとき、当該要素または層は、直接的に他の要素または層の「上部に配置」されるか、「上に配置」されてもよく、または中間に介在する要素または層が存在してもよい。明細書全体にわたって、同じ参照番号は、同一または類似の機能を有する同じ要素を指し示す。

以下、本開示の例示的な実施例を、添付した図面を参照して詳細に説明する。本明細書で使用される、例示的な実施例による発光デバイスまたは発光ダイオードは、当業界で公知のように、約10,000μm2未満の表面積を有するマイクロLEDを含むことができる。他の例示的な実施例において、マイクロLEDは、特定の応用例によって、約4,000μm2未満または約2,500μm2未満の表面積を有することができる。

図1は、本開示の1つの例示的な実施例によるディスプレイ用発光ダイオードスタック100の概略断面図である。

図1を参照すると、発光ダイオードスタック100は、支持基板51と、第2基板31と、第3基板41と、第1LEDスタック23と、第2LEDスタック33と、第3LEDスタック43と、第1−p反射電極25と、第2−p透明電極35と、第3−p透明電極45と、第1カラーフィルタ37と、第2カラーフィルタ47と、第1ボンディング層53と、第2ボンディング層55と、第3ボンディング層57とを含むことができる。

支持基板51は、半導体スタック23、33および43を支持する。支持基板51は、その表面上にまたはその内部に回路を含むことができるが、これに限定されるものではない。支持基板51は、例えば、Si基板またはGe基板を含むことができる。

第1LEDスタック23、第2LEDスタック33および第3LEDスタック43のそれぞれは、n型半導体層と、p型半導体層と、その間に介在する活性層とを含む。活性層は、多重量子井戸構造を有してもよい。

例えば、第1LEDスタック23は、赤色光を放出するように適合化される無機発光ダイオードであってもよく、第2LEDスタック33は、緑色光を放出するように適合化される無機発光ダイオードであってもよいし、第3LEDスタック43は、青色光を放出するように適合化される無機発光ダイオードであってもよい。第1LEDスタック23は、GaInP系井戸層を含むことができ、第2LEDスタック33および第3LEDスタック43のそれぞれは、GaInN系井戸層を含むことができる。

同時に、第1〜第3LEDスタック23、33および43のそれぞれの両面は、それぞれn型半導体層およびp型半導体層である。このような例示的な実施例において、第1〜第3LEDスタック23、33および43のそれぞれは、n型上部表面およびp型下部表面を有する。第3LEDスタック43がn型上部表面を有するので、粗面化された表面(roughened surface)が第3LEDスタック43の上部表面上に化学的エッチングにより形成される。しかし、本開示がこれに限定されるものではなく、各LEDスタックの上部および下部表面の半導体タイプは変化可能であることを理解しなければならない。

第1LEDスタック23は、支持基板51近傍に配置され、第2LEDスタック33は、第1LEDスタック23上に配置され、第3LEDスタック43は、第2LEDスタック33上に配置される。第1LEDスタック23が第2および第3LEDスタック33および43より長い波長を有する光を放出するので、第1LEDスタック23から発生する光は、第2および第3LEDスタック33および43を介して外部に放出される。また、第2LEDスタック33が第3LEDスタック43より長い波長を有する光を放出するので、第2LEDスタック33から発生する光は、第3LEDスタック43を介して外部に放出される。

第2基板31は、第2LEDスタック33のための成長基板であり、例えば、GaN系基板であってもよい。第2基板31は、第2LEDスタック33に対する均質基板であり、第2LEDスタック33にモノリシックに(monolithically)結合される。第2基板31は、n型半導体層として用いられるために、Siのようなn型ドーパントでドーピングされる。第2LEDスタック33に対する均質基板が第2基板31として用いられるので、第2基板31上に成長する第2LEDスタック33の転位密度(dislocation density)が減少可能であり、それによって、第2LEDスタック33の発光効率が向上する。第2LEDスタック33は、例えば、103〜107/cm2の転位密度を有することができる。サファイア基板上に成長するGaN系半導体層が一般的に108/cm2以上の転位密度を有するので、第2LEDスタック33の転位密度がGaN成長基板を用いることで大きく減少できる。

第3基板41は、第3LEDスタック43のための成長基板であり、GaN系基板、例えば、GaN基板であってもよい。第3基板41は、第3LEDスタック43に対する均質基板であり、第3LEDスタック43にモノリシックに結合される。第3基板41は、n型半導体層として用いられるために、Siのようなn型ドーパントでドーピングされる。第3LEDスタック43に対する均質基板が第3基板41として用いられるので、第3基板41上に成長する第3LEDスタック43の転位密度が減少可能であり、それによって、第3LEDスタック43の発光効率が向上する。第3LEDスタック43は、例えば、103〜107/cm2の転位密度を有することができる。

第2基板31および第3基板41ともが本例示的な実施例で用いられるが、第2基板31および第3基板41のうちの1つは省略可能である。また、第2基板31および第3基板41ともが図13を参照して後述するように除去可能である。

第1−p反射電極25は、第1LEDスタック23のp型半導体層とオーミック接触を形成し、第1LEDスタック23から発生する光を反射させる。例えば、第1−p反射電極25は、Au−TiまたはAu−Snで形成される。また、第1−p反射電極25は、拡散バリア層を含むことができる。

第2−p透明電極35は、第2LEDスタック33のp型半導体層とオーミック接触を形成する。第2−p透明電極35は、赤色光および緑色光に関して透過性である金属層または導電性酸化物層で構成される。

加えて、第3−p透明電極45は、第3LEDスタック43のp型半導体層とオーミック接触を形成する。第3−p透明電極45は、赤色光、緑色光および青色光に関して透過性である金属層または導電性酸化物層で構成される。

第1−p反射電極25、第2−p透明電極35および第3−p透明電極45は、各LEDスタックのp型半導体層とのオーミック接触により電流拡散(current spreading)を助けることができる。

第1カラーフィルタ37は、第1LEDスタック23と第2LEDスタック33との間に介在してもよい。加えて、第2カラーフィルタ47は、第2LEDスタック33と第3LEDスタック43との間に介在してもよい。第1カラーフィルタ37は、第2LEDスタック33から発生する光を反射させながら、第1LEDスタック23から発生する光を透過させる。第2カラーフィルタ47は、第3LEDスタック43から発生する光を反射させながら、第1および第2LEDスタック23および33から発生する光を透過させる。結果として、第1LEDスタック23から発生する光は、第2LEDスタック33および第3LEDスタック43を介して外部に放出され、第2LEDスタック33から発生する光は、第3LEDスタック43を介して外部に放出される。また、発光ダイオードスタックは、第2LEDスタック33から発生する光が第1LEDスタック23に進入するのを防止することができるか、または第3LEDスタック43から発生する光が第2LEDスタック33に進入するのを防止することができ、それによって、光損失を防止する。一方、第1LEDスタック23から発生する光は、第2−p透明電極35および第3−p透明電極45を介して外部に放出され、第2LEDスタック33から発生する光は、第3−p透明電極45を介して外部に放出される。

いくつかの例示的な実施例において、第1カラーフィルタ37は、第3LEDスタック43から発生する光を反射させることができる。

第1および第2カラーフィルタ37および47は、例えば、低周波数帯域で、すなわち、長波長帯域で、光を通過させるローパスフィルタ、所定の波長帯域で光を通過させるバンドパスフィルタ、または所定の波長帯域で光の通過を防止するバンドストップフィルタであってもよい。特に、第1および第2カラーフィルタ37および47のそれぞれは、分布ブラッグ反射器(DBR)を含むバンドストップフィルタであってもよい。分布ブラッグ反射器は、互いに異なる屈折率を有する絶縁層、例えば、TiO2およびSiO2を交互に積層することにより形成可能である。同時に、分布ブラッグ反射器の阻止帯域は、TiO2およびSiO2層の厚さを調節することにより制御可能である。ローパスフィルタおよびバンドパスフィルタも、互いに異なる屈折率を有する絶縁層を交互に積層することにより形成可能である。

第1ボンディング層53は、第1LEDスタック23を支持基板51に結合する。図示のように、第1−p反射電極25は、第1ボンディング層53に隣接していてもよい。第1ボンディング層53は、光透過性または不透明層であってもよい。第1ボンディング層53は、例えば、透明無機絶縁層、透明有機絶縁層または透明導電層であってもよい。

第2ボンディング層55は、第2LEDスタック33を第1LEDスタック23に結合する。図示のように、第2ボンディング層55は、第1LEDスタック23および第1カラーフィルタ37に隣接していてもよい。しかし、本開示がこれに限定されるものではなく、透明導電層が第1LEDスタック23上に配置できることを理解しなければならない。第2ボンディング層55は、第1LEDスタック23から発生する光を透過させる。第2ボンディング層55は、例えば、透明無機絶縁層、透明有機絶縁層または透明導電層であってもよく、例えば、光透過性スピンオンガラスで形成される。

第3ボンディング層57は、第3LEDスタック43を第2LEDスタック33に結合する。図示のように、第3ボンディング層57は、第2LEDスタック33にモノリシックに結合される第2基板31に隣接していてもよく、第2カラーフィルタ47にも隣接していてよい。しかし、本開示がこれに限定されるものではないことを理解しなければならない。第2基板31が省略されると、第3ボンディング層57は、第2LEDスタック33に隣接していてもよい。また、透明導電層が第2LEDスタック33または第2基板31上に配置され、第3ボンディング層57は、透明導電層に隣接していてもよい。第3ボンディング層57は、第1LEDスタック23および第2LEDスタック33から発生する光を透過させる。第3ボンディング層57は、例えば、透明無機絶縁層、透明有機絶縁層または透明導電層であってもよく、例えば、光透過性スピンオンガラスで形成される。

図2は、本開示の1つの例示的な実施例によるディスプレイ用発光ダイオードスタックを製造する方法を示す概略断面図である。

図2を参照すると、まず、第1LEDスタック23が第1基板21上に成長し、第1−p反射電極25が第1LEDスタック23上に形成される。

第1基板21は、例えば、GaAs基板であってもよい。加えて、第1LEDスタック23は、AlGaInP系半導体層で構成され、n型半導体層と、活性層と、p型半導体層とを含む。第1−p反射電極25は、p型半導体層とオーミック接触を形成する。

一方、第2LEDスタック33が第2基板31上に成長し、第2−p透明電極35および第1カラーフィルタ37が第2LEDスタック33上に形成される。第2LEDスタック33は、GaN系半導体層で構成され、GaInN井戸層を含むことができる。第2基板31は、GaN系半導体層に対する均質基板であり、例えば、GaN基板であってもよい。また、第2基板31は、n型ドーパントでドーピングされたn型半導体であってもよい。第2LEDスタック33のためのGaInNの組成比は、第2LEDスタック33が緑色光を放出するように決定されてもよい。一方、第2−p透明電極35は、p型半導体層とオーミック接触を形成する。

また、第3LEDスタック43が第3基板41上に成長し、第3−p透明電極45および第2カラーフィルタ47が第3LEDスタック43上に形成される。第3LEDスタック43は、GaN系半導体層で構成され、GaInN井戸層を含むことができる。第3基板41は、GaN系半導体層に対する均質基板であり、例えば、GaN基板であってもよい。第3LEDスタック43のためのGaInNの組成比は、第3LEDスタック43が青色光を放出するように決定されてもよい。他方、第3−p透明電極45は、p型半導体層とオーミック接触を形成する。

第1カラーフィルタ37および第2カラーフィルタ47は、図1を参照して説明したものと同一であり、その繰り返される説明は省略する。

図1および図2を参照すると、第1LEDスタック23が第1ボンディング層53を経由して支持基板51に結合される。第1ボンディング層53は、支持基板51上に予め形成されてもよく、第1−p反射電極25は、支持基板51に向かうように配置され、第1ボンディング層53にボンディングされてもよい。第1基板21が化学的エッチングにより第1LEDスタック23から除去される。

その後、第2LEDスタック33が第2ボンディング層55を経由して第1LEDスタック23に結合される。第1カラーフィルタ37は、第1LEDスタック23に向かうように配置され、第2ボンディング層55にボンディングされる。第2ボンディング層55は、第1LEDスタック23上に予め形成されてもよく、第1カラーフィルタ37は、第2ボンディング層55に向かうように配置され、第2ボンディング層55にボンディングされてもよい。第2基板31は、第2基板が成長基板として用いられる場合に比べて、薄化工程(thinning proces)により減少した厚さを有することができる。また、第2基板31全体が除去可能である。

その後、第3LEDスタック43が第3ボンディング層57を経由して第2LEDスタック33に結合される。第2カラーフィルタ47は、第2基板31に向かうように配置され、第3ボンディング層57にボンディングされる。第3ボンディング層57は、第2基板31上に予め配置されてもよく、第2カラーフィルタ47は、第3ボンディング層57に向かうように配置され、第3ボンディング層57にボンディングされてもよい。結果として、図1に示すように、外部に露出する第3LEDスタック43を有する、ディスプレイ用発光ダイオードスタックが提供される。第3基板41はさらに、薄化工程が施されてもよく、完全に除去されてもよい。

ディスプレイ装置が、ピクセルユニット内の支持基板51上で第1〜第3LEDスタック23、33および43のスタックをパターニングし、次いで、インターコネクションラインを介して第1〜第3LEDスタックを互いに接続することにより提供できる。以下、ディスプレイ装置の例示的な実施例を説明する。

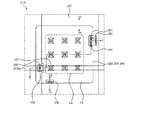

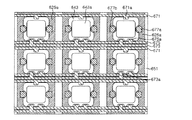

図3は、本開示の1つの例示的な実施例によるディスプレイ装置の作動を示す概略回路図であり、図4は、本開示の例示的な実施例によるディスプレイ装置の概略平面図である。

まず、図3および図4を参照すると、本例示的な実施例によるディスプレイ装置は、パッシブマトリクス方式で作動するように実現できる。

例えば、図1を参照して説明したディスプレイ用発光ダイオードスタックは、第1〜第3LEDスタック23、33および43が垂直方向に積層される構造を有するので、1つのピクセルが3つの発光ダイオードR、GおよびBを含む。第1発光ダイオードRは、第1LEDスタック23に対応し、第2発光ダイオードGは、第2LEDスタック33に対応し、第3発光ダイオードBは、第3LEDスタック43に対応する。

図3および図4で、1つのピクセルは、第1〜第3発光ダイオードR、GおよびBを含み、そのそれぞれは、サブピクセルに対応する。第1〜第3発光ダイオードR、GおよびBのアノードは、共通ライン、例えば、データラインに接続され、そのカソードは、異なるライン、例えば、スキャンラインに接続される。例えば、第1ピクセルにおいて、第1〜第3発光ダイオードR、GおよびBのアノードは、データラインVdata1に共通に接続され、そのカソードは、スキャンラインVscan1−1、Vscan1−2およびVscan1−3にそれぞれ接続される。結果として、各ピクセル内の発光ダイオードR、GおよびBは、独立して駆動可能である。

また、発光ダイオードR、GおよびBのそれぞれは、パルス幅変調によってまたは電流の大きさを変更することにより駆動され、それによって、各サブピクセルの明るさの調節を可能にする。

図4を再度参照すると、複数のピクセルが図1を参照して説明したスタックをパターニングすることにより形成され、各ピクセルは、第1−p反射電極25およびインターコネクションライン71、73および75に接続される。図3に示すように、第1−p反射電極25は、データラインVdataとして使用可能であり、インターコネクションライン71、73および75は、スキャンラインとして形成可能である。

ピクセルは、各ピクセルの発光ダイオードR、GおよびBのアノードが第1−p反射電極25に共通に接続され、そのカソードが互いに分離されたインターコネクションライン71、73および75に接続される、マトリクス状に配列される。インターコネクションライン71、73および75は、スキャンラインVscanとして使用可能である。

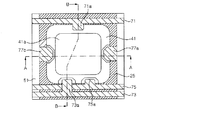

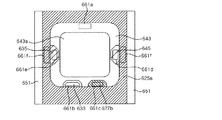

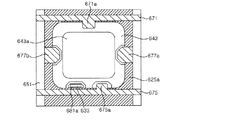

図5は、図4に示すディスプレイ装置の1つのピクセルの拡大平面図であり、図6は、図5のA−A線に沿った概略断面図であり、図7は、図5のB−B線に沿った概略断面図である。

図4、図5、図6および図7を参照すると、各ピクセルにおいて、第1−p反射電極25の一部分、第1LEDスタック23の上部表面の一部分、第2−p透明電極35の一部分、第2基板31の上部表面の一部分、第3−p透明電極45の一部分、および第3基板41の上部表面が外部に露出する。

第3LEDスタック43は、その上部表面上に粗面化された表面43aを有してもよい。粗面化された表面43aは、図示のように、第3基板41の上部表面の全体にわたって形成されるか、またはそのいくつかの領域に形成されてもよい。第3基板41が除去される構造では、粗面化された表面は、第3LEDスタック43上に形成される。

第1絶縁層61は、各ピクセルの側面を覆うことができる。第1絶縁層61は、SiO2のような光透過性材料で形成される。この場合、第1絶縁層61は、第3基板41の全体上部表面を覆うことができる。その代わりとして、第1絶縁層61は、分布ブラッグ反射器を含み、第1〜第3LEDスタック23、33および43の側面に向かって進行する光を反射させてもよい。この場合、第1絶縁層61は、第3基板41の上部表面を少なくとも部分的に露出させる。

第1絶縁層61は、第3基板41の上部表面を露出させる開口部61aと、第2基板31の上部表面を露出させる開口部61bと、第1LEDスタック23のオーミック電極29を露出させる開口部61c(図8H参照)と、第3−p透明電極45を露出させる開口部61dと、第2−p透明電極35を露出させる開口部61eと、第1−p反射電極25を露出させる開口部61fとを含むことができる。

インターコネクションライン71および75は、支持基板51上で第1〜第3LEDスタック23、33および43近傍に形成され、第1−p反射電極25から絶縁されるように第1絶縁層61上に配置される。一方、第1LEDスタック23、第2LEDスタック33および第3LEDスタック43のアノードが第1−p反射電極25に共通に接続されるように、接続部分77aが第3−p透明電極45を第1−p反射電極25に接続し、接続部分77bが第2−p透明電極35を第1−p反射電極25に接続する。

接続部分71aは、第3基板41の上部表面をインターコネクションライン71に接続し、接続部分75aは、第1LEDスタック23の上部表面をインターコネクションライン75に接続する。

第2絶縁層81がインターコネクションライン71および73上に配置されて第3基板41の上部表面を覆うことができる。第2絶縁層81は、第2基板31の上部表面を部分的に露出させる開口部81aを有してもよい。

インターコネクションライン73は、第2絶縁層81上に配置され、接続部分73aは、第2基板31の上部表面をインターコネクションライン73に接続することができる。接続部分73aは、インターコネクションライン75の上部部分を通過することができ、第2絶縁層81によってインターコネクションライン75から絶縁される。

各ピクセルの電極が本例示的な実施例でデータラインおよびスキャンラインに接続されるものと説明されるが、多様な実施形態が可能であることを理解しなければならない。本例示的な実施例では、インターコネクションライン71および75が第1絶縁層61上に形成され、インターコネクションライン73が第2絶縁層81上に形成されるが、本開示がこれに限定されないことを理解しなければならない。例えば、すべてのインターコネクションライン71、73および73が第1絶縁層61上に形成され、インターコネクションライン73を露出させるように構成される開口部を有し得る、第2絶縁層81によって覆われてもよい。この構造において、接続部分73aは、第2基板31の上部表面を第2絶縁層81の開口部を介してインターコネクションライン73に接続することができる。

その代わりとして、インターコネクションライン71、73および75は、支持基板51の内部に形成され、第1絶縁層61上の接続部分71a、73aおよび75aは、第1LEDスタック23の上部表面および第2および第3基板31および41の上部表面をインターコネクションライン71、73および75に接続してもよい。

図8A〜図8Kは、本開示の1つの例示的な実施例によるディスプレイ装置を製造する方法を示す概略断面図である。以下の説明は、図5のピクセルを形成する方法について与えられる。

まず、図1で説明した発光ダイオードスタック100が用意される。

その後、図8Aを参照すると、粗面化された表面41aが第3基板41の上部表面上に形成される。粗面化された表面41aは、各ピクセル領域に対応するように第3基板41の上部表面上に形成される。粗面化された表面41aは、化学的エッチング、例えば、光−増強化学的エッチング(photo−enhanced chemical etching:PEC)により形成される。

粗面化された表面41aは、後続の工程でエッチングされる第3基板41の領域を考慮して各ピクセル領域内に部分的に形成されてもよいが、これに限定されるものではない。その代わりとして、粗面化された表面41aは、第3基板41の全体上部表面にわたって形成されてもよい。

図8Bを参照すると、各ピクセルにおいて第3基板41および第3LEDスタック43の周囲領域がエッチングにより除去されて、第3−p透明電極45を露出させる。図示のように、第3基板41は、長方形状または正方形状を有するように保持できる。複数の陥没部が第3基板41および第3LEDスタック43の周縁に沿って形成される。これらの陥没部は、第3基板41および第3LEDスタック43上に連続的に形成されてもよい。

図8Cを参照すると、1つの陥没部内で露出する第3−p透明電極45の一部分を除いた他の領域で露出する第3−p透明電極45を除去することにより、第2基板31の上部表面が露出する。したがって、第2基板31の上部表面は、第3基板41の周囲で、そして第3−p透明電極45が部分的に残留する陥没部を除いた他の陥没部内で露出する。

図8Dを参照すると、1つの陥没部内で露出する第2基板31の一部分を除いた他の領域で露出する第2基板31を除去し、次いで、第2LEDスタック33を除去することにより、第2−p透明電極35が露出する。

図8Eを参照すると、1つの陥没部内で露出する第2−p透明電極35の一部分を除いた他の領域で露出する第2−p透明電極35を除去することにより、第1LEDスタック23の上部表面が露出する。したがって、第1LEDスタック23の上部表面が第3基板41の周囲で露出し、第1LEDスタック23の上部表面は、第3基板41内に形成される陥没部のうちの少なくとも1つ内で露出する。

図8Fを参照すると、1つの陥没部内で露出する第1LEDスタック23を除いた他の領域で第1LEDスタック23の露出する部分を除去することにより、第1−p反射電極25が露出する。第1−p反射電極25は、第3基板41の周囲で露出する。

図8Gを参照すると、線形インターコネクションラインが第1−p反射電極25をパターニングすることにより形成される。ここで、支持基板51が露出してもよい。第1−p反射電極25は、マトリクスに配列されるピクセルのうちの1つの行(row)内に配列されるピクセルを互いに接続することができる(図4参照)。

図8Hを参照すると、第1絶縁層61(図6および図7参照)がピクセルを覆うように形成される。第1絶縁層61は、第1−p反射電極25、第1〜第3LEDスタック23、33および43の側面および第2および第3基板31および41の側面を覆う。加えて、第1絶縁層61は、第3基板41の上部表面を少なくとも部分的に覆うことができる。第1絶縁層61がSiO2層のような透明層であれば、第1絶縁層61は、第3基板41の全体上部表面を覆うことができる。その代わりとして、第1絶縁層61は、分布ブラッグ反射器を含んでもよい。この場合、第1絶縁層61は、第3基板41の上部表面を少なくとも部分的に露出させて、光が外部に放出されることを許容することができる。

第1絶縁層61は、第3基板41を露出させる開口部61aと、第2基板31を露出させる開口部61bと、第1LEDスタック23を露出させる開口部61cと、第3−p透明電極45を露出させる開口部61dと、第2−p透明電極35を露出させる開口部61eと、第1−p反射電極25を露出させる開口部61fとを含むことができる。第1−p反射電極25を露出させるように適合化される開口部61fは、複数形成されてもよい。

図8Iを参照すると、インターコネクションライン71および75および接続部分71a、75a、77aおよび77bが形成される。これらはリフトオフ工程により形成される。インターコネクションライン71および75は、第1絶縁層61によって第1−p反射電極25から絶縁される。接続部分71aは、第3基板41をインターコネクションライン71に電気的に接続し、接続部分75aは、第1LEDスタック23をインターコネクションライン75に電気的に接続する。接続部分77aは、第3−p透明電極45を第1−p反射電極25に電気的に接続し、接続部分77bは、第2−p透明電極35を第1−p反射電極25に電気的に接続する。

図8Jを参照すると、第2絶縁層81(図6および図7参照)がインターコネクションライン71および75および接続部分71a、75a、77aおよび77bを覆う。第2絶縁層81も、第3基板41の全体上部表面を覆うことができる。第2絶縁層81は、第2基板31の上部表面を露出させる開口部81aを有する。第2絶縁層81は、例えば、シリコン酸化物またはシリコン窒化物で形成され、分布ブラッグ反射器を含むことができる。第2絶縁層81が分布ブラッグ反射器を含む構造において、第2絶縁層81は、第3基板41の上部表面の少なくとも一部を露出させるように形成されて、光が外部に放出されることを許容する。

図8Kを参照すると、インターコネクションライン73および接続部分73aが形成される。インターコネクションライン75および接続部分73aは、リフトオフ工程により形成される。インターコネクションライン73は、第2絶縁層81上に配置され、第1−p反射電極25およびインターコネクションライン71および75から絶縁される。接続部分73aは、第2基板31をインターコネクションライン73に電気的に接続する。接続部分73aは、インターコネクションライン75の上部部分を貫通することができ、第2絶縁層81によってインターコネクションライン75から絶縁される。

結果として、ピクセル領域が図5に示すように完成する。加えて、図4に示すように、複数のピクセルが支持基板51上に形成され、第1−p反射電極25およびインターコネクションライン71、73および75によって互いに接続されて、パッシブマトリクス方式で動作可能である。

パッシブマトリクス方式で動作するように適合化されるディスプレイ装置を製造する方法を本例示的な実施例で示したが、本開示がこれに限定されないことを理解しなければならない。すなわち、例示的な実施例によるディスプレイ装置は、図1に示す発光ダイオードスタックを用いてパッシブマトリクス方式で動作するように多様な方式で製造できる。

例えば、本例示的な実施例において、インターコネクションライン73が第2絶縁層81上に形成されるものとして示されるが、インターコネクションライン73は、第1絶縁層61上でインターコネクションライン71および75とともに形成されてもよいし、接続部分73aは、第2絶縁層81上に形成されて第2基板31をインターコネクションライン73に接続することができる。その代わりとして、インターコネクションライン71、73および75は、支持基板51の内部に配置されてもよい。

図9は、本開示のもう1つの例示的な実施例によるディスプレイ装置の作動を示す概略回路図である。上記の実施例は、パッシブマトリクス方式で駆動されるディスプレイ装置に関するのに対し、本例示的な実施例は、アクティブマトリクス方式で駆動されるディスプレイ装置に関するものである。

図9を参照すると、本例示的な実施例による駆動回路は、2つ以上のトランジスタTr1およびTr2およびキャパシタを含む。電源が選択ラインVrow1〜Vrow3に接続され、電圧がデータラインVdata1〜Vdata3に印加されると、電圧が対応する発光ダイオードに印加される。また、対応するキャパシタは、データラインVdata1〜Vdata3の値に応じて充電される。トランジスタTr2のターンオン状態がキャパシタの充電された電圧によって保持できるので、キャパシタの電圧は、選択ラインVrow1に供給される電源が遮断されても保持されて発光ダイオードLED1〜LED3に印加される。さらに、発光ダイオードLED1〜LED3内で流れる電流は、データラインVdata1〜Vdata3の値に応じて変更可能である。電流は、電流供給源Vddを介して連続的に供給可能であり、それによって、連続的な発光を可能にする。

トランジスタTr1およびTr2およびキャパシタは、支持基板51の内部で形成される。例えば、シリコン基板上に形成される薄膜トランジスタがアクティブマトリクス駆動のために使用可能である。

発光ダイオードLED1〜LED3は、1つのピクセル内に積層される第1〜第3LEDスタック23、33および43にそれぞれ対応する。第1〜第3LEDスタックのアノードは、トランジスタTr2に接続され、そのカソードは、接地(ground)に接続される。

たとえアクティブマトリクス駆動のための回路の一例が本例示的な実施例で示されたとしても、他の類型の回路も使用可能であることを理解しなければならない。加えて、本例示的な実施例において、発光ダイオードLED1〜LED3のアノードが互いに異なるトランジスタTr2に接続され、そのカソードが接地に接続されるが、他の例示的な実施例において、発光ダイオードのアノードは、電流供給源Vddに接続され、そのカソードは、互いに異なるトランジスタに接続されてもよい。

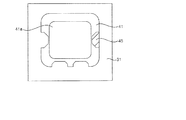

図10は、本開示のもう1つの例示的な実施例によるディスプレイ装置の概略平面図である。以下の説明は、支持基板151上に配列される複数のピクセルのうちの1つのピクセルについて与えられる。

図10を参照すると、本例示的な実施例によるピクセルは、支持基板151がトランジスタおよびキャパシタを含む薄膜トランジスタパネルであり、第1−p反射電極25が第1LEDスタック23の下部領域内に制限的に位置することを除けば、図4〜図7を参照して説明したピクセルと実質的に類似している。

第3LEDスタック43のカソードは、接続部分171aを介して支持基板151に接続される。例えば、図9に示すように、第3LEDスタック43のカソードは、支持基板151への電気的な接続により接地に接続される。第2LEDスタック33および第1LEDスタック23のカソードはさらに、接続部分173aおよび175aを経由した支持基板151への電気的な接続により接地に接続されてもよい。

一方、第1−p反射電極25は、支持基板151の内部でトランジスタTr2(図9参照)に接続される。第3−p透明電極45および第2−p透明電極35も、接続部分171aおよび173bを介して支持基板151の内部でトランジスタTr2(図9参照)に接続される。

この方式により、第1〜第3LEDスタック23、33および43は、互いに接続され、それによって、図9に示すように、アクティブマトリクス駆動のための回路を構成する。

アクティブマトリクス駆動のための電気的な接続の一例が本例示的な実施例で示されるが、本開示がこれに限定されるものではなく、ディスプレイ装置用回路が多様な方式でアクティブマトリクス駆動のための多様な回路に変形可能であることを理解しなければならない。

一方、図1を参照して説明した例示的な実施例では、第1−p反射電極25、第2−p透明電極35および第3−p透明電極45がそれぞれ第1LEDスタック23、第2LEDスタック33および第3LEDスタック43のp型半導体層とオーミック接触を形成するが、第2基板31および第3基板41のそれぞれには別途のオーミック接触層が提供されない。ピクセルが200μm以下の小さい大きさを有する場合、n型半導体層内に別途のオーミック接触層を形成しなくても、電流拡散(curent spreading)における困難がない。しかし、電流拡散を確保するために、透明電極層が第2基板31および第3基板41のそれぞれの上に配置されてもよい。

加えて、第1〜第3LEDスタック23、33および43は、多様な構造で互いに接続される。

図11は、本開示のもう1つの例示的な実施例によるディスプレイ用発光ダイオードスタック101の概略断面図である。

図11を参照すると、図1を参照して説明した発光ダイオードスタック100と同じく、発光ダイオードスタック101は、支持基板51と、第1LEDスタック23と、第2LEDスタック33と、第3LEDスタック43と、第2基板31と、第3基板41と、第2−p透明電極35と、第3−p透明電極45と、第1カラーフィルタ137と、第2カラーフィルタ47と、第1ボンディング層153と、第2ボンディング層155と、第3ボンディング層157とを含む。加えて、発光ダイオードスタック101は、第1−n反射電極129と、第1−p透明電極125と、第2−n透明電極139とをさらに含んでもよい。

支持基板51は、半導体スタック23、33および43を支持する。支持基板51は、その表面上にまたはその内部に回路を含むことができるが、これに限定されるものではない。支持基板51は、例えば、Si基板またはGe基板を含むことができる。

第1LEDスタック23、第2LEDスタック33および第3LEDスタック43は、図1を参照して説明したものと類似しており、その詳細な説明は省略する。しかし、本例示的な実施例は、第1LEDスタック23および第2LEDスタック33のそれぞれがn型下部表面およびp型上部表面を有するという点から、図1に示す例示的な実施例とは異なる。図1に示す例示的な実施例におけるのと同じく、本例示的な実施例による第3LEDスタック43は、p型下部表面およびn型上部表面を有する。

第2基板31および第3基板41は、図1を参照して説明したものと類似しており、その詳細な説明は省略する。

一方、第1LEDスタック23がp型上部表面を有するので、第1−p透明電極125は、第1LEDスタック23の上部表面とオーミック接触を形成する。第1−p透明電極125は、第1LEDスタック23から発生する光、例えば、赤色光を透過させる。

第1−n反射電極129は、第1LEDスタック23の下部表面とオーミック接触を形成する。第1−n反射電極129は、第1LEDスタック23とオーミック接触を形成し、第1LEDスタック23から発生する光を反射させる。第1−n反射電極129は、例えば、Au−TiまたはAu−Snで形成される。また、第1−n反射電極129は、拡散バリア層を含むことができる。

第2−p透明電極35は、第2LEDスタック33のp型半導体層とオーミック接触を形成する。第2LEDスタック33がp型上部表面を有するので、第2−p透明電極35は、第2LEDスタック33上に配置される。第2−p透明電極35は、赤色光および緑色光に関して透過性である金属層または導電性酸化物層で構成される。

第2−n透明電極139は、第2基板31の下部表面とオーミック接触を形成することができる。第2−n透明電極139も、赤色光および緑色光に関して透過性である金属層または導電性酸化物層で構成される。第2−n透明電極139は、第2LEDスタック33および第2基板31をパターニングすることにより部分的に露出して、第2LEDスタック33のn型半導体層への電気的な接続のための接続端子を提供する。

第3−p透明電極45は、第3LEDスタック43のp型半導体層とオーミック接触を形成する。第3−p透明電極45は、赤色光、緑色光および青色光に関して透過性である金属層または導電性酸化物層で構成される。

第1カラーフィルタ137は、第1LEDスタック23と第2LEDスタック33との間に介在する。加えて、第2カラーフィルタ47は、第2LEDスタック33と第3LEDスタック43との間に介在する。第1カラーフィルタ137は、第1LEDスタック23から発生する光を透過させ、第2LEDスタック33から発生する光を反射させる。一方、第2カラーフィルタ47は、第1および第2LEDスタック23および33から発生する光を透過させ、第3LEDスタック43から発生する光を反射させる。したがって、第1LEDスタック23から発生する光は、第2基板31、第2LEDスタック33、第3LEDスタック43および第3基板41を介して外部に放出され、第2LEDスタック33から発生する光は、第3LEDスタック43および第3基板41を介して外部に放出される。また、発光ダイオードスタック101は、第2LEDスタック33から発生する光が第1LEDスタック23に進入するのを防止することができ、第3LEDスタック43から発生する光が第2LEDスタック33に進入するのを防止することができ、それによって、光損失を防止する。第1LEDスタック23から発生する光は、第1−p透明電極125、第2−p透明電極35、第2−n透明電極139および第3−p透明電極45を介して外部に放出される。さらに、第2LEDスタック33から発生する光は、第2−p透明電極35および第3−p透明電極45を介して外部に放出される。

いくつかの例示的な実施例において、第1カラーフィルタ137は、第3LEDスタック43から発生する光を反射させることができる。

第1および第2カラーフィルタ137および47は、例えば、低周波数帯域で、すなわち、長波長帯域で、光のそれを介した通過を許容するローパスフィルタ、所定の波長帯域で光のそれを介した通過を許容するバンドパスフィルタ、または所定の波長帯域で光のそれを介した通過を防止するバンドストップフィルタであってもよい。特に、第1および第2カラーフィルタ137および47のそれぞれは、分布ブラッグ反射器(DBR)を含むバンドストップフィルタであってもよい。分布ブラッグ反射器は、互いに異なる屈折率を有する絶縁層、例えば、TiO2およびSiO2を交互に積層することにより形成可能である。同時に、分布ブラッグ反射器の阻止帯域は、TiO2およびSiO2層の厚さを調節することにより制御可能である。ローパスフィルタおよびバンドパスフィルタも、互いに異なる屈折率を有する絶縁層を交互に積層することにより形成可能である。

第1ボンディング層153は、第1LEDスタック23を支持基板51に結合する。図示のように、第1−n反射電極129は、第1ボンディング層153に隣接していてもよい。第1ボンディング層153は、光透過性または不透明層であってもよい。第1ボンディング層153は、例えば、透明無機絶縁層、透明有機絶縁層または透明導電層であってもよい。

第2ボンディング層155は、第2LEDスタック33を第1LEDスタック23に結合する。図示のように、第2ボンディング層155は、第1カラーフィルタ137上に配置され、第2−n透明電極139に隣接していてもよい。第2ボンディング層155は、第1LEDスタック23から発生する光を透過させる。第2ボンディング層155は、例えば、透明無機絶縁層、透明有機絶縁層または透明導電層であってもよく、例えば、光透過性スピンオンガラスで形成される。

第3ボンディング層157は、第3LEDスタック43を第2LEDスタック33に結合する。図示のように、第3ボンディング層157は、第2−p透明電極35および第2カラーフィルタ47に隣接していてもよい。第3ボンディング層157は、第1LEDスタック23および第2LEDスタック33から発生する光を透過させる。第3ボンディング層157は、例えば、透明無機絶縁層、透明有機絶縁層または透明導電層であってもよく、例えば、光透過性スピンオンガラスで形成される。

図12A〜図12Fは、本開示のさらに他の例示的な実施例によるディスプレイ用発光ダイオードスタックを製造する方法を示す概略断面図である。

図12Aを参照すると、まず、第3LEDスタック43が第3基板41上に成長し、第3−p透明電極45および第2カラーフィルタ47が第3LEDスタック43上に形成される。第3LEDスタック43は、GaN系半導体層で構成され、GaInN井戸層を含むことができる。第3基板41は、GaN系半導体層に対する均質基板であり、例えば、n型ドーパントでドーピングされたGaN基板であってもよい。第3LEDスタック43のためのGaInNの組成比は、第3LEDスタック43が青色光を放出するように決定されてもよい。第3−p透明電極45は、p型半導体層とオーミック接触を形成する。

図12Bを参照すると、第2LEDスタック33が第2基板31上に成長し、第2−p透明電極35が第2LEDスタック33上に形成される。第2LEDスタック33は、GaN系半導体層で構成され、GaInN井戸層を含むことができる。第2基板31は、GaN系半導体層に対する均質基板であり、例えば、n型ドーパントでドーピングされたGaN基板であってもよい。第2LEDスタック33のためのGaInNの組成比は、第2LEDスタック33が緑色光を放出するように決定されてもよい。一方、第2−p透明電極35は、p型半導体層とオーミック接触を形成する。

第2基板31は、第3ボンディング層157が第2カラーフィルタ47に提供され、第2基板31上の第2−p透明電極35が第3ボンディング層157に隣接するように配置される。第3ボンディング層157は、例えば、スピンオンガラスで形成される。したがって、第2LEDスタック33は、第3LEDスタック43に結合される。

図12Cを参照すると、第2−n透明電極139が第2基板31上に形成される。第2−n透明電極139は、第2基板31とオーミック接触を形成する。第2−n透明電極139は、金属層または導電性酸化物層で構成される。第2−n透明電極139は省略可能である。

図12Dを参照すると、第1LEDスタック23が第1基板21上に成長し、第1−p透明電極125が第1LEDスタック23上に形成され、第1カラーフィルタ137が第1−p透明電極125上に形成される。

第1基板21は、例えば、GaAs基板であってもよい。加えて、第1LEDスタック23は、AlGaInP系半導体層で構成され、n型半導体層と、活性層と、p型半導体層とを含む。第1−p透明電極125は、p型半導体層とオーミック接触を形成する。

第1カラーフィルタ137は、図1を参照して説明したものと実質的に同一であり、繰り返しを避けるためにその詳細な説明は省略する。

その後、第2ボンディング層155が第2−n透明電極139に提供され、第2基板31は、第1基板21上の第1カラーフィルタ137が第2ボンディング層155に隣接するように配置される。第2ボンディング層155は、例えば、スピンオンガラスで形成される。したがって、第1LEDスタック23が第2LEDスタック33に結合される。

図12Eを参照すると、第1LEDスタック23が第2LEDスタック33にボンディングされ、第1基板21は、化学的エッチングにより第1LEDスタック23から除去される。結果として、第1LEDスタック23が露出する。

図12Fを参照すると、第1−n反射電極129が露出した第1LEDスタック23上に形成される。第1−n反射電極129は、第1LEDスタック23から発生する光を反射させる金属層を含む。

その後、第1ボンディング層153が第1−n反射電極129上に配置され、支持基板51がそれにボンディングされる。結果として、図11に示すように、外部に露出する第3基板41を有する発光ダイオードスタック101が提供される。

ピクセルユニット内で支持基板51上の第1〜第3LEDスタック23、33および43のスタック101をパターニングし、次いで、インターコネクションラインを介して第1〜第3LEDスタックを互いに接続することにより、ディスプレイ装置が提供できる。

図13は、本開示の他の例示的な実施例によるディスプレイ用発光ダイオードスタック102の概略断面図である。

図13を参照すると、本例示的な実施例による発光ダイオードスタック102は、第2基板31および第3基板41が除去されることを除けば、図1を参照して説明した発光ダイオードスタック100と概ね類似している。第2基板31および第3基板41は、それぞれ第2LEDスタック33および第3LEDスタック43のための成長基板として用いられた後、第2LEDスタック33および第3LEDスタック43から除去される。第2LEDスタック33および第3LEDスタック43のそれぞれは、均質なGaN系基板上に成長し、それによって、103〜107/cm2の減少した転位密度を提供する。

第2基板31および第3基板41が除去されるので、これらの基板31および41に電気的に接続されるインターコネクションラインは、第2LEDスタック33および第3LEDスタック43にそれぞれ電気的に接続される。加えて、粗面化された表面41aが第3LEDスタック43の上部表面上に形成される。

図14は、本開示のさらに他の1つの例示的な実施例によるディスプレイ用発光ダイオードスタック103の概略断面図である。

図14を参照すると、本例示的な実施例による発光ダイオードスタック103は、第2基板31および第3基板41が除去されることを除けば、図11を参照して説明した発光ダイオードスタック101と概ね類似している。第2基板31および第3基板41は、それぞれ第2LEDスタック33および第3LEDスタック43のための成長基板として用いられた後、第2LEDスタック33および第3LEDスタック43から除去される。第2LEDスタック33および第3LEDスタック43のそれぞれは、均質なGaN系基板上に成長し、それによって、103〜107/cm2の減少した転位密度を提供する。

第2基板31および第3基板41が除去されるので、これらの基板31および41に電気的に接続されるインターコネクションラインは、第2LEDスタック33および第3LEDスタック43にそれぞれ電気的に接続される。加えて、粗面化された表面41aが第3LEDスタック43の上部表面上に形成される。

例示的な実施例によれば、ディスプレイ用発光ダイオードスタック100;101;102;および103を用いてウエハレベルで複数のピクセルを形成することが可能なため、発光ダイオードを個別に実装する必要がない。加えて、例示的な実施例による発光ダイオードスタックは、第1〜第3LEDスタック23、33および43が垂直方向に積層される構造を有し、それによって、限られたピクセル面積内でサブピクセルのための面積を確保する。また、例示的な実施例による発光ダイオードスタックは、第1LEDスタック23、第2LEDスタック33および第3LEDスタック43から発生する光がそれを介して外部に放出されることを許容し、それによって、光損失を減少させる。さらに、第2LEDスタック33および第3LEDスタック43のそれぞれが均質基板上に成長してその転位密度を減少させることができ、それによって、発光効率を向上させる。また、第2基板31および第3基板41が除去されずに第2LEDスタック33および第3LEDスタック43上に残留可能であり、それによって、発光ダイオードスタックを製造する工程を単純化する。

図15は、本開示の例示的な実施例による発光積層構造を示す断面図である。

図15を参照すると、本開示の例示的な実施例による発光積層構造は、互いに積層される複数のエピタキシャルスタックを含む。エピタキシャルスタックは、基板210上に配置される。

基板210は、前面および後面が提供されるプレート形状を有する。

基板210は、エピタキシャルスタックがその上に実装される前面がそれぞれ提供される、多様な形状を有することができる。基板210は、絶縁材料を含むことができる。基板210の材料として、ガラス、石英、シリコン、有機ポリマーまたは有機−無機複合材料が使用できるが、これにまたはこれによって限定されるものではない。すなわち、基板210の材料は、絶縁特性を有する限り、特に限定されるべきではない。本開示の例示的な実施例において、ライン部(line part)が基板210上にさらに配置され、各エピタキシャルスタックに発光信号および共通電圧を印加することができる。特に、各エピタキシャルスタックがアクティブマトリクス方法によって作動する場合、薄膜トランジスタを含む駆動デバイスがライン部に加えて基板上にさらに配置されてもよい。このために、基板210は、ライン部および/または駆動デバイスをガラス、石英、シリコン、有機ポリマーまたは有機−無機複合材料上に形成することにより得られる、印刷回路基板または複合基板として提供できる。

エピタキシャルスタックは、基板210の前面上に順に積層される。

本開示の例示的な実施例において、2つ以上のエピタキシャルスタックが提供され、エピタキシャルスタックは、互いに異なる波長帯域を有する光を放出する。すなわち、エピタキシャルスタックは、複数提供され、エピタキシャルスタックは、互いに異なるエネルギーバンドを有する。本例示的な実施例では、基板210上に順に積層される3つのエピタキシャルスタックが示される。以下の実施例において、基板210上に順に積層される3つの層は、第1、第2および第3エピタキシャルスタック220、230および240としてそれぞれ言及される。

各エピタキシャルスタックは、多様な波長帯域の光のうち、可視光帯域の色光を放出することができる。最下端に配置されるエピタキシャルスタックから放出される光は、最も低いエネルギーバンドを有する最も長い波長の色光であり、エピタキシャルスタックから放出される色光の波長は、エピタキシャルスタックの底から頂部まで次第に短くなる。最上端に配置されるエピタキシャルスタックから放出される光は、最も高いエネルギーバンドを有する最も短い波長の色光である。例えば、第1エピタキシャルスタック220は、第1色光L1を放出し、第2エピタキシャルスタック230は、第2色光L2を放出し、第3エピタキシャルスタック240は、第3色光L3を放出する。第1、第2および第3色光L1、L2およびL3は、互いに異なる色光であってもよく、第1、第2および第3色光L1、L2およびL3は、順に短くなる互いに異なる波長帯域を有する色光であってもよい。すなわち、第1、第2および第3色光L1、L2およびL3は、互いに異なる波長帯域を有してもよく、色光は、第1色光L1から第3色光L3まで次第に高いエネルギーを有する次第に短い波長帯域の色光であってもよい。

本例示的な実施例において、第1色光L1は、赤色光であってもよく、第2色光L2は、緑色光であってもよいし、第3色光L3は、青色光であってもよい。

各エピタキシャルスタックは、基板210の前面が向かう方向に進行するように光を放出する。この場合、1つのエピタキシャルスタックから放出される光は、当該エピタキシャルスタックから放出される光の光路上に位置する他のエピタキシャルスタックを通過した後、基板210の前面が向かう方向に進行する。基板210の前面が向かう方向は、第1、第2および第3エピタキシャルスタック220、230および240が積層される方向を示す。

以下、説明の便宜のために、基板210の前面が向かう方向は、「前面方向」または「上方向」と称し、基板210の後面が向かう方向は、「後面方向」または「下方向」と称する。しかし、「上」および「下」という用語は、互いに相対的な方向を示し、発光積層構造体の配列または積層方向によって変化可能である。

各エピタキシャルスタックは、光を上方向に放出し、その下に配置されるエピタキシャルスタックから放出される光の大部分を透過させる。すなわち、第1エピタキシャルスタック220から放出される光は、第2エピタキシャルスタック230および第3エピタキシャルスタック240を通過した後、前面方向に進行し、第2エピタキシャルスタック230から放出される光は、第3エピタキシャルスタック240を通過した後、前面方向に進行する。このために、最下端に配置されるエピタキシャルスタックを除いた他のエピタキシャルスタックの少なくとも一部分、好ましくは、全体部分は、光透過性材料で形成される。「光透過性材料」という用語は、光透過性材料がすべての光を透過させる場合のみならず、光透過性材料が所定の波長を有する光または所定の波長を有する光の一部分を透過させる場合も表す。例示的な実施例において、各エピタキシャルスタックは、その下に配置されるエピタキシャルスタックからの光の約60%以上を透過させることができる。他の実施例により、各エピタキシャルスタックは、その下に配置されるエピタキシャルスタックからの光の約80%以上を透過させることができ、他の実施例により、各エピタキシャルスタックは、その下に配置されるエピタキシャルスタックからの光の約90%以上を透過させることができる。

本開示の例示的な実施例による上記の構造を有する発光積層構造では、エピタキシャルスタックは、エピタキシャルスタックに発光信号をそれぞれ印加する信号ラインがエピタキシャルスタックに独立に接続されるため、独立して駆動可能であり、光が各エピタキシャルスタックから放出されるかによって多様な色相をディスプレイすることができる。加えて、互いに異なる波長を有する光を放出するエピタキシャルスタックが互いに重なるように形成されるので、発光積層構造は、狭い面積内に形成可能である。

図16は、各エピタキシャルスタックが独立して駆動されることを許容する、ライン部を有する本開示の例示的な実施例による発光積層構造を示す断面図である。図17A〜図17Cは、図16の各エピタキシャルスタックを詳細に示す断面図である。

図16を参照すると、発光積層構造は、発光区域EAと、発光区域EAに隣接して配置される周辺区域PAとを含む。

発光区域EAは、光が第1、第2および第3エピタキシャルスタック220、230および240から上方向に放出される区域である。第1、第2および第3エピタキシャルスタック220、230および240の発光区域EAは、互いに重なり、そのため、第1、第2および第3エピタキシャルスタック220、230および240の発光区域EAは、互いに同一の面積を有する。

周辺区域PAは、第1、第2および第3エピタキシャルスタック220、230および240に接続されるライン部が配置される区域である。光は、周辺区域PA内に配置される第1、第2および第3エピタキシャルスタック220、230および240から放出される。しかし、図示しないが、多様な付加的な構成要素がライン部に加えて周辺区域PA内に配置され、光が外部に出射するのを防止する別途の遮断層または反射層が周辺区域PA内にさらに配置されてもよい。したがって、光が周辺区域PAを介して出射しない。

第1、第2および第3エピタキシャルスタック220、230および240のそれぞれは基板210上に配置され、第1、第2および第3接着層250a、250bおよび250cのうち対応する接着層がその間に介在する。第1、第2および第3接着層250a、250bおよび250cは、非導電性材料を含むことができ、光透過材料を含むことができる。例えば、第1、第2および第3接着層250a、250bおよび250cは、光学用透明接着剤(optically clear adhesive:OCA)を含むことができる。第1、第2および第3接着層250a、250bおよび250cの材料は、第1、第2および第3接着層250a、250bおよび250cの材料が光学的に透明で安定して各エピタキシャルスタックに貼り合わされる限り、特に限定されるべきではない。例えば、第1、第2および第3接着層250a、250bおよび250cは、SU−8、多様なレジスト、パリレン、ポリ(メチルメタクリレート)(PMMA)およびベンゾシクロブテン(BCB)のようなエポキシ系ポリマーのような有機材料およびシリコン酸化物、アルミニウム酸化物および溶融ガラスのような無機材料を含むことができる。また、必要に応じて、導電性酸化物が接着層として使用可能であり、この場合、導電性酸化物は、他の構成要素から絶縁される必要がある。有機材料が接着層として用いられ、無機材料のうち溶融ガラスが接着層として用いられる場合、第1、第2および第3エピタキシャルスタック220、230および240および基板210は、第1、第2および第3エピタキシャルスタック220、230および240および基板210の接着側(adhesive side)上に材料をコーティングし、高真空下で材料に高温および高圧を印加することにより、互いに貼り合わされる。(溶融ガラスを除いた)無機材料が接着層として用いられる場合、第1、第2および第3エピタキシャルスタック220、230および240および基板210は、第1、第2および第3エピタキシャルスタック220、230および240および基板210の接着側上に材料を蒸着し、化学機械的平坦化(CMP)を利用して材料を平坦化し、材料の表面上でプラズマ処理を行い、高真空下で貼り合わされることにより、互いに貼り合わされる。

図17A〜17Cを参照すると、第1、第2および第3エピタキシャルスタック220、230および240は、順に積層される第1半導体層221、231および241、活性層223、233および243および第2半導体層225、235および245を含む。図17A〜図17Cで、第1半導体層221、231および241、活性層223、233および243および第2半導体層225、235および245は、上方向に順に積層されるが、図17A〜図17Cの第1、第2および第3エピタキシャルスタック220、230および240が図16では逆に示されていることに注目しなければならない。すなわち、図16に示す第1、第2および第3エピタキシャルスタック220、230および240は、上方向で第2半導体層225、235および245、活性層223、233および243および第1半導体層221、231および241の順に配列されている。

図17Aを参照すると、第1エピタキシャルスタック220の第1半導体層221、活性層223および第2半導体層225は、赤色光を放出する半導体材料を含むことができる。赤色光を放出する半導体材料として、アルミニウムガリウム砒化物(AlGaAs)、ガリウム砒化リン化物(GaAsP)、アルミニウムガリウムインジウムリン化物(AlGaInP)およびガリウムリン化物(GaP)が使用できる。しかし、赤色光を放出する半導体材料はこれにまたはこれによって限定されるべきではなく、多様な他の材料が使用できる。

第1半導体層221は、第1導電型不純物を含む半導体層であってもよく、第2半導体層225は、第2導電型不純物を含む半導体層であってもよい。第1導電型と第2導電型は、互いに反対の極性を有する。第1導電型がn型の場合、第2導電型はp型であり、第1導電型がp型の場合、第2導電型はn型である。本開示の例示的な実施例において、n型半導体層、活性層およびp型半導体層が順に形成された構造を代表例として説明することとし、第1半導体層221は、「n型半導体層」と称され、第2半導体層225は、「p型半導体層」と称されてもよい。これは説明の便宜のためのものであり、本開示の他の実施例により、第1半導体層221および第2半導体層225は、それぞれp型半導体層およびn型半導体層であってもよい。

n型半導体層221、活性層223およびp型半導体層225の部分を除去することにより、メサ(mesa)が第1エピタキシャルスタック220に形成される。第1n型コンタクト電極229が露出したn型半導体層221の上部表面上に配置され、第1p型コンタクト電極227がメサの形成されたp型半導体層225上に配置される。

第1n型コンタクト電極229および第1p型コンタクト電極227は、金属材料の単層構造または多層構造を有してもよい。例えば、第1n型コンタクト電極229および第1p型コンタクト電極227は、Al、Ti、Cr、Au、Ag、Ti、Sn、Ni、Cr、W、Cuまたはその合金のような金属材料を含むことができる。特に、第1p型コンタクト電極227は、高い反射率を有する金属材料を含むことができ、第1p型コンタクト電極227が高い反射率を有する金属材料を含むので、第1エピタキシャルスタック220から放出される光の上方向への発光効率が向上することができる。

第1エピタキシャルスタック220は、第1接着層250aが間に介在した状態で基板210上に反転して配置されるので、第1n型コンタクト電極229および第1p型コンタクト電極227は、基板210と第2接着層250bとの間に配置される。第1p型コンタクト電極227は、発光区域EAと重なり、第1エピタキシャルスタック220の活性層223から放出される光を上方向に反射させる。

図17Bを参照すると、第2エピタキシャルスタック230は、順に積層されるn型半導体層231、活性層233およびp型半導体層235を含む。n型半導体層231、活性層233およびp型半導体層235は、緑色光を放出する半導体材料を含むことができる。緑色光を放出する半導体材料として、インジウムガリウム窒化物(InGaN)、ガリウム窒化物(GaN)、ガリウムリン化物(GaP)、アルミニウムガリウムインジウムリン化物(AlGaInP)およびアルミニウムガリウムリン化物(AlGaP)が使用できる。しかし、緑色光を放出する半導体材料はこれにまたはこれによって限定されるべきではなく、多様な他の材料が使用できる。

図16を再度参照すると、第2p型コンタクト電極237が第2エピタキシャルスタック230のp型半導体層235上に配置される。図16で、第2エピタキシャルスタック230が図17Bの反転した第2エピタキシャルスタック230に対応するので、第2p型コンタクト電極237は、第1エピタキシャルスタック220と第2エピタキシャルスタック230との間に、詳しくは、第2接着層250bと第2エピタキシャルスタック230との間に配置される。

第2p型コンタクト電極237は、透明導電性材料、例えば、透明導電性酸化物(TCO)を含むことができ、約2000オングストローム〜約2マイクロメートルの厚さを有することができる。

図17Cを参照すると、第3エピタキシャルスタック240は、順に積層されるn型半導体層241、活性層243およびp型半導体層245を含む。n型半導体層241、活性層243およびp型半導体層235は、青色光を放出する半導体材料を含むことができる。青色光を放出する半導体材料として、ガリウム窒化物(GaN)、インジウムガリウム窒化物(InGaN)および亜鉛セレン化物(ZnSe)が使用できる。しかし、青色光を放出する半導体材料はこれにまたはこれによって限定されるべきではなく、多様な他の材料が使用できる。

図16を再度参照すると、第3p型コンタクト電極247が第3エピタキシャルスタック240のp型半導体層245上に配置される。図16で、第3エピタキシャルスタック240が図17Cの反転した第3エピタキシャルスタック240に対応するので、第3p型コンタクト電極247は、第2エピタキシャルスタック230と第3エピタキシャルスタック240との間に、詳しくは、第3接着層250cと第3エピタキシャルスタック240との間に配置される。

本例示的な実施例において、第1、第2および第3エピタキシャルスタック220、230および240のそれぞれのn型半導体層221、231および241およびそれぞれのp型半導体層225、235および245は、単層構造を有するものの、実施例により、第1、第2および第3エピタキシャルスタック220、230および240のそれぞれのn型半導体層221、231および241およびそれぞれのp型半導体層225、235および245は、多層構造を有してもよく、超格子層を含むことができる。第1、第2および第3エピタキシャルスタック220、230および240の活性層223、233および243は、単一量子井戸構造または多重量子井戸構造を有してもよい。

本例示的な実施例において、第2および第3p型コンタクト電極237および247は、発光区域EAと重なるように配置される。第2および第3p型コンタクト電極237および247は、下に配置されるエピタキシャルスタックからの光を透過させるために透明導電性材料を含むことができる。例えば、第2および第3p型コンタクト電極237および247のそれぞれは、透明導電性酸化物(TCO)を含むことができる。透明導電性酸化物は、スズ酸化物(SnO)、インジウム酸化物(InO2)、亜鉛酸化物(ZnO)、インジウムスズ酸化物(ITO)およびインジウムスズ亜鉛酸化物(ITZO)を含むことができる。透明導電性酸化物は、蒸発器またはスパッタを用いた化学気相蒸着(CVD)または物理気相蒸着(PVD)によって蒸着できる。第2および第3p型コンタクト電極237および247は、透過率の満足する範囲内で以下の製造工程でエッチングストッパとして機能するのに十分な厚さを有することができる。

本例示的な実施例において、第1、第2および第3p型コンタクト電極227、237および247は、共通ラインに接続される。共通ラインは、共通電圧が印加されるラインである。また、共通信号ラインは、第2および第3エピタキシャルスタック230および240の第1n型コンタクト電極229およびp型半導体層235および245にそれぞれ接続される。本例示的な実施例において、共通電圧Scが共通ラインを介して第1p型コンタクト電極227、第2p型コンタクト電極237および第3p型コンタクト電極247に印加され、発光信号は、発光信号ラインを介して第1n型コンタクト電極229、第2エピタキシャルスタック230のn型半導体層231および第3エピタキシャルスタック240のn型半導体層241に印加される。したがって、第1、第2および第3エピタキシャルスタック220、230および240の発光が制御される。発光信号は、第1、第2および第3エピタキシャルスタック220、230および240にそれぞれ対応する第1、第2および第3発光信号SR、SGおよびSBを含み、第1、第2および第3発光信号SR、SGおよびSBは、赤色光、緑色光および青色光の発光にそれぞれ対応する信号である。

上述した実施例において、共通電圧が第1、第2および第3エピタキシャルスタック220、230および240のp型半導体層に印加され、発光信号は、第1、第2および第3エピタキシャルスタック220、230および240のn型半導体層に印加されるが、本開示の実施例がこれにまたはこれによって限定されるべきではない。本開示の他の実施例により、共通電圧が第1、第2および第3エピタキシャルスタック220、230および240のn型半導体層に印加され、発光信号は、第1、第2および第3エピタキシャルスタック220、230および240のp型半導体層に印加されてもよい。この構造は、p型半導体層、活性層およびn型半導体層の順に各エピタキシャルスタックを形成することにより容易に実現可能であり、この順序は、上述した実施例でn型半導体層、活性層およびp型半導体層の順に形成される各エピタキシャルスタックの積層順序とは異なる。上述した実施例により、第1、第2および第3エピタキシャルスタック220、230および240は、それに印加される発光信号に応答して駆動される。すなわち、第1エピタキシャルスタック220は、第1発光信号SRに応答して駆動され、第2エピタキシャルスタック230は、第2発光信号SGに応答して駆動され、第3エピタキシャルスタック240は、第3発光信号SBに応答して駆動される。この場合、第1、第2および第3発光信号SR、SGおよびSBは、第1、第2および第3エピタキシャルスタック220、230および220に独立して印加され、結果として、第1、第2および第3エピタキシャルスタック220、230および240は、独立して駆動される。発光積層構造は、第1、第2および第3エピタキシャルスタックから上方向に放出される第1、第2および第3色光の組み合わせによって多様な色相の光を提供することができる。

色相をディスプレイするときには、上述した構造を有する発光積層構造は、平面上の互いに異なる区域を介して互いに異なる色光を提供するよりは、互いに重なる区域を介して互いに異なる色光を提供し、そのため、発光素子が小型化され、集積化されることが可能である。従来技術によれば、互いに異なる色光、例えば、赤色、緑色および青色光を放出する発光素子は、フルカラーディスプレイを実現するために、平面上で互いに離隔して配置される。したがって、発光素子が平面上で互いに離隔して配置されるので、従来技術において発光素子によって占有される面積は相対的に大きい。一方、本開示によれば、互いに異なる色光を放出する発光素子が互いに重なるように同一の面積内に配置されて発光積層構造を形成し、そのため、従来技術より著しく小さな面積によりフルカラーディスプレイが実現できる。そのため、高解像度ディスプレイデバイスが小さい面積内に製造できる。

また、積層方式で製造される従来の発光デバイスの場合にも、従来の発光デバイスは、各発光素子内にコンタクト部を個別に形成することにより、例えば、発光素子を個別に、そして分離的に形成し、ワイヤリングを用いて発光素子を互いに接続することにより製造される。結果として、発光デバイスの構造は複雑で、発光デバイスを製造することが容易でない。しかし、本開示の例示的な実施例による発光積層構造は、1つの基板上に複数のエピタキシャルスタックを順に積層し、最小工程によりエピタキシャルスタック内にコンタクト部を形成し、ライン部をエピタキシャルスタックに接続することにより製造される。加えて、本開示の例示的な実施例によれば、従来の発光素子の代わりに1つの発光積層構造が実装されるので、個別の色相の発光素子を分離的に製造し、発光素子を個別に実装する従来のディスプレイデバイスの製造方法に比べて、ディスプレイデバイスの製造方法が単純化できる。

本開示の例示的な実施例による発光積層構造は、色光を高純度および高効率で提供するための多様な構成要素を追加的に含んでもよい。例えば、本開示の例示的な実施例による発光積層構造は、相対的に短い波長を有する光が相対的に長い波長を有する光を放出するエピタキシャルスタックに進行するのを防止するための波長通過フィルタを含むことができる。

以下の実施例では、重複を避けるために、上述した実施例の特徴とは異なる特徴が主に説明される。説明されていない部分は、上述した実施例のそれと同一または類似するものと仮定する。

図18は、本開示の例示的な実施例による所定の波長通過フィルタを有する発光積層構造を示す断面図である。

図18を参照すると、本開示の例示的な実施例による発光積層構造は、第1エピタキシャルスタック220と第2エピタキシャルスタック230との間に配置される第1波長通過フィルタ261を含むことができる。

第1波長通過フィルタ261は、所定の波長を有する光を選択的に透過させる。第1波長通過フィルタ261は、第1エピタキシャルスタック220から放出される第1色光を透過させることができ、第1色光を除いた光を遮断または反射させることができる。したがって、第1エピタキシャルスタック220から放出される第1色光は、上方向に進行することができ、第2および第3エピタキシャルスタック230および240からそれぞれ放出される第2および第3色光は、第1波長通過フィルタ261によって第1エピタキシャルスタック220に向かって進行しなくてもよいし、反射または遮断可能である。

第2および第3色光は、第1色光より相対的に短い波長および相対的に高いエネルギーを有する。第2および第3色光が第1エピタキシャルスタック220内に入射する場合、第1エピタキシャルスタック220内で付加的な発光が誘導されることがある。本例示的な実施例において、第2および第3色光は、第1波長通過フィルタ261によって第1エピタキシャルスタック220内に入射することが防止できる。

本開示の例示的な実施例において、第2波長通過フィルタ263が第2エピタキシャルスタック230と第3エピタキシャルスタック240との間に配置される。第2波長通過フィルタ263は、第1および第2エピタキシャルスタック220および230からそれぞれ放出される第1および第2色光を透過させることができ、第1および第2色光を除いた光を遮断または反射させることができる。したがって、第1および第2エピタキシャルスタック220および230からそれぞれ放出される第1および第2色光は、上方向に進行することができ、第3エピタキシャルスタック240から放出される第3色光は、第2波長通過フィルタ263によって第1および第2エピタキシャルスタック220および230に向かって進行しなくてもよいし、反射または遮断可能である。

上記の説明と類似して、第3色光は、第1および第2色光より相対的に短い波長および相対的に高いエネルギーを有する。第3色光が第1および第2エピタキシャルスタック220および230内に入射する場合、付加的な発光が第1および第2エピタキシャルスタック220および230内で誘導されることがある。本例示的な実施例において、第3色光は、第2波長通過フィルタ263によって第1および第2エピタキシャルスタック220および230内に入射することが防止できる。

本開示の例示的な実施例による発光積層構造は、高効率の均一な光を提供するために多様な構成要素を追加的に含んでもよい。一例として、本開示の例示的な実施例による発光積層構造は、発光面上で多様な凹凸部分を含むことができる。

図19および図20は、本開示の例示的な実施例によるエピタキシャルスタックの少なくとも一部分で凹凸部分が形成される発光積層構造を示す断面図である。

本開示の例示的な実施例による発光積層構造は、第1、第2および第3エピタキシャルスタック220、230および240のn型半導体層221、231および241のうちの少なくとも1つのn型半導体層の上部表面上に形成される凹凸部分PRを含むことができる。本開示の例示的な実施例において、各エピタキシャルスタックの凹凸部分PRは、選択的に形成可能である。例えば、凹凸部分PRは、図19に示すように、第1および第3エピタキシャルスタック220および240上に配置され、凹凸部分PRは、図20に示すように、第1、第2および第3エピタキシャルスタック220、230および240上に配置される。各エピタキシャルスタックの凹凸部分PRは、第1、第2および第3エピタキシャルスタック220、230および240の発光面にそれぞれ対応するn型半導体層221、231および241上に配置される。

凹凸部分PRは、発光効率を向上させるために用いられる。凹凸部分PRは、その上に凹凸部分がランダムに配列される、多角形ピラミッド、半球または粗さを有する表面のような、多様な形状に提供できる。凹凸部分PRは、多様なエッチング工程によりテクスチャリングされるか、またはパターニングされたサファイア基板を用いて形成されてもよい。

本開示の例示的な実施例において、第1、第2および第3エピタキシャルスタック220、230および240からの第1、第2および第3色光は、光度において差を有することができ、光度差は可視性において差を誘発することがある。本例示的な実施例において、発光効率は、第1、第2および第3エピタキシャルスタック220、230および240の発光面上に選択的に形成される凹凸部分PRによって向上することができ、そのため、第1、第2および第3色光間の光度差は減少できる。赤色および/または青色に対応する色光は、緑色に対応する色光より低い可視性を有するので、可視性における差は、第1エピタキシャルスタック220および/または第3エピタキシャルスタック240をテクスチャリングすることにより減少できる。特に、赤色光は、発光積層構造の最下部分から提供されるので、相対的により小さい光度を有する。この場合、凹凸部分PRが第1エピタキシャルスタック220上に形成される場合、光効率が向上することができる。

上述した構造を有する発光積層構造は、多様な色相をディスプレイ可能な発光素子に対応し、ピクセルとしてディスプレイデバイスで使用できる。以下の説明では、上述した構造を有する発光積層構造をその構成要素として用いるディスプレイデバイスが説明される。

図21は、本開示の例示的な実施例によるディスプレイデバイス2100を示す平面図であり、図22は、図21の部分P1を示す拡大平面図である。

図21および図22を参照すると、本開示の例示的な実施例によるディスプレイデバイス2100は、テキスト、ビデオ、写真および二次元または三次元イメージのような任意の視覚情報をディスプレイする。

ディスプレイデバイス2100は、長方形状のような直線面を有する閉多角形、曲面を有する円形または楕円形および直線面と曲面を有する半円形または半楕円形のような、多様な形状を有することができる。本開示の例示的な実施例では、長方形状を有するディスプレイデバイスが示される。

ディスプレイデバイス2100は、イメージをディスプレイする複数のピクセル2110を含む。各ピクセル2110は、イメージをディスプレイする最小単位である。各ピクセル2110は、上述した構造を有する発光積層構造を含むことができ、白色光および/または色光を放出することができる。

本開示の例示的な実施例において、各ピクセル2110は、赤色光を放出する第1サブピクセル2110Rと、緑色光を放出する第2サブピクセル2110Gと、青色光を放出する第3サブピクセル2110Bとを含む。第1、第2および第3サブピクセル2110R、2110Gおよび2110Bは、上述した発光積層構造の第1、第2および第3エピタキシャルスタック220、230および240にそれぞれ対応することができる。

ピクセル2110は、マトリクス状に配列される。ピクセル2110がマトリクス状に配列されるという表現は、ピクセル2110が行または列に沿って正確に一列に配列されるだけでなく、ピクセル2110の細部位置が、例えば、ジグザグ状に変化しながら、ピクセル2110が全体的に行または列に沿って配列されることを示すことができる。

図23は、本開示の例示的な実施例によるディスプレイデバイスを示すブロック図である。

図23を参照すると、本開示の例示的な実施例によるディスプレイデバイス2100は、タイミングコントローラ2350と、スキャンドライバ2310と、データドライバ2330と、ライン部と、ピクセルとを含む。各ピクセルが複数のサブピクセルを含む場合、各サブピクセルは、ライン部を介してスキャンドライバ2310およびデータドライバ2330に個別に接続される。

タイミングコントローラ2350は、外部ソース(例えば、イメージデータを伝送するシステム)から、ディスプレイデバイス2100を駆動するために必要な多様な制御信号およびイメージデータを受信する。タイミングコントローラ2350は、受信されたイメージデータを再配列し、再配列されたイメージデータをデータドライバ2330に印加する。また、タイミングコントローラ2350は、スキャンドライバ2310およびデータドライバ2330を駆動するために必要なスキャン制御信号およびデータ制御信号を生成し、生成されたスキャン制御信号およびデータ制御信号をスキャンドライバ2310およびデータドライバ2330にそれぞれ印加する。

スキャンドライバ2310は、タイミングコントローラ2350からスキャン制御信号を受信し、スキャン制御信号に応答してスキャン信号を生成する。

データドライバ2330は、タイミングコントローラ2350からデータ制御信号およびイメージデータを受信し、データ制御信号に応答してデータ信号を生成する。

ライン部は、複数の信号ラインを含む。具体的には、ライン部は、スキャンドライバ2310とサブピクセルとを接続するスキャンライン2130と、データドライバ2330とサブピクセルとを接続するデータライン2120とを含む。スキャンライン2130は、サブピクセルにそれぞれ接続され、サブピクセルにそれぞれ接続されるスキャンラインは、第1、第2および第3サブスキャンライン2130R、2130Gおよび2130Bとして示される。

加えて、ライン部は、信号を伝送するために、タイミングコントローラ2350とスキャンドライバ2310、タイミングコントローラ2350とデータドライバ2330、またはその他の構成要素を互いに接続する、ラインをさらに含んでもよい。

スキャンライン2130は、スキャンドライバ2310によって生成されるスキャン信号をサブピクセルに印加する。データドライバ2330によって生成されるデータ信号は、データライン2120に印加される。

サブピクセルは、スキャンライン2130およびデータライン2120に接続される。サブピクセルは、スキャンライン2130からのスキャン信号がそれに印加されるとき、データライン2120から提供されるデータ信号に応答して選択的に発光する。一例として、各サブピクセルは、各フレーム期間にそれに印加されるデータ信号に対応する明るさで光を放出する。ブラックの明るさに相当するデータ信号が印加されるサブピクセルは、当該フレーム期間に光を放出せず、そのため、黒色がディスプレイされる。

本開示の例示的な実施例において、サブピクセルは、パッシブまたはアクティブマトリクス方式で駆動可能である。ディスプレイデバイスがアクティブマトリクス方式で駆動される場合、ディスプレイデバイス2100は、スキャン信号およびデータ信号に加えて、第1および第2ピクセル電源を追加的に受信することにより駆動できる。

図24は、パッシブマトリクスタイプのディスプレイデバイス用の1つのサブピクセルを示す回路図である。この場合、サブピクセルは、サブピクセル、例えば、レッドサブピクセル、グリーンサブピクセルおよびブルーサブピクセルのうちの1つであってもよいし、第1サブピクセル2110Rが本例示的な実施例で示される。

図24を参照すると、第1サブピクセル2110Rは、スキャンライン2130とデータライン2120との間に接続される発光素子2150を含む。発光素子2150は、第1エピタキシャルスタック220に相当する。閾値電圧以上の電圧がp型半導体層とn型半導体層との間に印加されるとき、第1エピタキシャルスタック220は、それに印加される電圧のレベルに対応する明るさで光を放出する。すなわち、第1サブピクセル2110Rの発光は、スキャンライン2130に印加されるスキャン信号の電圧および/またはデータライン2120に印加されるデータ信号の電圧を制御することにより制御可能である。

図25は、アクティブマトリクスタイプのディスプレイデバイス用の第1サブピクセル2110Rを示す回路図である。ディスプレイデバイスがアクティブマトリクスタイプのディスプレイデバイスの場合、第1サブピクセル2110Rは、スキャン信号およびデータ信号に加えて、第1および第2ピクセル電源ELVDDおよびELVSSをさらに受信することにより駆動できる。

図25を参照すると、第1サブピクセル2110Rは、1つ以上の発光素子2150と、発光素子2150に接続されるトランジスタ部とを含む。

発光素子2150は、第1エピタキシャルスタック220に相当することができ、発光素子2150のp型半導体層は、トランジスタ部を経由して第1ピクセル電源ELVDDに接続され、発光素子2150のn型半導体層は、第2ピクセル電源ELVSSに接続される。第1ピクセル電源ELVDDおよび第2ピクセル電源ELVSSは、互いに異なる電位を有することができる。例えば、第2ピクセル電源ELVSSは、発光素子2150の閾値電圧以上だけ第1ピクセル電源ELVDDの電位より低い電位を有することができる。発光素子2150のそれぞれは、トランジスタ部によって制御される駆動電流に対応する明るさで光を放出する。

本開示の例示的な実施例により、トランジスタ部は、第1および第2トランジスタM1およびM2およびストレージキャパシタCstを含む。しかし、トランジスタ部の構成は、図25に示す実施例に限定されるべきではない。

第1トランジスタ(スイッチングトランジスタ)M1は、データライン2120に接続されるソース電極と、第1ノードN1に接続されるドレイン電極と、スキャンライン2130に接続されるゲート電極とを含む。第1トランジスタM1は、第1トランジスタM1をターンオンさせるのに十分な電圧を有するスキャン信号がスキャンライン2130を介して提供されるとき、ターンオンされてデータライン2120および第1ノードN1を電気的に接続する。この場合、当該フレームのデータ信号は、データライン2120に印加され、そのため、データ信号は、第1ノードN1に印加される。ストレージキャパシタCstは、第1ノードN1に印加されるデータ信号で充電される。

第2トランジスタ(駆動トランジスタ)M2は、第1ピクセル電源ELVDDに接続されるソース電極と、発光素子2150のn型半導体層に接続されるドレイン電極と、第1ノードN1に接続されるゲート電極とを含む。第2トランジスタM2は、第1ノードN1の電圧に応答して発光素子2150に供給される駆動電流の量を制御する。

ストレージキャパシタCstの1つの電極は、第1ピクセル電源ELVDDに接続され、ストレージキャパシタCstの他の1つの電極は、第1ノードN1に接続される。ストレージキャパシタCstは、第1ノードN1に印加されるデータ信号に対応する電圧に充電され、次のフレームのデータ信号が提供されるまで充電された電圧を保持する。

説明の便宜のために、図25は、2つのトランジスタを含むトランジスタ部を示す。しかし、トランジスタ部に含まれるトランジスタの個数は2つに限定されるべきではなく、トランジスタ部の構成は、多様な方式で変化可能である。例えば、トランジスタ部は、より多いトランジスタおよびより多いキャパシタを含むことができる。加えて、本例示的な実施例において、第1および第2トランジスタ、ストレージキャパシタおよびラインの構成は詳細に示されていないが、第1および第2トランジスタ、ストレージキャパシタおよびラインは、本開示の例示的な実施例による回路を実現する範囲内で多様な方式で変化可能である。

上述したピクセルは、本開示の範囲内で多様な方式で変化可能であり、以下の構造で実現できる。

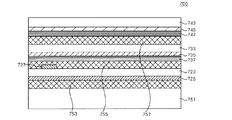

図26は、本開示の例示的な実施例によるピクセルを示す平面図であり、図27Aおよび図27Bは、それぞれ図26のI−I’およびII−II’線に沿った断面図である。

図26、図27Aおよび図27Bを参照すると、本開示の例示的な実施例によるピクセルは、発光区域EAと、周辺区域PAとを含む。エピタキシャルスタックは、発光区域EA内で積層される。本例示的な実施例において、エピタキシャルスタックは、第1、第2および第3エピタキシャルスタック220、230および240を含む。

第1、第2および第3エピタキシャルスタック220、230および240は、第1、第2および第3サブスキャンライン2130R、2130Gおよび2130Bおよびデータライン2120に接続される。本開示の例示的な実施例において、第1、第2および第3サブスキャンライン2130R、2130Gおよび2130Bは、第1方向、例えば、図26の水平方向に延びてもよい。データライン2120は、第1コンタクトホールCH1を介して第1p型コンタクト電極227に接続され、第1p型コンタクト電極227は、実質的にデータライン2120として作用する。したがって、以下、第1p型コンタクト電極227は、データライン2120と称されてもよい。データライン2120は、第2方向、例えば、第1、第2および第3サブスキャンライン2130R、2130Gおよび2130Bを横切る図26の垂直方向に延びてもよい。しかし、第1、第2および第3サブスキャンライン2130R、2130Gおよび2130Bおよびデータライン2120の延びる方向はこれにまたはこれによって限定されるべきではなく、ピクセルの配列によって多様な方式で変化可能である。

第1サブスキャンライン2130Rおよびデータライン、具体的には、第1p型コンタクト電極227は、第1エピタキシャルスタック220に接続される。データライン2120および第2サブスキャンライン2130Gは、それぞれ第1および第2コンタクトホールCH1およびCH2を介して第2エピタキシャルスタック230に接続される。データライン2120および第3サブスキャンライン2130Bは、それぞれ第1および第2コンタクトホールCH1およびCH2を介して第3エピタキシャルスタック240に接続される。本例示的な実施例において、第1および第2コンタクトホールCH1およびCH2は、周辺区域PA内に形成される。

接着層、コンタクト電極および波長通過フィルタが基板210と第1エピタキシャルスタック220との間、第1エピタキシャルスタック220と第2エピタキシャルスタック230との間、および第2エピタキシャルスタック230と第3エピタキシャルスタック240との間に配置される。以下、本開示の例示的な実施例によるピクセルを積層順序に従って説明する。

本例示的な実施例により、メサ構造を有する第1エピタキシャルスタック220が、第1接着層250aが間に介在する状態で、基板210上に配置される。

第1絶縁層271が第1エピタキシャルスタック220の下部表面、すなわち、基板210と向かい合う表面上に配置される。第1絶縁層271にはそれを介して設けられる複数のコンタクトホールが提供される。第1エピタキシャルスタック220のn型半導体層と接触する第1n型コンタクト電極229は、周辺区域PAに対応するコンタクトホール内に配置され、第1エピタキシャルスタック220のp型半導体層と接触する第1p型コンタクト電極227は、発光区域EAに対応するコンタクトホール内に配置される。第1および第2オーミック電極229’および227’は、第1p型コンタクト電極227および第1n型コンタクト電極229とのオーミック接触のために、第1n型コンタクト電極229および第1p型コンタクト電極227が形成される区域上に配置される。オーミック接触のための第1および第2オーミック電極229’および227’は、多様な材料を含むことができる。本開示の例示的な実施例において、p型オーミック電極に対応する第2オーミック電極227’は、Au(Zn)またはAu(Be)を含むことができる。この場合、第2オーミック電極227’用材料がAg、AlおよびAuより低い反射率を有するので、追加の反射電極がさらに配置されてもよい。追加の反射電極用材料として、AgまたはAuが使用可能であり、Ti、Ni、CrまたはTaを含む層が隣接した構成要素への接着のための接着層として配置されてもよい。この場合、接着層は、AgまたはAuを含む反射電極の上部および下部表面上に薄く蒸着される。

第1p型コンタクト電極227は、発光区域EAと重なり、平面図からみて、発光区域EAの全体を覆うように提供される。第1p型コンタクト電極227は、反射性を有する材料を含み、第1エピタキシャルスタック220内で光を反射させることができる。この場合、第1絶縁層271は、第1エピタキシャルスタック220内で光の反射が容易に行われるように、反射性を有するように形成される。例えば、第1絶縁層271は、全方向反射器(omni−directional reflector:ODR)構造を有してもよい。

第2絶縁層273が第1p型コンタクト電極227および基板210の間に配置される。第2絶縁層273は、第1p型コンタクト電極227が上に形成される第1エピタキシャルスタック220の下部表面を覆い、第1n型コンタクト電極229が露出した状態で貫通するコンタクトホールを有する。第1サブスキャンライン2130Rは、第2絶縁層273と基板210との間に配置され、データ信号を第1n型コンタクト電極229に印加する。

第2接着層250bが第1エピタキシャルスタック220上に配置され、第1波長通過フィルタ261、第2p型コンタクト電極237および第2エピタキシャルスタック230が第2接着層250b上に順に配置される。別途に示さないが、第2エピタキシャルスタック230は、第2エピタキシャルスタック230の底から上方向に順に積層される、p型半導体層、活性層およびn型半導体層を含む。

本例示的な実施例において、第1波長通過フィルタ261および第2p型コンタクト電極237は、第1エピタキシャルスタック220と実質的に同一の面積を有することができ、第2エピタキシャルスタック230は、第1エピタキシャルスタック220より小さい面積を有することができる。第2エピタキシャルスタック230が第1エピタキシャルスタック220より小さい面積を有するので、第2p型コンタクト電極237の一部分が露出してもよい。

第3接着層250cが第2エピタキシャルスタック230上に配置され、第2波長通過フィルタ263、第3p型コンタクト電極247および第3エピタキシャルスタック240が第3接着層250c上に順に配置される。別途に示さないが、第3エピタキシャルスタック240は、第3エピタキシャルスタック240の底から上方向に順に積層される、p型半導体層、活性層およびn型半導体層を含む。

第3エピタキシャルスタック240は、第2エピタキシャルスタック230より小さい面積を有することができる。第3エピタキシャルスタック240は、第3p型コンタクト電極247より小さい面積を有することができ、そのため、第3p型コンタクト電極247の上部表面の一部分が露出してもよい。加えて、第3p型コンタクト電極247が第2エピタキシャルスタック230より小さい面積を有することができ、そのため、第2エピタキシャルスタック230の上部表面の一部分が露出してもよい。

第3絶縁層275が第3エピタキシャルスタック240上に配置されて第1、第2および第3エピタキシャルスタック220、230および240の積層構造を覆う。第3絶縁層275は、多様な有機/無機絶縁材料を含むことができるが、これにまたはこれによって限定されるべきではない。例えば、第3絶縁層275は、シリコン窒化物およびシリコン酸化物を含む無機絶縁材料またはポリイミドのような有機絶縁材料を含むことができる。

第3絶縁層275は、第1、第2および第3p型コンタクト電極227、237および247の上部表面が露出した状態で貫通する第1コンタクトホールCH1と、第2および第3エピタキシャルスタック230および240のn型半導体層の上部表面が露出した状態で貫通する第2コンタクトホールCH2とを含む。

データライン2120および第1、第2および第3サブスキャンライン2130R、2130Gおよび2130Bが第3絶縁層275上に配置される。データライン2120は、第3絶縁層275を介して形成される第1コンタクトホールCH1を介して第1、第2および第3p型コンタクト電極227、237および247に同時に接続される。第2および第3サブスキャンライン2130Gおよび2130Bのそれぞれは、第2コンタクトホールCH2を介して第2エピタキシャルスタック230のn型半導体層および第3エピタキシャルスタック240のn型半導体層にそれぞれ接続される。

本開示の例示的な実施例において、第2サブスキャンライン2130Gは、第2エピタキシャルスタック230のn型半導体層と直接接触して電気的に接続され、第3サブスキャンライン2130Bは、第3エピタキシャルスタック240のn型半導体層と直接接触して電気的に接続される。しかし、他の実施例により、第2n型コンタクト電極が第2サブスキャンライン2130Gと第2エピタキシャルスタック230のn型半導体層との間にさらに配置されてもよく、第2サブスキャンライン2130Gおよび第2エピタキシャルスタック230のn型半導体層は、第2n型コンタクト電極によって互いに電気的に接続されてもよい。また、第3n型コンタクト電極が第3サブスキャンライン2130Bと第3エピタキシャルスタック240のn型半導体層との間にさらに配置されてもよく、第3サブスキャンライン2130Bおよび第3エピタキシャルスタック240のn型半導体層は、第3n型コンタクト電極によって互いに電気的に接続されてもよい。

第4絶縁層277がデータライン2120および第1、第2および第3サブスキャンライン2130R、2130Gおよび2130B上に配置されてデータライン2120および第1、第2および第3サブスキャンライン2130R、2130Gおよび2130Bを覆う。また、第4絶縁層277は、多様な有機/無機絶縁材料を含むことができるが、これにまたはこれによって限定されるべきではない。

本例示的な実施例で別途に示さないが、凹凸部分が第1、第2および第3エピタキシャルスタック220、230および240の上部表面、すなわち、第1、第2および第3エピタキシャルスタック220、230および240のそれぞれのn型半導体層の上部表面上に選択的に配置されてもよい。各凹凸部分は、発光区域EAに対応する面積内にのみ配置されるか、または各n型半導体層の全体上部表面上に配置されてもよい。したがって、第2および第3サブスキャンライン2130Gおよび2130Bは、凹凸部分PRがその上に配置されていないn型半導体層と接触して電気的に接続されるか、または凹凸部分PRがその上に配置されるn型半導体層と接触して電気的に接続されてもよい。

また、詳細に示さないが、本開示の例示的な実施例において、光不透過性層がピクセルの側面に対応する第4絶縁層277上にさらに配置されてもよい。光不透過性層は、光遮断層として作用して、第1、第2および第3エピタキシャルスタック220、230および240からの光がピクセルの側面に出射するのを防止することができ、光を吸収または反射させる材料を含むことができる。

光不透過性層は、光不透過性層が光を吸収または反射させて光の透過を遮断する限り、特に限定されるべきではない。本開示の例示的な実施例において、光不透過性層は、分布ブラッグ反射器(DBR)誘電体ミラー、絶縁層上に形成される金属反射層または黒色有機ポリマー層であってもよい。金属反射層が光不透過性層として用いられる場合、金属反射層は、金属反射層が他のピクセルの構成要素から電気的に絶縁される、フローティング状態であってもよい。

ピクセルの側面に配置される光不透過性層によって、特定のピクセルから出射する光が隣接したピクセルに影響を及ぼすか、隣接したピクセルから出射する光と混合されるのを防止することができる。

上記の構造を有するピクセルは、基板上に第1、第2および第3エピタキシャルスタックを順に積層することにより製造可能であり、以下、図28および図29A〜図29Lを参照して詳細に説明する。

図28は、第1〜第3エピタキシャルスタックがその上に積層される基板を示す平面図であり、図29A〜図29Lは、図28のI−I’線に沿った、基板上に第1〜第3エピタキシャルスタックを積層する工程を順に示す断面図である。

図28および図29Aを参照すると、第1エピタキシャルスタック220が第1初期基板210p上に形成される。本開示の例示的な実施例において、第1初期基板210pは、第1エピタキシャルスタック220を形成するために必要な半導体、例えば、ガリウム砒化物(GaAs)からなってもよい。第1エピタキシャルスタック220は、第1初期基板210p上にn型半導体層、活性層およびp型半導体層を形成し、n型半導体層、活性層およびp型半導体層の一部分を除去してメサ構造を形成することにより製造される。

図28および図29Bを参照すると、第1絶縁層271が第1初期基板210p上に形成され、コンタクトホールが第1絶縁層271を介して形成されて、p型半導体層およびn型半導体層を部分的に露出させる。p型半導体層の上部に設けられるコンタクトホールは、複数提供されてもよい。オーミック電極227’および229’は、コンタクトホールを介して露出するp型半導体層およびn型半導体層上にそれぞれ形成される。

図28および図29Cを参照すると、第1n型コンタクト電極229および第1p型コンタクト電極227は、オーミック電極227’および229’がその上に形成される、第1初期基板210p上に形成される。第1n型コンタクト電極229は、n型半導体層上に形成され、第1p型コンタクト電極227は、p型半導体層上に形成される。第1n型コンタクト電極229および第1p型コンタクト電極227は、反射材料で形成される。

図28および図29Dを参照すると、第2絶縁層273は、第1n型コンタクト電極229および第1p型コンタクト電極227がその上に形成される、第1初期基板210p上に形成され、第1サブスキャンライン2130Rが第2絶縁層273上に形成される。コンタクトホールが第1n型コンタクト電極229に対応する位置で第2絶縁層273を介して形成され、第1サブスキャンライン2130Rは、第1n型コンタクト電極229に対応する位置に形成されるコンタクトホールを介して第1n型コンタクト電極229に接続される。

図28および図29Eを参照すると、第1初期基板210p上に形成された第1エピタキシャルスタック220が反転して、第1接着層250aが間に介在する状態で、基板210に貼り合わされる。

図28および図29Fを参照すると、第1初期基板210pは、第1エピタキシャルスタック220が基板210に貼り合わされた後に、除去される。第1初期基板210pは、ウェットエッチング工程、ドライエッチング工程、物理的除去工程またはレーザリフトオフ工程のような多様な方法によって除去可能である。図示しないが、第1初期基板210pが除去された後、凹凸部分PRが第1エピタキシャルスタック220の上部表面(n型半導体層)上に形成される。凹凸部分PRは、多様なエッチング工程によりテクスチャリングされる。例えば、凹凸部分PRは、マイクロフォトグラフィーを利用したドライエッチング工程、結晶特性を利用したウェットエッチング工程、サンドブラストのような物理的方法を利用したテクスチャリング工程、イオンビームエッチング工程またはブロックコポリマーのエッチング速度差を利用したテクスチャリング工程のような多様な工程により形成されてもよい。

図28および図29Gを参照すると、第2エピタキシャルスタック230が第2初期基板210q上に形成される。第2初期基板210qは、サファイア基板であってもよい。第2初期基板210q上にn型半導体層、活性層およびp型半導体層を形成することにより、第2エピタキシャルスタック230が製造される。第2p型コンタクト電極237および第1波長通過フィルタ261が第2エピタキシャルスタック230上にさらに形成されてもよい。

図28および図29Hを参照すると、第2初期基板210q上に形成された第2エピタキシャルスタック230は反転して、第2接着層250bが間に介在する状態で、第1エピタキシャルスタック220に貼り合わされる。

図28および図29Iを参照すると、第2エピタキシャルスタック230が第1エピタキシャルスタック220に貼り合わされた後、第2初期基板210qは除去される。

図示しないが、第2初期基板210qが除去された後、凹凸部分PRが第2エピタキシャルスタック230の上部表面(n型半導体層)上に形成される。凹凸部分PRは、多様なエッチング工程によりテクスチャリングされるか、またはパターニングされたサファイア基板を第2初期基板210qとして用いて形成されてもよい。第2初期基板210qは、多様な方法で除去可能である。例えば、第2初期基板210qがサファイア基板の場合、サファイア基板は、レーザリフトオフ工程、ストレスリフトオフ工程、化学的リフトオフ工程または物理的研磨工程によって除去可能である。

図28および図29Jを参照すると、第3エピタキシャルスタック240が第3初期基板210r上に形成される。第3初期基板210rは、サファイア基板であってもよい。第3初期基板210r上にn型半導体層、活性層およびp型半導体層を形成することにより、第3エピタキシャルスタック240が製造される。第3p型コンタクト電極247および第2波長通過フィルタ263が第3エピタキシャルスタック240上にさらに形成されてもよい。

図28および図29Kを参照すると、第3初期基板210r上に形成された第3エピタキシャルスタック240は反転して、第3接着層250cが間に介在する状態で、第2エピタキシャルスタック230に貼り合わされる。

図28および図29Lを参照すると、第3初期基板210rは、第3エピタキシャルスタック240が第2エピタキシャルスタック230に貼り合わされた後に除去され、そのため、すべての第1、第2および第3エピタキシャルスタック220、230および240が基板210上に積層される。図示しないが、第3初期基板210rが除去された後、凹凸部分PRが第3エピタキシャルスタック240の上部表面(n型半導体層)上に形成される。凹凸部分PRは、多様なエッチング工程によりテクスチャリングされるか、またはパターニングされたサファイア基板を第3初期基板210rとして用いて形成されてもよい。

上述した工程により、第1エピタキシャルスタック220が第1サブスキャンライン2130Rおよびデータライン、すなわち、第1p型コンタクト電極227に接続されるが、第2および第3エピタキシャルスタック230および240は、第2および第3サブスキャンライン2130Gおよび2130Bおよびデータライン2120に接続されない。したがって、第2および第3エピタキシャルスタック230および240を第2および第3サブスキャンライン2130Gおよび2130Bおよびデータライン2120に接続するための工程が行われる。

図30A〜図35Aは、第2および第3エピタキシャルスタック230および240を第2および第3サブスキャンライン2130Gおよび2130Bおよびデータライン2120に接続するための工程を順に示す平面図であり、図30B〜図35Bは、それぞれ図30A〜図35AのI−I’、IIa−IIa’およびIIb−IIb’線に沿った断面図である。

図30Aおよび図30Bを参照すると、第3p型コンタクト電極247の上部表面の一部分が外部に露出するように、第3エピタキシャルスタック240の一部分が除去される。第3p型コンタクト電極247は、第3エピタキシャルスタック240がエッチングされるときに、エッチングストッパとして機能する。

図31Aおよび図31Bを参照すると、第3p型コンタクト電極247、第2波長通過フィルタ263および第3接着層250cの一部分がエッチングされる。したがって、第2エピタキシャルスタック230の上部表面の一部分が外部に露出する。この場合、第3p型コンタクト電極247およびデータライン2120が接続されるコンタクト区域はエッチングされない。

図32Aおよび図32Bを参照すると、第2エピタキシャルスタック230の一部分が除去されて、第2p型コンタクト電極237の上部表面の一部分を露出させる。第2p型コンタクト電極237は、第2エピタキシャルスタック230がエッチングされるときに、エッチングストッパとして機能する。

図33Aおよび図33Bを参照すると、第2p型コンタクト電極237、第1波長通過フィルタ261、第2接着層250b、第1エピタキシャルスタック220および第1絶縁層271の一部分がエッチングされる。そのため、第2絶縁層273および第1p型コンタクト電極227の一部分が外部に露出する。この場合、第2p型コンタクト電極237およびデータライン2120が接続されるコンタクト区域はエッチングされない。

図34Aおよび図34Bを参照すると、第1および第2コンタクトホールCH1およびCH2がそれを貫通して形成される第3絶縁層275が基板210上に形成される。データライン2120が接続される部分、すなわち、第1、第2および第3p型コンタクト電極227、237および247の上部表面の部分が第1コンタクトホールCH1を介して露出する。第2および第3サブスキャンライン2130Gおよび2130Bが接続される一部分、すなわち、第2および第3エピタキシャルスタック230および240のn型半導体層の上部表面の一部分が第2コンタクトホールCH2を介して露出する。

図35Aおよび図35Bを参照すると、第2および第3サブスキャンライン2130Gおよび2130Bおよびデータライン2120は、第1および第2コンタクトホールCH1およびCH2がその上に形成される、基板210上に形成される。第2および第3サブスキャンライン2130Gおよび2130Bおよびデータライン2120は、基板210上に金属層を形成し、金属層をパターニングすることにより形成される。第2および第3サブスキャンライン2130Gおよび2130Bは、第2コンタクトホールCH2を介して第2および第3n型半導体層にそれぞれ接続され、データライン2120は、第1コンタクトホールCH1を介して第1、第2および第3p型コンタクト電極227、237および247に接続される。

第4絶縁層277は、第2および第3サブスキャンライン2130Gおよび2130Bおよびデータライン2120がその上に形成される、基板210上に形成される。

本開示の例示的な実施例において、たとえ図示していなくても、光不透過性層がピクセルの側面に対応する第3絶縁層275または第4絶縁層277上にさらに配置されてもよい。光不透過性層は、DBR誘電体ミラーによって、絶縁層上に形成される金属反射層によって、または有機ポリマーによって形成される。金属反射層が光不透過性層として用いられる場合に、金属反射層は、金属反射層が他のピクセルの構成要素から電気的に絶縁される、フローティング状態にあってもよい。

上述のように、本開示の例示的な実施例によるディスプレイデバイスは、複数のエピタキシャルスタックを順に積層し、エピタキシャルスタック内にライン部とコンタクト構造を実質的に同時に形成することにより製造できる。

本開示の実施例は、光を放出する発光積層構造に関する。本開示の発光積層構造は、多様なデバイスにおける光源として利用可能である。

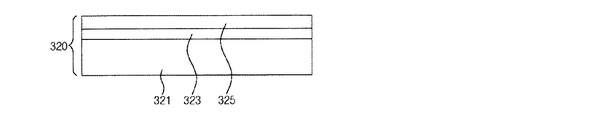

図36A〜図36Cは、本開示の例示的な実施例による発光積層構造を示す断面図である。

図36A〜図36Cを参照すると、本開示の例示的な実施例による発光積層構造は、順に積層される2つのエピタキシャルスタック、すなわち、第1エピタキシャルスタック320および第2エピタキシャルスタック330を含む。第1および第2エピタキシャルスタック320および330は、基板310上に配置される。

基板310は、前面および後面が提供されるプレート形状を有する。

基板310は、光透過性絶縁材料で形成される。「基板310は光透過特性を有する」という表現は、基板310が光を実質的に全体的に透過させるように透明な場合、基板310が特定の波長を有する光のみを透過させるように半透明の場合、または基板310が特定の波長を有する光の一部分のみを透過させるように部分的に透明な場合のような、多様な場合を示す。

基板310の材料として、基板310の前上に配置されるエピタキシャルスタック、すなわち、第1エピタキシャルスタック320がその上に成長する、成長基板のうちの1つが使用できる。この場合、基板310は、サファイア基板であってもよいが、基板310がこれにまたはこれによって限定されるべきではない。すなわち、材料が透明で絶縁特性を有し、エピタキシャルスタックが基板310の上部表面上に配置される限り、サファイア基板のほかに、多様な透明絶縁材料が基板310の材料として使用可能である。例えば、基板310の材料として、ガラス、石英、有機ポリマーまたは有機−無機複合材料が使用できる。本開示の例示的な実施例において、ライン部が基板310上にさらに配置され、各エピタキシャルスタックに発光信号および共通電圧を印加することができる。このために、基板310は、ライン部および/または駆動デバイスをガラス、石英、シリコン、有機ポリマーまたは有機−無機複合材料上に形成することにより得られる、印刷回路基板または複合基板として提供できる。第1エピタキシャルスタック320は、順に積層されるn型半導体層321、活性層323およびp型半導体層325を含む。本例示的な実施例において、n型半導体層321およびp型半導体層325は、単層構造、多層構造または超格子層を有することができる。加えて、活性層323は、単一量子井戸構造または多重量子井戸構造を有してもよい。第2エピタキシャルスタック330は、順に積層されるn型半導体層331、活性層333およびp型半導体層335を含む。本例示的な実施例において、n型半導体層331およびp型半導体層335は、単層構造、多層構造または超格子層を有してもよい。加えて、活性層333は、単一量子井戸構造または多重量子井戸構造を有してもよい。

第2エピタキシャルスタック330のn型半導体層331、活性層333およびp型半導体層335は、赤色光を放出する半導体材料を含むことができる。

赤色光を放出する半導体材料として、アルミニウムガリウム砒化物(AlGaAs)、ガリウム砒化リン化物(GaAsP)、アルミニウムガリウムインジウムリン化物(AlGaInP)およびガリウムリン化物(GaP)が使用できる。しかし、赤色光を放出する半導体材料はこれにまたはこれによって限定されるべきではなく、多様な他の材料が使用できる。本例示的な実施例において、半導体層が他の色光を放出する場合、他の色光に対応する半導体材料が選択されてもよい。

第1および第2エピタキシャルスタック320および330は、基板310の前面上に順に積層され、第1および第2エピタキシャルスタック320および330のそれぞれは、光を放出する。第1エピタキシャルスタック320は、第2エピタキシャルスタック330より相対的により短い波長および相対的により高いエネルギーバンドを有する色光を放出し、第2エピタキシャルスタック330は、第1エピタキシャルスタック320より相対的により長い波長および相対的により低いエネルギーバンドを有する色光を放出する。

本開示の例示的な実施例において、第1および第2エピタキシャルスタック320および330は、互いに異なる波長帯域を有する光を放出することができる。すなわち、エピタキシャルスタックは、複数提供され、エピタキシャルスタックは、互いに異なるエネルギーバンドを有する。各エピタキシャルスタックは、多様な波長帯域の光のうち可視光帯域の色光を放出することができる。例えば、第1エピタキシャルスタック320は、第1色光L1を放出することができ、第2エピタキシャルスタック330は、第2色光L2を放出することができる。

第1および第2光L1およびL2は、互いに異なる色光であってもよい。第1および第2色光L1およびL2は、順に長くなる、互いに異なる波長帯域を有する色光であってもよい。本例示的な実施例において、第1および第2色光L1およびL2のそれぞれは、所定の波長帯域の色相を示すことができ、第1および第2色光L1およびL2が互いに混合されるときに白色を示すように選択されてもよい。例えば、第1色光L1は、青色光であってもよく、第2色光L2は、赤色光であってもよい。他の例として、第1色光L1は、青色光であってもよく、第2色光L2は、黄色光であってもよい。他の例として、第1色光L1は、青色光であってもよく、第2色光L2は、緑色光であってもよい。第1および第2色光L1およびL2が互いに混合されるとき、第1および第2色光L1およびL2の混合光は、略白色を示すことができるが、第1および第2色光L1およびL2の光度差によって、色温度および色座標に差が存在する。

以下、説明の便宜のために、第1色光L1は、青色光として説明し、第2色光L2は、赤色光として説明することとする。

各エピタキシャルスタックは、基板310の後面方向に光を放出する。後面方向は、第1および第2エピタキシャルスタック320および330が積層される反対方向に対応する。以下、説明の便宜のために、基板310の前面が向かう方向は、「前面方向」または「上方向」と称し、基板310の後面が向かう方向は、「後面方向」または「下方向」と称する。しかし、「上」および「下」という用語は、互いに相対的な方向を示し、発光積層構造の配列または積層方向によって変化可能である。

第1および第2エピタキシャルスタック320および330のそれぞれは、下方向に光を放出する。すなわち、第1エピタキシャルスタック320は、その下に配置される基板310に光を放出し、第2エピタキシャルスタック330は、その下に配置される第1エピタキシャルスタック320および基板310に光を放出する。この場合、第1エピタキシャルスタック320は、その上に配置される第2エピタキシャルスタック330から放出される光の大部分を透過させる。このために、第1エピタキシャルスタック320の少なくとも一部分、好ましくは、全体部分が光透過性材料で形成される。「光透過性材料」という用語は、光透過性材料が光を実質的に全体的に透過させる場合のみならず、光透過性材料が所定の波長を有する光または所定の波長を有する光の一部分を透過させる場合も表す。例示的な実施例において、第1エピタキシャルスタック320は、その上に配置される第2エピタキシャルスタック330からの光の約60%以上を透過させることができる。他の実施例により、第1エピタキシャルスタック320は、その上に配置される第2エピタキシャルスタック330からの光の約80%以上を透過させることができ、他の実施例によれば、第1エピタキシャルスタック320は、その上に配置される第2エピタキシャルスタック330からの光の約90%以上を透過させることができる。

本開示の例示的な実施例による上述した構造を有する発光積層構造では、第1および第2エピタキシャルスタック320および330は、第1および第2エピタキシャルスタック320および330に発光信号をそれぞれ印加する信号ラインが第1および第2エピタキシャルスタック320および330に独立に接続されるため、独立して駆動可能であり、光が各エピタキシャルスタックから放出されるかによって、多様な色温度を有する色光および白色光をディスプレイすることができる。加えて、互いに異なる波長を有する光を放出する第1および第2エピタキシャルスタック320および330が互いに重なるように形成されるので、発光積層構造は、狭い面積内に形成可能である。

結果として、本開示の例示的な実施例による発光積層構造は、太陽光に近い白色光を実現することができ、使用者の要求に応じて多様な色相を有する光を放出することができる。

図37Aは、本開示の例示的な実施例による発光積層構造を示す平面図であり、図37Bは、図37AのI−I’線に沿った断面図である。以下、説明の便宜のために、平面における発光積層構造の構造を、図37Aを参照して平面で説明し、断面における発光積層構造の構造を、図37Bを参照して断面で説明することとする。

図37Aおよび図37Bを参照すると、本開示の例示的な実施例による発光積層構造は、実質的に長方形状を有することができるが、発光積層構造の形状は、長方形状に限定されるべきではない。

本開示の例示的な実施例において、発光積層構造は、平面図からみて、発光区域EAと、周辺区域PAとを含む。第1および第2エピタキシャルスタック320および330は、発光積層構造の発光区域EA内で積層される。周辺区域PAは、発光区域EAの少なくとも一側に隣接して配置される。本例示的な実施例において、周辺区域PAは、発光区域EAを取り囲むように提供される。コンタクト部が周辺区域PA内に配置され、第1および第2エピタキシャルスタック320および330を配線に電気的に接続する。コンタクト部は、コンタクトホールが第1および第2エピタキシャルスタック320および330の少なくとも一部分を介して設けられる区域であり、コンタクト部は、第1、第2および第3コンタクト部320C、330Cおよび340Cを含む。第1コンタクト部320Cは、第1エピタキシャルスタック320に発光信号を供給するために設けられ、第2コンタクト部330Cは、第2エピタキシャルスタック330に発光信号を供給するために設けられ、第3コンタクト部340Cは、第1および第2エピタキシャルスタック320および330に共通電圧を供給するために設けられる。本例示的な実施例において、電極部と配線との電気的な接続のために、第1コンタクトホールCH1が第1コンタクト部320Cに設けられ、第2コンタクトホールCH2が第2コンタクト部330Cに設けられ、第3および第4コンタクトホールCH3およびCH4が第3コンタクト部340Cに設けられる。

本例示的な実施例において、コンタクト部は、長方形状の各角に対応する位置に配置される。すなわち、発光積層構造が四角形状を有する場合、第1コンタクト部320C、第2コンタクト部330Cおよび第3コンタクト部340Cは、発光区域が中心部分に位置するように、四角形状の4つの角のうち3つの角に配置される。しかし、コンタクト部の位置はこれにまたはこれによって限定されるべきではなく、多様な方式で変更可能である。すなわち、コンタクト部は、四角形状の辺の中心または四角形状の内部に配置されてもよい。

本例示的な実施例において、第1および第2エピタキシャルスタック320および330は、平面図からみて、互いに重なってもよい。第1および第2エピタキシャルスタック320および330は、発光区域EA内で互いに完全に重なってもよいが、電極部との接触のために、周辺区域内では互いに完全に重ならなくてもよい。

第1および第2エピタキシャルスタック320および330のそれぞれは、第1および第2エピタキシャルスタック320および330に発光信号を印加するための電極部を含む。

電極部は、第1信号電極320Eと、第2信号電極330Eと、共通電極340Eとを含む。

第1信号電極320E、第2信号電極330Eおよび共通電極340Eは、平面図からみて、互いに離隔する。第1信号電極320E、第2信号電極330Eおよび共通電極340Eは、第1コンタクト部320C、第2コンタクト部330Cおよび第3コンタクト部340Cにそれぞれ対応する位置に配置される。

この場合、第1信号電極320E、第2信号電極330Eおよび共通電極340Eのそれぞれは、周辺区域PAにのみ配置されるか、または周辺区域PAおよび発光区域EAにわたって配置されてもよい。本開示の例示的な実施例による発光積層構造は、光Lを下方向に放出するので、発光積層構造上に形成される第1信号電極320E、第2信号電極330Eおよび共通電極340Eは、光路上に配置されず、そのため、第1信号電極320E、第2信号電極330Eおよび共通電極340Eは、発光区域EAを覆うように提供される。本例示的な実施例において、第1信号電極320Eおよび第2信号電極330Eは、周辺区域PAに配置され、共通電極340Eは、第1および第2信号電極320Eおよび330Eより広い面積を有し、周辺区域PAおよび発光区域EAの一部分上に配置される。

第1信号電極320Eおよび共通電極340Eは、第1エピタキシャルスタック320に接続される。第2信号電極330Eおよび共通電極340Eは、第2エピタキシャルスタック330に接続される。第1信号電極320Eは、第1コンタクトホールCH1を介して第1エピタキシャルスタック320に接続され、共通電極340Eは、第3コンタクトホールCH3を介して第1エピタキシャルスタック320に接続される。第2信号電極330Eは、第2コンタクトホールCH2を介して第2エピタキシャルスタック330に接続され、共通電極340Eは、第4コンタクトホールCH4を介して第2エピタキシャルスタック330に接続される。

次に、発光積層構造を図37Aおよび図37Bを参照してその積層順序に従って説明する。

本例示的な実施例により、第1エピタキシャルスタック320が基板310上に配置される。

第1p型コンタクト電極327が第1エピタキシャルスタック320上に配置される。具体的には、第1p型コンタクト電極327は、第1エピタキシャルスタック320のp型半導体層と接触するように提供される。第1p型コンタクト電極327は、透明導電性材料、例えば、透明導電性酸化物(TCO)を含むことができ、約2000オングストローム〜約2マイクロメートルの厚さを有することができる。透明導電性酸化物は、スズ酸化物(SnO)、インジウム酸化物(InO2)、亜鉛酸化物(ZnO)、インジウムスズ酸化物(ITO)およびインジウムスズ亜鉛酸化物(ITZO)を含むことができる。透明導電性酸化物は、蒸発器またはスパッタを用いた化学気相蒸着(CVD)または物理気相蒸着(PVD)によって蒸着できる。第1p型コンタクト電極327の材料はこれにまたはこれによって限定されるべきではない。

本開示の例示的な実施例において、長波長通過フィルタ360は、第1p型コンタクト電極327上に配置される。長波長通過フィルタ360は、高純度および高効率を有する色光を提供するための構成要素であってもよく、発光積層構造において選択的に利用可能である。長波長通過フィルタ360は、相対的により短い波長を有する光が相対的により長い波長を有する光を放出するエピタキシャルスタックに進行することを遮断するために使用される。

本例示的な実施例において、長波長通過フィルタ360は、所定の波長を有する光を選択的に透過させる。長波長通過フィルタ360は、第2エピタキシャルスタック330から放出される第2色光を透過させることができ、第2色光を除いた光を遮断または反射させることができる。したがって、第2エピタキシャルスタック330から放出される第2色光は、下方向に進行することができ、第1エピタキシャルスタック320から放出される第1色光は、第2エピタキシャルスタック330に向かって進行しなくてもよいし、長波長通過フィルタ360によって反射または遮断可能である。

第1色光は、第2色光より相対的により短い波長および相対的に高いエネルギーを有する光である。第1色光が第2エピタキシャルスタック330内に入射する場合、付加的な発光が第2エピタキシャルスタック330内で誘発されることがある。本例示的な実施例において、第1色光は、第2エピタキシャルスタック330内に入射することが長波長通過フィルタ360によって防止できる。

長波長通過フィルタ360は、発光区域EAおよび周辺区域PA内に配置されるが、長波長通過フィルタ360は、必要に応じて、周辺区域(AP)内には配置されなくてもよい。

第2エピタキシャルスタック330は、接着層350が間に介在する状態で第1p型コンタクト電極327がその上に配置される、第1エピタキシャルスタック320上に配置される。

接着層350は、非導電性材料を含むことができ、光透過性材料を含むことができる。例えば、接着層350は、光学用透明接着剤(optically clear adhesive:OCA)を含むことができる。接着層350の材料は、接着層350の材料が光学的に透明で各エピタキシャルスタックに安定して貼り合わされる限り、特に限定されるべきではない。例えば、接着層350は、SU−8、多様なレジスト、パリレン、ポリ(メチルメタクリレート)(PMMA)およびベンゾシクロブテン(BCB)のようなエポキシ系ポリマーのような有機材料、およびシリコン酸化物、アルミニウム酸化物および溶融ガラスのような無機材料を含むことができる。また、必要に応じて、導電性酸化物が接着層として使用可能であり、この場合、導電性酸化物は、他の構成要素から絶縁される必要がある。有機材料が接着層として用いられ、無機材料のうち溶融ガラスが接着層として用いられる場合、第1および第2エピタキシャルスタック320および330は、第1および第2エピタキシャルスタック320および330の接着側(adhesive side)上に材料をコーティングし、高真空状態下で材料に高温および高圧を印加することにより、互いに貼り合わされる。(溶融ガラスを除いた)無機材料が接着層として用いられる場合、第1および第2エピタキシャルスタック320および330は、第1および第2エピタキシャルスタック320および330の接着側上に無機材料を蒸着し、化学機械的平坦化(CMP)を利用して無機材料を平坦化し、無機材料の表面上でプラズマ処理を行い、第1および第2エピタキシャルスタック320および330を高真空状態下で貼り合わされることにより、互いに付貼り合わされる。

第2エピタキシャルスタック330は、接着層350上に配置される。

n型半導体層、活性層およびp型半導体層の一部分を除去することにより、メサMが第2エピタキシャルスタック330に形成される。半導体層の一部分(詳しくは、n型半導体層および活性層の一部分)がメサMの形成されない部分から除去され、そのため、n型半導体層の上部表面が露出する。メサMが配置される区域は、発光区域EAと重なってもよく、メサMが配置されない区域は、周辺区域PA、特に、コンタクト部と重なってもよい。

第2n型コンタクト電極339がn型半導体層の露出した上部表面上に配置される。第2p型コンタクト電極337は、オーミック電極337’および第1絶縁層371が間に介在する状態で、メサがその上に形成されるp型半導体層の上部に配置される。

第1絶縁層371は、第2エピタキシャルスタック330の上部表面を覆い、オーミック電極337’が配置される部分に対応してそれを貫通して設けられるコンタクトホールを含む。オーミック電極337’は、第3コンタクト部340Cが配置される区域に対応して配置され、多様な形状、例えば、図37Aに示すようなドーナツ形状を有することができる。

オーミック電極337’は、オーミック接触のために使用可能であり、多様な材料を含むことができる。本開示の例示的な実施例において、オーミック電極337’は、Au(Zn)またはAu(Be)を含むことができる。この場合、オーミック電極337’用材料は、Ag、AlおよびAuより低い反射率を有するので、追加の反射電極がさらに配置されてもよい。追加の反射電極用材料として、AgまたはAuが使用可能であり、Ti、Ni、CrまたはTaを含む層が隣接した構成要素への接着のための接着層として配置されてもよい。この場合、接着層は、AgまたはAuを含む反射電極の上部および下部表面上に薄く蒸着される。

第2p型コンタクト電極337が第1絶縁層371上に配置される。第2p型コンタクト電極337は、発光区域EAと重なってもよく、平面図からみて、発光区域EAの全体を覆うように提供される。第2p型コンタクト電極337は、反射性を有する材料を含み、第2エピタキシャルスタック330からの光を下方向に反射させることができる。第2p型コンタクト電極337用の反射性を有する材料として、多様な反射性金属、例えば、Ag、AlおよびAuが使用可能であり、Ti、Ni、CrまたはTaを含む層が隣接した構成要素への接着のための接着層として配置されてもよい。

特に、第2エピタキシャルスタック330が赤色光を放出する場合、第2p型コンタクト電極337は、赤色光の波長帯域で高い反射率を有する材料を含むことができる。例えば、第2p型コンタクト電極337は、赤色光の波長帯域で高い反射率を有する「Au」を含むことができ、この場合、「Au」は、第2p型コンタクト電極337の底から漏れる青色光を吸収可能なため、不必要な色干渉が減少できる。

本例示的な実施例において、第1絶縁層271は、第2エピタキシャルスタック330からの光の反射が容易に行われるように、反射性を有するように形成される。例えば、第1絶縁層371は、全方向反射器(omni−directional reflector:ODR)構造を有してもよい。

第2絶縁層373が、第2p型コンタクト電極337がその上に配置される、第1絶縁層371の上部に配置される。第2絶縁層373は、第2エピタキシャルスタック330の上部表面および第2絶縁層373の下に配置される各構成要素の側面を覆う。

本例示的な実施例において、第2絶縁層373はさらに、反射性を有することができる。加えて、詳細に示さないが、本開示の例示的な実施例において、光不透過性層が、発光積層構造の側面に対応する第2絶縁層373の側部分上に、さらに配置されてもよい。光不透過性層は、光遮断層として作用して、第1および第2エピタキシャルスタック320および330からの光が発光積層構造の側面を介して出射するのを防止することができ、光を吸収または反射させる材料を含むことができる。

光不透過性層は、光不透過性層が光を吸収または反射させて光の透過を遮断する限り、特に限定されるべきではない。本開示の例示的な実施例において、光不透過性層は、分布ブラッグ反射器(DBR)誘電体ミラー、絶縁層上に形成される金属反射層または黒色有機ポリマー層であってもよい。金属反射層が光不透過性層として用いられる場合、金属反射層は、金属反射層が他の発光積層構造の構成要素から電気的に絶縁される、フローティング状態であってもよい。

発光積層構造の側面上に配置される光不透過性層によって、特定の発光積層構造から出射する光が隣接した発光積層構造に影響を及ぼすか、隣接した発光積層構造から出射する光と混合されるのを防止することができる。

第1および第2信号電極320Eおよび330Eおよび共通電極340Eは、第2絶縁層373上に配置される。第1および第2信号電極320Eおよび330Eおよび共通電極340Eは、単層または多層金属を有してもよい。例えば、第1および第2信号電極320Eおよび330Eおよび共通電極340Eは、Al、Ti、Cr、Ni、Au、Ag、Sn、WおよびCuの金属またはその合金を含む多様な材料を含むことができる。

第1および第2信号電極320Eおよび330Eおよび共通電極340Eは、その下に設けられる第1、第2、第3および第4コンタクトホールCH1、CH2、CH3およびCH4を介して対応する構成要素にそれぞれ接続される。

第1信号電極320Eは、第1コンタクトホールCH1を介して第1エピタキシャルスタック320のn型半導体層に接続される。第1コンタクトホールCH1は、上から第2絶縁層373、第1絶縁層371、第2エピタキシャルスタック330、接着層350、長波長通過フィルタ360、第1p型コンタクト電極327および第1エピタキシャルスタック320の部分を貫通することにより設けられる。特に、第1エピタキシャルスタック320のp型半導体層および活性層の部分が除去され、第1エピタキシャルスタック320のn型半導体層の上部表面が露出するので、第1信号電極320Eが第1コンタクトホールCH1を介して第1エピタキシャルスタック320のn型半導体層に接続される。

第2信号電極330Eは、第2コンタクトホールCH2を介して第2エピタキシャルスタック330のn型半導体層に接続される。第2コンタクトホールCH2は、上から第2絶縁層373および第1絶縁層371を貫通することにより設けられる。したがって、第2エピタキシャルスタック330のn型半導体層の上部表面が第2コンタクトホールCH2を介して露出し、そのため、第2信号電極330Eが第2コンタクトホールCH2を介して第2エピタキシャルスタック330のn型半導体層に接続される。

共通電極340Eは、第3コンタクトホールCH3を介して第1エピタキシャルスタック320の第1p型コンタクト電極327に接続される。第3コンタクトホールCH3は、上から第2絶縁層373、第1絶縁層371、第2エピタキシャルスタック330、接着層350および長波長通過フィルタ360の部分を貫通することにより設けられる。したがって、第1p型コンタクト電極327の上部表面が露出し、共通電極340Eは、第3コンタクトホールCH3を介して第1p型コンタクト電極327に接続される。

加えて、共通電極340Eは、第4コンタクトホールCH4を介して第2エピタキシャルスタック330の第2p型コンタクト電極337に接続される。第4コンタクトホールCH4は、第2絶縁層373の部分を貫通することにより設けられる。したがって、第2p型コンタクト電極337の上部表面が露出し、共通電極340Eは、第4コンタクトホールCH4を介して第2p型コンタクト電極337に接続される。

上述した構造を有する発光積層構造は、第1および第2エピタキシャルスタック320および330からの発光を利用して光を下方向に放出する。この場合、別途の駆動信号が第1および第2信号電極320Eおよび330Eを介して第1および第2エピタキシャルスタック320および330に印加され、そのため、第1および第2エピタキシャルスタック320および330の発光が独立して制御可能である。つまり、第1エピタキシャルスタック320が発光するか否かは、第1信号電極320Eおよび共通電極340Eを介して第1エピタキシャルスタック320にそれぞれ印加される発光信号および共通電圧によって決定可能である。第2エピタキシャルスタック330が発光するか可かは、第2信号電極330Eおよび共通電極340Eを介して第2エピタキシャルスタック330にそれぞれ印加される発光信号および共通電圧によって決定可能である。結果として、第1エピタキシャルスタック320および第2エピタキシャルスタック330の発光は、第1信号電極320Eに印加される信号および第2信号電極330Eに印加される信号によって、個別に異なってもよい。

上述した実施例において、共通電圧が第1および第2エピタキシャルスタック320および330のp型半導体層に印加され、発光信号が第1および第2エピタキシャルスタック320および330のn型半導体層に印加されるが、本開示の実施例がこれにまたはこれによって限定されるべきではない。本開示の他の実施例により、共通電圧が第1および第2エピタキシャルスタック320および330のn型半導体層に印加され、発光信号が第1および第2エピタキシャルスタック320および330のp型半導体層に印加される。このような構造は、p型半導体層、活性層およびn型半導体層の順に各エピタキシャルスタックの構成要素を配列することにより容易に実現可能であり、このような順序は、本開示において半導体層の積層順序、すなわち、n型半導体層、活性層およびp型半導体層の順序とは異なる。

したがって、本例示的な実施例による発光積層構造は、第1および第2エピタキシャルスタックを個別に駆動することにより、各動作モードによって異なる色温度を有する白色光を提供することができる。特に、第1および第2エピタキシャルスタックに印加される電流が個別に制御されるので、色温度が微細に制御可能である。そのため、本例示的な実施例による発光積層構造が照明装置に適用される場合、光は使用者の感度によって制御可能である。加えて、第1および第2エピタキシャルスタックからの光を利用して色光を多様な方式で互いに混合することにより白色光が発生し、結果として、高い演色指数(color rendering index)および広い相関色温度(correlated color temperature)を有する白色光が実現できる。

また、色相をディスプレイするときに、上述した構造を有する発光積層構造は、平面上の互いに異なる区域を介して互いに異なる色光を提供するよりは、互いに重なる区域を介して互いに異なる色光を提供し、そのため、発光素子が小型化され、集積化されることが可能である。従来技術によれば、互いに異なる色光、例えば、赤色および青色光を放出する発光素子は、白色光を実現するために平面上で互いに離隔して配置される。したがって、発光素子が平面上で互いに離隔して配置されるので、従来技術において発光素子によって占有される面積は相対的に大きい。一方、本開示によれば、互いに異なる色光を放出する発光素子が互いに重なる同一の面積内に配置されて発光積層構造を形成し、そのため、従来技術より著しく小さな面積により白色光が実現できる。そのため、高解像度ディスプレイデバイスが小さい面積内に製造できる。

また、積層方式で製造される従来の発光素子の場合にも、従来の発光素子は、各発光素子内にコンタクト部を個別に形成することにより、例えば、発光素子を個別に、そして分離的に形成し、ワイヤリングを用いて発光素子を互いに接続することにより製造される。結果として、発光デバイスの構造が複雑で、発光デバイスを製造することが容易でない。しかし、本開示の例示的な実施例による発光積層構造は、1つの基板上に複数のエピタキシャルスタックを順に積層し、最小工程によりエピタキシャルスタックにライン部を接続することにより製造され、そのため、発光積層構造の構造および製造方法が単純化できる。

上述した構造を有する発光積層構造は、基板上に第1および第2エピタキシャルスタックを順に積層することにより製造可能であり、これについて添付した図面を参照して説明する。本開示の例示的な実施例による発光積層構造は、単一個数で製造されるか、または複数の発光積層構造が広い面積を有する基板を用いて実質的に同時に形成されてもよい。発光積層構造が実質的に同時に形成される場合、互いに隣接した発光積層構造を互いに電気的に物理的に分離するためにリセス部分が形成されてもよく、各発光積層構造は、最終工程でリセス部分に対応する部分を切断することにより単一発光積層構造として分離可能である。

以下の実施例において、1つの発光積層構造が代表例として示される。複数の発光積層構造が形成される場合、図面において、最外郭ラインに相当する部分が基板の周縁および互いに隣接した発光積層構造間の境界に相当する。

図38A、図39A、図40A、図41A、図42Aおよび図43Aは、本開示の例示的な実施例による発光積層構造の製造方法を順に示す平面図であり、図38B、図39B、図40B〜図40G、図41B〜図41D、図42Bおよび図43Bは、それぞれ図38A、図39A、図40A、図41A、図42Aおよび図43AのI−I線に沿った断面図である。

本開示の例示的な実施例による発光積層構造は、基板310上に第1エピタキシャルスタック320を形成し、別途の仮基板上に第2エピタキシャルスタック330を形成し、第1エピタキシャルスタック320上に第2エピタキシャルスタック330を形成し、第1および第2エピタキシャルスタック320および330を接続する電極部を形成することにより製造できる。以下、説明の便宜のために、発光積層構造の製造について、第2エピタキシャルスタック330を仮基板上に形成し、第2エピタキシャルスタック330を第1エピタキシャルスタック230上で形成する順序で説明する。

図38Aおよび図38Bを参照すると、第1エピタキシャルスタック320が第1仮基板310p上に配置される。

第1仮基板310pは、第2エピタキシャルスタック330を形成するための半導体基板310であってもよい。第1仮基板310pは、形成される半導体層によって異なって設定可能であり、第2エピタキシャルスタック330が赤色光を放出する半導体層を含む場合、第1仮基板310pは、ガリウム砒化物(GaAs)基板であってもよい。第2エピタキシャルスタック330は、第1仮基板310p上にn型半導体層、活性層およびp型半導体層を形成し、活性層およびp型半導体層の一部分、および必要であれば、メサ構造Mを形成するために、n型半導体層の一部分を除去することにより製造される。メサ構造Mが形成されるので、第2エピタキシャルスタック330のn型半導体層の上部表面が露出する。

図39Aおよび図39Bを参照すると、第2n型コンタクト電極339、オーミック電極337’および第1絶縁層371は、メサ構造Mがその上に形成される、第2エピタキシャルスタック330上に形成される。第2n型コンタクト電極339は、第2コンタクト部330Cに相当する区域内に配置され、オーミック電極337’は、第3コンタクト部340Cに相当する区域内に配置される。第2エピタキシャルスタック330のp型半導体層の上部表面を介して露出するコンタクトホールが、オーミック電極337’の形成される区域内で、第1絶縁層371を介して形成され、オーミック電極337’は、コンタクトホール内に形成される。

図40Aおよび図40Bを参照すると、第2p型コンタクト電極337は、第1絶縁層371がその上に形成される、第1仮基板310pの上部に形成される。第2p型コンタクト電極337は、反射材料を含むことができ、発光区域EAを覆うように形成される。第2p型コンタクト電極337は、第1絶縁層371およびオーミック電極337’の全体表面上に反射性導電材料を形成し、フォトリソグラフィー工程を利用して反射性導電材料をパターニングすることにより形成される。

図40Aおよび図40Cを参照すると、第2p型コンタクト電極337がその上に形成される、第2エピタキシャルスタック330は、第1仮基板310pとともに反転し、仮接着層351が間に介在する状態で第2仮基板310qに貼り合わされる。

仮接着層351は、第2エピタキシャルスタック330を第2仮基板310qに貼り合わせて所定の工程が実行された後に、除去される。したがって、仮接着層351は、所定の接着力を有しかつ除去しやすい材料の中から選択される材料で形成される。仮接着層351の材料は特に限定されるべきではない。

第2仮基板310qは、第2エピタキシャルスタック330がその上に一時的に貼り合わされるキャリア基板であり、第2仮基板310qの類型は特に限定されるべきではない。

図40Aおよび図40Dを参照すると、第1仮基板310pは、第2エピタキシャルスタック330が第2仮基板310qに貼り合わされた後に、除去される。第1仮基板310pは、ウェットエッチング工程、ドライエッチング工程、物理的除去工程またはレーザリフトオフ工程のような多様な方法によって除去可能である。しかし、第1仮基板310pを除去するための方法はこれにまたはこれによって限定されるべきではない。第1仮基板310pは、第1仮基板310pと第2エピタキシャルスタック330との間に犠牲層を形成し犠牲層を除去することにより除去可能である。

図40Aおよび図40Eを参照すると、第1エピタキシャルスタック320が第2エピタキシャルスタック330とは別途に製造される。第1エピタキシャルスタック320は、n型半導体層、活性層およびp型半導体層を基板310上に順に形成することにより製造できる。第1p型コンタクト電極327、長波長通過フィルタ360および接着層350が第1エピタキシャルスタック320上に順に形成される。

図40Aおよび図40Fを参照すると、第2仮基板310q上に形成された第2エピタキシャルスタック330は反転して、接着層350が間に介在する状態で、第1エピタキシャルスタック320に貼り合わされる。この場合、第2エピタキシャルスタック330のn型半導体層の下部表面は、第1エピタキシャルスタック320のp型半導体層と向かい合うように配置され、その後、第2エピタキシャルスタック330は、第1エピタキシャルスタック320に貼り合わされる。接着層350は、非導電性材料を含むことができ、光透過特性を有する材料を含むことができる。例えば、光学用透明接着剤が接着層350として使用可能である。

図40Aおよび図40Gを参照すると、第2エピタキシャルスタック330の上部に配置される仮接着層351および第2仮基板310qは、第2エピタキシャルスタック330が第1エピタキシャルスタック320上に貼り合わされた後に、除去される。第2仮基板310qは、多様な方法で除去可能である。例えば、第2仮基板310qがサファイア基板の場合、サファイア基板は、レーザリフトオフ工程、ストレスリフトオフ工程、化学的リフトオフ工程または物理的研磨工程により除去可能である。

上述のように、第1エピタキシャルスタック320および第2エピタキシャルスタック330が基板310上に形成された後、電極部およびコンタクト部が形成される。これを以下に詳細に説明する。

図41Aおよび図41Bを参照すると、第1絶縁層371、第2エピタキシャルスタック330、接着層350および長波長通過フィルタ360の部分が第1コンタクト部320Cおよび第3コンタクト部340Cに対応する区域から除去されて、第1仮コンタクトホールCH1’および第3コンタクトホールCH3をそれぞれ形成する。この場合、第1仮コンタクトホールCH1’および第3コンタクトホールCH3を有する発光積層構造の周辺に沿ってリセス部分が形成される。リセス部分は、発光積層構造が形成されるときに、互いに隣接した発光積層構造を電気的に、そして物理的に分離するように形成される。

第1仮コンタクトホールCH1’、第3コンタクトホールCH3およびリセス部分は、フォトリソグラフィー工程を利用して形成される。第1p型コンタクト電極327の上部表面が第1仮コンタクトホールCH1’、第3コンタクトホールCH3およびリセス部分Rによって外部に露出する。

図41Aおよび図41Cを参照すると、第1p型コンタクト電極327および第1エピタキシャルスタック320の部分、具体的には、第1エピタキシャルスタック320のp型半導体層および活性層の部分が第1コンタクト部320Cに相当する区域から除去されて、第1コンタクトホールCH1を形成する。この場合、第1エピタキシャルスタック320のp型半導体層および活性層の部分が発光積層構造の周辺に沿って除去され、そのため、リセス部分がさらにエッチングされる。

第1コンタクトホールCH1およびリセス部分の追加的なエッチングは、フォトリソグラフィー工程により実行されてもよい。したがって、第1エピタキシャルスタック320のn型半導体層の上部表面は、第1コンタクト部320Cに対応する区域で第1コンタクトホールCH1を介して、そして発光積層構造の周辺内のリセス部分を介して外部に露出する。

図41Aおよび図41Dを参照すると、第1エピタキシャルスタック320のn型半導体層の部分が発光積層構造の周辺に沿って除去され、そのため、リセス部分がさらにエッチングされる。これは、各発光積層構造をそれに隣接した発光積層構造から電気的に、そして物理的に分離するためのものである。本作業においてリセス部分の追加的なエッチングは、フォトリソグラフィー工程により実行されてもよく、基板310の上部表面は、発光積層構造の周辺で露出する。

図42Aおよび図42Bを参照すると、第2絶縁層373が基板310の全体表面上部に形成されパターニングされて、第2コンタクト部330Cおよび第3コンタクト部340Cに第2コンタクトホールCH2および第4コンタクトホールCH4をそれぞれ形成する。第2絶縁層373は、第2エピタキシャルスタック330の上部の構成要素だけでなく、第1および第2エピタキシャルスタック320および330およびリセス部分が形成される発光積層構造の側面も覆う。

第2コンタクトホールCH2および第4コンタクトホールCH4は、フォトグラフィー工程により形成される。

第2コンタクトホールCH2が形成されると、第2絶縁層373の下に配置される第1絶縁膜371がパターニングされ、そのため、第2n型コンタクト電極339の上部表面が外部に露出する。第4コンタクトホールCH4は、第2p型コンタクト電極337の上部表面の一部分が第3コンタクト部340Cで外部に露出するように形成される。本例示的な実施例において、第4コンタクトホールCH4が形成される区域は、オーミック電極337’が形成される区域と重なるが、これは説明の便宜のためのものに過ぎず、これにまたはこれによって限定されるべきではない。

本例示的な実施例において、第2絶縁層373が第1および第3コンタクトホールCH1およびCH3内に形成され、第2絶縁層373がパターニングされるときに、第1エピタキシャルスタック320のn型半導体層の上部表面上の第2絶縁層373および第1p型コンタクト電極327の上部表面上の第2絶縁層373は、第1エピタキシャルスタック320のn型半導体層の上部表面および第1p型コンタクト電極327の上部表面の露出が保持されるように除去される。しかし、第1および第3コンタクトホールCH1およびCH3の側壁上に形成される第2絶縁層373は、除去されずに保持できる。

図43Aおよび図43Bを参照すると、第1信号電極320E、第2信号電極330Eおよび共通電極340Eが、第1、第2、第3および第4コンタクトホールCH1、CH2、CH3およびCH4が形成された、基板310上に形成される。

第1信号電極320E、第2信号電極330Eおよび共通電極340Eは、フォトリソグラフィー工程により形成され、第1信号電極320E、第2信号電極330Eおよび共通電極340Eは、1つのマスクを用いる単一工程により形成される。

第1信号電極320Eは、第1コンタクト部320Cに相当する区域に形成され、第2信号電極330Eは、第2コンタクト部330Cに相当する区域に形成され、共通電極340Eは、第3コンタクト部340Cに相当する区域に形成される。したがって、第1信号電極320Eは、第1コンタクトホールCH1を介して第1エピタキシャルスタック320のn型半導体層に接続され、第2信号電極330Eは、第2コンタクトホールCH2を介して第2n型コンタクト電極339に直接接続され、共通電極340Eは、第3および第4コンタクトホールCH3およびCH4を介して第1p型コンタクト電極327および第2p型コンタクト電極337にそれぞれ接続される。

各発光積層構造は、上述した作業によって製造される。図示しないが、複数の発光積層構造が実質的に同時に製造される場合、発光積層構造の境界に沿って基板310を切断する工程がさらに実行されてもよい。複数の発光積層構造が広い面積を有する基板を用いて実質的に同時に製造され、発光積層構造を各発光積層構造に分割するために切断される場合、発光積層構造の製造効率が改善され、発光積層構造の製造費用が減少することが可能である。

本開示の例示的な実施例による発光積層構造は、高効率の均一な光を提供するために多様な構成要素を追加的に含んでもよい。一例として、本開示の例示的な実施例による発光積層構造は、発光面上で多様な凹凸部分PRを含むことができる。

図44は、本開示の例示的な実施例による発光積層構造を示す断面図である。具体的には、図44は、第2エピタキシャルスタック330上に形成される凹凸部分PRを示す。以下の実施例では、重複を避けるために、上述した実施例の特徴と異なる特徴が主に説明される。説明されていない部分は、上述した実施例のそれと同一または類似するものと仮定する。

本開示の例示的な実施例による発光積層構造は、第2エピタキシャルスタック330上に形成される凹凸部分PRを含むことができる。本開示の例示的な実施例において、凹凸部分PRは、第2エピタキシャルスタック330の発光面に対応するn型半導体層の下部表面上に配置される。

凹凸部分PRは、発光効率を向上させるために用いられる。凹凸部分PRは、その上に凹凸部分がランダムに配列される、多角形ピラミッド、半球または粗さを有する表面のような、多様な形状に提供できる。凹凸部分PRは、多様なエッチング工程によるテクスチャリングによって形成されてもよい。例えば、凹凸部分PRは、マイクロフォトグラフィーを利用したドライエッチング工程、結晶特性を利用したウェットエッチング工程、サンドブラストのような物理的方法を利用したテクスチャリング工程、イオンビームエッチング工程またはブロックコポリマーのエッチング速度差を利用したテクスチャリング工程のような多様な工程により形成されてもよい。

本開示の例示的な実施例において、第1および第2エピタキシャルスタックからの第1および第2色光間の光度差があり得、光度差は、白色光が発生するときに、色温度における差を誘発することがある。本例示的な実施例において、凹凸部分は、第1および第2エピタキシャルスタックの発光面上に選択的に形成されて発光効率を向上させ、結果として、第1および第2色光間の光度差が減少できる。特に、赤色に対応する色光は、青色より可視性が低く、光の光度差は、第2エピタキシャルスタックをテクスチャリングすることにより減少できる。

第2エピタキシャルスタックのn型半導体層の下部表面上に凹凸部分を形成する工程は、図40Dに示す作業後に実行され、図45は、図40Dの第2エピタキシャルスタック上に形成される凹凸部分を示す断面図である。

図45を参照すると、第2エピタキシャルスタック330のn型半導体層と接触する第1仮基板310pが除去された後、テクスチャリング工程が露出したn型半導体層上で行われて凹凸部分PRを形成する。

本開示の例示的な実施例により、凹凸部分は、他のエピタキシャルスタックに提供され、基板は除去可能である。

図46は、本開示の例示的な実施例による発光積層構造を示す断面図である。具体的には、図46は、基板310が除去され、凹凸部分PRが第2エピタキシャルスタック330に加えて、第1エピタキシャルスタック320上に形成される構造を示す。

図46を参照すると、本開示の例示的な実施例による発光積層構造は、基板310が除去された構造を有してもよい。基板310は、相対的に厚い厚さを有するので、発光積層構造の厚さは、基板310が除去されると著しく減少できる。したがって、基板310が除去された発光積層構造を別途の配線基板上に転写して所定のデバイスが製造される場合、所定のデバイスを薄くすることが容易である。

本例示的な実施例により、凹凸部分PRは、第1エピタキシャルスタック320上に配置されて光効率を向上させることができる。すなわち、凹凸部分PRは、第1エピタキシャルスタック320の発光表面に対応するn型半導体層の下部表面上に配置される。この場合、パターニングされたサファイア基板が基板310として用いられ、パターニングされたサファイア基板が除去されると、凹凸部分PRが第1エピタキシャルスタック320の発光面上に容易に形成できる。

本開示の例示的な実施例により、発光積層構造は、高い演色指数および広い相関色温度のための追加の構成要素をさらに用いることができる。一例として、発光積層構造は、第1および第2エピタキシャルスタックからそれぞれ放出される光の少なくとも一部分を他の波長を有する光に変換するための光変換層をさらに含んでもよい。

図47および図48は、本開示の例示的な実施例による光変換層を有する発光積層構造を示す断面図である。図47は、基板が除去された発光積層構造を示し、図48は、基板を含む発光積層構造を示す。

図47を参照すると、光変換層380が第1エピタキシャルスタック320の発光面に対応する下部表面上に追加的に配置されてもよい。図48を参照すると、光変換層380が基板310の下部表面上に追加的に配置され、発光積層構造の側面を選択的に覆うように光変換層380が提供されてもよい。

光変換層380は、蛍光物質および量子ドット(quantum dot)のようなナノ構造、色変換が可能な有機物質またはこれらの組み合わせを含むことができる。例えば、蛍光物質が光変換層380の材料として使用される場合、蛍光物質は、所定の波長を有する光を吸収し、所定の波長より長い波長を有する光を放出することができる。蛍光物質は、PDMS(ポリジメチルシロキサン)、PI(ポリイミド)、PMMA(ポリ(メチル2−メチルプロペノエート))またはセラミックのような透明または半透明バインダーと混合された形態で提供される。

本例示的な実施例において、発光積層構造が光変換層380を含むので、発光積層構造は、第1および第2エピタキシャルスタック320および330から放出される第1色光および/または第2色光とは異なる波長を有する光を出力することができる。したがって、本開示の例示的な実施例では、最終的に提供される光を混合することにより高い演色指数および広い相関色温度を得ることができる。

本開示の例示的な実施例による発光積層構造は、独立して使用可能であるが、これにまたはこれによって限定されるべきではない。すなわち、発光積層構造は、配線が形成されるベース基板、例えば、印刷回路基板に実装された後、多様な類型の光源として使用可能である。

図49および図50は、本開示の例示的な実施例による印刷回路基板3110上に実装される発光積層構造を示す平面図である。

図49を参照すると、本開示の例示的な実施例による複数の発光積層構造3120は、一方向に延びる印刷回路基板3110上に縦方向に沿って配列される。図50を参照すると、本開示の例示的な実施例による発光積層構造3120は、長方形状のような所定の形状および所定の面積を有する印刷回路基板3110上にマトリクス状に配列される。印刷回路基板3110の形状および発光積層構造3120の配列はこれにまたはこれによって限定されるべきではなく、多様な方式で変化可能である。そのため、発光積層構造は、点光源、線形光源または表面光源の形態で光を提供することができる。

端子が印刷回路基板3110上に形成され、発光積層構造に発光信号および共通電圧をそれぞれ印加することができ、発光積層構造の発光は、端子を介して発光積層構造に印加される発光信号および共通電圧によって決定されてもよい。

本開示の例示的な実施例による発光積層構造は、白色光を必要とする多様な照明装置に使用可能である。例えば、発光積層構造は、受光型ディスプレイデバイスに含まれるバックライトユニットおよび/または日常生活で室内および/または室外照明として使用可能である。

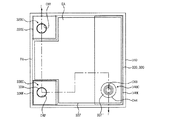

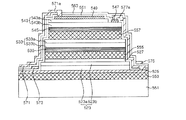

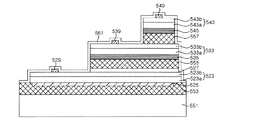

図51は、本開示の1つの例示的な実施例によるディスプレイ用発光ダイオードスタック400の概略断面図である。

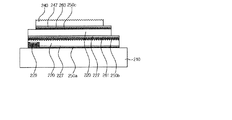

図51を参照すると、発光ダイオードスタック400は、支持基板451と、第1LEDスタック423と、第2LEDスタック433と、第3LEDスタック443と、反射電極425と、オーミック電極426と、第1絶縁層427と、第2絶縁層428と、インターコネクションライン429と、第2−p透明電極435と、第3−p透明電極445と、第1カラーフィルタ437と、第2カラーフィルタ447と、第1ボンディング層453と、第2ボンディング層455と、第3ボンディング層457とを含む。

支持基板451は、半導体スタック423、433および443を支持する。支持基板451は、その表面上にまたはその内部に回路を含むことができるが、これに限定されるものではない。支持基板451は、例えば、ガラス、サファイア基板、Si基板またはGe基板を含むことができる。

第1LEDスタック423、第2LEDスタック433および第3LEDスタック443のそれぞれは、n型半導体層423a、433aまたは443aと、p型半導体層423b、433bまたは443bと、その間に介在する活性層とを含む。活性層は、多重量子井戸構造を有してもよい。

例えば、第1LEDスタック423は、赤色光を放出するように適合化される無機発光ダイオードであってもよく、第2LEDスタック433は、緑色光を放出するように適合化される無機発光ダイオードであってもよいし、第3LEDスタック443は、青色光を放出するように適合化される無機発光ダイオードであってもよい。第1LEDスタック423は、GaInP系井戸層を含むことができ、第2LEDスタック433および第3LEDスタック443のそれぞれは、GaInN系井戸層を含むことができる。

同時に、第1〜第3LEDスタック423、433および443のそれぞれの両面は、それぞれn型半導体層およびp型半導体層である。本例示的な実施例において、第1〜第3LEDスタック423、433および443の第1導電型半導体層423a、433aおよび443aのそれぞれは、n型半導体層であり、第1〜第3LEDスタック423、433および443の第2導電型半導体層423b、433bおよび443bは、p型半導体層である。第3LEDスタック443がn型上部表面を有するので、粗面化された表面(roughened surface)が第3LEDスタック443の上部表面上に化学的エッチングにより形成される。しかし、本開示がこれに限定されるものではなく、各LEDスタックの上部および下部表面の半導体タイプは変化可能であることを理解しなければならない。

第1LEDスタック423は、支持基板451近傍に配置され、第2LEDスタック433は、第1LEDスタック423上に配置され、第3LEDスタック443は、第2LEDスタック433上に配置される。第1LEDスタック423が第2および第3LEDスタック433および443より長い波長を有する光を放出するので、第1LEDスタック423から発生する光は、第2および第3LEDスタック433および443を介して外部に放出される。また、第2LEDスタック433が第3LEDスタック443より長い波長を有する光を放出するので、第2LEDスタック433から発生する光は、第3LEDスタック443を介して外部に放出される。

反射電極425は、第1LEDスタック423の第2導電型半導体層とオーミック接触を形成し、第1LEDスタック423から発生する光を反射させる。例えば、反射電極425は、オーミック接触層425aと、反射層425bとを含むことができる。

オーミック接触層425aは、第2導電型半導体層、すなわち、p型半導体層と部分的に接触する。オーミック接触層425aによる光の吸収を防止するために、オーミック接触層425aがp型半導体層と接触する領域は、p型半導体層の全体面積の50%を超えない。反射層425bは、オーミック接触層425aおよび絶縁層427を覆う。図示のように、反射層425bは、オーミック接触層425a全体を覆うことができるが、これに限定されるものではない。その代わりとして、反射層425bは、オーミック接触層425aの一部分を覆ってもよい。

反射層425bが第1絶縁層427を覆うので、全方向反射器は、比較的高い屈折率を有する第1LEDスタック423と比較的低い屈折率を有する絶縁層427との積層構造、および反射層425bによって形成される。反射層425bは、第1LEDスタック423の面積の50%以上または第1LEDスタック423の大部分を覆い、それによって、発光効率を向上させる。

オーミック接触層425aおよび反射層425bは、金(Au)を含む金属層であってもよい。オーミック接触層425aは、例えば、Au−Zn合金またはAu−Be合金で形成される。反射層425bは、第1LEDスタック423から発生する光、例えば、赤色光に対して相対的に高い反射率を有する金属、例えば、Al、AgまたはAuで形成される。特に、Auは、第2LEDスタック433および第3LEDスタック443から発生する光、例えば、緑色光または青色光に対して相対的に低い反射率を有することができ、それによって、第2および第3LEDスタック433および443から発生して支持基板451に向かって進行する光の光吸収による光干渉を減少させることができる。

絶縁層427は、支持基板451と第1LEDスタック423との間に介在し、第1LEDスタック423を露出させる開口部を有する。オーミック接触層425aは、絶縁層427の開口部内で第1LEDスタック423に接続される。

オーミック電極426は、第1LEDスタック423の第1導電型半導体層423aとオーミック接触を形成する。オーミック電極426は、第2導電型半導体層423bを部分的に除去することにより露出する第1導電型半導体層423a上に配置される。単一オーミック電極426を図51に示すが、複数のオーミック電極426が支持基板451上の複数の領域内に整列される。オーミック電極426は、例えば、Au−Te合金またはAu−Ge合金で形成される。

第2絶縁層428は、支持基板425と反射電極425との間に介在し、反射電極425を覆う。第2絶縁層428は、オーミック電極426を露出させる開口部を有する。

インターコネクションライン429は、第2絶縁層428と支持基板451との間に介在し、第2絶縁層428の開口部を介してオーミック電極426に接続される。インターコネクションライン429は、支持基板451上で複数のオーミック電極426を互いに接続することができる。

第2−p透明電極435は、第2LEDスタック433の第2導電型半導体層433b、すなわち、そのp型半導体層とオーミック接触を形成する。第2−p透明電極435は、赤色光および緑色光に関して透過性である金属層または導電性酸化物層で構成される。

加えて、第3−p透明電極445は、第3LEDスタック443の第2導電型半導体層443b、すなわち、そのp型半導体層とオーミック接触を形成する。第3−p透明電極445は、赤色光、緑色光および青色光に関して透過性である金属層または導電性酸化物層で構成される。

反射電極425、第2−p透明電極435および第3−p透明電極445は、各LEDスタックのp型半導体層とのオーミック接触により電流拡散(current spreading)を助けることができる。

第1カラーフィルタ437は、第1LEDスタック423と第2LEDスタック433との間に介在してもよい。加えて、第2カラーフィルタ447は、第2LEDスタック433と第3LEDスタック443との間に介在してもよい。第1カラーフィルタ437は、第2LEDスタック433から発生する光を反射させながら、第1LEDスタック423から発生する光を透過させる。第2カラーフィルタ447は、第3LEDスタック443から発生する光を反射させながら、第1および第2LEDスタック423および433から発生する光を透過させる。結果として、第1LEDスタック423から発生する光は、第2LEDスタック433および第3LEDスタック443を介して外部に放出され、第2LEDスタック433から発生する光は、第3LEDスタック443を介して外部に放出される。また、発光ダイオードスタックは、第2LEDスタック433から発生する光が第1LEDスタック423に進入するのを防止することができるか、または第3LEDスタック443から発生する光が第2LEDスタック433に進入するのを防止することができ、それによって、光損失を防止する。

いくつかの例示的な実施例において、第1カラーフィルタ437は、第3LEDスタック443から発生する光を反射させることができる。

第1および第2カラーフィルタ437および447は、例えば、低周波数帯域で、すなわち、長波長帯域で、光のそれを介した通過を許容するローパスフィルタ、所定の波長帯域で光のそれを介した通過を許容するバンドパスフィルタ、または所定の波長帯域で光のそれを介した通過を防止するバンドストップフィルタであってもよい。特に、第1および第2カラーフィルタ437および447のそれぞれは、互いに異なる屈折率を有する絶縁層を互いに交互に積層することにより形成可能である。例えば、第1および第2カラーフィルタ437および447のそれぞれは、TiO2およびSiO2層、Ta2O5およびSiO2層、Nb2O5およびSiO2層、HfO2およびSiO2層、またはZrO2およびSiO2層を交互に積層することにより形成可能である。また、第1および/または第2カラーフィルタ437および447は、分布ブラッグ反射器(DBR)を含むことができる。分布ブラッグ反射器は、互いに異なる屈折率を有する絶縁層を交互に互いに積層することにより形成可能である。同時に、分布ブラッグ反射器の阻止帯域は、TiO2およびSiO2層の厚さを調節することにより制御可能である。

第1ボンディング層453は、第1LEDスタック423を支持基板451に結合する。図示のように、インターコネクションライン429は、第1ボンディング層453に隣接していてもよい。また、インターコネクションライン429は、その上に形成されるインターコネクションライン429を有しない第2絶縁層428の領域が第1ボンディング層453に隣接するように、第2絶縁層428のいくつかの領域の下に配置される。第1ボンディング層453は、光透過性であるか、不透明であってもよい。特に、光を吸収可能な黒色エポキシ樹脂で形成されるボンディング層が第1ボンディング層453として用いられ、それによって、ディスプレイ装置のコントラストを向上させる。

第2ボンディング層455は、第2LEDスタック433を第1LEDスタック423に結合する。図示のように、第2ボンディング層455は、第1LEDスタック423および第1カラーフィルタ437に隣接していてもよい。オーミック電極426は、第2ボンディング層455によって覆われてもよい。第2ボンディング層455は、第1LEDスタック423から発生する光を透過させる。第2ボンディング層455は、例えば、光透過性スピンオンガラス(spin−on−glass:SOG)で形成される。

第3ボンディング層457は、第3LEDスタック443を第2LEDスタック433に結合する。図示のように、第3ボンディング層457は、第2LEDスタック433および第2カラーフィルタ447に隣接していてもよい。しかし、本開示がこれに限定されるものではないことを理解しなければならない。例えば、透明導電層が第2LEDスタック433上に配置されてもよい。第3ボンディング層457は、第1LEDスタック423および第2LEDスタック433から発生する光を透過させる。第3ボンディング層457は、例えば、光透過性スピンオンガラスで形成される。

本例示的な実施例において、第1〜第3ボンディング層453、455および457は、SOGで形成される。しかし、本開示がこれに限定されるものではなく、第1〜第3ボンディング層が他の透明な有機または無機材料で形成できることを理解しなければならない。有機材料の例は、SU8、ポリ(メチルメタクリレート)(PMMA)、ポリイミド、パリレン、ベンゾシクロブテン(BCB)などを含むことができ、無機材料の例は、Al2O3、SiO2、SiNxなどを含むことができる。有機材料層は、高真空および高圧条件下でボンディングされてもよく、無機材料層は、例えば、無機材料層の表面を平坦化するための化学機械的研磨によりプラズマを用いて表面エネルギーを変化させた後、高真空条件下でボンディングされてもよい。

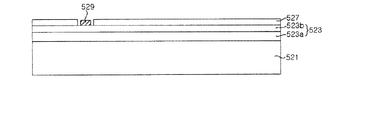

図52A、図52B、図52C、図52Dおよび図52Eは、本開示の1つの例示的な実施例によるディスプレイ用発光ダイオードスタックを製造する方法を示す概略断面図である。

図52Aを参照すると、まず、第1LEDスタック423が第1基板421上に成長する。第1基板421は、例えば、GaAs基板であってもよい。加えて、第1LEDスタック423は、AlGaInP系半導体層で構成され、第1導電型半導体層423aと、活性層と、第2導電型半導体層423bとを含む。

その後、第1導電型半導体層423aが、第2導電型半導体層423bを部分的に除去することにより露出する。単一ピクセル領域を示すが、第1導電型半導体層423aは、各ピクセル領域で部分的に露出する。

絶縁層427が第1LEDスタック423上に形成され、開口部を形成するようにパターニングが施される。例えば、SiO2層が第1LEDスタック423上に形成され、フォトレジストがSiO2層上に蒸着され、フォトレジストパターンを形成するようにフォトリソグラフィーおよび現像(development)が続く。その後、SiO2層がエッチングマスクとして用いられるフォトレジストパターンを介してパターニングが施され、それによって、絶縁層427を形成する。第1絶縁層427に形成される開口部のうちの1つは、第1導電型半導体層423a上に配置され、他の開口部は、第2導電型半導体層423b上に配置される。

その後、オーミック接触層425aおよびオーミック電極426が第1絶縁層427の開口部内に形成される。オーミック接触層425aおよびオーミック電極426は、リフトオフ工程により形成される。オーミック接触層425aは、オーミック電極426の形成前に形成されてもよいし、その逆も可能である。また、いくつかの例示的な実施例において、オーミック電極426およびオーミック接触層425aは、同一の材料層で同時に形成されてもよい。

オーミック接触層425aが形成された後に、反射層425bがオーミック接触層425aおよび第1絶縁層427を覆うように形成される。反射層425bは、リフトオフ工程により形成される。反射層425bは、図示のように、オーミック接触層425aの一部分またはその全体を覆うことができる。オーミック接触層425aおよび反射層425bは、反射電極425を形成する。

反射電極425は、第1LEDスタック423のp型半導体層とオーミック接触を形成し、そのため、第1−p反射電極425と称される。反射電極425は、オーミック電極426から分離され、そのため、第1導電型半導体層423aから電気的に絶縁される。

その後、第2絶縁層428が形成されて、反射電極425を覆い、オーミック電極426を露出させる開口部を有する。第2絶縁層428は、例えば、SiO2またはSOGで形成される。

一方、インターコネクションライン429が第2絶縁層428上に形成される。インターコネクションライン429は、第2絶縁層428の開口部を介してオーミック電極426に接続され、第1導電型半導体層423aに電気的に接続される。

インターコネクションライン429が第2絶縁層428の全体表面を覆うものとして図52Aに示されるが、インターコネクションライン429は、第2絶縁層428の上部表面がインターコネクションライン429の周囲で露出するように、第2絶縁層428上に部分的に配置されてもよい。

単一ピクセル領域を示すが、基板421上に配置される第1LEDスタック423は、複数のピクセル領域を覆うことができ、インターコネクションライン429は、複数の領域内に形成されるオーミック電極426に共通に接続されてもよい。また、複数のインターコネクションライン429が基板421上に形成されてもよい。

図52Bを参照すると、第2LEDスタック433が第2基板431上に成長し、第2−p透明電極435および第1カラーフィルタ437が第2LEDスタック433上に形成される。第2LEDスタック433は、GaN系の第1導電型半導体層433aと、第2導電型半導体層433bと、その間に介在し、GaInN井戸層を含む活性層とを含むことができる。第2基板431は、GaN系半導体層がその上に成長することを許容する基板であり、第1基板421とは異なる。第2LEDスタック433のためのGaInNの組成比は、第2LEDスタック433が緑色光を放出するように決定されてもよい。他方、第2−p透明電極435は、第2導電型半導体層433bとオーミック接触を形成する。

第1カラーフィルタ437が第2−p透明電極435上に形成される。第1カラーフィルタ437の細部事項は、図51を参照して説明したものと同一であり、繰り返しの説明は省略する。