JP2018502545A - 深い減光のための電源 - Google Patents

深い減光のための電源 Download PDFInfo

- Publication number

- JP2018502545A JP2018502545A JP2017533547A JP2017533547A JP2018502545A JP 2018502545 A JP2018502545 A JP 2018502545A JP 2017533547 A JP2017533547 A JP 2017533547A JP 2017533547 A JP2017533547 A JP 2017533547A JP 2018502545 A JP2018502545 A JP 2018502545A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- mode

- power supply

- power

- current signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B45/00—Circuit arrangements for operating light-emitting diodes [LED]

- H05B45/10—Controlling the intensity of the light

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B45/00—Circuit arrangements for operating light-emitting diodes [LED]

- H05B45/30—Driver circuits

- H05B45/37—Converter circuits

- H05B45/3725—Switched mode power supply [SMPS]

Abstract

Description

− 電源回路から第1電力量を受け取るための第1誘導回路と、

− 前記組み合わせに第2電力量を供給するための、前記第1誘導回路に結合される第2誘導回路と、

− 前記第2電力量を制御するための制御回路と、

− 前記制御回路を、時間間隔に等しい第1持続期間を持つ第1モードにするためのトリガ回路とを有し、前記制御回路は、前記第1モードにおいて、前記組み合わせに供給するために供給電流信号を案内し、その後、前記コンデンサ回路の電荷を減らすために放電電流信号を案内するよう構成され、前記制御回路の第2モードにおいて、前記放電電流信号が流れるのを防止するよう構成される。

− 電源回路から第1電力量を受け取るための第1誘導回路と、

− 前記組み合わせに第2電力量を供給するための、前記第1誘導回路に結合される第2誘導回路と、

− 前記第2電力量を制御するための制御回路とを有し、前記方法は、前記制御回路を、時間間隔に等しい第1持続期間を持つ第1モードにするステップを有し、前記制御回路は、前記第1モードにおいて、前記組み合わせに供給するために供給電流信号を案内し、その後、前記コンデンサ回路の電荷を減らすために放電電流信号を案内するよう構成され、前記制御回路の第2モードにおいて、前記放電電流信号が流れるのを防止するよう構成される。

Claims (15)

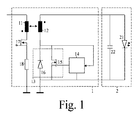

- 照明回路とコンデンサ回路との組み合わせに供給するための電源であって、前記電源が、

電源回路から第1電力量を受け取るための第1誘導回路と、

前記組み合わせに第2電力量を供給するための、前記第1誘導回路に結合される第2誘導回路と、

前記第2電力量を制御するための制御回路と、

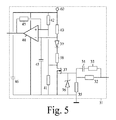

前記制御回路を、時間間隔に等しい第1持続期間を持つ第1モードにするためのトリガ回路とを有し、前記制御回路が、前記第1モードにおいて、前記組み合わせに供給するために供給電流信号を案内し、その後、前記コンデンサ回路の電荷を減らすために放電電流信号を案内するよう構成され、前記制御回路の第2モードにおいて、前記放電電流信号が流れるのを防止するよう構成される電源。 - 前記制御回路が、トランジスタとダイオードとの並列組み合わせを有する請求項1に記載の電源。

- 前記トランジスタが、電界効果トランジスタを有し、前記ダイオードが、前記電界効果トランジスタの寄生逆方向ダイオードを有する、又は前記トランジスタが、バイポーラトランジスタを有し、前記ダイオードが、逆方向ダイオードを有する請求項2に記載の電源。

- 前記第1モードが、前記トランジスタの導通モードを有し、前記第2モードが、前記トランジスタの非導通モードを有する請求項2に記載の電源。

- 前記時間間隔の長さが、実質的に固定された値を持つ請求項1に記載の電源。

- 前記第1電力量が、前記時間間隔より大きい周期を持つ電力パルスを有する請求項1に記載の電源。

- 前記トリガ回路が、電力パルスの端部の検出に応じて、前記制御回路を前記第1モードにするよう構成される請求項6に記載の電源。

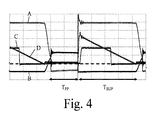

- 前記電源が、通常減光モードと、深い減光モードとを持つ請求項1に記載の電源。

- 前記制御回路が、前記深い減光モードにおいては、前記第1モードにおいて、前記供給電流信号を案内し、その後、前記放電電流信号を案内するよう構成され、前記第2モードにおいて、前記放電電流信号が流れるのを防止するよう構成され、前記制御回路が、前記通常減光モードにおいては、前記第1モードにおいて、前記供給電流信号だけを案内するよう構成され、前記第2モードにおいて、前記第2モードの第2持続期間の多くても一部の間、前記供給電流信号だけを案内するよう構成される請求項8に記載の電源。

- 前記第1電力量が、電力パルスを有し、前記電源が、しきい値より小さい電力パルス幅に応じて、前記深い減光モードに入るよう構成され、前記電源が、前記しきい値より大きい前記電力パルス幅に応じて、前記通常減光モードに入るよう構成される請求項8に記載の電源。

- 前記第1誘導回路が、第1巻線を有し、前記第2誘導回路が、第2巻線を有し、両巻線が、誘導結合される、又は各々の前記第1及び第2誘導回路が、同一巻線の各々の第1及び第2部分を有する請求項1に記載の電源。

- 前記トリガ回路が、前記第2誘導回路に存在する電圧信号を検出し、検出結果に応じて、前記制御回路を前記モードのうちの1つのモードにするための制御信号を生成するための集積回路を有する、又は前記トリガ回路が、前記第2誘導回路に存在する電圧信号を検出するための検出回路と、前記検出回路からの検出結果に応じて、前記制御回路を前記モードのうちの1つのモードにするための制御信号を生成するための生成回路とを有する請求項1に記載の電源。

- 請求項1に記載の電源を有し、前記照明回路と前記コンデンサ回路との前記組み合わせを更に有する装置。

- 前記照明回路が、発光ダイオード回路を有する請求項13に記載の装置。

- 照明回路とコンデンサ回路との組み合わせに供給するための電源を動作させるための方法であって、前記電源が、

電源回路から第1電力量を受け取るための第1誘導回路と、

前記組み合わせに第2電力量を供給するための、前記第1誘導回路に結合される第2誘導回路と、

前記第2電力量を制御するための制御回路とを有し、前記方法が、前記制御回路を、時間間隔に等しい第1持続期間を持つ第1モードにするステップを有し、前記制御回路が、前記第1モードにおいて、前記組み合わせに供給するために供給電流信号を案内し、その後、前記コンデンサ回路の電荷を減らすために放電電流信号を案内するよう構成され、前記制御回路の第2モードにおいて、前記放電電流信号が流れるのを防止するよう構成される方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP15150093.1 | 2015-01-05 | ||

| EP15150093 | 2015-01-05 | ||

| PCT/EP2015/080528 WO2016110396A1 (en) | 2015-01-05 | 2015-12-18 | Power supply for deep dimming light |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018502545A true JP2018502545A (ja) | 2018-01-25 |

| JP2018502545A5 JP2018502545A5 (ja) | 2019-01-10 |

Family

ID=52146408

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017533547A Pending JP2018502545A (ja) | 2015-01-05 | 2015-12-18 | 深い減光のための電源 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10237930B2 (ja) |

| EP (1) | EP3243362A1 (ja) |

| JP (1) | JP2018502545A (ja) |

| CN (1) | CN107113933A (ja) |

| WO (1) | WO2016110396A1 (ja) |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4051411A (en) * | 1976-09-02 | 1977-09-27 | General Electric Company | Discharge lamp operating circuit |

| DE2731373A1 (de) * | 1977-07-12 | 1979-02-01 | Bosch Gmbh Robert | Zuendeinrichtung fuer brennkraftmaschinen |

| JPH0832160B2 (ja) * | 1990-01-31 | 1996-03-27 | 三菱電機株式会社 | パルス電源装置 |

| FR2707051B1 (ja) * | 1993-06-10 | 1996-03-08 | Matsushita Electric Works Ltd | |

| US6175195B1 (en) * | 1997-04-10 | 2001-01-16 | Philips Electronics North America Corporation | Triac dimmable compact fluorescent lamp with dimming interface |

| US7327095B2 (en) | 2000-05-24 | 2008-02-05 | Mitsubishi Denki Kabushiki Kaisha | Discharge lamp lighting apparatus |

| CN100420136C (zh) * | 2003-09-30 | 2008-09-17 | 三垦电气株式会社 | 开关电源装置 |

| JP4126558B2 (ja) * | 2004-07-02 | 2008-07-30 | サンケン電気株式会社 | スイッチング電源装置 |

| JP4876521B2 (ja) * | 2005-10-13 | 2012-02-15 | ウシオ電機株式会社 | 放電ランプ点灯装置 |

| CA2775511A1 (en) * | 2009-09-28 | 2011-03-31 | Koninklijke Philips Electronics N.V. | Method and apparatus providing deep dimming of solid state lighting systems |

| US8611109B2 (en) | 2010-09-30 | 2013-12-17 | Infineon Technologies Ag | Flyback converter with an adaptively controlled rectifier arrangement |

| EP2538753A1 (en) * | 2011-06-21 | 2012-12-26 | Helvar Oy Ab | Driver device for LEDs, and a method for providing electric current to LEDs |

| US8570772B2 (en) | 2012-01-26 | 2013-10-29 | Linear Technology Corporation | Isolated flyback converter with efficient light load operation |

| US8873254B2 (en) | 2012-03-12 | 2014-10-28 | Linear Technology Corporation | Isolated flyback converter with sleep mode for light load operation |

| US9882497B2 (en) * | 2012-09-28 | 2018-01-30 | Microchip Technology Incorporated | Soft switching synchronous quasi resonant converter |

| RU2675793C2 (ru) * | 2014-01-17 | 2018-12-25 | Филипс Лайтинг Холдинг Б.В. | Драйвер светодиодов и способ управления |

| US9689536B2 (en) * | 2015-03-10 | 2017-06-27 | Jiaxing Super Lighting Electric Appliance Co., Ltd. | LED tube lamp |

-

2015

- 2015-12-18 CN CN201580072410.XA patent/CN107113933A/zh active Pending

- 2015-12-18 EP EP15813841.2A patent/EP3243362A1/en not_active Withdrawn

- 2015-12-18 WO PCT/EP2015/080528 patent/WO2016110396A1/en active Application Filing

- 2015-12-18 US US15/540,196 patent/US10237930B2/en not_active Expired - Fee Related

- 2015-12-18 JP JP2017533547A patent/JP2018502545A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US20170359870A1 (en) | 2017-12-14 |

| WO2016110396A1 (en) | 2016-07-14 |

| EP3243362A1 (en) | 2017-11-15 |

| US10237930B2 (en) | 2019-03-19 |

| CN107113933A (zh) | 2017-08-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9490716B2 (en) | Isolated converter with initial rising edge PWM delay | |

| US7638954B2 (en) | Light emitting diode drive apparatus | |

| US9504105B2 (en) | On-time control for switched mode power supplies | |

| KR20120019314A (ko) | 발광소자 구동 장치 | |

| JP6273894B2 (ja) | Led点灯装置及びled照明装置 | |

| JP5042536B2 (ja) | 電源装置及びこれを備えた電気機器 | |

| US9655175B2 (en) | Off-time control for switched mode power supplies | |

| JP2017225248A (ja) | 絶縁型のdc/dcコンバータ、それを用いた電源アダプタおよび電子機器 | |

| JP5408161B2 (ja) | 自励式スイッチング電源回路 | |

| US9608527B1 (en) | Overshoot prevention for deep dimming startup | |

| US9482724B2 (en) | Load detecting method and power supply device where the method is applied | |

| KR102197271B1 (ko) | 동기 정류기 구동 회로 및 이를 포함하는 전원 공급 장치 | |

| JP6171754B2 (ja) | Led点灯装置及びled照明装置 | |

| JP2018502545A (ja) | 深い減光のための電源 | |

| US20170324322A1 (en) | Supply voltage generating circuit and switching power supply | |

| JP6358526B2 (ja) | 点灯装置および、これを用いた照明器具 | |

| JP5129208B2 (ja) | スイッチング電源装置 | |

| JP2011244619A (ja) | スイッチング電源装置 | |

| JP6365162B2 (ja) | 電源装置および照明装置 | |

| JP2014155300A (ja) | 半導体照明用電源制御回路、半導体集積回路、および、半導体照明用電源 | |

| JP5280467B2 (ja) | 発光ダイオード駆動装置 | |

| JP6841134B2 (ja) | 点灯装置および照明器具 | |

| JP6035769B2 (ja) | 電源回路 | |

| KR101004521B1 (ko) | 스위칭 모드 전력 공급장치 | |

| KR101644296B1 (ko) | Led 구동용 주파수 제어 회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181120 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20181120 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20191001 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190927 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20200513 |