JP2018190793A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2018190793A JP2018190793A JP2017090394A JP2017090394A JP2018190793A JP 2018190793 A JP2018190793 A JP 2018190793A JP 2017090394 A JP2017090394 A JP 2017090394A JP 2017090394 A JP2017090394 A JP 2017090394A JP 2018190793 A JP2018190793 A JP 2018190793A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- semiconductor

- semiconductor substrate

- magnetic sensing

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N52/00—Hall-effect devices

- H10N52/101—Semiconductor Hall-effect devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N52/00—Hall-effect devices

- H10N52/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N52/00—Hall-effect devices

- H10N52/80—Constructional details

Abstract

Description

横型ホール素子は、例えば、半導体基板に設けられた磁気感受部と、該磁気感受部の表面に設けられた一対の入力電極と、一対の出力電極とを有して構成される。

すなわち、第一のウェル層の外側に設けられた第一のウェル層よりも濃度の低い第二のウェル層は、イオン注入等により半導体基板にN型の不純物を導入することにより形成されているため、第二のウェル層には、不純物の濃度分布が生じる。このように、第二のウェル層が濃度分布を有していると、第二のウェル層と半導体基板とのPN接合部に形成される空乏層は、第二のウェル層が濃度分布を有することの影響により、均一な厚さにはなり難い。このため、場所によっては、第一のウェル層内にまで空乏層が伸びてしまう可能性がある。結果的に、磁気感受部となる第一のウェル層が場所によって空乏層の影響を受けることになり、その抵抗値が変動し、特性ばらつきが生じることとなってしまう。

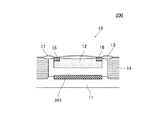

図1は、本発明の第一の実施形態による半導体装置100を説明するための図であり、図1(a)は、平面図、図1(b)は、図1(a)のA−A線に沿った断面図である。

なお、図1に示す半導体装置100と同一の構成要素には同一の符号を付し、重複する説明は適宜省略する。

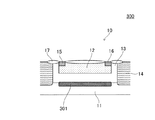

このように、半導体基板11よりも高濃度のP型の埋込層201を設けることにより、ホール素子10の下部に形成されるPN接合は、半導体基板11と半導体層13との間ではなく、P型の埋込層201とN型の半導体層13との間に形成される。

ここで、埋込層201は、例えば、半導体基板11の表面からP型不純物を導入し、その後、エピタキシャル成長により半導体層13を形成することにより形成される。

このように、半導体膜13よりも高濃度のN型の埋込層301を設けることにより、ホール素子10の下部に形成されるPN接合は、半導体基板11と半導体層13との間ではなく、P型の半導体基板11とN型の埋込層301との間に形成される。

ここで、埋込層301は、例えば、半導体基板11の表面からN型不純物を導入し、その後、エピタキシャル成長により半導体層13を形成することにより形成される。

P型の埋込層402は、P型の半導体基板11よりも高濃度であり、N型の埋込層403は、N型の半導体層13よりも高濃度である。

例えば、上記実施形態においては、第一導電型をP型、第二導電型をN型として説明したが、導電型を入れ替えて、第一導電型をN型、第二導電型をP型としても構わない。

11 P型半導体基板

12 N型磁気感受部

13 N型半導体層

14 素子分離拡散層

15、16、17、18 電極

100、200、300、400 半導体装置

201、402 P型埋込層

301、403 N型埋込層

401 埋込層

Claims (5)

- 第一導電型の半導体基板と、

前記半導体基板上に設けられたホール素子とを有する半導体装置であって、

前記ホール素子は、

前記半導体基板上に前記半導体基板と離間して設けられた第二導電型の磁気感受部と、

前記半導体基板上において、前記磁気感受部の側面および底面を囲むように設けられ、前記磁気感受部より低濃度かつ濃度分布が一定の第二導電型の半導体層とを備えることを特徴とする半導体装置。 - 前記磁気感受部の下部において、前記半導体基板と前記半導体層との間に設けられ、前記半導体基板よりも高濃度の第一導電型の埋込層をさらに備えることを特徴とする請求項1に記載の半導体装置。

- 前記磁気感受部の下部において、前記半導体基板と前記半導体層との間に設けられ、前記半導体層よりも高濃度の第二導電型の埋込層をさらに備えることを特徴とする請求項1に記載の半導体装置。

- 前記磁気感受部の下部において、前記半導体基板と前記半導体層との間に設けられた埋込層をさらに備え、

前記埋込層は、

前記半導体基板側に設けられ、前記半導体基板よりも高濃度の第一導電型の第一の埋込層と、

前記第一の埋込層の上面に接するように前記半導体層側に設けられ、前記半導体層よりも高濃度の第二導電型の第二の埋込層とを含むことを特徴とする請求項1に記載の半導体装置。 - 前記半導体層は、エピタキシャル層であることを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017090394A JP2018190793A (ja) | 2017-04-28 | 2017-04-28 | 半導体装置 |

| TW107112480A TW201840023A (zh) | 2017-04-28 | 2018-04-12 | 半導體裝置 |

| KR1020180045454A KR20180121369A (ko) | 2017-04-28 | 2018-04-19 | 반도체 장치 |

| US15/964,923 US20180315919A1 (en) | 2017-04-28 | 2018-04-27 | Semiconductor device |

| CN201810393464.1A CN108807659A (zh) | 2017-04-28 | 2018-04-27 | 半导体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017090394A JP2018190793A (ja) | 2017-04-28 | 2017-04-28 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018190793A true JP2018190793A (ja) | 2018-11-29 |

| JP2018190793A5 JP2018190793A5 (ja) | 2020-05-28 |

Family

ID=63916183

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017090394A Pending JP2018190793A (ja) | 2017-04-28 | 2017-04-28 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20180315919A1 (ja) |

| JP (1) | JP2018190793A (ja) |

| KR (1) | KR20180121369A (ja) |

| CN (1) | CN108807659A (ja) |

| TW (1) | TW201840023A (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10333056B2 (en) * | 2017-07-27 | 2019-06-25 | Globalfoundries Singapore Pte. Ltd. | Hall element for 3-D sensing and method for producing the same |

| JP7266386B2 (ja) * | 2018-11-09 | 2023-04-28 | エイブリック株式会社 | 半導体装置 |

| CN116113309B (zh) * | 2023-04-13 | 2023-07-25 | 南京邮电大学 | 一种采用双保护环的低失调霍尔器件及其使用方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005333103A (ja) * | 2004-03-30 | 2005-12-02 | Denso Corp | 縦型ホール素子およびその製造方法 |

| WO2006085503A1 (ja) * | 2005-02-08 | 2006-08-17 | Rohm Co., Ltd. | 磁気センサ回路、及び、その磁気センサ回路を有する携帯端末 |

| JP2016152271A (ja) * | 2015-02-16 | 2016-08-22 | エスアイアイ・セミコンダクタ株式会社 | 縦型ホール素子の製造方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CH668146A5 (de) * | 1985-05-22 | 1988-11-30 | Landis & Gyr Ag | Einrichtung mit einem hallelement in integrierter halbleitertechnologie. |

| JP4940965B2 (ja) * | 2007-01-29 | 2012-05-30 | 株式会社デンソー | 回転センサ及び回転センサ装置 |

| EP2234185B1 (en) * | 2009-03-24 | 2012-10-10 | austriamicrosystems AG | Vertical Hall sensor and method of producing a vertical Hall sensor |

| JP5815986B2 (ja) * | 2010-07-05 | 2015-11-17 | セイコーインスツル株式会社 | ホールセンサ |

| US9217783B2 (en) * | 2012-09-13 | 2015-12-22 | Infineon Technologies Ag | Hall effect device |

| KR102116147B1 (ko) * | 2014-03-06 | 2020-05-28 | 매그나칩 반도체 유한회사 | 매립형 마그네틱 센서 |

| DE102015204637A1 (de) * | 2015-03-13 | 2016-09-15 | Infineon Technologies Ag | Verfahren zum Dotieren eines aktiven Hall-Effekt-Gebiets einer Hall-Effekt-Vorrichtung und Hall-Effekt-Vorrichtung mit einem dotierten aktiven Hall-Effekt-Gebiet |

| US10109787B2 (en) * | 2016-10-27 | 2018-10-23 | Texas Instruments Incorporated | Well-based vertical hall element with enhanced magnetic sensitivity |

-

2017

- 2017-04-28 JP JP2017090394A patent/JP2018190793A/ja active Pending

-

2018

- 2018-04-12 TW TW107112480A patent/TW201840023A/zh unknown

- 2018-04-19 KR KR1020180045454A patent/KR20180121369A/ko unknown

- 2018-04-27 CN CN201810393464.1A patent/CN108807659A/zh not_active Withdrawn

- 2018-04-27 US US15/964,923 patent/US20180315919A1/en not_active Abandoned

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005333103A (ja) * | 2004-03-30 | 2005-12-02 | Denso Corp | 縦型ホール素子およびその製造方法 |

| WO2006085503A1 (ja) * | 2005-02-08 | 2006-08-17 | Rohm Co., Ltd. | 磁気センサ回路、及び、その磁気センサ回路を有する携帯端末 |

| JP2016152271A (ja) * | 2015-02-16 | 2016-08-22 | エスアイアイ・セミコンダクタ株式会社 | 縦型ホール素子の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20180121369A (ko) | 2018-11-07 |

| CN108807659A (zh) | 2018-11-13 |

| US20180315919A1 (en) | 2018-11-01 |

| TW201840023A (zh) | 2018-11-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6132032B2 (ja) | 半導体装置およびその製造方法 | |

| CN105633274B (zh) | 纵型霍尔元件 | |

| JP2018190793A (ja) | 半導体装置 | |

| JP2017174863A (ja) | 半導体装置 | |

| JP2014067986A (ja) | 半導体装置 | |

| TW201735187A (zh) | 半導體裝置 | |

| KR20160063262A (ko) | 종형 홀 소자 | |

| US10263176B2 (en) | Semiconductor device having vertical hall element | |

| JP2018117036A (ja) | 半導体装置 | |

| US10998492B2 (en) | Semiconductor device | |

| CN110945633A (zh) | 半导体装置 | |

| JP2019201097A (ja) | 半導体装置 | |

| JP2011082505A (ja) | ゲート−ソース容量を小さくするための交流4端子jfet幾何構造 | |

| JP6001309B2 (ja) | 半導体装置 | |

| TWI772556B (zh) | 暫態電壓抑制裝置、暫態電壓抑制裝置總成及其形成方法 | |

| JP2018206934A (ja) | 炭化ケイ素半導体装置およびその製造方法 | |

| JP2019040960A (ja) | 窒化物半導体装置 | |

| TW202306206A (zh) | 半導體裝置及其製造方法 | |

| JP2016162898A (ja) | 半導体装置 | |

| JP5069776B2 (ja) | 磁気検出装置 | |

| JP2016134480A (ja) | 半導体装置 | |

| JP6099956B2 (ja) | 半導体装置 | |

| JP2020092208A (ja) | トレンチゲート型半導体装置の製造方法 | |

| JP2018074106A (ja) | 半導体素子の製造方法、及び半導体素子を有するチップ | |

| US20150091104A1 (en) | Semiconductor structure and semiconductor device having the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200415 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200415 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210226 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210303 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20211005 |