JP2017520105A - Nir撮像素子のための深いウェルのフォトダイオード - Google Patents

Nir撮像素子のための深いウェルのフォトダイオード Download PDFInfo

- Publication number

- JP2017520105A JP2017520105A JP2016563172A JP2016563172A JP2017520105A JP 2017520105 A JP2017520105 A JP 2017520105A JP 2016563172 A JP2016563172 A JP 2016563172A JP 2016563172 A JP2016563172 A JP 2016563172A JP 2017520105 A JP2017520105 A JP 2017520105A

- Authority

- JP

- Japan

- Prior art keywords

- photodiode

- deep

- region

- photodiode region

- depletion

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/199—Back-illuminated image sensors

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/78—Readout circuits for addressed sensors, e.g. output amplifiers or A/D converters

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/011—Manufacture or treatment of image sensors covered by group H10F39/12

- H10F39/014—Manufacture or treatment of image sensors covered by group H10F39/12 of CMOS image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/18—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors

- H10F39/184—Infrared image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/802—Geometry or disposition of elements in pixels, e.g. address-lines or gate electrodes

- H10F39/8027—Geometry of the photosensitive area

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/803—Pixels having integrated switching, control, storage or amplification elements

- H10F39/8033—Photosensitive area

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/803—Pixels having integrated switching, control, storage or amplification elements

- H10F39/8037—Pixels having integrated switching, control, storage or amplification elements the integrated elements comprising a transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/807—Pixel isolation structures

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Light Receiving Elements (AREA)

Abstract

Description

図1は、例示的な撮像素子10を示す。撮像素子10は、半導体基板、例えば、以下でより詳細に説明するシリコン基板上に形成される。撮像素子10は、画素アレイ部11を含み、画素アレイ部11には、複数の画素110が、n行m列を有するn×m行列に配置される。画素アレイ部11は、有効画素領域、及びオプティカルブラック画素領域(図示せず)を含んでもよい。有効領域内の画素110は、撮像素子によって生成される画像のビット(ドット又は画素ともいう)に対応する、画素信号を出力するように構成される。一方、オプティカルブラック領域内の画素は、各種のノイズ除去技術のための基準として用いられる、黒レベル信号を出力するように構成される。オプティカルブラック領域内の画素は、それらが入射光から遮蔽されているという点を除いては、有効画素領域内の画素110と構造的には同じである。オプティカルブラック領域は、好ましくは、画素アレイ部11の1つ以上の縁に沿って、有効画素領域の周縁に位置する。画素アレイ部11は、各種の機能を実行するように構成されるが、出力画像内のビットには対応しない、ダミー画素も含んでもよい。以下、“画素110”という用語は、明示的に別段の指示がない限り、撮像素子によって生成される画像のビットに対応する画像信号を出力する画素をいう。各画素110は、光電変換機能を有する受光素子であるフォトダイオードと、以下で詳細に説明する、MOSトランジスタとを備える。

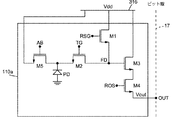

図3は、例示的なCMOSイメージセンサ画素110aを示す。図3は、いわゆる5T(five transistor)画素を示しているが、本開示は、この点について特に限定されない。例えば、例示的なCMOSイメージセンサ画素は、3T、4T、又は6T構成など、より多くの又はより少ないトランジスタを含んでもよい。さらに、コンデンサ及び/又は抵抗器を含む、他の能動回路素子又は受動回路素子が、本開示による画素に含まれてもよい。さらに、図3には示されていないが、各種のトランジスタが、隣接する画素間で共有されてもよい。

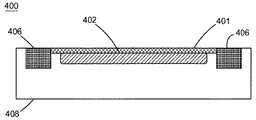

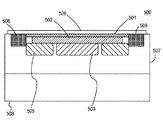

上述したように、本開示の画素110は、その全体構成に関わらず、入射光を電気信号に変換するように構成されるフォトダイオードを含む。本開示の態様の様々な利点は、フォトダイオードの構造に関係する。これらの利点を理解する助けとするために、比較例は、まず、フォトダイオードが本開示の態様のものとは異なる構造を有するものについて考えるものとする。

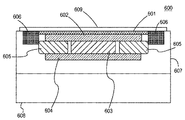

本開示の原理によれば、アクティブピクセル型CMOSイメージセンサは、改善された長波長の性能を示すフォトダイオードを実装する。例示的なフォトダイオードは、浅いフォトダイオード領域及び深いフォトダイオード領域を含む。例示的なフォトダイオードの全ての領域が、フォトダイオードリセット動作の間にキャリアを完全に空乏化される。即ち、中性領域は全く残らない。

好ましくは、深いフォトダイオード及び空乏インプラントは、製造プロセスの初期、即ち、ゲート酸化物の形成より前に実行される。この方法では、追加のサーマルバジェットは、フォトダイオードインプラントを深くすることの助けとなり、さらに、MTF性能を改善する。さらに、この方法では、インプラント障害は、よりよく防止され、及び/又はアニールアウトされ得る。あるいは、深いフォトダイオード及び/又は深い空乏インプラントのいずれかが、ゲート形成の後に行われ得る。この方法では、よりはっきりしたp−n接合が実現される可能性があるが、インプラントは深く拡散されない可能性があり、それによって、NIR改善がより小さくなる。

電子機器は、上述した撮像素子10を含むように構成され得る。例えば、電子機器は、デジタルカメラ(静止画を撮るように構成されるカメラ、及び動画を撮るように構成されるカメラの両方を含む)、携帯電話、スマートフォン、タブレット装置、携帯情報端末(PDA:personal digital assistant)、ラップトップコンピュータ、デスクトップコンピュータ、ウェブカメラ、望遠鏡、科学実験用センサ、並びに、光を検知し、及び/又は画像をキャプチャするのに有利であり得る任意の電子機器を含み得る。

Claims (21)

- フォトダイオード領域が、浅いフォトダイオード領域及び第1の深いフォトダイオード領域を含み、前記浅いフォトダイオード領域の長さが、前記第1の深いフォトダイオード領域の長さよりも長い、第1のドーパント型のフォトダイオード領域と、

空乏領域が、浅い空乏領域及び深い空乏領域を含み、前記深い空乏領域が、少なくとも2つの対称側において前記第1の深いフォトダイオード領域を取り囲む、第2のドーパント型の空乏領域と、を備え、

前記第2のドーパント型は、前記第1のドーパント型と反対のドーパント型である、撮像装置。 - 前記フォトダイオード領域の全体は、フォトダイオードリセットの間に、キャリアが完全に空乏化されるように構成される、請求項1に記載の撮像装置。

- 前記第1の深いフォトダイオード領域の深さは、前記深い空乏領域の深さと実質的に等しい、請求項1に記載の撮像装置。

- 前記フォトダイオード領域は、第2の深いフォトダイオード領域をさらに含み、前記第2の深いフォトダイオード領域の長さは、前記第1の深いフォトダイオード領域の前記長さよりも長い、請求項1に記載の撮像装置。

- 前記第2の深いフォトダイオード領域は、前記深い空乏領域よりも深い、請求項4に記載の撮像装置。

- ゲート酸化物層をさらに備える、請求項1に記載の撮像装置。

- 前記第1の深いフォトダイオード領域及び前記深い空乏領域は、前記ゲート酸化物層より前に形成される、請求項6に記載の撮像装置。

- 前記フォトダイオード領域は、前記ゲート酸化物層より前に形成され、前記空乏領域は、前記ゲート酸化物層より後に形成される、請求項6に記載の撮像装置。

- 前記空乏領域は、前記ゲート酸化物層より前に形成され、前記フォトダイオード領域は、前記ゲート酸化物層より後に形成される、請求項6に記載の撮像装置。

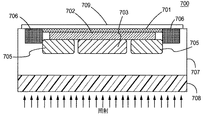

- 前記撮像装置は、裏面照射型撮像装置として構成される、請求項1に記載の撮像装置。

- 光学系と、

前記光学系から入射光を受光するように構成される撮像装置であって、前記撮像装置は、請求項1に記載の撮像装置である撮像装置と、

前記撮像装置から信号を受信し、データを出力するように構成される、信号プロセッサと、

を備える電子機器。 - フォトダイオード領域が、浅いフォトダイオード領域及び第1の深いフォトダイオード領域を含み、前記浅いフォトダイオード領域の長さが、前記第1の深いフォトダイオード領域の長さよりも長い、第1のドーパント型のフォトダイオード領域を形成することと、

空乏領域が、浅い空乏領域及び深い空乏領域を含み、前記深い空乏領域が、少なくとも2つの対称側において前記第1の深いフォトダイオード領域を取り囲む、第2のドーパント型の空乏領域を形成することと、を含み、

前記第2のドーパント型は、前記第1のドーパント型と反対のドーパント型である、撮像装置の製造方法。 - 前記フォトダイオード領域の全体は、フォトダイオードリセットの間に、キャリアが完全に空乏化されるように構成される、請求項12に記載の撮像装置の製造方法。

- 前記第1の深いフォトダイオード領域の深さは、前記深い空乏領域の深さと実質的に等しい、請求項12に記載の撮像装置の製造方法。

- 前記フォトダイオード領域は、第2の深いフォトダイオード領域をさらに含み、前記第2の深いフォトダイオード領域の長さは、前記第1の深いフォトダイオード領域の前記長さよりも長い、請求項12に記載の撮像装置の製造方法。

- 前記第2の深いフォトダイオード領域は、前記深い空乏領域よりも深い、請求項15に記載の撮像装置の製造方法。

- ゲート酸化物層を形成することをさらに含む、請求項12に記載の撮像装置の製造方法。

- 前記ゲート酸化物層を形成する前に、前記第1の深いフォトダイオード領域及び前記深い空乏領域を形成することをさらに含む、請求項17に記載の撮像装置の製造方法。

- 前記ゲート酸化物層を形成する前に、前記フォトダイオード領域を形成することと、前記ゲート酸化物層を形成した後に、前記空乏領域を形成することと、をさらに含む、請求項17に記載の撮像装置の製造方法。

- 前記ゲート酸化物層を形成する前に、前記空乏領域を形成することと、前記ゲート酸化物層を形成した後に、前記フォトダイオード領域を形成することと、をさらに含む、請求項17に記載の撮像装置の製造方法。

- 前記撮像装置は、裏面照射型撮像装置として構成される、請求項12に記載の撮像装置の製造方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/263,630 | 2014-04-28 | ||

| US14/263,630 US20150311240A1 (en) | 2014-04-28 | 2014-04-28 | Deep well photodiode for nir image sensor |

| PCT/US2015/023107 WO2015167723A1 (en) | 2014-04-28 | 2015-03-27 | Deep well photodiode for nir image sensor |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017520105A true JP2017520105A (ja) | 2017-07-20 |

| JP2017520105A5 JP2017520105A5 (ja) | 2018-04-19 |

Family

ID=54335506

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016563172A Pending JP2017520105A (ja) | 2014-04-28 | 2015-03-27 | Nir撮像素子のための深いウェルのフォトダイオード |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20150311240A1 (ja) |

| JP (1) | JP2017520105A (ja) |

| WO (1) | WO2015167723A1 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9930281B2 (en) | 2016-01-20 | 2018-03-27 | Semiconductor Components Industries, Llc | Image sensors having photodiode regions implanted from multiple sides of a substrate |

| KR20220072257A (ko) | 2020-11-25 | 2022-06-02 | 에스케이하이닉스 주식회사 | 이미지 센싱 장치 |

Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000031525A (ja) * | 1998-06-27 | 2000-01-28 | Hyundai Electron Ind Co Ltd | イメ―ジセンサのピンドフォトダイオ―ド及びその製造方法 |

| JP2001291858A (ja) * | 2000-04-04 | 2001-10-19 | Sony Corp | 固体撮像素子及びその製造方法 |

| JP2003282857A (ja) * | 2001-11-16 | 2003-10-03 | Hynix Semiconductor Inc | イメージセンサおよびその製造方法 |

| JP2004165589A (ja) * | 2002-11-14 | 2004-06-10 | Hynix Semiconductor Inc | Cmosイメージセンサ及びその製造方法 |

| JP2006073682A (ja) * | 2004-08-31 | 2006-03-16 | Sony Corp | 固体撮像素子、カメラモジュール及び電子機器モジュール |

| JP2006526290A (ja) * | 2003-03-28 | 2006-11-16 | マイクロン テクノロジー インコーポレイテッド | Cmosaps用のダブルピンフォトダイオードおよびその形成方法 |

| US20080217723A1 (en) * | 2007-03-08 | 2008-09-11 | Teledyne Licensing, Llc | Backside illuminated cmos image sensor with pinned photodiode |

| JP2009038309A (ja) * | 2007-08-03 | 2009-02-19 | Sharp Corp | 固体撮像素子およびその製造方法、電子情報機器 |

| US20090173975A1 (en) * | 2003-06-16 | 2009-07-09 | Rhodes Howard E | Well for cmos imager and method of formation |

| US20100109060A1 (en) * | 2008-11-06 | 2010-05-06 | Omnivision Technologies Inc. | Image sensor with backside photodiode implant |

| US20110249158A1 (en) * | 2010-04-13 | 2011-10-13 | Jaroslav Hynecek | Image sensor pixels with vertical charge transfer |

| US20140084409A1 (en) * | 2012-09-25 | 2014-03-27 | Aptina Imaging Corporation | Image sensors with in-pixel anti-blooming drains |

-

2014

- 2014-04-28 US US14/263,630 patent/US20150311240A1/en not_active Abandoned

-

2015

- 2015-03-27 JP JP2016563172A patent/JP2017520105A/ja active Pending

- 2015-03-27 WO PCT/US2015/023107 patent/WO2015167723A1/en not_active Ceased

Patent Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000031525A (ja) * | 1998-06-27 | 2000-01-28 | Hyundai Electron Ind Co Ltd | イメ―ジセンサのピンドフォトダイオ―ド及びその製造方法 |

| JP2001291858A (ja) * | 2000-04-04 | 2001-10-19 | Sony Corp | 固体撮像素子及びその製造方法 |

| JP2003282857A (ja) * | 2001-11-16 | 2003-10-03 | Hynix Semiconductor Inc | イメージセンサおよびその製造方法 |

| JP2004165589A (ja) * | 2002-11-14 | 2004-06-10 | Hynix Semiconductor Inc | Cmosイメージセンサ及びその製造方法 |

| JP2006526290A (ja) * | 2003-03-28 | 2006-11-16 | マイクロン テクノロジー インコーポレイテッド | Cmosaps用のダブルピンフォトダイオードおよびその形成方法 |

| US20090173975A1 (en) * | 2003-06-16 | 2009-07-09 | Rhodes Howard E | Well for cmos imager and method of formation |

| JP2006073682A (ja) * | 2004-08-31 | 2006-03-16 | Sony Corp | 固体撮像素子、カメラモジュール及び電子機器モジュール |

| US20080217723A1 (en) * | 2007-03-08 | 2008-09-11 | Teledyne Licensing, Llc | Backside illuminated cmos image sensor with pinned photodiode |

| JP2009038309A (ja) * | 2007-08-03 | 2009-02-19 | Sharp Corp | 固体撮像素子およびその製造方法、電子情報機器 |

| US20100109060A1 (en) * | 2008-11-06 | 2010-05-06 | Omnivision Technologies Inc. | Image sensor with backside photodiode implant |

| US20110249158A1 (en) * | 2010-04-13 | 2011-10-13 | Jaroslav Hynecek | Image sensor pixels with vertical charge transfer |

| US20140084409A1 (en) * | 2012-09-25 | 2014-03-27 | Aptina Imaging Corporation | Image sensors with in-pixel anti-blooming drains |

Also Published As

| Publication number | Publication date |

|---|---|

| US20150311240A1 (en) | 2015-10-29 |

| WO2015167723A1 (en) | 2015-11-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101939982B (zh) | 具有全域快门及储存电容器的背侧照明图像传感器 | |

| CN101312205B (zh) | 固态成像装置及照相机 | |

| KR102499590B1 (ko) | 고체 촬상 소자 및 그 제조 방법, 및 전자 기기 | |

| KR101466845B1 (ko) | 고체 촬상 장치 및 카메라 | |

| US9312299B2 (en) | Image sensor with dielectric charge trapping device | |

| US20160276380A1 (en) | Photosensitive capacitor pixel for image sensor | |

| TWI532158B (zh) | 具改良效能之大型互補金屬氧化物半導體影像感測器像素 | |

| JP2017519352A (ja) | フローティングディフュージョン・インターコネクト・キャパシタを有する撮像素子 | |

| CN104037180A (zh) | 具有带有单一植入的多个光电二极管的高动态范围像素 | |

| US9967504B1 (en) | Imaging sensor with boosted photodiode drive | |

| JP2014225536A (ja) | 固体撮像装置及びカメラ | |

| JP2015023250A (ja) | 固体撮像素子及びその駆動方法、並びに電子機器 | |

| US20190333958A1 (en) | Pixel circuit | |

| Takase et al. | First demonstration of 0.9 μm pixel global shutter operation by novel charge control in organic photoconductive film | |

| US9761624B2 (en) | Pixels for high performance image sensor | |

| JP5167693B2 (ja) | 固体撮像装置およびカメラ | |

| JP2016063142A (ja) | 半導体装置 | |

| US20160099283A1 (en) | Photosensor with channel region having center contact | |

| JP7126826B2 (ja) | 固体撮像素子および固体撮像素子の製造方法、並びに電子機器 | |

| JP2017520105A (ja) | Nir撮像素子のための深いウェルのフォトダイオード | |

| JP7198675B2 (ja) | 固体撮像素子、その駆動回路および撮像装置 | |

| US10477126B1 (en) | Dual eclipse circuit for reduced image sensor shading | |

| US20200099878A1 (en) | Cmos image sensor with multiple stage transfer gate | |

| HK1212818B (en) | Image sensor pixel and image sensor | |

| JP2020038910A (ja) | 固体撮像素子および電子装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180309 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180309 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190521 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190821 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20200116 |