JP2015182158A - Memsデバイス - Google Patents

Memsデバイス Download PDFInfo

- Publication number

- JP2015182158A JP2015182158A JP2014059445A JP2014059445A JP2015182158A JP 2015182158 A JP2015182158 A JP 2015182158A JP 2014059445 A JP2014059445 A JP 2014059445A JP 2014059445 A JP2014059445 A JP 2014059445A JP 2015182158 A JP2015182158 A JP 2015182158A

- Authority

- JP

- Japan

- Prior art keywords

- cavity

- semiconductor substrate

- lid

- trench

- mems device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C1/00—Manufacture or treatment of devices or systems in or on a substrate

- B81C1/00015—Manufacture or treatment of devices or systems in or on a substrate for manufacturing microsystems

- B81C1/00222—Integrating an electronic processing unit with a micromechanical structure

- B81C1/00246—Monolithic integration, i.e. micromechanical structure and electronic processing unit are integrated on the same substrate

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81B—MICROSTRUCTURAL DEVICES OR SYSTEMS, e.g. MICROMECHANICAL DEVICES

- B81B2201/00—Specific applications of microelectromechanical systems

- B81B2201/02—Sensors

- B81B2201/0271—Resonators; ultrasonic resonators

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C2203/00—Forming microstructural systems

- B81C2203/01—Packaging MEMS

- B81C2203/0136—Growing or depositing of a covering layer

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C2203/00—Forming microstructural systems

- B81C2203/01—Packaging MEMS

- B81C2203/0163—Reinforcing a cap, e.g. with ribs

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B81—MICROSTRUCTURAL TECHNOLOGY

- B81C—PROCESSES OR APPARATUS SPECIALLY ADAPTED FOR THE MANUFACTURE OR TREATMENT OF MICROSTRUCTURAL DEVICES OR SYSTEMS

- B81C2203/00—Forming microstructural systems

- B81C2203/07—Integrating an electronic processing unit with a micromechanical structure

- B81C2203/0707—Monolithic integration, i.e. the electronic processing unit is formed on or in the same substrate as the micromechanical structure

- B81C2203/0757—Topology for facilitating the monolithic integration

- B81C2203/0764—Forming the micromechanical structure in a groove

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Micromachines (AREA)

- Computer Hardware Design (AREA)

- Piezo-Electric Or Mechanical Vibrators, Or Delay Or Filter Circuits (AREA)

Abstract

【解決手段】このMEMSデバイスは、主面の第1の領域にトレンチが形成されると共に、主面の第2の領域に半導体回路素子の不純物拡散領域が形成された半導体基板と、半導体基板のトレンチの底面に直接又は絶縁膜を介して設けられた機能素子と、半導体基板のトレンチ内に設けられ、機能素子の周囲にキャビティーを形成する壁部と、キャビティーを覆う蓋部と、キャビティー内に設けられ、半導体基板のトレンチの底面又は絶縁膜と蓋部の裏面とに接する支柱とを備える。

【選択図】図1

Description

本発明の各実施形態に係るMEMSデバイスは、レゾネーター、センサー、アクチュエーター等の機能素子、及び、電子回路を1つの基板に集積化したデバイスである。

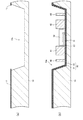

図1は、本発明の第1の実施形態に係るMEMSデバイスのトレンチ内の構造を示す平面図である。図1は、キャビティーが蓋部で覆われる前のトレンチ内の構造を示している。また、図2は、図1のA−A'線におけるMEMSデバイスの主要部を示す断面図である。図2に示すように、このMEMSデバイスにおいては、主面(図中上面)の第1の領域(図中右側)にトレンチ10aが形成されると共に、主面の第2の領域(図中左側)に半導体回路素子の不純物拡散領域が形成された半導体基板10が用いられる。

図3及び図4は、本発明の第1の実施形態に係るMEMSデバイスの製造工程における断面図である。まず、図3(a)に示すように、例えば、シリコン単結晶等で構成された半導体基板10の主面の一部に、フォトリソグラフィー法によってレジスト11を設けてドライエッチングを行うことにより、半導体基板10の主面の第1の領域に深いトレンチ(ディープトレンチ)10aが形成される。その後、レジスト11が除去される。

図5は、本発明の第2の実施形態に係るMEMSデバイスのトレンチ内の構造を示す平面図である。図5は、キャビティーが蓋部で覆われる前のトレンチ内の構造を示している。また、図6は、図5のB−B'線におけるMEMSデバイスの主要部を示す断面図である。第2の実施形態においては、機能素子の少なくとも一部が支柱を構成している。その他の点に関しては、第2の実施形態は、第1の実施形態と同様である。

Claims (8)

- 主面の第1の領域にトレンチが形成されると共に、主面の第2の領域に半導体回路素子の不純物拡散領域が形成された半導体基板と、

前記半導体基板のトレンチの底面に直接又は絶縁膜を介して設けられた機能素子と、

前記半導体基板のトレンチ内に設けられ、前記機能素子の周囲にキャビティーを形成する壁部と、

前記キャビティーを覆う蓋部と、

前記キャビティー内に設けられ、前記半導体基板のトレンチの底面又は前記絶縁膜と前記蓋部の裏面とに接する支柱と、

を備えるMEMSデバイス。 - 前記蓋部及び前記半導体回路素子が設けられた前記半導体基板の主面を覆う絶縁層をさらに備える、請求項1記載のMEMSデバイス。

- 前記蓋部上の前記絶縁層の表面が、CMP(化学機械研磨)によって加工されている、請求項2記載のMEMSデバイス。

- 前記支柱が、前記蓋部の裏面の中央部に接する、請求項1〜3のいずれか1項記載のMEMSデバイス。

- 前記機能素子の少なくとも一部が、前記支柱を構成する、請求項1〜4のいずれか1項記載のMEMSデバイス。

- 前記支柱が、前記壁部と一体的に構成されている、請求項1〜3記載のMEMSデバイス。

- 前記支柱が、前記機能素子と前記壁部との間の中央部に設けられている、請求項1〜3のいずれか1項記載のMEMSデバイス。

- 前記支柱が、前記機能素子に電気的に接続された外部接続電極を兼ねる、請求項1〜7のいずれか1項記載のMEMSデバイス。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014059445A JP2015182158A (ja) | 2014-03-24 | 2014-03-24 | Memsデバイス |

| US14/660,157 US9434607B2 (en) | 2014-03-24 | 2015-03-17 | MEMS device |

| CN201510129061.2A CN104944356A (zh) | 2014-03-24 | 2015-03-23 | 微机电系统装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014059445A JP2015182158A (ja) | 2014-03-24 | 2014-03-24 | Memsデバイス |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015182158A true JP2015182158A (ja) | 2015-10-22 |

| JP2015182158A5 JP2015182158A5 (ja) | 2017-03-16 |

Family

ID=54141419

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014059445A Withdrawn JP2015182158A (ja) | 2014-03-24 | 2014-03-24 | Memsデバイス |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9434607B2 (ja) |

| JP (1) | JP2015182158A (ja) |

| CN (1) | CN104944356A (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9868628B2 (en) * | 2016-03-10 | 2018-01-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method and structure for CMOS-MEMS thin film encapsulation |

| US10199424B1 (en) * | 2017-07-19 | 2019-02-05 | Meridian Innovation Pte Ltd | Thermoelectric-based infrared detector having a cavity and a MEMS structure defined by BEOL metals lines |

| US10319680B1 (en) | 2018-03-01 | 2019-06-11 | Sandisk Technologies Llc | Metal contact via structure surrounded by an air gap and method of making thereof |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5798283A (en) * | 1995-09-06 | 1998-08-25 | Sandia Corporation | Method for integrating microelectromechanical devices with electronic circuitry |

| JP2003530233A (ja) * | 2000-04-11 | 2003-10-14 | ローベルト ボツシユ ゲゼルシヤフト ミツト ベシユレンクテル ハフツング | マイクロメカニカル構成素子及び相応する製造法 |

| JP2007203420A (ja) * | 2006-02-03 | 2007-08-16 | Hitachi Ltd | Mems構造体およびその製造方法、並びにmems構造体混載半導体装置の製造方法 |

| JP2007210083A (ja) * | 2006-02-13 | 2007-08-23 | Hitachi Ltd | Mems素子及びその製造方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6012336A (en) * | 1995-09-06 | 2000-01-11 | Sandia Corporation | Capacitance pressure sensor |

| US5963788A (en) * | 1995-09-06 | 1999-10-05 | Sandia Corporation | Method for integrating microelectromechanical devices with electronic circuitry |

| JP2006289520A (ja) * | 2005-04-06 | 2006-10-26 | Toshiba Corp | Mems技術を使用した半導体装置 |

| US7417307B2 (en) * | 2005-07-29 | 2008-08-26 | Hewlett-Packard Development Company, L.P. | System and method for direct-bonding of substrates |

| JPWO2008023826A1 (ja) | 2006-08-25 | 2010-01-14 | 三洋電機株式会社 | 半導体装置及びその製造方法 |

| JP5040021B2 (ja) | 2007-08-31 | 2012-10-03 | セイコーインスツル株式会社 | 気密パッケージ及び気密パッケージの製造方法 |

| CN102449906B (zh) | 2010-03-18 | 2014-10-01 | 松下电器产业株式会社 | Mems元件以及mems元件的制造方法 |

| JP2012096316A (ja) * | 2010-11-02 | 2012-05-24 | Seiko Epson Corp | 電子装置および電子装置の製造方法 |

| CN102333254B (zh) * | 2011-09-13 | 2013-11-06 | 华景传感科技(无锡)有限公司 | 一种与cmos电路纵向集成的mems硅麦克风及其制备方法 |

| WO2013097135A1 (en) * | 2011-12-29 | 2013-07-04 | Goertek Inc. | A silicon based mems microphone, a system and a package with the same |

| CN103248994A (zh) * | 2012-02-06 | 2013-08-14 | 苏州敏芯微电子技术有限公司 | 集成电路与电容式微硅麦克风单片集成的制作方法及芯片 |

| CN103373698B (zh) * | 2012-04-26 | 2015-09-16 | 张家港丽恒光微电子科技有限公司 | 制作mems惯性传感器的方法及mems惯性传感器 |

| JP6314568B2 (ja) * | 2014-03-18 | 2018-04-25 | セイコーエプソン株式会社 | Memsデバイス及びその製造方法 |

-

2014

- 2014-03-24 JP JP2014059445A patent/JP2015182158A/ja not_active Withdrawn

-

2015

- 2015-03-17 US US14/660,157 patent/US9434607B2/en active Active

- 2015-03-23 CN CN201510129061.2A patent/CN104944356A/zh active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5798283A (en) * | 1995-09-06 | 1998-08-25 | Sandia Corporation | Method for integrating microelectromechanical devices with electronic circuitry |

| JP2003530233A (ja) * | 2000-04-11 | 2003-10-14 | ローベルト ボツシユ ゲゼルシヤフト ミツト ベシユレンクテル ハフツング | マイクロメカニカル構成素子及び相応する製造法 |

| JP2007203420A (ja) * | 2006-02-03 | 2007-08-16 | Hitachi Ltd | Mems構造体およびその製造方法、並びにmems構造体混載半導体装置の製造方法 |

| JP2007210083A (ja) * | 2006-02-13 | 2007-08-23 | Hitachi Ltd | Mems素子及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US9434607B2 (en) | 2016-09-06 |

| CN104944356A (zh) | 2015-09-30 |

| US20150266721A1 (en) | 2015-09-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10486964B2 (en) | Method for forming a micro-electro mechanical system (MEMS) including bonding a MEMS substrate to a CMOS substrate via a blocking layer | |

| TWI629460B (zh) | MEMS pressure sensor and method of forming same | |

| US5760455A (en) | Micromechanical semiconductor component and manufacturing method therefor | |

| US8513041B2 (en) | MEMS integrated chip and method for making same | |

| TWI621242B (zh) | 具有紅外線吸收結構層的氮化鋁(ain)裝置 | |

| US10202275B2 (en) | Process for manufacturing a semiconductor device including a microelectromechanical structure and an associated integrated electronic circuit and corresponding semiconductor device | |

| US10494252B2 (en) | MEMS devices and methods of manufacturing the same | |

| JP2015182158A (ja) | Memsデバイス | |

| US9499394B2 (en) | MEMS device and method of manufacturing the same | |

| KR20140118771A (ko) | 전자 장치 및 그의 제조 방법, 그리고 발진기 | |

| CN104051385A (zh) | 堆叠式半导体结构及其形成方法 | |

| JP6314568B2 (ja) | Memsデバイス及びその製造方法 | |

| JP6331551B2 (ja) | Memsデバイス | |

| US9365411B2 (en) | MEMS device and method for manufacturing the same | |

| US9388039B2 (en) | MEMS device and method of manufacturing the same | |

| TWI632358B (zh) | 電容式壓力感測器及方法 | |

| US11027967B2 (en) | Deformable membrane and a compensating structure thereof | |

| JP6269113B2 (ja) | Mems素子及びその製造方法 | |

| JP2015145037A (ja) | Mems素子及びその製造方法 | |

| JP2015145036A (ja) | Mems素子及びその製造方法 | |

| JP2009105277A (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170210 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170210 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180124 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180130 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20180307 |