JP2014104248A - 半導体回路及び該半導体回路を備える生体組織刺激装置 - Google Patents

半導体回路及び該半導体回路を備える生体組織刺激装置 Download PDFInfo

- Publication number

- JP2014104248A JP2014104248A JP2012260786A JP2012260786A JP2014104248A JP 2014104248 A JP2014104248 A JP 2014104248A JP 2012260786 A JP2012260786 A JP 2012260786A JP 2012260786 A JP2012260786 A JP 2012260786A JP 2014104248 A JP2014104248 A JP 2014104248A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- current

- voltage transistor

- breakdown voltage

- low breakdown

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

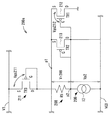

【解決手段】 半導体回路は、第1電源ラインと第1接地ラインを持つ第1回路の第1レベルの信号を,第2電源ラインと第2接地ラインを持つ第2回路の第2レベルの信号に変換するレベルシフト回路は、第1電源ラインに接続されて電流を出力する第1電流源と、第1レベルの信号に基づく導通と非導通の切り換えによって、第1電流源からの電流の出力の有無を切り換える高耐圧トランジスタと、電流を電圧に変換して前記第2レベルの信号を得る電流電圧変換手段と、電流電圧変換手段で変換される電圧が第2電源ラインの電圧以下となるように,高耐圧トランジスタを介して供給された電流を調整する第1低耐圧トランジスタからなるクランプ回路とを持つ。

【選択図】 図1

Description

しかし回路が電気的に切り離されると、切り離された回路の電位がフローティングとなり変動しうる。切り離された回路の電位が上昇すると回路の破損につながる。一方、生体組織刺激装置のように、フローティングによる電位変動の程度を予測することが困難な装置では、図7の従来技術に示されるように、回路の電位変動に十分に耐え得る耐圧を確保するため、複数の大型の高耐圧トランジスタを用いてレベルシフト回路が構成されている。しかし生体組織刺激装置のように、装置(回路)が置かれるスペースが限られている場合、大型の高耐圧トランジスタの組み合わせで構成されたレベルシフト回路を用いることは、装置の小型化に不利になる課題がある。

(2) 前記クランプ回路において、前記第1低耐圧トランジスタは、前記高耐圧のトランジスタと同極性であって、前記第1低耐圧トランジスタの第1ソースは前記高耐圧トランジスタのドレインに接続され,前記第1低耐圧トランジスタの第1ドレインは前記電流電圧変換手段に接続され、前記第1低耐圧トランジスタの前記第1ドレインから出力された電流が前記電流電圧変換手段で電圧に変換される(1)に記載の半導体回路。

(3) 前記クランプ回路は、前記第1低耐圧トランジスタと同極性の第2低耐圧トランジスタであって、前記第1ソースと前記第2低耐圧トランジスタの第2ソースを接続し,前記第2低耐圧トランジスタの第2ドレインを前記第2接地ラインに接続することで、前記第1電流源から供給される電流のうち前記第1低耐圧トランジスタへの流入量を超えた電流を流入させる前記第2低耐圧トランジスタと、を備える(2)に記載の半導体回路。

(4) 前記クランプ回路は、前記第2接地ラインに接続される第2電流源と、前記第1低耐圧トランジスタと同極性であって、第3ソースが前記第2電源ラインに接続され、第3ゲートならびに第3ドレインが共通に接続された第3低耐圧トランジスタと、前記第2電源ラインより前記クランプ回路の電位を低くする電位下降手段であって,一端が前記第3低耐圧トランジスタの前記第3ゲートと第3ドレインの共通接続点に接続され,他端が前記第2電流源に接続される電位下降手段と、を備える(3)に記載の半導体回路。

(5) 前記第1回路と前記第2回路の接続と非接続を切り換えるスイッチ手段を備え、前記レベルシフト回路は、前記スイッチ手段で前記第1回路と前記第2回路が接続されたときに,前記第1レベルの信号を前記第2レベルの信号に変換する(1)〜(4)のいずれかに記載の半導体回路。

(6) 前記第1接地ラインと前記第2接地ラインの電位は、前記スイッチ手段で前記第1回路と前記第2回路が接続されたときに等しくなる(1)〜(5)のいずれかに記載の半導体回路。

(7) 前記半導体回路は、前記第1レベルの信号がオンの時に前記高耐圧トランジスタを導通させて前記電流を前記クランプ回路に流入させ、前記第1レベルの信号がオフの時に前記高耐圧トランジスタを非導通として,前記電流を前記クランプ回路に流入させない(1)〜(6)のいずれかに記載の半導体回路。

(8) 前記第1低耐圧トランジスタは、前記高耐圧トランジスタよりも小型である(1)〜(7)に記載のいずれかの半導体回路。

(9) 前記第2低耐圧トランジスタは前記高耐圧トランジスタよりも小型である(3)〜(7)に記載のいずれかの半導体回路。

(10) 前記電流電圧変換手段は抵抗である(1)〜(9)のいずれかに記載の半導体回路。

(11) 前記電位下降手段は抵抗である(4)〜(9)のいずれかに記載の半導体回路。

(12) 前記第1電源ラインに交流電力を供給する交流電源と、前記交流電力を直流電力に整流する整流回路を備え,前記第2電源ラインに直流電力を供給する直流電源と、を備える(1)〜(11)のいずれかに記載の半導体回路を備える生体組織刺激装置。

(13) 生体組織を電気刺激する複数の刺激電極と、前記刺激電極から出力される刺激電流を制御するデマルチプレクサと、前記信号に基づき前記デマルチプレクサの動作制御をする制御手段と、を備える(12)に記載の生体組織刺激装置。

ここで、第1低耐圧トランジスタ212を流れる電流Id、第3低耐圧トランジスタ211に流れる電流(I3)による各トランジスタの電流密度を同程度とすると、式(1)の電圧降下Vgs211と電圧降下Vgs212は同程度になり、第1低耐圧トランジスタ212に電流Idが流れた時の接点p1の最大電圧(クランプ電圧)は、V3−Vr208となる。これによって、第1回路112aの電源電位V2よりも第2回路112bの電源電位V3の方が低い時でも、V2>V3−Vr208の範囲で、高耐圧トランジスタ210からの電流Iを第1低耐圧トランジスタ211に流すことができ、信号を伝送することができるようになる。

1 視覚再生補助装置

10 体外装置

20 体内装置

50a、50b、50c、50d 導線

100 刺激ユニット

100a 電力供給回路

100b 刺激電流供給回路

101 電極

112 デコーダ

112a 第1回路

112b 第2回路

120 デマルチプレクサ

200 レベルシフト回路

200a クランプ回路

201 入力端子

202 出力端子

205、206 定電流源

207、208 抵抗

210 高耐圧トランジスタ

211、212、213 低耐圧トランジスタ

Claims (13)

- 第1電源ラインと第1接地ラインを持つ第1回路の第1レベルの信号を,第2電源ラインと第2接地ラインを持つ第2回路の第2レベルの信号に変換するレベルシフト回路を備える半導体回路であって、

前記レベルシフト回路は、

前記第1電源ラインに接続されて電流を出力する第1電流源と、

前記第1レベルの信号に基づく導通と非導通の切り換えによって、前記第1電流源からの電流の出力の有無を切り換える高耐圧トランジスタと、

前記電流を電圧に変換して前記第2レベルの信号を得る電流電圧変換手段と、

前記電流電圧変換手段で変換される電圧が前記第2電源ラインの電圧以下となるように,前記高耐圧トランジスタを介して供給された電流を調整する第1低耐圧トランジスタとを備えるクランプ回路と、

を備えることを特徴とする半導体回路。 - 前記クランプ回路において、

前記第1低耐圧トランジスタは、前記高耐圧のトランジスタと同極性であって、

前記第1低耐圧トランジスタの第1ソースは前記高耐圧トランジスタのドレインに接続され,前記第1低耐圧トランジスタの第1ドレインは前記電流電圧変換手段に接続され、

前記第1低耐圧トランジスタの前記第1ドレインから出力された電流が前記電流電圧変換手段で電圧に変換される請求項1に記載の半導体回路。 - 前記クランプ回路は、

前記第1低耐圧トランジスタと同極性の第2低耐圧トランジスタであって、

前記第1ソースと前記第2低耐圧トランジスタの第2ソースを接続し,前記第2低耐圧トランジスタの第2ドレインを前記第2接地ラインに接続することで、

前記第1電流源から供給される電流のうち前記第1低耐圧トランジスタへの流入量を超えた電流を流入させる前記第2低耐圧トランジスタと、を備える請求項2に記載の半導体回路。 - 前記クランプ回路は、

前記第2接地ラインに接続される第2電流源と、

前記第1低耐圧トランジスタと同極性であって、第3ソースが前記第2電源ラインに接続され、第3ゲートならびに第3ドレインが共通に接続された第3低耐圧トランジスタと、

前記第2電源ラインより前記クランプ回路の電位を低くする電位下降手段であって,一端が前記第3低耐圧トランジスタの前記第3ゲートと第3ドレインの共通接続点に接続され,他端が前記第2電流源に接続される電位下降手段と、を備える請求項3に記載の半導体回路。 - 前記第1回路と前記第2回路の接続と非接続を切り換えるスイッチ手段を備え、

前記レベルシフト回路は、前記スイッチ手段で前記第1回路と前記第2回路が接続されたときに,前記第1レベルの信号を前記第2レベルの信号に変換する請求項1〜4のいずれかに記載の半導体回路。 - 前記第1接地ラインと前記第2接地ラインの電位は、前記スイッチ手段で前記第1回路と前記第2回路が接続されたときに等しくなる請求項1〜5のいずれかに記載の半導体回路。

- 前記半導体回路は、

前記第1レベルの信号がオンの時に前記高耐圧トランジスタを導通させて前記電流を前記クランプ回路に流入させ、前記第1レベルの信号がオフの時に前記高耐圧トランジスタを非導通として,前記電流を前記クランプ回路に流入させない請求項1〜6のいずれかに記載の半導体回路。 - 前記第1低耐圧トランジスタは、前記高耐圧トランジスタよりも小型である請求項1〜7に記載のいずれかの半導体回路。

- 前記第2低耐圧トランジスタは前記高耐圧トランジスタよりも小型である請求項3〜7に記載のいずれかの半導体回路。

- 前記電流電圧変換手段は抵抗である請求項1〜9のいずれかに記載の半導体回路。

- 前記電位下降手段は抵抗である請求項4〜9のいずれかに記載の半導体回路。

- 前記第1電源ラインに交流電力を供給する交流電源と、

前記交流電力を直流電力に整流する整流回路を備え,前記第2電源ラインに直流電力を供給する直流電源と、

を備える請求項1〜11のいずれかに記載の半導体回路を備える生体組織刺激装置。 - 生体組織を電気刺激する複数の刺激電極と、

前記刺激電極から出力される刺激電流を制御するデマルチプレクサと、

前記信号に基づき前記デマルチプレクサの動作制御をする制御手段と、

を備える請求項12に記載の生体組織刺激装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012260786A JP2014104248A (ja) | 2012-11-29 | 2012-11-29 | 半導体回路及び該半導体回路を備える生体組織刺激装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012260786A JP2014104248A (ja) | 2012-11-29 | 2012-11-29 | 半導体回路及び該半導体回路を備える生体組織刺激装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014104248A true JP2014104248A (ja) | 2014-06-09 |

| JP2014104248A5 JP2014104248A5 (ja) | 2016-01-21 |

Family

ID=51026228

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012260786A Pending JP2014104248A (ja) | 2012-11-29 | 2012-11-29 | 半導体回路及び該半導体回路を備える生体組織刺激装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2014104248A (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019155082A (ja) * | 2018-03-06 | 2019-09-19 | 株式会社ニデック | 生体刺激装置 |

| JP2020054872A (ja) * | 2019-12-27 | 2020-04-09 | 国立大学法人千葉大学 | 網膜に電気刺激を与えるための装置および方法 |

| JP2020092762A (ja) * | 2018-12-11 | 2020-06-18 | 日本電信電話株式会社 | 電気刺激装置 |

| CN111870812A (zh) * | 2020-08-24 | 2020-11-03 | 大悦创新(苏州)医疗科技股份有限公司 | 电刺激输出电路 |

| JP2020182743A (ja) * | 2019-05-09 | 2020-11-12 | 株式会社ニデック | 視覚再生補助装置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04307896A (ja) * | 1991-04-04 | 1992-10-30 | Mitsubishi Electric Corp | インタフェースシステム |

| JP2003032102A (ja) * | 2001-07-12 | 2003-01-31 | Mitsubishi Electric Corp | 逆レベルシフト回路およびパワー用半導体装置 |

| JP2010187747A (ja) * | 2009-02-16 | 2010-09-02 | Nidek Co Ltd | 視覚再生補助装置 |

-

2012

- 2012-11-29 JP JP2012260786A patent/JP2014104248A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04307896A (ja) * | 1991-04-04 | 1992-10-30 | Mitsubishi Electric Corp | インタフェースシステム |

| JP2003032102A (ja) * | 2001-07-12 | 2003-01-31 | Mitsubishi Electric Corp | 逆レベルシフト回路およびパワー用半導体装置 |

| JP2010187747A (ja) * | 2009-02-16 | 2010-09-02 | Nidek Co Ltd | 視覚再生補助装置 |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019155082A (ja) * | 2018-03-06 | 2019-09-19 | 株式会社ニデック | 生体刺激装置 |

| JP2020092762A (ja) * | 2018-12-11 | 2020-06-18 | 日本電信電話株式会社 | 電気刺激装置 |

| WO2020121816A1 (ja) * | 2018-12-11 | 2020-06-18 | 日本電信電話株式会社 | 電気刺激装置 |

| JP2020182743A (ja) * | 2019-05-09 | 2020-11-12 | 株式会社ニデック | 視覚再生補助装置 |

| JP7302268B2 (ja) | 2019-05-09 | 2023-07-04 | 株式会社ニデック | 視覚再生補助装置 |

| JP2020054872A (ja) * | 2019-12-27 | 2020-04-09 | 国立大学法人千葉大学 | 網膜に電気刺激を与えるための装置および方法 |

| CN111870812A (zh) * | 2020-08-24 | 2020-11-03 | 大悦创新(苏州)医疗科技股份有限公司 | 电刺激输出电路 |

| CN111870812B (zh) * | 2020-08-24 | 2024-04-02 | 大悦创新(苏州)医疗科技股份有限公司 | 电刺激输出电路 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5776165B2 (ja) | 生体組織用刺激回路 | |

| JP6118860B2 (ja) | 埋め込み可能医療デバイスのためのバッテリ管理 | |

| US7242597B2 (en) | Rectifier circuit and vision regeneration assisting apparatus having the same | |

| JP2014104248A (ja) | 半導体回路及び該半導体回路を備える生体組織刺激装置 | |

| CN101448547B (zh) | 具有无dc的输入和输出的植入的系统 | |

| JP4224396B2 (ja) | 埋込み型聴覚人工器官の埋込み型組織刺激構成部品 | |

| JP2012115545A (ja) | 生体組織用刺激回路 | |

| US9814882B2 (en) | Rechargeable-battery implantable medical device having a primary battery active during a rechargeable-battery undervoltage condition | |

| JP5405848B2 (ja) | 視覚再生補助装置 | |

| US20130018441A1 (en) | Electronic stimulator device pulse generator circuit | |

| US8504167B2 (en) | Living tissue stimulation circuit | |

| US8975941B2 (en) | Data and power system based on CMOS bridge | |

| US20160043720A1 (en) | Semiconductor integrated circuit device | |

| JP2010536507A (ja) | 体組織に電流を伝送するシステム | |

| JP5171828B2 (ja) | インプラント装置 | |

| Jung et al. | Design of safe two-wire interface-driven chip-scale neurostimulator for visual prosthesis | |

| US20070185573A1 (en) | Load modulation communication circuit and visual restoration aiding device provided with the same | |

| Xu et al. | A multichannel neurostimulator with transcutaneous closed-loop power control and self-adaptive supply | |

| JP6048053B2 (ja) | 生体組織刺激装置 | |

| JP6040027B2 (ja) | 内部電力伝達装置を持つ装置 | |

| JP2010504178A (ja) | インプラント装置 | |

| Rothermel et al. | A 1600-pixel subretinal chip with DC-free terminals and±2V supply optimized for long lifetime and high stimulation efficiency | |

| JP2012533330A5 (ja) | ||

| US10166389B2 (en) | Single-wire electrode array | |

| JP2021078907A (ja) | 体内埋植型電気刺激装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151127 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20151127 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160816 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161017 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170228 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20170501 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170629 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20171205 |