JP2012243136A - ラダープログラミングツール - Google Patents

ラダープログラミングツール Download PDFInfo

- Publication number

- JP2012243136A JP2012243136A JP2011113585A JP2011113585A JP2012243136A JP 2012243136 A JP2012243136 A JP 2012243136A JP 2011113585 A JP2011113585 A JP 2011113585A JP 2011113585 A JP2011113585 A JP 2011113585A JP 2012243136 A JP2012243136 A JP 2012243136A

- Authority

- JP

- Japan

- Prior art keywords

- programmable controller

- circuit

- input

- personal computer

- ladder

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Programmable Controllers (AREA)

Abstract

【課題】

従来は、プログラマブルコントローラに用いるシーケンスプログラムをデバッグする装置で、入出力接点の状態が時系列にどのように変化したかが分かるデバッガを提供するものがあった。

また、ラダープログラムを編集し直すことなく、着目した回路に限定して動作を確認することができるデバッグ装置およびプログラム確認方法があった。

【解決手段】

本発明は、プログラマブルコントローラのためのラダープログラミングツールにおいて、ユーザが作成したラダープログラムをデバッグするとき、ラダープログラムの変更を前記プログラマブルコントローラの記憶素子に記憶し、ユーザの要望に応じて、変更部分を前記パソコンの表示装置に遡って表示し、ラダープログラムの編集を行うことを特徴とする。

【選択図】 図1

従来は、プログラマブルコントローラに用いるシーケンスプログラムをデバッグする装置で、入出力接点の状態が時系列にどのように変化したかが分かるデバッガを提供するものがあった。

また、ラダープログラムを編集し直すことなく、着目した回路に限定して動作を確認することができるデバッグ装置およびプログラム確認方法があった。

【解決手段】

本発明は、プログラマブルコントローラのためのラダープログラミングツールにおいて、ユーザが作成したラダープログラムをデバッグするとき、ラダープログラムの変更を前記プログラマブルコントローラの記憶素子に記憶し、ユーザの要望に応じて、変更部分を前記パソコンの表示装置に遡って表示し、ラダープログラムの編集を行うことを特徴とする。

【選択図】 図1

Description

本発明は、グラマブルコントローラのラダープログラミングツールにおいて、編集戻し機能を備えたラダープログラミングツールに関する。

プログラマブルコントローラは、一般にCPUやメモリなどを内蔵したコントローラであり、センサやスイッチなどの入力信号を入力し、この入力信号のデータのプログラム演算を行い、この演算結果を出力データとして出力し、電磁弁、モータ又は表示灯などをON−OFFして制御するものである。

また、プログラマブルコントローラのプログラムは、一般にラダープログラムを使用する。ラダープログラムは、リレー回路を記号化したラダー図をベースにしてロジックを記述するプログラムで、入力条件と出力の関係を視覚的にイメージし易いプログラム言語である。このラダープログラムを作成するため、専用のエディタであるラダープログラミングツールを使ってプログラムを作成している。また、本発明の公知例として、特許文献1(特開2011−22838)及び特許文献2(特開平8−305418号公報)がある。

特許文献1には、ラダープログラムを編集し直すことなく、着目した回路に限定して動作を確認することができるデバッグ装置およびプログラム確認方法を実現することについて開示されている。

また、特許文献2には、プログラマブルコントローラに用いるシーケンスプログラムをデバッグする装置で、入出力接点の状態が時系列にどのように変化したかが分かるデバッガを提供することが記載されている。しかし、入出力接点を変更することは開示されていない。

本発明の目的は、実際にデバッグしたラダープログラムにおいて変更した箇所を記憶して格納し、ユーザは過去の変更した箇所を表示して選択して編集することができるプログラマブルコントローラのためのラダープログラミングツールを提供することにある。

本発明は、上記目的を達成するために、パソコンと、該パソコンと接続され、パソコンの内容を表示する表示装置と、前記パソコンとプログラマブルコントローラとを接続し、該プログラマブルコントローラは、中央演算装置、通信制御回路、記憶素子、入出力制御回路、入出力装置より構成され、前記パソコンと前記プログラマブルコントローラの中央演算装置は、前記通信制御回路を介して情報を送受信可能な構成で行うラダープログラミングツールにおいて、ユーザが作成したラダープログラムをデバッグするとき、ラダープログラムの変更を前記プログラマブルコントローラの記憶素子に記憶し、ユーザの要望に応じて、変更部分を前記パソコンの表示装置に遡って表示し、ラダープログラムの編集を行うことを特徴とする。

また、上記のラダープログラミングツールにおいて、ラダープログラムの変更部分はすべて前記プログラマブルコントローラの記憶素子に記憶することを特徴とする。

本発明は、ユーザが実際に過去にデバッグしたラダープログラムを表示し、選択できるラダープログラミングツールを提供することができ、また、ユーザは過去にデバッグを行なった動作のラダープログラムを格納しているため、プログラマブルコントローラを使用した装置の動作の急な変更にも対応できる。

また、過去にデバッグを行なったラダープログラムを再利用できるため、そのラダープログラムのデバッグの時間短縮効果を得られる。

また、過去にデバッグを行なったラダープログラムを再利用できるため、そのラダープログラムのデバッグの時間短縮効果を得られる。

以下、本発明の実施の形態について図面を用いて説明する。

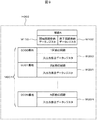

図1は、本発明の全体のシーケンスを示したものである。プログラマブルコントローラでは、プログラマブルコントローラ本体とパソコンを用いてユーザが作成したラダープログラムをプログラマブルコントローラで装置を動作させるためにそのラダープログラムの動作検証を行う。一般にこれをデバッグと呼んでいる。

本発明は、ラダープログラムのデバッグの際、修正を加え、何回もデバッグを行う。そのとき修正前に遡って入出力信号をユーザが選択できるプログラマブルコントローラのプログラミングツールを提供するものである。そのために、ユーザは、装置を動作させるため作成するラダープログラムを、その装置の機能毎に作成する。

本発明は、ラダープログラムのデバッグの際、修正を加え、何回もデバッグを行う。そのとき修正前に遡って入出力信号をユーザが選択できるプログラマブルコントローラのプログラミングツールを提供するものである。そのために、ユーザは、装置を動作させるため作成するラダープログラムを、その装置の機能毎に作成する。

図1に示すように、パソコンP001とプログラマブルコントローラ(プログラマブルコントローラ01)間の全体の通信制御において、先ず、ユーザが作成するラダープログラムを機能単位で宣言する必要があり、パソコン側(P001)よりプログラマブルコントローラ側(プログラマブルコントローラ01)へ回路定義設定(ステップS001)を送信してプログラマブルコントローラ側(プログラマブルコントローラ01)に記憶する。

ここで、ラダープログラムを宣言するということは、ラダープログラムの範囲を設定するということである。また、回路とはラダープログラムのことをいう。

ここで、ラダープログラムを宣言するということは、ラダープログラムの範囲を設定するということである。また、回路とはラダープログラムのことをいう。

次に、ユーザが実際に入出力接点を変更すると、パソコン側ではその入出力接点をプログラマブルコントローラ側に連絡する必要があるため、パソコン側よりプログラマブルコントローラ側へ入出力接点定義設定(ステップS002)を送信する。

ユーザが前のラダープログラムに戻したい状況が発生したとすると、パソコン側より編集戻し開始信号(ステップS003)をプログラマブルコントローラ側に送信し、プログラマブルコントローラ側では過去のラダープログラムを戻す準備を行う。

そして、プログラマブルコントローラ側では過去のラダープログラムを戻す準備が整うと、プログラマブルコントローラ側よりパソコン側へ戻し許可信号(ステップS004)を送信する。

そして、戻し許可信号をパソコン側で受信すると、パソコン側では過去のラダープログラムをパソコンに接続された表示器の画面に表示して、編集戻し完了信号(ステップS005)をパソコン側よりプログラマブルコントローラ側へ送信する。

以上のステップによりパソコン側とプログラマブルコントローラ側の通信制御は完了する。

ユーザが前のラダープログラムに戻したい状況が発生したとすると、パソコン側より編集戻し開始信号(ステップS003)をプログラマブルコントローラ側に送信し、プログラマブルコントローラ側では過去のラダープログラムを戻す準備を行う。

そして、プログラマブルコントローラ側では過去のラダープログラムを戻す準備が整うと、プログラマブルコントローラ側よりパソコン側へ戻し許可信号(ステップS004)を送信する。

そして、戻し許可信号をパソコン側で受信すると、パソコン側では過去のラダープログラムをパソコンに接続された表示器の画面に表示して、編集戻し完了信号(ステップS005)をパソコン側よりプログラマブルコントローラ側へ送信する。

以上のステップによりパソコン側とプログラマブルコントローラ側の通信制御は完了する。

次に、本発明のハードウエア構成について、図8を用いて説明する。

図8において、10はパソコン、20はパソコン10に接続された表示装置、30はプログラマブルコントローラ,40は通信制御装置、50は中央演算装置(CPU)、60は記憶素子、70は入出力制御回路、80は入出力装置、90はパソコン10とプログラマブルコントローラ30とで通信を行う通信線である。

プログラマブルコントローラ30の中央演算装置50は、CPUで構成され、プログラマブルコントローラ内の記憶装置60、入出力装置70、通信制御回路40を制御している。通信線90はRS―232Cなどのシリアル通信で行っても良い。中央演算装置50は外部との入出力信号を制御し、入出力制御回路70は、入出力装置80と接続されている。

図8において、10はパソコン、20はパソコン10に接続された表示装置、30はプログラマブルコントローラ,40は通信制御装置、50は中央演算装置(CPU)、60は記憶素子、70は入出力制御回路、80は入出力装置、90はパソコン10とプログラマブルコントローラ30とで通信を行う通信線である。

プログラマブルコントローラ30の中央演算装置50は、CPUで構成され、プログラマブルコントローラ内の記憶装置60、入出力装置70、通信制御回路40を制御している。通信線90はRS―232Cなどのシリアル通信で行っても良い。中央演算装置50は外部との入出力信号を制御し、入出力制御回路70は、入出力装置80と接続されている。

次に、図2を用いて、図1におけるパソコン側よりプログラマブルコントローラ側へ送信する回路定義設定(ステップS001)について説明する。

図2はパソコン側の回路定義設定のフローチャートである。

先ず、ユーザは、パソコン側でラダープログラムの機能単位の回路番号を宣言する。

そして、最初に図8におけるプログラマブルコントローラ側の中央演算装置(CPU)50は、図2において開始回路を選択する開始回路選択判定(ステップS200)を行う。開始回路の選択は、図10に示した回路定義開始ボタンC104を押して、回路番号C101を押すことにより実行される。

図2はパソコン側の回路定義設定のフローチャートである。

先ず、ユーザは、パソコン側でラダープログラムの機能単位の回路番号を宣言する。

そして、最初に図8におけるプログラマブルコントローラ側の中央演算装置(CPU)50は、図2において開始回路を選択する開始回路選択判定(ステップS200)を行う。開始回路の選択は、図10に示した回路定義開始ボタンC104を押して、回路番号C101を押すことにより実行される。

次に、図2における開始回路番号データを送信する処理(ステップS201)で、プログラマブルコントローラ側の通信制御回路40を経由してプログラマブルコントローラ側30へ送信する。次に、ラダープログラムの終了回路をユーザが宣言する。図2の終了回路データが選択されたかを図8における中央演算装置(CPU)50は終了回路選択判定(ステップS202)を実行する。そして、終了回路が選択されると、終了回路データを終了回路データ送信処理(ステップS203)にて、通信制御回路40を経由してプログラマブルコントローラ側へ送信する。終了回路の選択は、図10に示す回路定義終了ボタンC105を押して、回路番号C101を押して実行される。

なお、上記の終了回路データ送信処理(ステップS203)は、通信線90を経由してプログラマブルコントローラ側の通信制御回路40で終了回路データが受信処理されて、中央演算そうし(CPU)50にて記憶素子60に終了回路データを記憶する。そして、この一連の回路定義かが完了したことを定義終了判定(ステップS205)にて判定し、定義終了なら回路定義処理(ステップS206)を実行してプログラマブルコントローラ側へ送信する。

なお、上記の終了回路データ送信処理(ステップS203)は、通信線90を経由してプログラマブルコントローラ側の通信制御回路40で終了回路データが受信処理されて、中央演算そうし(CPU)50にて記憶素子60に終了回路データを記憶する。そして、この一連の回路定義かが完了したことを定義終了判定(ステップS205)にて判定し、定義終了なら回路定義処理(ステップS206)を実行してプログラマブルコントローラ側へ送信する。

次に、図3を用いて、プログラマブルコントローラ側の回路定義設定について説明する。

図3において、中央演算装置(CPU)40で、先ず開始回路データを受信したかを判断する(ステップS300)。受信していなければこの処理自体を終了し、受信していれば、次に開始回路データを記憶する処理を実行する(ステップS301)。開始回路データ記憶処理において、図9に示す記憶素子内のデータ保管構造で、開始回路データを開始回路格納データレジスタM100に書き込む。次に、パソコン側より通信制御回路40経由で送信された終了回路データを受信したかを判断する(ステップS302)。終了回路データが受信されたら、図9に示すデータ保管構造で、終了回路格納データレジスタM102に終了回路データ記憶処理(ステップS303)を実行して書き込まれる。そして、その後、中央演算装置(CPU)40は、記憶処理(ステップS304)を実行し、記憶素子60内のアドレスポインタM100の0000番地のアドレスポインタ1を書き込む。

この操作は、図6に説明する変更回路をこの記憶素子に書き込むために必要な記憶素子内のアドレスを指し示す必要があるために利用する。

図3において、中央演算装置(CPU)40で、先ず開始回路データを受信したかを判断する(ステップS300)。受信していなければこの処理自体を終了し、受信していれば、次に開始回路データを記憶する処理を実行する(ステップS301)。開始回路データ記憶処理において、図9に示す記憶素子内のデータ保管構造で、開始回路データを開始回路格納データレジスタM100に書き込む。次に、パソコン側より通信制御回路40経由で送信された終了回路データを受信したかを判断する(ステップS302)。終了回路データが受信されたら、図9に示すデータ保管構造で、終了回路格納データレジスタM102に終了回路データ記憶処理(ステップS303)を実行して書き込まれる。そして、その後、中央演算装置(CPU)40は、記憶処理(ステップS304)を実行し、記憶素子60内のアドレスポインタM100の0000番地のアドレスポインタ1を書き込む。

この操作は、図6に説明する変更回路をこの記憶素子に書き込むために必要な記憶素子内のアドレスを指し示す必要があるために利用する。

次に、図4を用いて、パソコン側での入出力接点の変更をプログラマブルコントローラ側に送信するフローチャートを説明する。

図4において、先ず、図10に示す開始回路番号C101を選択してから、開始回路選択ボタンC102を押す。そしてその後、終了回路番号C107を選択して、終了回路選択ボタンC103を押すと、開始回路番号データと終了回路番号データが、開始回路/終了回路送信処理(ステップS403)を実行し、パソコン側よりプログラマブルコントローラ側に送信される。

次に、ユーザが入出力接点を変更したかをチェック(ステップS404)する。

図10において、例えば、出力コイルの出力接点マークC200をY100からY200に変更すると、その接点であるC201とC202もY200に変わる。

この変更した入出力接点データは、入出力接点を変更されたデータ送信処理(ステップS403)を実行し、プログラマブルコントローラ側へ送信する。

そこで、ユーザが編集を完了するときは、もう一度図10の編集ボタンC100を押す。編集ボタンC100が押されると、編集完了が判断され(ステップS404)、編集完了信号がプログラマブルコントローラ側に送信され(ステップS405)、終了となる。

また、編集が完了していないときは、ユーザがまだ変更したい回路データがあるので、変更対象機能番号データの処理(ステップS401)へ戻る。

図4において、先ず、図10に示す開始回路番号C101を選択してから、開始回路選択ボタンC102を押す。そしてその後、終了回路番号C107を選択して、終了回路選択ボタンC103を押すと、開始回路番号データと終了回路番号データが、開始回路/終了回路送信処理(ステップS403)を実行し、パソコン側よりプログラマブルコントローラ側に送信される。

次に、ユーザが入出力接点を変更したかをチェック(ステップS404)する。

図10において、例えば、出力コイルの出力接点マークC200をY100からY200に変更すると、その接点であるC201とC202もY200に変わる。

この変更した入出力接点データは、入出力接点を変更されたデータ送信処理(ステップS403)を実行し、プログラマブルコントローラ側へ送信する。

そこで、ユーザが編集を完了するときは、もう一度図10の編集ボタンC100を押す。編集ボタンC100が押されると、編集完了が判断され(ステップS404)、編集完了信号がプログラマブルコントローラ側に送信され(ステップS405)、終了となる。

また、編集が完了していないときは、ユーザがまだ変更したい回路データがあるので、変更対象機能番号データの処理(ステップS401)へ戻る。

次に、プログラマブルコントローラ側において、変更された入出力接点を判定、受信し、記憶素子60に書き込むフローチャートを説明する。

図5において、先ず、パソコン側より送信された編集開始信号を受信したかを判断する(ステップS500)。編集開始信号を受信すると、次にプログラマブルコントローラ側の中央演算装置(CPU)50は、パソコン側より送信された開始回路番号データと終了回路番号データを受信したかを判断する(ステップS501)。開始回路番号データと終了回路番号データを受信すると、図3に示すフローチャートで登録した開始回路格納レジスタM100と、終了回路格納レジスタM102と同じ記憶素子60内のエリアを割り出し、開始回路/終了回路書き込み処理を中央演算装置(CPU)40で実行する(ステップS502)。次に、変更された入出力接点の変更データを受信し、判断する(ステップS503)。そして、1回前の変更入出力接点として、図9に示す記憶素子60の入出力接点データレジスタM200に、入出力接点変更データ書き込み処理を実行する(ステップS500)ことにより書き込まれる。

また、2回目からの記憶は、同様に記憶素子60内のアドレスポインタM0001の0001番地に1を書き込むと、入出力接点データレジスタM201に変更した入出力接点が書き込まれる。

同様に、n回目も記憶素子60内のアドレスポインタM001の000n番地に1を書き込むと、入出力接点データレジスタM20nに変更した入出力接点が書き込まれる。

図5において、先ず、パソコン側より送信された編集開始信号を受信したかを判断する(ステップS500)。編集開始信号を受信すると、次にプログラマブルコントローラ側の中央演算装置(CPU)50は、パソコン側より送信された開始回路番号データと終了回路番号データを受信したかを判断する(ステップS501)。開始回路番号データと終了回路番号データを受信すると、図3に示すフローチャートで登録した開始回路格納レジスタM100と、終了回路格納レジスタM102と同じ記憶素子60内のエリアを割り出し、開始回路/終了回路書き込み処理を中央演算装置(CPU)40で実行する(ステップS502)。次に、変更された入出力接点の変更データを受信し、判断する(ステップS503)。そして、1回前の変更入出力接点として、図9に示す記憶素子60の入出力接点データレジスタM200に、入出力接点変更データ書き込み処理を実行する(ステップS500)ことにより書き込まれる。

また、2回目からの記憶は、同様に記憶素子60内のアドレスポインタM0001の0001番地に1を書き込むと、入出力接点データレジスタM201に変更した入出力接点が書き込まれる。

同様に、n回目も記憶素子60内のアドレスポインタM001の000n番地に1を書き込むと、入出力接点データレジスタM20nに変更した入出力接点が書き込まれる。

次に、パソコン側より送信された編集完了信号を受信したかを判断する(ステップS505)。編集完了信号が受信されたら、一連の入出力接点の変更は終了する。編集完了信号が受信されなかったら、ユーザはまだ変更が発生するので開始回路番号データと終了回路番号データを受信し、判断するステップS501に戻り、動作を継続する。

以上のフローチャートで過去に変更した入出力接点がプログラマブルコントローラの記憶素子60に記憶される。

以上のフローチャートで過去に変更した入出力接点がプログラマブルコントローラの記憶素子60に記憶される。

次に、パソコン側での編集戻しについて、図6を用いて説明する。

図6は、今まで記憶してきた過去の入出力接点をユーザの要望により編集戻しをプログラマブルコントローラ側に送信するフローチャートである。

図10における編集戻しボタンC106を押すと、先ず、編集戻し開始信号がパソコン側よりプログラマブルコントローラ側に対して送信される(ステップS600)。これは、これまで変更などを行った過去の回路に編集を戻すことを宣言することである。

図6は、今まで記憶してきた過去の入出力接点をユーザの要望により編集戻しをプログラマブルコントローラ側に送信するフローチャートである。

図10における編集戻しボタンC106を押すと、先ず、編集戻し開始信号がパソコン側よりプログラマブルコントローラ側に対して送信される(ステップS600)。これは、これまで変更などを行った過去の回路に編集を戻すことを宣言することである。

次に、図10における開始回路番号C101を押して開始回路選択ボタンC102を押す。その後、終了回路番号C107を押して、終了回路選択ボタンC103を押すと、開始回路番号データと終了回路番号データが入力されたかを判断する(ステップS601)。入力されると、開始回路データと終了回路データを、開始回路/終了回路送信処理を実行することでプログラマブルコントローラ側へ送信処理される(ステップS602)。

次に、図10における編集戻しボタンC106を押すと、戻し判定で判断される(ステップS603)。その後、入出力接点データ送信処理(ステップS604)において、図9に示す記憶素子60内のアドレスポインタM001が1の行の入出力接点データレジスタM200の入出力接点データをプログラマブルコントローラ側へ送信する。

次に、プログラマブルコントローラ側より変更戻し許可信号が受信されたかを変更戻し表示許可信号を受信したかを判断する(ステップS605)。受信していると、過去表示戻し処理を実行する(ステップS606)。すなわち、変更した入出力接点を遡って表示する。この場合、回路番号001から002の入出力接点マークC200とC201がY200よりY100に戻したということになる。しかし、回路番号002の入出力接点はY200のままである。これは回路選択をしていないためである。

以上のことより、ユーザは過去にデバッグしたラダープログラムを選択することができる。ユーザからの編集戻し操作が終了したかを判断する(ステップS607)。これは、図10に示す編集ボタンC106を押すと、編集終了となり、編集戻し完了処理を実行(ステップS608)し、プログラマブルコントローラ側に編集戻し完了信号を送信する。編集戻しが完了していなければ、編集戻しを実行していると判断し、ステップS601へ戻る。

次に、図10における編集戻しボタンC106を押すと、戻し判定で判断される(ステップS603)。その後、入出力接点データ送信処理(ステップS604)において、図9に示す記憶素子60内のアドレスポインタM001が1の行の入出力接点データレジスタM200の入出力接点データをプログラマブルコントローラ側へ送信する。

次に、プログラマブルコントローラ側より変更戻し許可信号が受信されたかを変更戻し表示許可信号を受信したかを判断する(ステップS605)。受信していると、過去表示戻し処理を実行する(ステップS606)。すなわち、変更した入出力接点を遡って表示する。この場合、回路番号001から002の入出力接点マークC200とC201がY200よりY100に戻したということになる。しかし、回路番号002の入出力接点はY200のままである。これは回路選択をしていないためである。

以上のことより、ユーザは過去にデバッグしたラダープログラムを選択することができる。ユーザからの編集戻し操作が終了したかを判断する(ステップS607)。これは、図10に示す編集ボタンC106を押すと、編集終了となり、編集戻し完了処理を実行(ステップS608)し、プログラマブルコントローラ側に編集戻し完了信号を送信する。編集戻しが完了していなければ、編集戻しを実行していると判断し、ステップS601へ戻る。

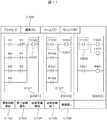

次に、図7を用いてプログラマブルコントローラ側での編集戻しの処理について説明する。

図7は、過去の入出力接点をユーザの要望により戻すプログラマブルコントローラ側のフローチャートである。

先ず、通信制御回路40で受信し、編集戻し開始信号が受信されたかを中央演算装置(CPU)50で判断する(ステップS700)。編集戻し開始信号が受信されると、次に開始回路/終了回路を受信したかを判断する(ステップS701)。開始回路/終了回路が受信されると、中央演算装置(CPU)50は、開始回路/終了回路のデータ処理を実行(ステップS702)し、記憶素子60内の開始回路格納レジスタM100と終了回路格納レジスタM102と同じ列のデータを検知処理する。次に、戻したい入出力接点データを受信したかを判断する(ステップS703)。受信されると、中央演算装置(CPU)50は、記憶素子60内のアドレスポインタM001が1の行の入出力接点データレジスタM200の入出力接点データを戻し開路実行処理(ステップS704)を実行し、検索処理を行う。また、このステップS704の処理では、図8に示すプログラマブルコントローラ側内の中央演算装置(CPU)50は、入出力制御回路70を制御して変更した入出力接点で入出力装置80を動作させる。その後、変更戻し表示許可信号の送信処理(ステップS705)を実行し、パソコン側へ送信する。また、この処理では過去のラダープログラムの回路を表示する。そして、編集戻し完了信号を受信したら終了となる。受信していないとステップS700に戻る。

図7は、過去の入出力接点をユーザの要望により戻すプログラマブルコントローラ側のフローチャートである。

先ず、通信制御回路40で受信し、編集戻し開始信号が受信されたかを中央演算装置(CPU)50で判断する(ステップS700)。編集戻し開始信号が受信されると、次に開始回路/終了回路を受信したかを判断する(ステップS701)。開始回路/終了回路が受信されると、中央演算装置(CPU)50は、開始回路/終了回路のデータ処理を実行(ステップS702)し、記憶素子60内の開始回路格納レジスタM100と終了回路格納レジスタM102と同じ列のデータを検知処理する。次に、戻したい入出力接点データを受信したかを判断する(ステップS703)。受信されると、中央演算装置(CPU)50は、記憶素子60内のアドレスポインタM001が1の行の入出力接点データレジスタM200の入出力接点データを戻し開路実行処理(ステップS704)を実行し、検索処理を行う。また、このステップS704の処理では、図8に示すプログラマブルコントローラ側内の中央演算装置(CPU)50は、入出力制御回路70を制御して変更した入出力接点で入出力装置80を動作させる。その後、変更戻し表示許可信号の送信処理(ステップS705)を実行し、パソコン側へ送信する。また、この処理では過去のラダープログラムの回路を表示する。そして、編集戻し完了信号を受信したら終了となる。受信していないとステップS700に戻る。

図10は、ユーザが作成するラダープログラムを機能単位で記憶する回路定義開始ボタンC104と回路定義終了ボタンC105を備えている。

ここで、回路の定義を行い、そのデータをプログラマブルコントローラ側の記憶素子60に登録する。

次に、ユーザはデバッグに移る。その時、編集ボタンC100を押して、編集開始したい回路番号C101を選択して、開始回路選択ボタンC102を押す。

次に、編集の終わり回路番号C107を選択して、終了回路選択ボタンC103を押す。このような作業により、この例では回路番号1と回路番号2が編集できる回路に選択できる。

次に、変更したい入出力接点C200の内容をY100からY201に変更する。

ここで、変更した内容は、プログラマブルコントローラ側の記憶素子に記憶される。

次に、上記内容で過去にデバッグした状態に戻したい時が発生した場合、ユーザは編集戻しボタンC106を押すと、回路番号0001と回路番号0002が過去で使用していた入出力接点C200がY100、C201がY100となり過去の状態に戻すことができる。また、回路番号0003の入出力接点C202は変更されない。従って、各回路の機能単位での過去にデバッグを行ったラダープログラムを再利用できるため、そのラダープログラムのデバッグの時間短縮効果を得られ、過去にデバッグしたラダープログラムをユーザが選択できる。

ここで、回路の定義を行い、そのデータをプログラマブルコントローラ側の記憶素子60に登録する。

次に、ユーザはデバッグに移る。その時、編集ボタンC100を押して、編集開始したい回路番号C101を選択して、開始回路選択ボタンC102を押す。

次に、編集の終わり回路番号C107を選択して、終了回路選択ボタンC103を押す。このような作業により、この例では回路番号1と回路番号2が編集できる回路に選択できる。

次に、変更したい入出力接点C200の内容をY100からY201に変更する。

ここで、変更した内容は、プログラマブルコントローラ側の記憶素子に記憶される。

次に、上記内容で過去にデバッグした状態に戻したい時が発生した場合、ユーザは編集戻しボタンC106を押すと、回路番号0001と回路番号0002が過去で使用していた入出力接点C200がY100、C201がY100となり過去の状態に戻すことができる。また、回路番号0003の入出力接点C202は変更されない。従って、各回路の機能単位での過去にデバッグを行ったラダープログラムを再利用できるため、そのラダープログラムのデバッグの時間短縮効果を得られ、過去にデバッグしたラダープログラムをユーザが選択できる。

また、図11に示すように、パソコン側の画面構成は縦長方向に表示することも可能である。画面の構成については、図10と同じなので説明は省略する。

10‥パソコン 20‥表示装置 30‥プログラマブルコントローラ

40‥通信制御装置 50‥中央演算装置(CPU) 60‥記憶素子

70‥入出力制御回路 80‥入出力装置

M001‥アドレスポインタ

M100‥開始回路格納データレジスタ

M102‥終了回路格納データレジスタ

M200‥1回前の回路の入出力接点データレジスタ

M201‥2回前の回路の入出力接点データレジスタ

M20N‥n回前の回路の入出力接点データレジスタ

C100‥編集ボタン

C101‥回路番号

C102‥開始回路選択ボタン

C103‥終了回路選択ボタン

C104‥回路定義開始ボタン

C105‥回路定義終了ボタン

C106‥編集戻しボタン。

40‥通信制御装置 50‥中央演算装置(CPU) 60‥記憶素子

70‥入出力制御回路 80‥入出力装置

M001‥アドレスポインタ

M100‥開始回路格納データレジスタ

M102‥終了回路格納データレジスタ

M200‥1回前の回路の入出力接点データレジスタ

M201‥2回前の回路の入出力接点データレジスタ

M20N‥n回前の回路の入出力接点データレジスタ

C100‥編集ボタン

C101‥回路番号

C102‥開始回路選択ボタン

C103‥終了回路選択ボタン

C104‥回路定義開始ボタン

C105‥回路定義終了ボタン

C106‥編集戻しボタン。

Claims (2)

- パソコンと、

該パソコンと接続され、パソコンの内容を表示する表示装置と、

前記パソコンとプログラマブルコントローラとを接続し、

該プログラマブルコントローラは、中央演算装置、通信制御回路、記憶素子、入出力制御回路、入出力装置より構成され、

前記パソコンと前記プログラマブルコントローラの中央演算装置は、前記通信制御回路を介して情報を送受信可能な構成で行うラダープログラミングツールにおいて、

ユーザが作成したラダープログラムをデバッグするとき、ラダープログラムの変更を前記プログラマブルコントローラの記憶素子に記憶し、

ユーザの要望に応じて、変更部分を前記パソコンの表示装置に遡って表示し、ラダープログラムの編集を行うことを特徴とするラダープログラミングツール。 - 請求項1記載のラダープログラミングツールにおいて、

ラダープログラムの変更部分はすべて前記プログラマブルコントローラの記憶素子に記憶することを特徴とするラダープログラミングツール。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011113585A JP2012243136A (ja) | 2011-05-20 | 2011-05-20 | ラダープログラミングツール |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011113585A JP2012243136A (ja) | 2011-05-20 | 2011-05-20 | ラダープログラミングツール |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012243136A true JP2012243136A (ja) | 2012-12-10 |

Family

ID=47464769

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011113585A Pending JP2012243136A (ja) | 2011-05-20 | 2011-05-20 | ラダープログラミングツール |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012243136A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111158301A (zh) * | 2018-11-07 | 2020-05-15 | 发那科株式会社 | 追踪装置以及可编程控制器 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001142510A (ja) * | 1999-11-11 | 2001-05-25 | Omron Corp | コントローラシステム及びプログラミングツール並びにコントローラ |

| JP2004021446A (ja) * | 2002-06-14 | 2004-01-22 | Mitsubishi Electric Corp | プログラマブルコントローラシステムおよびプログラマブルコントローラ |

| JP2011022838A (ja) * | 2009-07-16 | 2011-02-03 | Yokogawa Electric Corp | デバッグ装置およびラダープログラム確認方法 |

-

2011

- 2011-05-20 JP JP2011113585A patent/JP2012243136A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001142510A (ja) * | 1999-11-11 | 2001-05-25 | Omron Corp | コントローラシステム及びプログラミングツール並びにコントローラ |

| JP2004021446A (ja) * | 2002-06-14 | 2004-01-22 | Mitsubishi Electric Corp | プログラマブルコントローラシステムおよびプログラマブルコントローラ |

| JP2011022838A (ja) * | 2009-07-16 | 2011-02-03 | Yokogawa Electric Corp | デバッグ装置およびラダープログラム確認方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111158301A (zh) * | 2018-11-07 | 2020-05-15 | 发那科株式会社 | 追踪装置以及可编程控制器 |

| CN111158301B (zh) * | 2018-11-07 | 2023-12-01 | 发那科株式会社 | 追踪装置以及可编程控制器 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5474247B2 (ja) | 適合エレメント、テストシステム、および該適合エレメントおよびテストシステムの動作方法 | |

| CN102163047B (zh) | 学习控制机器人 | |

| JP5039428B2 (ja) | プログラマブルコントローラ及びplcシステム | |

| CN105765471B (zh) | 定序程序创建辅助装置 | |

| US9811361B2 (en) | Flexible allocation of I/O channels of a hardware component | |

| JP2008505415A (ja) | Cnc工作機械制御プログラムを作成する方法 | |

| KR20160014098A (ko) | 엔지니어링 툴, 프로그램 편집 장치 및 프로그램 편집 시스템 | |

| US7152030B2 (en) | Numerical control apparatus | |

| JP6442131B2 (ja) | 制御システムおよび制御装置 | |

| JP4971226B2 (ja) | 設計支援装置 | |

| JP2012243136A (ja) | ラダープログラミングツール | |

| CN112530615B (zh) | 一种适用于核电站设备的变量强制方法及系统 | |

| JP2016045712A (ja) | プログラマブルロジックコントローラ | |

| JP2009053823A (ja) | 加工シミュレーション装置 | |

| JP2005242682A (ja) | グラフィカルプログラミング装置及びプログラマブル表示器 | |

| US10048678B2 (en) | Numerical controller | |

| JP5544730B2 (ja) | プログラマブルコントローラのデータトレース方法 | |

| JP2010015509A (ja) | 加工プログラムチェック装置 | |

| JP7044086B2 (ja) | 制御システム、制御方法、および制御プログラム | |

| JP4937286B2 (ja) | デジタル制御システムおよびデジタル制御装置並びにデジタル制御システムの伝送試験方法 | |

| JP5108662B2 (ja) | 加工プログラム処理装置 | |

| JP7404645B2 (ja) | プログラマブルコントローラの動作履歴記録方法及びシーケンスプログラム | |

| JP2008310513A (ja) | プログラム検査装置 | |

| JP5432125B2 (ja) | 個別情報書込可能なマイクロコンピュータを備えた土木工事機械器具 | |

| JP3643321B2 (ja) | プログラマブルコントローラ用設定表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130823 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140422 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140423 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140819 |