JP2012203939A - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP2012203939A JP2012203939A JP2011065723A JP2011065723A JP2012203939A JP 2012203939 A JP2012203939 A JP 2012203939A JP 2011065723 A JP2011065723 A JP 2011065723A JP 2011065723 A JP2011065723 A JP 2011065723A JP 2012203939 A JP2012203939 A JP 2012203939A

- Authority

- JP

- Japan

- Prior art keywords

- current

- state

- tunnel junction

- magnetic tunnel

- cell transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1659—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1673—Reading or sensing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1675—Writing or programming circuits or methods

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/902—Specified use of nanostructure

- Y10S977/932—Specified use of nanostructure for electronic or optoelectronic application

- Y10S977/933—Spintronics or quantum computing

- Y10S977/935—Spin dependent tunnel, SDT, junction, e.g. tunneling magnetoresistance, TMR

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Mram Or Spin Memory Techniques (AREA)

- Hall/Mr Elements (AREA)

Abstract

【課題】過大な電流がMTJ素子に流れることを抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、抵抗状態の変化によってデータを記憶し、電流によってデータを書き換え可能な磁気トンネル接合素子を備える。セルトランジスタは、磁気トンネル接合素子に対応して設けられ、該対応する磁気トンネル接合素子に電流を流すときに導通状態となる。電流制限部は、データ書込み時にセルトランジスタおよび磁気トンネル接合素子に流れる電流を制限する。

【選択図】図4

【解決手段】半導体記憶装置は、抵抗状態の変化によってデータを記憶し、電流によってデータを書き換え可能な磁気トンネル接合素子を備える。セルトランジスタは、磁気トンネル接合素子に対応して設けられ、該対応する磁気トンネル接合素子に電流を流すときに導通状態となる。電流制限部は、データ書込み時にセルトランジスタおよび磁気トンネル接合素子に流れる電流を制限する。

【選択図】図4

Description

本発明の実施形態は、半導体記憶装置に関する。

抵抗変化型メモリの一つに磁気ランダムアクセスメモリ(MRAM(Magnetic Random Access Memory))がある。MRAMの書込み方式には、磁場書込み方式およびスピン注入書込み方式がある。このうちスピン注入書込み方式は、磁性体のサイズが小さくなる程、磁化反転に必要なスピン注入電流が小さくなるという性質を有するため、高集積化、低消費電力化および高性能化に有利である。

スピン注入書込み方式のMTJ(Magnetic Tunnel Junction)素子は、2枚の強磁性層とこれらに挟まれた非磁性バリア層(絶縁薄膜)とからなる積層構造を有し、スピン偏極トンネル効果による磁気抵抗の変化によりデジタルデータを記憶する。MTJ素子は、2枚の強磁性層の磁化配列によって、低抵抗状態と高抵抗状態とを取り得る。2枚の強磁性層の磁化配列が平行状態(P(Parallel)状態)の場合に、MTJ素子は低抵抗状態となり、2枚の強磁性層の磁化配列が非平行状態(AP(Anti Parallel)状態)の場合に、MTJ素子は高抵抗状態となる。

P状態を書き込むときには、MTJ素子をAP状態からP状態へ反転させるために必要な電流を流さなくてはならない。また、AP状態を書き込むときは、MTJをP状態からAP状態へ反転させるのに必要な電流を流さなくてはならない。

通常、MTJ素子およびセルトランジスタ等は抵抗分布(ばらつき)を有するため、MTJ素子およびセルトランジスタの抵抗および寄生抵抗の総和が最も高い場合であってもデータの書込みを確実に行うことができるように充分な書込み電流をMTJ素子に流す必要がある。

しかし、そのように充分な書込み電流を流すようにMTJ素子およびセルトランジスタ等を設計すると、逆に、MTJ素子の抵抗、セルトランジスタの抵抗、寄生抵抗等が最も低い場合には、電流が大き過ぎ、MTJ素子のバリア層が破壊されてしまうおそれがある。この場合、MTJ素子のバリア層に過大な電流が流れ、バリア層が破壊されるおそれがある。これは、MTJ素子の信頼性を低下させるという問題に繋がる。

過大な電流がMTJ素子に流れることを抑制し、信頼性の高い半導体記憶装置を提供する。

本実施形態による半導体記憶装置は、抵抗状態の変化によってデータを記憶し、電流によってデータを書き換え可能な磁気トンネル接合素子を備える。セルトランジスタは、磁気トンネル接合素子に対応して設けられ、該対応する磁気トンネル接合素子に電流を流すときに導通状態となる。電流制限部は、データ書込み時にセルトランジスタおよび磁気トンネル接合素子に流れる電流を制限する。

以下、図面を参照して本発明に係る実施形態を説明する。本実施形態は、本発明を限定するものではない。

(第1の実施形態)

図1は、第1の実施形態に従ったMARMの構成を示すブロック図である。メモリセルアレイ11内には、複数のメモリセルMCがマトリクス状に二次元配置されている。各メモリセルMCは、MTJ素子およびセルトランジスタを含む。MTJ素子は、抵抗状態の変化によってデータを記憶し、電流によってデータを書き換え可能な磁気トンネル接合素子である。セルトランジスタは、MTJ素子に対応して設けられ、該対応するMTJ素子に電流を流すときに導通状態となるように構成されている。

図1は、第1の実施形態に従ったMARMの構成を示すブロック図である。メモリセルアレイ11内には、複数のメモリセルMCがマトリクス状に二次元配置されている。各メモリセルMCは、MTJ素子およびセルトランジスタを含む。MTJ素子は、抵抗状態の変化によってデータを記憶し、電流によってデータを書き換え可能な磁気トンネル接合素子である。セルトランジスタは、MTJ素子に対応して設けられ、該対応するMTJ素子に電流を流すときに導通状態となるように構成されている。

複数のワード線WLはロウ方向に、複数のビット線BLはカラム方向にそれぞれ互いに交差するように配線されている。隣接する2つのビット線BLは対を成しており、メモリセルMCは、ワード線WLとビット線対(例えば、第1のビット線BL1、第2のビット線BL2)との交点に対応して設けられている。各メモリセルMCのMTJ素子およびセルトランジスタは、ビット線対の間(例えば、BL1とBL2との間)に直列に接続されている。また、セルトランジスタCTのゲートはワード線WLに接続されている。

メモリセルアレイ11のビット線方向の両側には、センスアンプ12およびライトドライバ22が配置されている。センスアンプ12は、ビット線BLに接続されており、選択ワード線WLに接続されたメモリセルMCに流れる電流を検知することによって、メモリセルに格納されたデータを読み出す。ライトドライバ22は、ビット線BLに接続されており、選択ワード線WLに接続されたメモリセルMCに電流を流すことによってデータを書き込む。

メモリセルアレイ11のワード線方向の両側には、ロウデコーダ13およびワード線ドライバ21がそれぞれ配置されている。ワード線ドライバ21は、ワード線に接続されており、データ読出しまたはデータ書込みの際に選択ワード線WLに電圧を印加するように構成されている。

センスアンプ12またはライトドライバ22と外部入出力端子I/Oとの間のデータの授受は、データバス14及びI/Oバッファ15を介して行われる。

コントローラ16には、各種の外部制御信号、例えば、チップイネーブル信号/CE、アドレスラッチイネーブル信号ALE、コマンドラッチイネーブル信号CLE、書き込みイネーブル信号/WE、及び読み出しイネーブル信号/REなどが入力される。コントローラ16は、これらの制御信号に基づいて、入出力端子I/Oから供給されるアドレスAddとコマンドComとを識別する。そして、コントローラ16は、アドレスAddを、アドレスレジスタ17を介してロウデコーダ13及びカラムデコーダ18に転送する。また、コントローラ16は、コマンドComをデコードする。センスアンプ12は、カラムデコーダ18によってデコードされたカラムアドレスに従って、ビット線に電圧を印加することができるように構成されている。ワード線ドライバ21は、ロウデコーダ13によってデコードされたロウアドレスに従って、選択ワード線WLに電圧を印加することができるように構成されている。

コントローラ16は、外部制御信号とコマンドに従って、データ読み出し、データ書き込み及び消去の各シーケンス制御を行う。内部電圧発生回路19は、各動作に必要な内部電圧(例えば、電源電圧より昇圧された電圧)を発生するために設けられている。この内部電圧発生回路19も、コントローラ16により制御され、昇圧動作を行い必要な電圧を発生する。

ライトドライバ22は、電流制限部としての電流制限回路24を含む。電流制限回路24は、データ書込み時においてセルトランジスタおよびMTJ素子に流れる電流を制限するように構成されている。電流制限回路24は、例えば、図5(A)から図6に示すようなカレントミラー回路で構成されている。

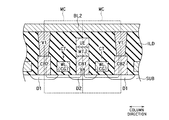

図2は、メモリセルMCの構成を示す断面図である。セルトランジスタCTは、半導体基板SUB上に形成されている。セルトランジスタCTの第1の拡散層D1は、コンタクトプラグCB2およびビアコンタクトV1を介してビット線BL2に接続されている。セルトランジスタCTの第2の拡散層D2は、コンタクトプラグCB1を介してMTJ素子の下端(下部電極)に接続されている。

MTJ素子上には、上部電極UEが設けられている。上部電極UEは、図2の紙面垂直方向(ロウ方向)に延伸しており、ロウ方向に隣接する2つのMTJ素子の上端に接続されている。そして、上部電極UEは、これら2つのMTJ素子の上端をビット線BL1(図2では図示せず)に共通に接続する。尚、ビット線BL1は、ビット線BL2に対してロウ方向に隣接するビット線である。従って、ビット線BL1は、図2において図示されていない。

ワード線WLは、ワード線としての機能、および、セルトランジスタCTのゲート電極CGとしての機能を兼ね備える。しかし、セルトランジスタCTのゲート電極CGを別途設け、ワード線WLは、ゲート電極CGとは別のレイヤに該ゲート電極CGと電気的に接続するように形成されてもよい。

ビット線BL2は、ビアコンタクトV1、コンタクトプラグCB2、セルトランジスタCTおよびコンタクトプラグCB1を介してMTJ素子の下端に電気的に接続されている。ビット線BL1は、上部電極UEを介してMTJ素子の上端に電気的に接続されている。即ち、MTJ素子およびセルトランジスタCTは、ビット線BL1と第2のビット線BL2との間に直列に接続されている。

図3は、メモリセルMCの書込み動作を示す説明図である。TMR(tunneling magnetoresistive)効果を利用したMTJ素子は、2枚の強磁性層F,Pとこれらに挟まれた非磁性層(絶縁薄膜)Bとからなる積層構造を有し、スピン偏極トンネル効果による磁気抵抗の変化によりデジタルデータを記憶する。MTJ素子は、2枚の強磁性層F,Pの磁化配列によって、低抵抗状態と高抵抗状態とを取り得る。例えば、低抵抗状態をデータ“0”と定義し、高抵抗状態をデータ“1”と定義すれば、MTJ素子に1ビットデータを記録することができる。もちろん、低抵抗状態をデータ“1”と定義し、高抵抗状態をデータ“0”と定義してもよい。

例えば、MTJ素子は、固定層(Pin層)P、トンネルバリア層B、記録層(Free層)Fを順次積層して構成される。Pin層PおよびFree層Fは、強磁性体で構成されており、トンネルバリア層Bは、絶縁膜(例えば、Al2O3,MgO)からなる。Pin層Pは、磁化の向きが固定されている層であり、Free層Fは、磁化の向きが可変であり、その磁化の向きによってデータを記憶する。

書込み時に矢印A1の向きに電界を印加すると、Pin層Pの磁化の向きに対してFree層Fのそれがアンチパラレル状態(AP状態)となり、高抵抗状態(データ“1”)となる。書込み時に矢印A2の向きに電界を印加すると、Pin層PとFree層Fとのそれぞれの磁化の向きがパラレル状態(P状態)となり、低抵抗状態(データ“0”)となる。このように、TMJ素子は、電界の印加方向によって異なるデータを書き込むことができる。

図4は、データ書込み動作時の選択メモリセルMCおよびそれに接続される電流経路の等価回路図である。選択メモリセルMCは、メモリセルアレイMCAの両側にあるライトドライバ22aと22bとの間に接続されている。ライトドライバ22aは、ビット線BL1を介して選択メモリセルMCの一端に接続されており、ライトドライバ22bは、ビット線BL2を介して選択メモリセルMCの他端に接続されている。ビット線BL1、BL2は、それぞれスイッチSW1,SW2を介してライトドライバ22a、22bに接続されている。セルトランジスタCTは、コンタクトCB1を介してMTJ素子に接続されており、コンタクトCB2を介してビット線BL2に接続されている。さらに、電流制限回路24は、ライトドライバ22aとビット線BL1との間に設けられている。このように、ライトドライバ22aと22bとの間において、電流制限回路24、スイッチSW1、ビット線BL1、MTJ素子、コンタクトCB1、セルトランジスタCT、コンタクトCB2、ビット線BL2およびスイッチSW2が直列に接続されている。

尚、図4において、スイッチSW1,SW2は抵抗で示されているが、実際には、FET(Field Effect Transistor)等のスイッチング素子で構成されている。そして、データ書込み時には、選択メモリセルMCに接続されたビット線BL1、BL2をそれぞれライトドライバ22a、22bに接続するために、スイッチSW1,SW2は導通状態となっている。また、選択メモリセルMCのセルトランジスタCTもワード線WLの駆動によって導通状態となっている。従って、図4では、スイッチSW1,SW2およびセルトランジスタCTを抵抗として図示している。

スイッチSW1、SW2、ビット線BL1、BL2、コンタクトCB1、CB2、セルトランジスタCTおよびMTJ素子の抵抗値を、それぞれRSW1、RSW2、RBL1、RBL2、RCB1、RCB2、RCTおよびRMTJとする。その他にも寄生抵抗(例えば、ビアV1の抵抗、上部電極UEの抵抗)は存在するが、それらの寄生抵抗は非常に小さいので、ここではそれらを省略する。

図4では、MTJ素子のFree層FがセルトランジスタCT側に接続されており、Pin層Pが電源側(ライトドライバ22a側)に接続されている。図4に示すMTJ素子とセルトランジスタCTとの接続関係は、図3に示すそれらの接続関係と同じである。

電流がライトドライバ22aから電流制限回路24を介してメモリセルMCAへ流れる場合に、AP状態(データ“1”)がMTJ素子に書き込まれる。このとき、ライトドライバ22a側の電源電圧VDDWTは、例えば、1.2Vであり、ライトドライバ22b側の電源電圧VDDWBは、例えば、0Vである。

MTJ素子がP状態(低抵抗状態)であり、かつ、セルトランジスタCTの抵抗RCTおよびその他の寄生抵抗の和(RCT+RSW1+RSW2+RBL1+RBL2+RCB1+RCB2)が低い方へばらついている場合、ライトドライバ22aと22bとの間の全体の抵抗値が小さくなる。従って、書込み電流が大きくなる。

さらに、図3および図4のA1に示すようにAP状態を書き込む場合、MTJ素子は、セルトランジスタCTのドレイン側あるいは高電圧側にある。この場合、セルトランジスタCTのソース電圧を上昇させないので、セルトランジスタCTのゲート−ソース間の電圧差が大きく維持される。このため、セルトランジスタCTの抵抗RCTが比較的低くなる。従って、図4に示すように、Free層FがセルトランジスタCT側に接続され、Pin層Pが電源側(高電圧源側)に接続されている場合、AP状態の書込み時に過大な電流がMTJ素子に流れる可能性がある。

そこで、電流制限回路24は、MTJ素子がセルトランジスタCTのドレイン側あるいは高電圧側にあるときに、電源VDDWTからMTJ素子へ流れる電流を制限する。この場合、電流制限回路24、MTJ素子、セルトランジスタCTは、電源VDDWTから電流制限回路24、MTJ素子、セルトランジスタCTの順番に接続される。即ち、電流制限回路24は、MTJ素子に関してセルトランジスタCTとは反対側に接続されていることになる。電流制限回路24は、電流の上限値を有し、その上限値よりも大きな電流が電源VDDWTから流れようとした場合に、その電流を上限値に抑制するように構成される。

一方、図3および図4のA2に示すようにP状態(データ“0”)を書き込む場合、電流をライトドライバ22bからセルトランジスタCTを介してメモリセルMCAへ流す。このとき、ライトドライバ22b側の電源電圧VDDWBは、例えば、1.2Vであり、ライトドライバ22a側の電源電圧VDDWTは、例えば、0Vである。

P状態を(データ“0”)を書き込む場合、MTJ素子は、セルトランジスタCTのソース側に接続される。この場合、MTJ素子に係る電圧VMTJの分だけセルトランジスタCTのソース電圧が上昇する。このため、セルトランジスタCTのゲート−ソース間の電圧差が小さくなり、セルトランジスタCTの抵抗RCTは、AP状態の書込み時のそれと比べて高くなる。従って、図4に示すように、Free層FがセルトランジスタCT側に接続され、Pin層Pが電源側に接続されている場合、P状態の書込み時にMTJ素子に流れる電流は、AP状態の書込み時にMTJ素子に流れる電流と比べて小さい。従って、この場合には、電流制限回路24は、MTJ素子に流れる電流を制限しない。

尚、寄生抵抗RSW1、RSW2、RCB1、RCB2等は、MTJ素子の抵抗RMTJに比べて非常に小さい。そのため、MTJ素子がセルトランジスタCTのドレイン側またはソース側のいずれに位置するかによって、セルトランジスタCTの導通状態(抵抗値)が比較的大きく変わる。

以上から、電流制限回路24は、MTJ素子がP状態(低抵抗状態)であり、かつ、AP状態を書き込む場合に、セルトランジスタCTのドレイン側あるいはMTJ素子の高電圧側に接続されることが好ましい。

例えば、図5(A)および図5(B)は、電流制限回路24の具体例としてのカレントミラー回路の回路図である。電流制限回路24は、図5(A)または図5(B)のいずれかに示すカレントミラー回路で構成することができる。この場合、電流制限回路24は、セルトランジスタCTのドレイン側、あるいは、MTJ素子よりも上流側(高電圧側)に接続されている必要がある。カレントミラー回路は、リファレンス回路に流れる電流と同じ大きさの電流をターゲット回路に流すために、ターゲット側に接続されたトランジスタのゲートに印加される電圧を調節するように構成されているからである。即ち、カレントミラー回路は、ターゲット回路の電流を電圧で制御しているからである。尚、ターゲット回路は、選択メモリセルMCが接続された図3に示す回路に該当する。

図5(A)に示すカレントミラー回路は、P型トランジスタP1、P2と、抵抗R1とを備える。トランジスタP1および抵抗R1は、電源Vddとリファレンス回路Crefとの間に直列に接続されている。トランジスタP2は、電源Vddとターゲット回路Ctrgとの間に接続されている。トランジスタP1、P2のゲートは共通に接続されており、トランジスタP1と抵抗R1との間の接続ノードN1に接続されている。従って、トランジスタP1およびP2の電流駆動能力が同じであるとすると、リファレンス回路Crefに流れる電流と同じ大きさの電流がターゲット回路Ctrgに流れる。トランジスタP1、P2の導通状態(抵抗値)は、ノードN1の電圧に依存する。従って、抵抗R1の抵抗値を所定値に調節することによって、リファレンス回路Crefおよびターゲット回路Ctrgに流れる電流を調節することができる。抵抗R1の抵抗値の設定は、MRAMのテスト工程において実測値あるいは統計値に基づいて設定される。

図5(B)に示すカレントミラー回路は、低電圧カスコードカレントミラー回路である。このカレントミラー回路は、P型トランジスタP10〜P50と、抵抗R10、R20とを備える。トランジスタP20、P40は、電源Vddとターゲット回路Ctrgとの間に直列に接続されている。トランジスタP10、P30は、電源Vddとリファレンス回路Cref1との間に直列に接続されている。トランジスタP50は、電源Vddとリファレンス回路Cref2との間に接続されている。低電圧カスコードカレントミラー回路は、トランジスタP10〜P50等の特性がばらついても電流を良好に制御することができる。

トランジスタP10、P20のゲートは、ターゲット回路Ctrg(トランジスタP40のソース)に共通に接続されている。また、トランジスタP30〜P50のゲートは、リファレンス回路Cref2のノードN2(トランジスタP50のソース)に共通に接続されている。ノードN2は、トランジスタP50と抵抗R20との間の接続ノードである。

トランジスタP30、P40およびP50の電流駆動能力が同じであるとすると、リファレンス回路Cref2に流れる電流と同じ大きさの電流がリファレンス回路Cref1およびターゲット回路Ctrgに流れようとする。トランジスタP10およびP20の電流駆動能力が同じであるとすると、ターゲット回路Ctrgに流れる電流と同じ大きさの電流がリファレンス回路Cref1に流れようとする。その結果、リファレンス回路Cref2に流れる電流とほぼ等しい電流がターゲット回路Ctrgに流れる。

トランジスタP30、P40、P50の導通状態(抵抗値)は、ノードN2の電圧に依存する。従って、抵抗R20の抵抗値を所定値に調節することによって、リファレンス回路Crefおよびターゲット回路Ctrg2に流れる電流を調節することができる。抵抗R20の抵抗値の設定は、MRAMのテスト工程において実測値あるいは統計値に基づいて設定される。

図6は、電流制限回路24の他の具体例としてのカレントミラー回路の回路図である。このカレントミラー回路は、P型トランジスタP11、P12と、抵抗R11とを備えている。トランジスタP12は、電源Vddとターゲット回路Ctrgとの間に接続されている。トランジスタP11および抵抗R11は、電源Vddとリファレンス側回路Cferとの間に直列に接続されている。

トランジスタP11およびP12のゲート(ノードN3)は、ターゲット回路Ctrg(トランジスタP12のソース)に共通に接続されている。トランジスタP11と抵抗R3との間のノードN4は、スイッチング素子SW1またはSW1のゲートに接続される。

これにより、リファレンス回路Crefおよびターゲット回路Ctrgには等しい電流が流れる。そして、ノードN4の電圧によってスイッチング素子SW1またはSW2の導通状態が制御される。即ち、図6に示すカレントミラー回路は、ターゲット側回路Ctrgに流れる電流をノードN4においてモニターし、このノードN4の電圧に基づいてスイッチング素子SW1またはSW2の導通状態(抵抗値)を制御するように構成されている。尚、ノードN4の電圧は、抵抗R11の両端に掛かる電圧である。

抵抗R11の抵抗値を所定値に調節することによって、スイッチング素子SW1またはSW2の導通状態(抵抗値)を制御することができる。抵抗R11の抵抗値の設定は、MRAMのテスト工程において実測値あるいは統計値に基づいて設定される。これにより、リファレンス回路Crefおよびターゲット回路Ctrgに流れる電流を調節することができる。このような図6に示すカレントミラー回路を電流制限回路24として用いてもよい。

図5(A)から図6に示すカレントミラー回路は、電流が少ない場合にはそのまま電流を流すが、電流が所定の上限値を超えようとするとほぼ一定の電流に維持される。即ち、カレントミラー回路は、電流を大きくしようとしても、上限値以上は流れないように機能する。

以上から1.MTJ素子がP状態(低抵抗状態)であり、2.セルトランジスタCTの抵抗RCTおよびその他の寄生抵抗の和が低い方へばらついており、かつ、3.MTJ素子がセルトランジスタCTのドレイン側に接続されている場合にMTJ素子に大きな電流が流れることが分かる。上記1および3の条件を本実施形態に当てはめると、P状態のMTJ素子にAP状態(データ“1”)を書き込む場合に大電流が流れ易いことになる。これは、もともとP状態のMTJ素子にAP状態を書き込むときに、MTJ素子がP状態からAP状態へ反転するまでの間に大電流が流れ易いことを意味する。

これに対し、本実施形態によれば、電流制限回路24が、MTJ素子と高電圧電源VDDWTとの間に介在し、MTJ素子に流れる電流を制限する。これにより、本実施形態によるMRAMは、過大な電流がMTJ素子に流れることを抑制し、TDDB(Time Dependent Dielectric Breakdown)破壊等を抑制することができる。これは、信頼性の向上に繋がる。

尚、一般に、MTJ素子において、P状態からAP状態への書込みは、AP状態からP状態への書込みよりも大きな電流を必要とする。電流制限回路24が流す電流の上限値は、このP状態からAP状態への書込みに必要な電流に基づいて決定すればよい。例えば、P状態からAP状態への書込みに約100μAの電流が必要な場合、電流制限回路24が流す電流の上限値は、100μAに設定される。上限値は、実験的あるいは統計的に決定される。例えば、10年間使用してもTDDB破壊が生じなかった最大電流値を上限値とすればよい。これにより、本実施形態は、MTJ素子の信頼性を維持しつつ、P状態からAP状態への書込みに支障を与えない。

(第2の実施形態)

図7は、第2の実施形態によるMRAMにおけるデータ書込み動作時の選択メモリセルMCおよびそれに接続される電流経路の等価回路図である。第2の実施形態は、MTJ素子の接続の向きが第1の実施形態のMTJ素子のそれと逆である。即ち、第2の実施形態では、Pin層PがセルトランジスタCT側に接続されており、Free層Fが電源側(ライトドライバ22a側)に接続されている。第2の実施形態のその他の構成は、第1の実施形態における対応する構成と同じでよい。

図7は、第2の実施形態によるMRAMにおけるデータ書込み動作時の選択メモリセルMCおよびそれに接続される電流経路の等価回路図である。第2の実施形態は、MTJ素子の接続の向きが第1の実施形態のMTJ素子のそれと逆である。即ち、第2の実施形態では、Pin層PがセルトランジスタCT側に接続されており、Free層Fが電源側(ライトドライバ22a側)に接続されている。第2の実施形態のその他の構成は、第1の実施形態における対応する構成と同じでよい。

第2の実施形態では、電流がライトドライバ22aから電流制限回路24を介してメモリセルMCAへ流れる場合(矢印A1)に、P状態(データ“0”)がMTJ素子に書き込まれる。このとき、ライトドライバ22a側の電源電圧VDDWTは、例えば、1.2Vであり、ライトドライバ22b側の電源電圧VDDWBは、例えば、0Vである。これにより、MTJ素子がセルトランジスタCTのドレイン側に接続された構成となる。

一方、電流がライトドライバ22bからセルトランジスタCTを介してメモリセルMCAへ流れる場合(矢印A2)に、AP状態(データ“1”)がMTJ素子に書き込まれる。このとき、ライトドライバ22a側の電源電圧VDDWTは、例えば、0Vであり、ライトドライバ22b側の電源電圧VDDWBは、例えば、1.2Vである。これにより、MTJ素子はセルトランジスタCTのソース側に接続される。

第1の実施形態において説明したように、MTJ素子がセルトランジスタCTのドレイン側に接続されているときに大きな電流がMTJ素子に流れ易い。従って、P状態(データ“0”)がMTJ素子に書き込まれる場合(矢印A1の向きに電流が流れる場合)に、電流制限回路24は、セルトランジスタCTのドレイン側あるいはMTJ素子よりも上流側(高電圧側)に設けられる。この場合も、電源VDDWTから電流制限回路24、MTJ素子、セルトランジスタCTの順番に接続される。即ち、電流制限回路24は、MTJ素子に関してセルトランジスタCTとは反対側に接続されていることになる。

上記1および3の条件を本実施形態に当てはめると、P状態のMTJ素子にP状態(データ“0”)を書き込む場合に大電流が流れ易いことになる。これは、もともとP状態のMTJ素子にP状態を書き込む動作を行う場合に、大電流が流れ易いことを意味する。さらに、これは、もともとAP状態のMTJ素子にP状態を書き込む場合に、MTJ素子がAP状態からP状態へ反転した後に大電流が流れ易いことも意味する。

これに対し、本実施形態によれば、電流制限回路24が、MTJ素子と高電圧電源VDDWTとの間に介在し、MTJ素子に流れる電流を制限する。これにより、本実施形態によるMRAMは、過大な電流がMTJ素子に流れることを抑制し、信頼性を向上させることができる。

尚、上述の通り、MTJ素子において、AP状態からP状態への書込みは、P状態からAP状態への書込みよりも少ない電流で足りる。電流制限回路24が流す電流の上限値は、このAP状態からP状態への書込みに必要な電流に基づいて決定すればよい。例えば、AP状態からP状態への書込みに約50μAの電流が必要な場合、電流制限回路24が流す電流の上限値は、50μAに設定される。上限値は、実験的あるいは統計的に決定される。例えば、10年間使用してもTDDB破壊が生じなかった最大電流値を上限値とすればよい。これにより、本実施形態は、MTJ素子の信頼性を維持しつつ、AP状態からP状態への書込みに支障を与えない。

(第3の実施形態)

図8は、第3の実施形態に従ったMRAMにおけるデータ書込み動作時の選択メモリセルMCおよびそれに接続される電流経路の等価回路図である。第3の実施形態は、電源VDDWTおよび電流制限回路24に代えて、定電流源25を備えている。第3の実施形態のその他の構成は、第1の実施形態における対応する構成と同様でよい。定電流源25は、P状態のMTJ素子をAP状態に反転させるために必要な電流を流すように構成されている。例えば、定電流源25は、第1の実施形態における上限値の電流を流すように構成されている。

図8は、第3の実施形態に従ったMRAMにおけるデータ書込み動作時の選択メモリセルMCおよびそれに接続される電流経路の等価回路図である。第3の実施形態は、電源VDDWTおよび電流制限回路24に代えて、定電流源25を備えている。第3の実施形態のその他の構成は、第1の実施形態における対応する構成と同様でよい。定電流源25は、P状態のMTJ素子をAP状態に反転させるために必要な電流を流すように構成されている。例えば、定電流源25は、第1の実施形態における上限値の電流を流すように構成されている。

このように、定電流源25を用いた第3の実施形態も、AP状態の書込み時に矢印A1方向に流れる電流を制限することができるので、第1の実施形態と同様の効果を得ることができる。

(第4の実施形態)

図9は、第4の実施形態に従ったMRAMにおけるデータ書込み動作時の選択メモリセルMCおよびそれに接続される電流経路の等価回路図である。第4の実施形態は、電源VDDWTおよび電流制限回路24に代えて、定電流源25を備えている。第4の実施形態のその他の構成は、第2の実施形態における対応する構成と同様でよい。定電流源25は、AP状態のMTJ素子をP状態に反転させるために必要な電流を流すように構成されている。例えば、定電流源25は、第2の実施形態における上限値の電流を流すように構成されている。

図9は、第4の実施形態に従ったMRAMにおけるデータ書込み動作時の選択メモリセルMCおよびそれに接続される電流経路の等価回路図である。第4の実施形態は、電源VDDWTおよび電流制限回路24に代えて、定電流源25を備えている。第4の実施形態のその他の構成は、第2の実施形態における対応する構成と同様でよい。定電流源25は、AP状態のMTJ素子をP状態に反転させるために必要な電流を流すように構成されている。例えば、定電流源25は、第2の実施形態における上限値の電流を流すように構成されている。

このように、定電流源25を用いた第4の実施形態も、P状態の書込み時に矢印A1方向に流れる電流を制限することができるので、第2の実施形態と同様の効果を得ることができる。

MC・・・メモリセル、MTJ・・・MTJ素子、RMTJ・・・MTJ素子の抵抗、CT・・・セルトランジスタ、RCT・・・セルトランジスタの抵抗、BL1、BL2・・・ビット線、RBL1、RBL2・・・ビット線の抵抗、CB1、CB2・・・コンタクトプラグ、RCB1、RCB2・・・コンタクトプラグの抵抗、SW1、SW2・・・スイッチング素子、RSW1、RSW2・・・スイッチング素子の抵抗、WL・・・ワード線、24・・・電流制限回路、25・・・定電流源

Claims (6)

- 抵抗状態の変化によってデータを記憶し、電流によってデータを書き換え可能な磁気トンネル接合素子と、

前記磁気トンネル接合素子に対応して設けられ、該対応する磁気トンネル接合素子に電流を流すときに導通状態となるセルトランジスタと、

データ書込み時に前記セルトランジスタおよび前記磁気トンネル接合素子に流れる電流を制限する電流制限部とを備えた半導体記憶装置。 - 第1のビット線と、

第2のビット線とをさらに備え、

前記磁気トンネル接合素子および前記セルトランジスタは、前記第1のビット線と前記第2のビット線との間に直列に接続されており、

前記電流制限部は、前記第1のビット線と電源との間に接続されていることを特徴とする請求項1に記載の半導体記憶装置。 - 前記電流制限部は、前記磁気トンネル接合素子に関して前記セルトランジスタとは反対側に接続されていることを特徴とする請求項1または請求項2に記載の半導体記憶装置。

- 前記磁気トンネル接合素子は、高抵抗状態と低抵抗状態とを有し、

前記電流制限部は、前記磁気トンネル接合素子が低抵抗状態である場合に、前記磁気トンネル接合素子への電流を制限することを特徴とする請求項1から請求項3のいずれかに記載の半導体記憶装置。 - 前記電流制限部は、前記磁気トンネル接合素子が前記セルトランジスタのドレイン側または高電圧側に接続されているときに前記磁気トンネル接合素子への電流を制限することを特徴とする請求項1から請求項4のいずれかに記載の半導体記憶装置。

- 前記電流制限部は、所定の抵抗値を有する抵抗素子に流れる電流にほぼ等しい電流を前記MTJ素子に流すカレントミラー回路であることを特徴とする請求項1から請求項5に記載の半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011065723A JP2012203939A (ja) | 2011-03-24 | 2011-03-24 | 半導体記憶装置 |

| US13/231,799 US8804408B2 (en) | 2011-03-24 | 2011-09-13 | Semiconductor storage device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011065723A JP2012203939A (ja) | 2011-03-24 | 2011-03-24 | 半導体記憶装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012203939A true JP2012203939A (ja) | 2012-10-22 |

Family

ID=46877229

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011065723A Withdrawn JP2012203939A (ja) | 2011-03-24 | 2011-03-24 | 半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8804408B2 (ja) |

| JP (1) | JP2012203939A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2017187995A1 (ja) * | 2016-04-27 | 2017-11-02 | ソニー株式会社 | 半導体記憶装置、駆動方法、および電子機器 |

| JP6462191B1 (ja) * | 2018-02-01 | 2019-01-30 | Tdk株式会社 | データの書き込み方法、検査方法、スピン素子の製造方法及び磁気抵抗効果素子 |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8901529B2 (en) * | 2013-03-15 | 2014-12-02 | International Business Machines Corporation | Memory array with self-aligned epitaxially grown memory elements and annular FET |

| JP2021150497A (ja) * | 2020-03-19 | 2021-09-27 | キオクシア株式会社 | 記憶装置 |

| JP2021190146A (ja) * | 2020-05-29 | 2021-12-13 | ソニーセミコンダクタソリューションズ株式会社 | 半導体記憶装置 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004280892A (ja) * | 2003-03-13 | 2004-10-07 | Toshiba Corp | 半導体記憶装置及びその制御方法 |

| US7230804B2 (en) * | 2003-05-02 | 2007-06-12 | Hitachi Global Storage Technologies Netherlands B.V. | Method and apparatus for providing a magnetic tunnel transistor with a self-pinned emitter |

| JP2006031795A (ja) * | 2004-07-14 | 2006-02-02 | Renesas Technology Corp | 不揮発性半導体記憶装置 |

| JP5160724B2 (ja) * | 2004-09-06 | 2013-03-13 | ソニー株式会社 | メモリ |

| US20070211523A1 (en) * | 2006-03-07 | 2007-09-13 | Juhan Kim | Magnetic random access memory |

| JP2007294010A (ja) | 2006-04-25 | 2007-11-08 | Sony Corp | 記憶素子の記録方法、メモリ |

| JP5002401B2 (ja) * | 2007-10-03 | 2012-08-15 | 株式会社東芝 | 抵抗変化メモリ |

| US8154913B2 (en) * | 2007-10-25 | 2012-04-10 | Nec Corporation | Magnetoresistance effect element and magnetic random access memory |

| US8503222B2 (en) * | 2009-01-27 | 2013-08-06 | Nec Corporation | Non-volatile logic circuit |

| JP5287544B2 (ja) * | 2009-06-25 | 2013-09-11 | ソニー株式会社 | 不揮発性メモリの記録方法及び不揮発性メモリ |

-

2011

- 2011-03-24 JP JP2011065723A patent/JP2012203939A/ja not_active Withdrawn

- 2011-09-13 US US13/231,799 patent/US8804408B2/en active Active

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2017187995A1 (ja) * | 2016-04-27 | 2017-11-02 | ソニー株式会社 | 半導体記憶装置、駆動方法、および電子機器 |

| US10600464B2 (en) | 2016-04-27 | 2020-03-24 | Sony Corporation | Semiconductor storage device, driving method, and electronic device |

| JP6462191B1 (ja) * | 2018-02-01 | 2019-01-30 | Tdk株式会社 | データの書き込み方法、検査方法、スピン素子の製造方法及び磁気抵抗効果素子 |

| WO2019150532A1 (ja) * | 2018-02-01 | 2019-08-08 | Tdk株式会社 | データの書き込み方法、検査方法、スピン素子の製造方法及び磁気抵抗効果素子 |

| US10490249B2 (en) | 2018-02-01 | 2019-11-26 | Tdk Corporation | Data writing method, inspection method, spin device manufacturing method, and magnetoresistance effect element |

Also Published As

| Publication number | Publication date |

|---|---|

| US20120243303A1 (en) | 2012-09-27 |

| US8804408B2 (en) | 2014-08-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1610001B (zh) | 具有磁阻元件的半导体存储器件及其数据写入方法 | |

| JP5046194B2 (ja) | ワード線駆動電位可変のmram | |

| JP5010700B2 (ja) | 半導体集積回路 | |

| KR101067538B1 (ko) | 반도체 메모리 장치 | |

| US9171618B2 (en) | Semiconductor integrated circuit and processor | |

| CN108022613B (zh) | 非易失性存储器器件及其操作方法 | |

| TW201735026A (zh) | 磁性記憶體 | |

| TWI630607B (zh) | Memory device | |

| JP2014026719A (ja) | スピン注入トルク磁気抵抗ランダムアクセスメモリでのビットラインの電圧制御 | |

| KR20200003732A (ko) | 소형 자기 저장 메모리 셀 | |

| US9711219B2 (en) | Storage device including magnetic elements | |

| KR101068573B1 (ko) | 반도체 메모리 장치 | |

| US20110305067A1 (en) | Semiconductor memory device in which resistance state of memory cell is controllable | |

| US20040012995A1 (en) | Thim film magnetic memory device permitting high precision data read | |

| KR20030089078A (ko) | 자기터널접합소자를 갖는 자기메모리셀 | |

| JP2012203939A (ja) | 半導体記憶装置 | |

| KR101057724B1 (ko) | 반도체 메모리 장치와 그의 구동 방법 | |

| US20170076791A1 (en) | Semiconductor memory device | |

| TWI790497B (zh) | 半導體記憶裝置 | |

| US8107285B2 (en) | Read direction for spin-torque based memory device | |

| US9767863B2 (en) | Redundancy memory device comprising a plurality of selecting circuits | |

| TW201533739A (zh) | 磁阻記憶體裝置 | |

| KR101095829B1 (ko) | 비휘발성 메모리 장치 | |

| JP5140855B2 (ja) | 半導体装置 | |

| US20260038552A1 (en) | Unit cell structure for spin orbit torque magnetoresistive random access memory |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A300 | Application deemed to be withdrawn because no request for examination was validly filed |

Free format text: JAPANESE INTERMEDIATE CODE: A300 Effective date: 20140603 |