JP2012190885A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2012190885A JP2012190885A JP2011051224A JP2011051224A JP2012190885A JP 2012190885 A JP2012190885 A JP 2012190885A JP 2011051224 A JP2011051224 A JP 2011051224A JP 2011051224 A JP2011051224 A JP 2011051224A JP 2012190885 A JP2012190885 A JP 2012190885A

- Authority

- JP

- Japan

- Prior art keywords

- land

- wiring

- connection conductor

- base

- width

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H10W72/012—

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

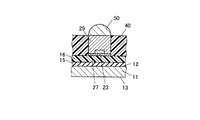

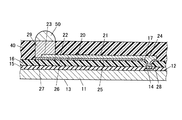

【解決手段】半導体装置1が、半導体基板11と、半導体基板11の上に形成された配線21と、半導体基板11の上に形成され、配線21に接続された接続導体22と、半導体基板11の上に形成され、接続導体22に接続されたランド23と、ランド23の上に形成され、ランド23の外縁からはみ出るように形成された端子29と、を備る。接続導体22が端子29の外周からはみ出て、接続導体22の幅W2が配線21の幅W1よりも広い。

【選択図】図2

Description

また、電気めっきにより柱状電極(11)を形成する際、ドライフィルム(19)を用いている。そして、シード層(9)の上面には配線(10)が形成されているので、配線(10)およびシード層(9)の上面にドライフィルム(19)をラミネートすることになる。ところで、最近では、狭ピッチ化の進行に伴い、配線(10)のランドと配線(10)の引き回し線部との間隔が狭くなってきている。配線(10)のランドの直径は柱状電極(11)の直径よりも例えば数μm〜10μm大きくなっている。また、配線(10)の厚さは例えば6μm程度と比較的厚くなっている。

この結果、ラミネートローラを用いた熱圧着方法では、ローラ圧力が配線(10)のランドと配線(10)の引き回し線部との間に十分に伝わらず、配線(10)のランドの周辺部上面へのドライフィルムの密着性が低下し、メッキ液が配線(10)のランドと配線(10)の引き回し線部との間に染み出し、シード層(9)のエッチング工程においてシード層(9)のエッチング不良が発生し、配線(10)間でショートが発生してしまうことがある。

そこで、本発明が解決しようとする課題は、ドライフィルム(19)の密着性の低下によるメッキ液の染み出しが起こりにくいようにすると共に、配線の断線を防止することである。

また、1体の導体構造20に接続される半田バンプ50の数が複数である場合、1体の導体構造20が有する接続導体22、ランド23、接続導体下地26及びランド下地27の数が複数である。その場合、配線21及び配線下地25が分岐しており、分かれたそれぞれの端部ごとに接続導体22及び接続導体下地26が接続される。

次に、図6に示すように、無電解メッキ法若しくは気相成長法(例えば、スパッタ法)又はこれらの組合せによって、絶縁膜16(絶縁膜16が無い場合には、パッシベーション膜15)の上及びコンタクトホール17の中にシード層73を成長させる。シード層73は、銅(Cu)の薄膜、チタン(Ti)の薄膜、チタンに銅を積層した薄膜その他の金属薄膜である。

配線21、接続導体22、ランド23及びインナーランド24の形成後、レジスト74を除去する。

アウター端子29の形成後、ドライフィルムレジスト76を除去する。

次に、半導体ウエハ70の裏面を研削し、半導体ウエハ70を薄くする。なお、半導体ウエハ70の裏面の研削は、後述の個片化処理時に行ってもよい。

次に、図16に示すように、半田バンプ50をアウター端子29の頭頂面に形成する。半田バンプ50の形成は後述の個片化処理の後に行ってもよいし、半田バンプ50を形成しなくてもよい。

次に、封止層40、パッシベーション膜15及び半導体ウエハ70を境界線72(図5参照)に沿って分断することによって、半導体ウエハ70から封止層40までの積層体をチップサイズに細分割する。具体的には、1種類又は複数種類のダイシングブレードによって封止層40、パッシベーション膜15及び半導体ウエハ70を境界線72に沿って切断する。これにより、複数の半導体装置1を得られる。

(1) 平面視して、細い配線21及び配線下地25がアウター端子29の外周を横切っていない。つまり、配線21及び配線下地25よりも幅広の接続導体22及び接続導体下地26がアウター端子29の外周から外側へはみ出ている。そのため、配線21及び配線下地25の端部からアウター端子29の外周までの部分で電力集中が起こりにくく、断線が生じない。

(2) 図10に示すように、ドライフィルムレジスト76の露光時における遮光領域78がランド23よりも広いから、形成される開口80が解像不良となることがない。つまり、開口80のうち底の部分が遮光領域78よりも狭くならず、ドライフィルムレジスト76がランド23の上に残留しない。一方、従来の技術(特許文献1:特開2008−218731号公報の図2参照)では、ドライフィルム(19)に開口(12)を形成する際には、ドライフィルム(19)を露光・現像し、ドライフイルム(19)の露光に際しては、開口(12)の縁が、露光領域と遮光領域の明暗境界線となる。ところが、配線(10)やその保護金属膜(18)が電解メッキによって形成されているから、配線(10)や保護金属膜(18)の表面が粗いので、露光時の光が配線(10)や保護金属膜(18)の表面で乱反射してしまう。そのため、露光領域と遮光領域の明暗境界線がはっきりせず、ドライフィルム(19)を現像しても、ドライフィルム(19)の一部が開口(12)内に残留してしまう。従って、本発明の実施の形態によれば、従来技術では得ることができない効果を得られる。

(3) 図11に示すように、ランド23の外縁がドライフィルムレジスト76の開口80の縁から内側に離れていることで、アウター端子29をその近傍の他の配線に短絡させずに、アウター端子29を成長させることができる。そのため、アウター端子29を周の他の配線に近づけて形成することができ、単位面積当たりに形成することができるアウター端子29の数を増やすことができる。

(4) 平面視して、ランド23の面積をアウター端子29の面積よりも小さくし、単位面積当たりに形成することができるアウター端子29の数を増やすことができるから、アウター端子29を形成することができる範囲を拡げることができる。

(5) ランド23がアウター端子29の外周からはみ出ていないから、アウター端子29とその近くの配線との距離を長くすることができる。そのため、アウター端子29とその近くの配線との間でイオンマイグレーションが発生することを抑えることができるとともに、アウター端子29とその近くの配線との短絡を防止することができる。

<請求項1>

半導体基板と、

前記半導体基板の上方に設けられた配線と、

一端部が、前記配線の一端部に接続された接続導体と、

前記接続導体の他端部に接続され、平面視して前記配線の幅より広い幅のランドと、

前記ランド上及び前記ランドの周側面の少なくとも一部を覆うように設けられた端子と、

を備えていることを特徴とする半導体装置。

<請求項2>

前記接続導体と前記ランドとは、前記半導体基板の上方に設けられており、

平面視して前記接続導体の前記ランド側の端部の幅は、前記接続導体の前記配線側の端部の幅より広いことを特徴とする請求項1に記載の半導体装置。

<請求項3>

前記半導体基板の上方であって前記配線の下に形成された配線下地と、

前記半導体基板の上方であって前記接続導体の下に形成され、前記配線下地に接続された接続導体下地と、

前記半導体基板の上方であって前記ランドの下に形成され、前記接続導体下地に接続されたランド下地と、を更に備え、

前記ランド下地が前記ランドよりも広く形成され、

前記端子のうち前記ランドの外縁からはみ出た部分が前記ランド下地上に設けられ、

前記端子の外周が前記ランド下地の外縁に重なり、

前記接続導体下地が前記端子の外周からはみ出て、

前記配線の幅と前記配線下地の幅が等しく、

前記接続導体下地の幅が前記配線及び前記配線下地の幅よりも広いことを特徴とする請求項1又は2に記載の半導体装置。

<請求項4>

前記接続導体の幅が前記ランド側から前記配線側に向かって漸減し、

前記接続導体下地の幅が前記ランド下地側から前記配線下地側に向かって漸減することを特徴とする請求項3に記載の半導体装置。

<請求項5>

前記端子の周囲において前記半導体基板の上に形成されているとともに前記配線及び前記接続導体を覆う封止層を更に備えることを特徴とする請求項1から4の何れか一項に記載の半導体装置。

<請求項6>

前記端子が前記ランド上に設けられた柱状電極であることを特徴とする請求項1から5の何れか一項に記載の半導体装置。

<請求項7>

配線と、前記配線の一端部に、一端部が接続された接続導体と、前記接続導体の他端部に接続され、平面視して前記配線の幅より広い幅のランドと、を半導体ウエハの上方に形成し、

前記ランド上及び前記ランドの周側面を覆うように端子を形成することを特徴とする半導体装置の製造方法。

<請求項8>

平面視して前記接続導体の前記ランド側の端部の幅は、前記接続導体の前記配線側の端部の幅より広く、

前記接続導体の形成に際しては、前記接続導体の幅を前記ランド側から前記配線側に向かって漸減させることを特徴とする請求項7に記載の半導体装置の製造方法。

<請求項9>

前記配線、前記接続導体及び前記ランドの形成の前に前記半導体ウエハの上にシード層を成膜した後、前記配線、前記接続導体及び前記ランドを前記シード層上に形成し、

前記配線、前記接続導体及び前記ランドの形成の後に前記配線、前記接続導体、前記ランド及び前記シード層をネガ型のレジストで被覆し、前記ランド及びその周辺の上を遮光してその遮光領域から前記接続導体をはみ出させるように前記レジストを露光し、前記レジストを現像することによって前記遮光領域に開口を形成し、

前記端子の形成に際しては、前記ランド及び前記シード層を電極として電解メッキを行って、前記開口内に端子を成長させ、

前記端子の形成後に前記レジストを除去し、

前記シード層のうち前記配線、前記接続導体及び前記端子の重なっていない部分を除去することを特徴とする請求項8に記載の半導体装置の製造方法。

<請求項10>

前記シード層の成膜後に前記シード層の上にレジストをパターニングして、前記シード層を電極として電解メッキを行うことによって前記配線、前記接続導体及び前記ランドを前記シード層上に成長させることを特徴とする請求項9に記載の半導体装置の製造方法。

<請求項11>

前記シード層の部分的な除去後に前記半導体基板の上に封止層を形成して、前記配線、前記接続導体及び前記端子を前記封止層によって覆い、

前記封止層の表面を研削して前記端子を露出させ、

前記封止層及び前記半導体ウエハをチップサイズに分断することを特徴とする請求項89又は10に記載の半導体装置の製造方法。

11 半導体基板

20 導体構造

21 配線

22 接続導体

23 ランド

24 インナーランド

25 配線下地

26 接続導体下地

27 ランド下地

28 インナーランド下地

29 アウター端子

40 封止層

70 半導体ウエハ

73 シード層

74 レジスト

75 溝

75a 線状部分

75b 幅広部

75c 大開口部

75d 小開口部

76 ドライフィルムレジスト

77 レクチル

78 遮光領域

79 露光領域

80 開口

Claims (11)

- 半導体基板と、

前記半導体基板の上方に設けられた配線と、

一端部が、前記配線の一端部に接続された接続導体と、

前記接続導体の他端部に接続され、平面視して前記配線の幅より広い幅のランドと、

前記ランド上及び前記ランドの周側面の少なくとも一部を覆うように設けられた端子と、

を備えていることを特徴とする半導体装置。 - 前記接続導体と前記ランドとは、前記半導体基板の上方に設けられており、

平面視して前記接続導体の前記ランド側の端部の幅は、前記接続導体の前記配線側の端部の幅より広いことを特徴とする請求項1に記載の半導体装置。 - 前記半導体基板の上方であって前記配線の下に形成された配線下地と、

前記半導体基板の上方であって前記接続導体の下に形成され、前記配線下地に接続された接続導体下地と、

前記半導体基板の上方であって前記ランドの下に形成され、前記接続導体下地に接続されたランド下地と、を更に備え、

前記ランド下地が前記ランドよりも広く形成され、

前記端子のうち前記ランドの外縁からはみ出た部分が前記ランド下地上に設けられ、

前記端子の外周が前記ランド下地の外縁に重なり、

前記接続導体下地が前記端子の外周からはみ出て、

前記配線の幅と前記配線下地の幅が等しく、

前記接続導体下地の幅が前記配線及び前記配線下地の幅よりも広いことを特徴とする請求項1又は2に記載の半導体装置。 - 前記接続導体の幅が前記ランド側から前記配線側に向かって漸減し、

前記接続導体下地の幅が前記ランド下地側から前記配線下地側に向かって漸減することを特徴とする請求項3に記載の半導体装置。 - 前記端子の周囲において前記半導体基板の上に形成されているとともに前記配線及び前記接続導体を覆う封止層を更に備えることを特徴とする請求項1から4の何れか一項に記載の半導体装置。

- 前記端子が前記ランド上に設けられた柱状電極であることを特徴とする請求項1から5の何れか一項に記載の半導体装置。

- 配線と、前記配線の一端部に、一端部が接続された接続導体と、前記接続導体の他端部に接続され、平面視して前記配線の幅より広い幅のランドと、を半導体ウエハの上方に形成し、

前記ランド上及び前記ランドの周側面を覆うように端子を形成することを特徴とする半導体装置の製造方法。 - 平面視して前記接続導体の前記ランド側の端部の幅は、前記接続導体の前記配線側の端部の幅より広く、

前記接続導体の形成に際しては、前記接続導体の幅を前記ランド側から前記配線側に向かって漸減させることを特徴とする請求項7に記載の半導体装置の製造方法。 - 前記配線、前記接続導体及び前記ランドの形成の前に前記半導体ウエハの上にシード層を成膜した後、前記配線、前記接続導体及び前記ランドを前記シード層上に形成し、

前記配線、前記接続導体及び前記ランドの形成の後に前記配線、前記接続導体、前記ランド及び前記シード層をネガ型のレジストで被覆し、前記ランド及びその周辺の上を遮光してその遮光領域から前記接続導体をはみ出させるように前記レジストを露光し、前記レジストを現像することによって前記遮光領域に開口を形成し、

前記端子の形成に際しては、前記ランド及び前記シード層を電極として電解メッキを行って、前記開口内に端子を成長させ、

前記端子の形成後に前記レジストを除去し、

前記シード層のうち前記配線、前記接続導体及び前記端子の重なっていない部分を除去することを特徴とする請求項8に記載の半導体装置の製造方法。 - 前記シード層の成膜後に前記シード層の上にレジストをパターニングして、前記シード層を電極として電解メッキを行うことによって前記配線、前記接続導体及び前記ランドを前記シード層上に成長させることを特徴とする請求項9に記載の半導体装置の製造方法。

- 前記シード層の部分的な除去後に前記半導体基板の上に封止層を形成して、前記配線、前記接続導体及び前記端子を前記封止層によって覆い、

前記封止層の表面を研削して前記端子を露出させ、

前記封止層及び前記半導体ウエハをチップサイズに分断することを特徴とする請求項8、9又は10に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011051224A JP2012190885A (ja) | 2011-03-09 | 2011-03-09 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011051224A JP2012190885A (ja) | 2011-03-09 | 2011-03-09 | 半導体装置及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012190885A true JP2012190885A (ja) | 2012-10-04 |

Family

ID=47083760

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011051224A Pending JP2012190885A (ja) | 2011-03-09 | 2011-03-09 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012190885A (ja) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002093946A (ja) * | 2000-09-19 | 2002-03-29 | Hitachi Ltd | 半導体装置及び半導体装置の実装構造体 |

| JP2007305694A (ja) * | 2006-05-09 | 2007-11-22 | Oki Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2011014843A (ja) * | 2009-07-06 | 2011-01-20 | Casio Computer Co Ltd | 半導体装置およびその製造方法 |

-

2011

- 2011-03-09 JP JP2011051224A patent/JP2012190885A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002093946A (ja) * | 2000-09-19 | 2002-03-29 | Hitachi Ltd | 半導体装置及び半導体装置の実装構造体 |

| JP2007305694A (ja) * | 2006-05-09 | 2007-11-22 | Oki Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2011014843A (ja) * | 2009-07-06 | 2011-01-20 | Casio Computer Co Ltd | 半導体装置およびその製造方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11545424B2 (en) | Package structure and manufacturing method thereof | |

| CN101587886B (zh) | 电子元件封装体及其制造方法 | |

| KR100730707B1 (ko) | 반도체 장치의 제조 방법 | |

| US9165890B2 (en) | Chip package comprising alignment mark and method for forming the same | |

| JP4193897B2 (ja) | 半導体装置およびその製造方法 | |

| US20190385975A1 (en) | Integrated fan-out package and manufacturing method thereof | |

| WO2006054606A1 (ja) | 半導体装置および半導体装置の製造方法 | |

| TW201917863A (zh) | 半導體裝置封裝 | |

| KR20210009762A (ko) | 팬-아웃 웨이퍼 레벨 패키지 제조 방법 | |

| JP5758605B2 (ja) | 半導体装置及びその製造方法 | |

| CN109727942B (zh) | 半导体装置以及半导体装置的制造方法 | |

| JP7048153B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| WO2011078319A1 (ja) | 半導体装置,半導体ウエハ,及び半導体装置の製造方法 | |

| JP6424996B1 (ja) | Csp型半導体デバイスおよびその製造方法 | |

| JP4232044B2 (ja) | 半導体装置の製造方法 | |

| JP2012023259A (ja) | 半導体装置及びその製造方法 | |

| JP2012190885A (ja) | 半導体装置及びその製造方法 | |

| CN113725106B (zh) | 采用切割道沟槽工艺芯片的晶圆级芯片封装技术 | |

| JP2011258733A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP5574780B2 (ja) | 半導体装置及びその製造方法 | |

| JP2012169411A (ja) | 半導体装置の製造方法 | |

| JP2011171644A (ja) | 半導体装置及びその製造方法 | |

| JP3351345B2 (ja) | 半導体装置及びその製造方法 | |

| JP7271754B2 (ja) | 半導体装置 | |

| CN115527872B (zh) | 半导体结构及其形成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20131118 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140205 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20141009 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20141111 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150107 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20150804 |