JP2012190064A - 情報処理装置、メモリ管理方法、およびメモリ管理プログラム - Google Patents

情報処理装置、メモリ管理方法、およびメモリ管理プログラム Download PDFInfo

- Publication number

- JP2012190064A JP2012190064A JP2011050502A JP2011050502A JP2012190064A JP 2012190064 A JP2012190064 A JP 2012190064A JP 2011050502 A JP2011050502 A JP 2011050502A JP 2011050502 A JP2011050502 A JP 2011050502A JP 2012190064 A JP2012190064 A JP 2012190064A

- Authority

- JP

- Japan

- Prior art keywords

- memory

- storage area

- redundant

- page

- information processing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Techniques For Improving Reliability Of Storages (AREA)

Abstract

【解決手段】情報処理装置201は、データを記憶するための記憶装置103を用いる。情報処理装置201は、記憶装置103よりも高速にアクセス可能なメモリ102と、メモリ102において複数の記憶領域を論理的に設け、記憶領域に他の記憶領域を冗長記憶領域として割り当て、冗長記憶領域にデータのコピーを格納することが可能なメモリ管理部151とを備える。メモリ管理部151は、メモリ102の使用率が所定の閾値を超えた場合には、冗長記憶領域の割り当てられた1または複数の記憶領域について、メモリ102の使用率が所定の閾値以下になるまで、各冗長記憶領域を段階的に未使用領域とする。

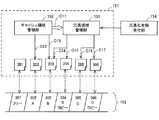

【選択図】図2

Description

[装置構成]

次に、情報処理装置201における各種機能を提供するための制御構造について説明する。

次に、本発明の実施の形態に係る情報処理装置の動作について図面を用いて説明する。本発明の実施の形態では、情報処理装置201を動作させることによって、本発明の実施の形態に係るメモリ管理方法が実施される。よって、本発明の実施の形態に係るメモリ管理方法の説明は、以下の情報処理装置201の動作説明に代える。なお、以下の説明においては、適宜図2を参照する。

レベル0:「影響なし」

未使用ページおよびクリーンページは、冗長化を行なわなくてもメモリエラーから復旧可能である。そこで、これらのページを、メモリエラーに対して「影響なし」であると定義する。

アプリケーションの部分的な処理を担うプロセスの中には、処理が失敗してもリトライできるものがある。このようなプロセスが使用するページにおいてメモリエラーが発生した場合には、当該プロセスの親プロセスの段階から処理をリトライし、当該プロセスを再起動することにより処理を継続できる。このようなプロセスが使用するページを、メモリエラーに対して「リトライ可能」なページであると定義する。

アプリケーションの中核となるプロセスが使用するページにおいてメモリエラーが発生した場合には、当該アプリケーションに関わるすべてのプロセスがエラーの影響を受ける。このため、システム全体のダウンは避けることができるものの、当該アプリケーション全体の再起動が必要である。このようなプロセスが使用するページを、メモリエラーに対して「アプリケーションダウン」なページであると定義する。

OSが使用するページにおいてメモリエラーが発生した場合には、システム全体がエラーの影響を受けるため、システムの再起動が必要である。このようなページを、メモリエラーに対して「システムダウン」なページであると定義する。

データを記憶するための記憶装置を用いる情報処理装置であって、

前記記憶装置よりも高速にアクセス可能なメモリと、

前記メモリにおいて複数の記憶領域を論理的に設け、前記記憶領域に他の前記記憶領域を冗長記憶領域として割り当て、前記冗長記憶領域にデータのコピーを格納することが可能なメモリ管理部とを備え、

前記メモリ管理部は、前記メモリの使用率が所定の閾値を超えた場合には、前記冗長記憶領域の割り当てられた1または複数の前記記憶領域について、前記メモリの使用率が前記所定の閾値以下になるまで、各前記冗長記憶領域を段階的に未使用領域とする、情報処理装置。

前記メモリ管理部は、前記冗長記憶領域の割り当てられた1または複数の前記記憶領域を、前記記憶領域に異常が発生した場合における影響度に応じて複数のレベルに分類し、前記レベルに従って未使用領域とする前記冗長記憶領域を選択する、付記1に記載の情報処理装置。

前記複数のレベルは、

未使用状態の記憶領域、または記憶領域のデータのコピーが前記記憶装置に格納されている記憶領域を示す第1レベルと、

アプリケーションが使用中の記憶領域であって、前記アプリケーションにおいてリトライが可能なプロセスが使用する記憶領域を示す第2レベルと、

アプリケーションが使用中の記憶領域であって、前記アプリケーションにおいてリトライが不可能なプロセスが使用する記憶領域を示す第3レベルと、

オペレーティングシステムが使用中の記憶領域を示す第4レベルとを含む、付記2に記載の情報処理装置。

前記メモリ管理部は、前記メモリにおける複数の記憶領域の中で使用状態が遷移する対象記憶領域が、前記記憶装置に前記対象記憶領域のデータのコピーが格納される第1の使用状態へ遷移するか前記記憶装置に前記対象記憶領域のデータのコピーが格納されない第2の使用状態へ遷移するかに基づいて、前記対象記憶領域に他の前記記憶領域を冗長記憶領域として割り当てて前記対象記憶領域のデータのコピーを格納するか否かを決定する、付記1から3のいずれかに記載の情報処理装置。

前記情報処理装置は、さらに、

アプリケーション単位または仮想アドレス空間の範囲の単位で、前記記憶領域に冗長記憶領域を割り当てるか否かの指示をユーザから受け付けるための冗長化有無受け付け部を備える、付記1から4のいずれかに記載の情報処理装置。

データを記憶するための記憶装置を用い、前記記憶装置よりも高速にアクセス可能なメモリを備える情報処理装置におけるメモリ管理方法であって、

前記メモリにおいて複数の記憶領域を論理的に設けるステップと、

前記記憶領域に他の前記記憶領域を冗長記憶領域として割り当て、前記冗長記憶領域にデータのコピーを格納するステップと、

前記メモリの使用率が所定の閾値を超えた場合には、前記冗長記憶領域の割り当てられた1または複数の前記記憶領域について、前記メモリの使用率が前記所定の閾値以下になるまで、各前記冗長記憶領域を段階的に未使用領域とするステップとを含む、メモリ管理方法。

前記冗長記憶領域を未使用領域とするステップにおいては、前記冗長記憶領域の割り当てられた1または複数の前記記憶領域を、前記記憶領域に異常が発生した場合における影響度に応じて複数のレベルに分類し、前記レベルに従って未使用領域とする前記冗長記憶領域を選択する、付記6に記載のメモリ管理方法。

前記複数のレベルは、

未使用状態の記憶領域、または記憶領域のデータのコピーが前記記憶装置に格納されている記憶領域を示す第1レベルと、

アプリケーションが使用中の記憶領域であって、前記アプリケーションにおいてリトライが可能なプロセスが使用する記憶領域を示す第2レベルと、

アプリケーションが使用中の記憶領域であって、前記アプリケーションにおいてリトライが不可能なプロセスが使用する記憶領域を示す第3レベルと、

オペレーティングシステムが使用中の記憶領域を示す第4レベルとを含む、付記7に記載のメモリ管理方法。

前記メモリ管理方法は、さらに、

前記メモリにおける複数の記憶領域の中で使用状態が遷移する対象記憶領域が、前記記憶装置に前記対象記憶領域のデータのコピーが格納される第1の使用状態へ遷移するか前記記憶装置に前記対象記憶領域のデータのコピーが格納されない第2の使用状態へ遷移するかに基づいて、前記対象記憶領域に他の前記記憶領域を冗長記憶領域として割り当てて前記対象記憶領域のデータのコピーを格納するか否かを決定するステップを含む、付記6から8のいずれかに記載のメモリ管理方法。

前記メモリ管理方法は、さらに、

アプリケーション単位または仮想アドレス空間の範囲の単位で、前記記憶領域に冗長記憶領域を割り当てるか否かの指示をユーザから受け付けるステップを含む、付記6から9のいずれかに記載のメモリ管理方法。

データを記憶するための記憶装置を用い、前記記憶装置よりも高速にアクセス可能なメモリを備える情報処理装置におけるメモリ管理プログラムであって、コンピュータに、

前記メモリにおいて複数の記憶領域を論理的に設けるステップと、

前記記憶領域に他の前記記憶領域を冗長記憶領域として割り当て、前記冗長記憶領域にデータのコピーを格納するステップと、

前記メモリの使用率が所定の閾値を超えた場合には、前記冗長記憶領域の割り当てられた1または複数の前記記憶領域について、前記メモリの使用率が前記所定の閾値以下になるまで、各前記冗長記憶領域を段階的に未使用領域とするステップとを実行させる、メモリ管理プログラム。

前記冗長記憶領域を未使用領域とするステップにおいては、前記冗長記憶領域の割り当てられた1または複数の前記記憶領域を、前記記憶領域に異常が発生した場合における影響度に応じて複数のレベルに分類し、前記レベルに従って未使用領域とする前記冗長記憶領域を選択する、付記11に記載のメモリ管理プログラム。

前記複数のレベルは、

未使用状態の記憶領域、または記憶領域のデータのコピーが前記記憶装置に格納されている記憶領域を示す第1レベルと、

アプリケーションが使用中の記憶領域であって、前記アプリケーションにおいてリトライが可能なプロセスが使用する記憶領域を示す第2レベルと、

アプリケーションが使用中の記憶領域であって、前記アプリケーションにおいてリトライが不可能なプロセスが使用する記憶領域を示す第3レベルと、

オペレーティングシステムが使用中の記憶領域を示す第4レベルとを実行させる、付記12に記載のメモリ管理プログラム。

前記メモリ管理プログラムは、さらに、コンピュータに、

前記メモリにおける複数の記憶領域の中で使用状態が遷移する対象記憶領域が、前記記憶装置に前記対象記憶領域のデータのコピーが格納される第1の使用状態へ遷移するか前記記憶装置に前記対象記憶領域のデータのコピーが格納されない第2の使用状態へ遷移するかに基づいて、前記対象記憶領域に他の前記記憶領域を冗長記憶領域として割り当てて前記対象記憶領域のデータのコピーを格納するか否かを決定するステップを実行させる、付記11から13のいずれかに記載のメモリ管理プログラム。

前記メモリ管理プログラムは、さらに、コンピュータに、

アプリケーション単位または仮想アドレス空間の範囲の単位で、前記記憶領域に冗長記憶領域を割り当てるか否かの指示をユーザから受け付けるステップを実行させる、付記11から14のいずれかに記載のメモリ管理プログラム。

102 メインメモリ

103 ハードディスク

104 入力インタフェース

105 表示コントローラ

106 データリーダ/ライタ

107 通信インタフェース

108 キーボード

109 マウス

110 ディスプレイ

111 記録媒体

121 バス

151 メモリ管理部

152 キャッシュ領域管理部

153 冗長領域管理部

154 冗長化有無受付部

201 情報処理装置

Claims (7)

- データを記憶するための記憶装置を用いる情報処理装置であって、

前記記憶装置よりも高速にアクセス可能なメモリと、

前記メモリにおいて複数の記憶領域を論理的に設け、前記記憶領域に他の前記記憶領域を冗長記憶領域として割り当て、前記冗長記憶領域にデータのコピーを格納することが可能なメモリ管理部とを備え、

前記メモリ管理部は、前記メモリの使用率が所定の閾値を超えた場合には、前記冗長記憶領域の割り当てられた1または複数の前記記憶領域について、前記メモリの使用率が前記所定の閾値以下になるまで、各前記冗長記憶領域を段階的に未使用領域とする、情報処理装置。 - 前記メモリ管理部は、前記冗長記憶領域の割り当てられた1または複数の前記記憶領域を、前記記憶領域に異常が発生した場合における影響度に応じて複数のレベルに分類し、前記レベルに従って未使用領域とする前記冗長記憶領域を選択する、請求項1に記載の情報処理装置。

- 前記複数のレベルは、

未使用状態の記憶領域、または記憶領域のデータのコピーが前記記憶装置に格納されている記憶領域を示す第1レベルと、

アプリケーションが使用中の記憶領域であって、前記アプリケーションにおいてリトライが可能なプロセスが使用する記憶領域を示す第2レベルと、

アプリケーションが使用中の記憶領域であって、前記アプリケーションにおいてリトライが不可能なプロセスが使用する記憶領域を示す第3レベルと、

オペレーティングシステムが使用中の記憶領域を示す第4レベルとを含む、請求項2に記載の情報処理装置。 - 前記メモリ管理部は、前記メモリにおける複数の記憶領域の中で使用状態が遷移する対象記憶領域が、前記記憶装置に前記対象記憶領域のデータのコピーが格納される第1の使用状態へ遷移するか前記記憶装置に前記対象記憶領域のデータのコピーが格納されない第2の使用状態へ遷移するかに基づいて、前記対象記憶領域に他の前記記憶領域を冗長記憶領域として割り当てて前記対象記憶領域のデータのコピーを格納するか否かを決定する、請求項1から3のいずれかに記載の情報処理装置。

- 前記情報処理装置は、さらに、

アプリケーション単位または仮想アドレス空間の範囲の単位で、前記記憶領域に冗長記憶領域を割り当てるか否かの指示をユーザから受け付けるための冗長化有無受け付け部を備える、請求項1から4のいずれかに記載の情報処理装置。 - データを記憶するための記憶装置を用い、前記記憶装置よりも高速にアクセス可能なメモリを備える情報処理装置におけるメモリ管理方法であって、

前記メモリにおいて複数の記憶領域を論理的に設けるステップと、

前記記憶領域に他の前記記憶領域を冗長記憶領域として割り当て、前記冗長記憶領域にデータのコピーを格納するステップと、

前記メモリの使用率が所定の閾値を超えた場合には、前記冗長記憶領域の割り当てられた1または複数の前記記憶領域について、前記メモリの使用率が前記所定の閾値以下になるまで、各前記冗長記憶領域を段階的に未使用領域とするステップとを含む、メモリ管理方法。 - データを記憶するための記憶装置を用い、前記記憶装置よりも高速にアクセス可能なメモリを備える情報処理装置におけるメモリ管理プログラムであって、コンピュータに、

前記メモリにおいて複数の記憶領域を論理的に設けるステップと、

前記記憶領域に他の前記記憶領域を冗長記憶領域として割り当て、前記冗長記憶領域にデータのコピーを格納するステップと、

前記メモリの使用率が所定の閾値を超えた場合には、前記冗長記憶領域の割り当てられた1または複数の前記記憶領域について、前記メモリの使用率が前記所定の閾値以下になるまで、各前記冗長記憶領域を段階的に未使用領域とするステップとを実行させる、メモリ管理プログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011050502A JP2012190064A (ja) | 2011-03-08 | 2011-03-08 | 情報処理装置、メモリ管理方法、およびメモリ管理プログラム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011050502A JP2012190064A (ja) | 2011-03-08 | 2011-03-08 | 情報処理装置、メモリ管理方法、およびメモリ管理プログラム |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012190064A true JP2012190064A (ja) | 2012-10-04 |

Family

ID=47083188

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011050502A Pending JP2012190064A (ja) | 2011-03-08 | 2011-03-08 | 情報処理装置、メモリ管理方法、およびメモリ管理プログラム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012190064A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016095836A (ja) * | 2014-11-14 | 2016-05-26 | 廣達電腦股▲ふん▼有限公司 | メモリ障害許容率を増加する方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62166456A (ja) * | 1986-01-20 | 1987-07-22 | Hitachi Ltd | 情報処理装置 |

| JPH0887450A (ja) * | 1994-09-16 | 1996-04-02 | Toshiba Corp | 情報記憶装置 |

| JP2000215099A (ja) * | 1996-01-31 | 2000-08-04 | Toshiba Corp | 情報処理装置の資源管理装置、及び情報処理システムにおける資源管理方法 |

| JP2002182972A (ja) * | 2000-10-18 | 2002-06-28 | Internatl Business Mach Corp <Ibm> | メモリ・ミラーリングを用いるデータ処理システムでの枯渇回復のサポート |

| JP2007206826A (ja) * | 2006-01-31 | 2007-08-16 | Sanyo Electric Co Ltd | データ再生装置 |

| JP2009199478A (ja) * | 2008-02-25 | 2009-09-03 | Hitachi Ltd | メモリミラーリング自動構成制御方式 |

-

2011

- 2011-03-08 JP JP2011050502A patent/JP2012190064A/ja active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62166456A (ja) * | 1986-01-20 | 1987-07-22 | Hitachi Ltd | 情報処理装置 |

| JPH0887450A (ja) * | 1994-09-16 | 1996-04-02 | Toshiba Corp | 情報記憶装置 |

| JP2000215099A (ja) * | 1996-01-31 | 2000-08-04 | Toshiba Corp | 情報処理装置の資源管理装置、及び情報処理システムにおける資源管理方法 |

| JP2002182972A (ja) * | 2000-10-18 | 2002-06-28 | Internatl Business Mach Corp <Ibm> | メモリ・ミラーリングを用いるデータ処理システムでの枯渇回復のサポート |

| JP2007206826A (ja) * | 2006-01-31 | 2007-08-16 | Sanyo Electric Co Ltd | データ再生装置 |

| JP2009199478A (ja) * | 2008-02-25 | 2009-09-03 | Hitachi Ltd | メモリミラーリング自動構成制御方式 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016095836A (ja) * | 2014-11-14 | 2016-05-26 | 廣達電腦股▲ふん▼有限公司 | メモリ障害許容率を増加する方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7107411B2 (en) | Apparatus method and system for fault tolerant virtual memory management | |

| JP5265654B2 (ja) | システムにおけるメモリ冗長性の制御 | |

| US20080120518A1 (en) | Replacing system hardware | |

| US9507671B2 (en) | Write cache protection in a purpose built backup appliance | |

| JP2008269142A (ja) | ディスクアレイ装置 | |

| JP2011170477A (ja) | ハイパーバイザ及びサーバ装置 | |

| JP2018088134A (ja) | マイグレーションプログラム、情報処理装置およびマイグレーション方法 | |

| US20230251931A1 (en) | System and device for data recovery for ephemeral storage | |

| KR100827287B1 (ko) | 반도체 보조 기억 장치 및 이를 이용한 데이터 저장 방법 | |

| US20100205482A1 (en) | Mirroring controller, storage device, and mirroring control method | |

| JP2009104369A (ja) | ディスクサブシステム | |

| JP2014038551A (ja) | データ記憶装置、データ記憶装置の制御方法、及びデータ記憶装置の制御プログラム | |

| JP2021026375A (ja) | ストレージシステム | |

| JP2012190064A (ja) | 情報処理装置、メモリ管理方法、およびメモリ管理プログラム | |

| JP2006107045A (ja) | ストレージ装置 | |

| JP2009265973A (ja) | データ同期システム、障害復旧方法、及び、プログラム | |

| JP2011159101A (ja) | 情報処理装置、メモリ管理方法、およびメモリ管理プログラム | |

| JP2017157098A (ja) | 情報処理装置、情報処理方法、プログラム | |

| WO2016006108A1 (ja) | ストレージおよびその制御方法 | |

| JP6928148B1 (ja) | フォールトトレラントシステム、フォールトトレラント制御方法、及び、フォールトトレラント制御プログラム | |

| JP4876662B2 (ja) | メモリダンプ機能を備えたコンピュータシステム、プログラム及びメモリダンプの方法 | |

| JP2009157880A (ja) | サーバ装置及びファイルシステム | |

| US20240069742A1 (en) | Chassis servicing and migration in a scale-up numa system | |

| JP2003330737A (ja) | 計算機システム | |

| JP4788516B2 (ja) | 動的置き換えシステム、動的置き換え方法およびプログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140213 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140811 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140909 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141029 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20150123 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20150331 |