JP2012109355A - 多層フェライト基板及び電子部品の製造方法 - Google Patents

多層フェライト基板及び電子部品の製造方法 Download PDFInfo

- Publication number

- JP2012109355A JP2012109355A JP2010256212A JP2010256212A JP2012109355A JP 2012109355 A JP2012109355 A JP 2012109355A JP 2010256212 A JP2010256212 A JP 2010256212A JP 2010256212 A JP2010256212 A JP 2010256212A JP 2012109355 A JP2012109355 A JP 2012109355A

- Authority

- JP

- Japan

- Prior art keywords

- ferrite

- multilayer

- substrate

- auxiliary layer

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H10W90/724—

Landscapes

- Production Of Multi-Layered Print Wiring Board (AREA)

- Structure Of Printed Boards (AREA)

Abstract

【解決手段】 フェライト補助層と、前記フェライト補助層よりも透磁率が高いフェライト基材層を、最外層がフェライト補助層となるように交互に複数積層して積層体6を形成し、前記積層体6を圧着することで未焼成状態の多層集合基板10を得る第1工程と、前記多層集合基板10の表裏両主面に、最外層に設けられたフェライト補助層を分断する深さの分割溝50を形成する第2工程と、前記多層集合基板10を焼成し、焼結された多層集合基板20を得る第3工程と、前記焼結された多層集合基板20を子基板に分割し、多層フェライト基板30を得る第4工程を実行する。

【選択図】 図1

Description

図1〜3は本発明の実施形態1に係る多層フェライト基板の製造方法を説明するための工程図である。

実施例1として実施形態1に示す多層集合基板10を用い、変形例1〜4、及び比較例1、2として実施例1と同様に積層した多層集合基板で、ハーフカットによって形成する分割溝50の深さが異なる多層集合基板を用いる。

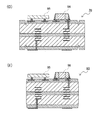

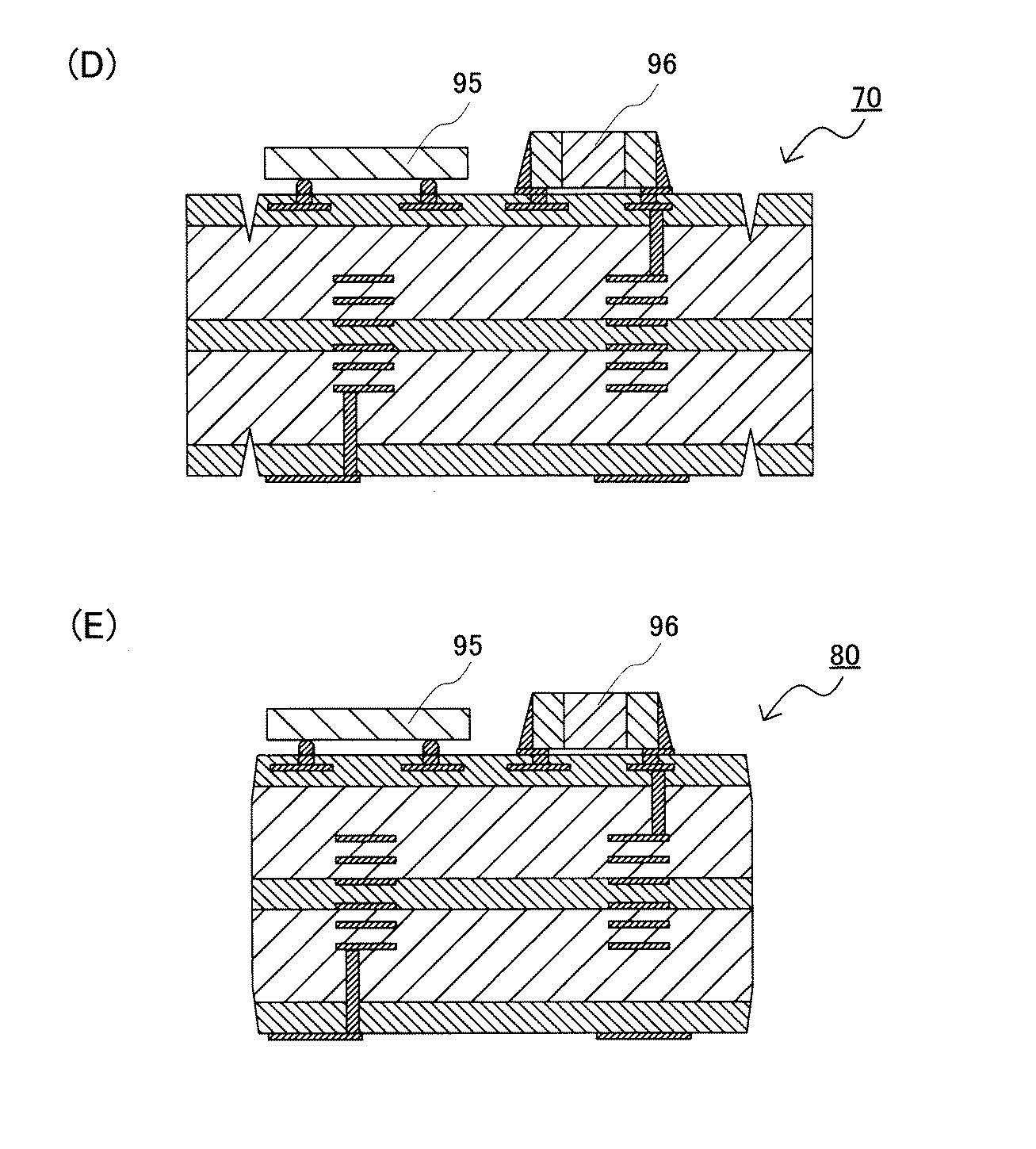

図4、5は本実施形態2に係る電子部品80の製造方法を説明するための工程図である。

2、62…第1のフェライト基材層

3、63…第2のフェライト補助層

4、64…第2のフェライト基材層

5、65…第3のフェライト補助層

6、66…積層体

7、67…コイル

10、60…多層集合基板

t1…第3のフェライト補助層の厚み

t2…第1のフェライト補助層の厚み

20、70…焼結された多層集合基板

30…多層フェライト基板

80…電子部品

50、90…分割溝

51、91…一次分割溝

52、92…二次分割溝

Claims (6)

- フェライト補助層と、前記フェライト補助層よりも透磁率が高いフェライト基材層とを、最外層がフェライト補助層となるように交互に複数積層して積層体を形成し、前記積層体を圧着することで未焼成状態の多層集合基板を得る第1工程と、前記多層集合基板の表裏両主面に、最外層に設けられたフェライト補助層を分断する深さの分割溝を形成する第2工程と、前記多層集合基板を焼成し、焼結された多層集合基板を得る第3工程と、前記多層集合基板を子基板に分割し、多層フェライト基板を得る第4工程と、を備えることを特徴とする多層フェライト基板の製造方法。

- 前記第1工程において、前記フェライト補助層は、前記積層体の厚みの中央に直交する面を中心軸として、前記積層体の厚み方向に対して対称に配置されていることを特徴とする請求項1に記載の多層フェライト基板の製造方法。

- 前記第2工程において、前記分割溝は、表裏面共に、一次分割溝の形成と前記一次分割溝に直交する二次分割溝を形成することにより形成され、前記一次分割溝及び前記二次分割溝の深さは、前記最外層に設けられたフェライト補助層の深さよりも大きく形成されており、表裏面に形成された少なくとも一方の前記一次分割溝の深さは、前記一次分割溝に直交する二次分割溝の深さよりも大きいことを特徴とする請求項1または2に記載の多層フェライト基板の製造方法。

- 前記第1工程において、前記積層体は、第1のフェライト補助層、第1のフェライト基材層、第2のフェライト補助層、第2のフェライト基材層、第3のフェライト補助層を順次積層して形成されることを特徴とする請求項1〜3のうち、いずれか1項に記載の多層フェライト基板の製造方法。

- 前記第2工程において、前記分割溝の深さは、表面と裏面の各分割溝の深さが合わせて積層体の厚みの1/2以下になるように形成されていることを特徴とする請求項1〜4のうち、いずれか1項に記載の多層フェライト基板の製造方法。

- フェライト補助層と、前記フェライト補助層よりも透磁率が高いフェライト基材層とを、最外層がフェライト補助層となるように交互に複数積層して積層体を形成し、前記積層体を圧着することで未焼成状態の多層集合基板を得る第1工程と、前記多層集合基板の表裏両主面に、最外層に設けられたフェライト補助層を分断する深さの分割溝を形成する第2工程と、前記多層集合基板を焼成し、焼結した多層集合基板を得る第3工程と、前記多層集合基板の一方主面に表面実装部品を搭載する第4工程と、前記多層集合基板を子基板に分割し、電子部品を得る第5工程と、を備えることを特徴とする電子部品の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010256212A JP2012109355A (ja) | 2010-11-16 | 2010-11-16 | 多層フェライト基板及び電子部品の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010256212A JP2012109355A (ja) | 2010-11-16 | 2010-11-16 | 多層フェライト基板及び電子部品の製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2012109355A true JP2012109355A (ja) | 2012-06-07 |

Family

ID=46494674

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010256212A Pending JP2012109355A (ja) | 2010-11-16 | 2010-11-16 | 多層フェライト基板及び電子部品の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2012109355A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015119133A (ja) * | 2013-12-20 | 2015-06-25 | 株式会社村田製作所 | 撮像装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10270813A (ja) * | 1997-03-27 | 1998-10-09 | Murata Mfg Co Ltd | ブレーク溝付きセラミック基板およびこのセラミック基板から製造される電子部品 |

| JP2003110238A (ja) * | 2001-09-28 | 2003-04-11 | Murata Mfg Co Ltd | ガラスセラミック多層基板の製造方法 |

| JP2006013318A (ja) * | 2004-06-29 | 2006-01-12 | Hitachi Metals Ltd | 多層基板及び高周波電子部品、並びにその製造方法 |

| JP2006156499A (ja) * | 2004-11-25 | 2006-06-15 | Kyocera Corp | 複数個取り基板およびガラスセラミック基板 |

| WO2007145189A1 (ja) * | 2006-06-14 | 2007-12-21 | Murata Manufacturing Co., Ltd. | 積層型セラミック電子部品 |

-

2010

- 2010-11-16 JP JP2010256212A patent/JP2012109355A/ja active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10270813A (ja) * | 1997-03-27 | 1998-10-09 | Murata Mfg Co Ltd | ブレーク溝付きセラミック基板およびこのセラミック基板から製造される電子部品 |

| JP2003110238A (ja) * | 2001-09-28 | 2003-04-11 | Murata Mfg Co Ltd | ガラスセラミック多層基板の製造方法 |

| JP2006013318A (ja) * | 2004-06-29 | 2006-01-12 | Hitachi Metals Ltd | 多層基板及び高周波電子部品、並びにその製造方法 |

| JP2006156499A (ja) * | 2004-11-25 | 2006-06-15 | Kyocera Corp | 複数個取り基板およびガラスセラミック基板 |

| WO2007145189A1 (ja) * | 2006-06-14 | 2007-12-21 | Murata Manufacturing Co., Ltd. | 積層型セラミック電子部品 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015119133A (ja) * | 2013-12-20 | 2015-06-25 | 株式会社村田製作所 | 撮像装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN103430252B (zh) | 层叠型电感元件及其制造方法 | |

| JP5921074B2 (ja) | 積層基板の製造方法 | |

| KR101589567B1 (ko) | 적층 세라믹 전자부품, 및 적층 세라믹 전자부품의 제조방법 | |

| JP2015026760A (ja) | 積層コイル | |

| JP5621573B2 (ja) | コイル内蔵基板 | |

| KR20030003072A (ko) | 다층 세라믹 기판의 제조 방법 | |

| US8736413B2 (en) | Laminated type inductor element and manufacturing method therefor | |

| KR20140024151A (ko) | 인덕터 제조방법 | |

| KR20070066973A (ko) | 배선기판 내장용 콘덴서, 그 제조방법 및 배선기판 | |

| WO2012144103A1 (ja) | 積層型インダクタ素子及び製造方法 | |

| JPWO2017110460A1 (ja) | 低背インダクタ | |

| CN203760245U (zh) | 电感元件 | |

| JP2001251024A (ja) | 多層集合基板および多層セラミック部品の製造方法 | |

| WO2011148678A1 (ja) | Lc共焼結基板及びその製造方法 | |

| JP4788544B2 (ja) | 多層セラミック基板およびその製造方法 | |

| JP5278782B2 (ja) | 集合基板の製造方法 | |

| JP2012109355A (ja) | 多層フェライト基板及び電子部品の製造方法 | |

| JP2012129367A (ja) | コイル内蔵基板の製造方法 | |

| JP2012089818A (ja) | 積層型セラミック電子部品の製造方法 | |

| JP7579067B2 (ja) | コイル部品 | |

| WO2018159482A1 (ja) | 積層型電子部品および積層型電子部品の製造方法 | |

| JP2011018783A (ja) | 多層セラミック基板の製造方法 | |

| JP2005032807A (ja) | 積層セラミック電子部品およびその製造方法 | |

| WO2010007878A1 (ja) | 多層セラミック基板およびその製造方法 | |

| JP6119843B2 (ja) | 積層型インダクタ素子の製造方法、積層型インダクタ素子、及び積層体 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130820 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20140110 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140320 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140401 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140527 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140715 |