JP2011049311A - 半導体パッケージ及び製造方法 - Google Patents

半導体パッケージ及び製造方法 Download PDFInfo

- Publication number

- JP2011049311A JP2011049311A JP2009195737A JP2009195737A JP2011049311A JP 2011049311 A JP2011049311 A JP 2011049311A JP 2009195737 A JP2009195737 A JP 2009195737A JP 2009195737 A JP2009195737 A JP 2009195737A JP 2011049311 A JP2011049311 A JP 2011049311A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor element

- semiconductor

- heat sink

- heat dissipation

- wiring board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

- H01L23/04—Containers; Seals characterised by the shape of the container or parts, e.g. caps, walls

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/367—Cooling facilitated by shape of device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/42—Fillings or auxiliary members in containers or encapsulations selected or arranged to facilitate heating or cooling

- H01L23/433—Auxiliary members in containers characterised by their shape, e.g. pistons

- H01L23/4334—Auxiliary members in encapsulations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/291—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/29101—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of less than 400°C

- H01L2224/29109—Indium [In] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/2919—Material with a principal constituent of the material being a polymer, e.g. polyester, phenolic based polymer, epoxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/29198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/29199—Material of the matrix

- H01L2224/292—Material of the matrix with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/29198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/29199—Material of the matrix

- H01L2224/2929—Material of the matrix with a principal constituent of the material being a polymer, e.g. polyester, phenolic based polymer, epoxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/29198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/29298—Fillers

- H01L2224/29299—Base material

- H01L2224/29393—Base material with a principal constituent of the material being a solid not provided for in groups H01L2224/293 - H01L2224/29391, e.g. allotropes of carbon, fullerene, graphite, carbon-nanotubes, diamond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/7525—Means for applying energy, e.g. heating means

- H01L2224/753—Means for applying energy, e.g. heating means by means of pressure

- H01L2224/75301—Bonding head

- H01L2224/75314—Auxiliary members on the pressing surface

- H01L2224/75317—Removable auxiliary member

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/7525—Means for applying energy, e.g. heating means

- H01L2224/753—Means for applying energy, e.g. heating means by means of pressure

- H01L2224/75301—Bonding head

- H01L2224/75314—Auxiliary members on the pressing surface

- H01L2224/75318—Shape of the auxiliary member

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/757—Means for aligning

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/757—Means for aligning

- H01L2224/75754—Guiding structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies and for methods related thereto

- H01L2224/75—Apparatus for connecting with bump connectors or layer connectors

- H01L2224/7598—Apparatus for connecting with bump connectors or layer connectors specially adapted for batch processes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/83001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector involving a temporary auxiliary member not forming part of the bonding apparatus

- H01L2224/83002—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector involving a temporary auxiliary member not forming part of the bonding apparatus being a removable or sacrificial coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8312—Aligning

- H01L2224/83136—Aligning involving guiding structures, e.g. spacers or supporting members

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8319—Arrangement of the layer connectors prior to mounting

- H01L2224/83191—Arrangement of the layer connectors prior to mounting wherein the layer connectors are disposed only on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/838—Bonding techniques

- H01L2224/8385—Bonding techniques using a polymer adhesive, e.g. an adhesive based on silicone, epoxy, polyimide, polyester

- H01L2224/83855—Hardening the adhesive by curing, i.e. thermosetting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/96—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being encapsulated in a common layer, e.g. neo-wafer or pseudo-wafer, said common layer being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L24/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies

- H01L24/75—Apparatus for connecting with bump connectors or layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0102—Calcium [Ca]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01041—Niobium [Nb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01049—Indium [In]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01074—Tungsten [W]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15158—Shape the die mounting substrate being other than a cuboid

- H01L2924/15159—Side view

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15312—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a pin array, e.g. PGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/1615—Shape

- H01L2924/16152—Cap comprising a cavity for hosting the device, e.g. U-shaped cap

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/161—Cap

- H01L2924/1615—Shape

- H01L2924/16195—Flat cap [not enclosing an internal cavity]

Abstract

【解決手段】配線基板35に搭載された半導体素子32に、面31aの一部又は全部に凸状曲面の部分34を形成した半導体素子用放熱板31を載置する放熱板載置工程と、平面を有する押圧板Nの平面部を、前記凸状曲面の部分34に押し付けて、半導体素子用放熱板31を半導体素子32に押付けることにより、自動的に半導体素子用放熱板31と半導体素子32との面合せを行う自動面合せ工程とを有する半導体パッケージの製造方法を提供する。また、半導体素子32を搭載した配線基板35と、半導体素子32に接合された半導体素子用放熱板31とを有し、かつ、半導体素子用放熱板31が、半導体素子32の反対側の面31aの一部又は全部に、凸状曲面の部分34を形成している半導体パッケージを提供する。

【選択図】図5

Description

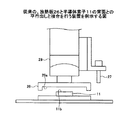

図3は、本発明の第1の実施の形態に係る半導体素子用放熱板31を例示する図である。半導体素子用放熱板31の、半導体素子32に対向する面31bは、接合層33を介して半導体素子32と接合されている。半導体素子用放熱板31は、放熱側の面31aの一部分または全部に、滑らかな凸状曲面の部分34を形成している。放熱側の面31aの中央部に設け、盛り上がった凸形状、または、なだらかな曲面の凸形状等、種々の形状とすることができる。通常、放熱側の面31aの中央部の位置に凸形状の最高地点を置く。また、凸状曲面の製作上の都合等で、凸状曲面の裾野の部分は、凹状曲面を呈していてもよい。

半導体パッケージの製造において、半導体素子と半導体素子用放熱板との自動面合せを可能にする機構を提供して、半導体素子用放熱板31と半導体素子32との接合面間の平行度を容易に確保することができ、半導体素子の放熱効果を高めることができる。従って、品質の向上及び生産性の向上を図ることができる。

本発明の第1の実施の形態の変形例は、半導体素子用放熱板の凸状曲面の部分の材料が、半導体素子用放熱板の他の部分の材料と異なる半導体素子用放熱板の例である。材料としては、プレス機械からの押付け力に耐えることのできる金属、または樹脂を使用することできる。樹脂を使用する場合には、半導体素子用放熱板の面31aの中央部36(図3の(c))に、樹脂を塗布して滑らかな曲面の盛り上がった形状等を形成し、硬化させた後、自動面合せを行う。そして、半導体素子用放熱板と半導体素子との相互位置関係を定めた後に、その樹脂を削除してもよい。樹脂等の削除により、放熱面31aを平坦にする場合、例えば、接合面が平坦な放熱フィンを接合する場合等に、樹脂削除の方法を利用することができる。

自動面合せを行った後、放熱面が平坦な半導体素子用放熱板を得ることができる。接合面に平坦性を必要とする放熱フィン機構等の取り付けに、特に有効である。

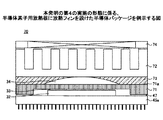

図4は、本発明の第2の実施の形態に係る、半導体素子を搭載した配線基板と半導体素子用放熱板とを有する、半導体パッケージを例示する図である。半導体パッケージは、半導体素子を囲むような形状の凹部を放熱板の半導体素子側の面に有し、または、配線基板にキャビティ(凹型領域)を有したパッケージである。

半導体素子用放熱板が凹部を有し、または、配線基板がキャビティを有する場合の、半導体素子と半導体素子用放熱板との接合は、これらの閉空間における接合であるため、従来の、接合面の相互距離把握と接合の押付け方向の設定は困難を伴うものであった。半導体素子の側面からの接合部位の計測、測定が困難であったからである。しかし、本発明の、凸状曲面の部分を有する半導体素子用放熱板を使用すれば、容易に自動面合せを行うことができるので、一連の高精度の接合の工程を容易に実施することができ、放熱効果の優れた半導体パッケージを得ることができる。従って、品質の向上、生産性の向上を図ることができる。

本発明の第3の実施の形態は、自動面合せ工程を有する半導体パッケージの製造方法の例である。

本発明に係る「自動面合せ」は、半導体素子と半導体素子用放熱板のおのおのの接合面を相互に平行の位置に定めるための方法で、プレス機械等に測定、制御の機構を設けることなく、プレス機械等の押付け力のみによって、接合すべき対象部品が自動的に作動し、いわば、self−alignment(自動調芯)ともいうべき動作によって、接合面の平行度を出す方法である。

図5の(b)に示す片当たりの状態になり、押付け力がかかると、半導体素子接合面32aの、点Pの箇所の接合層33が圧迫される。流動性を有する接合層33は、点Pの箇所における肉厚が減少して、半導体素子用放熱板31と半導体素子32とが点Pにおいてほぼ接した状態となり、点Pにおいて、両者間に強い反力が発生する。点Pにおいて片当たりしている一方で、点Q、R付近においては反力が発生せず、無負荷状態となる。半導体素子用放熱板31の全体は、プレス機械の押圧板Nにより、矢印Xの方向に押されているので、半導体素子用放熱板31が受ける偶力のモーメントの釣り合いが崩れる。すると、半導体素子用放熱板31は、点Pを中心として、矢印Aの方向に回転し始める。そして、この回転の動きは、接合面間が平行となって、偶力のモーメントが釣り合いの状態となるまで継続する。すなわち、図5の(a)に示すような半導体素子用放熱板31の面31bが、半導体素子32の面32aに平行な状態となるまで、継続する。平行状態においては、接合面における矢印Xの方向の発生応力は、点P,Q,Rを含め、ほぼ全ての点において、等しくなり、半導体素子用放熱板31にかかる力の偶力のモーメントが釣り合うこととなる。さらに、プレス機械等によるX方向の押付け力によって、接続層33の粘度等の物性値に応じて、半導体素子用放熱板の面31bと半導体素子の面32aとの面間距離が定まる。以上のように、半導体素子の面と半導体素子用放熱板の面との平行度の自動調整を、プレス機械等に、測定、制御の機構を設けることなく、行わせることができる。

図6は、本発明の第3の実施の形態に係る、半導体パッケージの製造方法の工程を例示する図である。工程は、ステップ1.放熱板載置工程(S101)、ステップ2.自動面合せ工程(S102)、ステップ3.接合層硬化工程(S103)を有している。半導体パッケージの構造として、図3の(a)の例を参照して説明する。

半導体素子を搭載した配線基板35を準備して、半導体素子32の放熱面(通常集積回路面の裏面)32aに接合層33を塗布する。接合層33の部材は、TIMといい、例えば、シリコンポリマー系樹脂を使用する。TIMを塗布し半硬化状態とする手順は、周知の樹脂塗布技術に従う。次に、TIMが塗布された半導体素子32に、凸状曲面の部分34を形成した半導体素子用放熱板31を載置する。その他、TIMには、インジウム、インジウムの合金等の金属、カーボンを含有した樹脂又はカーボンを含有した金属等を使用することができる。TIMが流動性を有しない硬い材料の場合であっても、工程を進めることができる。

プレス機械等(図示せず)を用いて、半導体素子用放熱板31を半導体素子32の側に向かって押付け、自動面合せを行う。自動面合せについては、前出の〈第3の実施の形態〉において詳説したので、説明を省く。

周知の樹脂硬化技術に従って、接合層の硬化を行う。図4の半導体パッケージの例に示されているように、半導体素子用放熱板が、半導体素子との接合層33以外に、配線基板との接合層47等を有している場合には、接合層47等の肉厚を確保しながら、半導体素子との自動面合せを行う。半導体パッケージにおける接合層47の肉厚の値は、例えば、0.2〜0.25mmである。

自動面合せ、すなわち、半導体素子の接合面と半導体素子用放熱板の接合面との平行度の自動調整を、プレス機械等に測定、制御の機構を設けることなく、行わせることができる。従って、生産性の向上及び品質の向上を図ることができる。

図7は、本発明の第4の実施の形態に係る、半導体素子用放熱板71に放熱フィン72を設けた半導体パッケージ70を例示する図である。放熱フィン72の接合により、半導体素子の放熱の熱効率を、さらに高めることができる。放熱フィン72については、周知の種々の形状、材質を使用することができる。

半導体素子用放熱板のみの放熱機構と比較して、さらに高い放熱の熱効率を得ることができ、製品性能の向上を図ることができる。

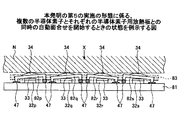

本発明の第5の実施の形態は、配線基板上に2次元配列した複数の半導体素子に対して半導体素子用放熱板の自動面合せ及び接合を行う、半導体パッケージの製造方法の例である。製造工程は、〈第3の実施の形態〉における工程と、半導体素子の個数以外は同様であるので、詳細の説明を省く。

複数の半導体素子に対し、同時に、半導体素子用放熱板の自動面合せを行い、接合を行うことができるので、生産性の向上及び製造コストの削減を図ることができる。

以上、本発明の好ましい実施の形態について詳説したが、本発明は、上述した実施の形態に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施の形態に種々の変形及び置換を加えることができる。

31,42a,42b,42c,71,82p,82q,82r,82s 半導体素子用放熱板

31a 放熱側の面

31b 半導体素子用放熱板31の、半導体素子32に対向する面

32,32p,32q,32r,32s 半導体素子

32a 半導体素子32の半導体素子用放熱板との接合面

33,47,73 接合層

34 凸状曲面の部分

35,45a,45b,45c,81 配線基板

41 凹部

43 キャビティ

44 配線基板45bのキャビティ43の周縁部

48 半導体素子用放熱板42aの凹部41を形成する周壁

49 バンプ

71a 半導体素子用放熱板71の放熱面

72 放熱フィン

74 冷却ファン

83 リテーナ(支持枠)

Ca 凹部41の深さ

Cb キャビティ43の深さ

D 周壁48の幅

N プレス機械の押圧板

P,Q,R 半導体素子の接合面の点

Claims (7)

- 配線基板に搭載された半導体素子に、前記半導体素子との接合面と反対側の面の一部又は全部に凸状曲面の部分を形成した半導体素子用放熱板を載置する放熱板載置工程と、

平面を有する押圧板の平面部を、前記凸状曲面の部分に押し付けて、前記半導体素子用放熱板を前記半導体素子に押付けることにより、自動的に前記半導体素子用放熱板と前記半導体素子との面合せを行う自動面合せ工程とを有する半導体パッケージの製造方法。 - 同一の配線基板上に搭載された複数の半導体素子に対して、それぞれの前記半導体素子に接合すべき前記半導体素子用放熱板を、前記それぞれの半導体素子の接合すべき面に載置し、前記半導体素子用放熱板と前記半導体素子とを接合する請求項1記載の半導体パッケージの製造方法。

- 前記凸状曲面の部分の材料が、前記半導体素子用放熱板の他の部分と異なる材料で形成した前記半導体素子用放熱板を使用し、前記自動面合せ工程終了後、前記凸状曲面の部分を除去することを特徴とする請求項1又は2記載の半導体パッケージの製造方法。

- 半導体素子を搭載した配線基板と、

半導体素子用放熱板とを有し、

前記半導体素子用放熱板は、前記半導体素子に接合され、かつ、半導体素子との接合面と反対側の面の一部又は全部に、凸状曲面の部分を形成している半導体パッケージ。 - 前記凸状曲面の部分は、前記半導体素子用放熱板の他の部分と異なる材料で形成した請求項4記載の半導体パッケージ。

- 前記半導体素子用放熱板は、前記半導体素子の占有空間を確保する凹部を有し、かつ、前記凹部を形成する周壁と前記配線基板とが接合していることを特徴とする請求項4又は5記載の半導体パッケージ。

- 前記配線基板は前記半導体素子を収容するキャビティを有し、前記半導体素子用放熱板と、前記配線基板における前記キャビティ周縁部とが接合していることを特徴とする請求項4又は5記載の半導体パッケージ。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009195737A JP2011049311A (ja) | 2009-08-26 | 2009-08-26 | 半導体パッケージ及び製造方法 |

| US12/861,008 US20110049702A1 (en) | 2009-08-26 | 2010-08-23 | Semiconductor package and method of producing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009195737A JP2011049311A (ja) | 2009-08-26 | 2009-08-26 | 半導体パッケージ及び製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011049311A true JP2011049311A (ja) | 2011-03-10 |

| JP2011049311A5 JP2011049311A5 (ja) | 2012-09-06 |

Family

ID=43623617

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009195737A Pending JP2011049311A (ja) | 2009-08-26 | 2009-08-26 | 半導体パッケージ及び製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20110049702A1 (ja) |

| JP (1) | JP2011049311A (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103954260A (zh) * | 2014-05-28 | 2014-07-30 | 苏州艾酷玛赫设备制造有限公司 | 汽车散热器检测装置 |

| US10607857B2 (en) * | 2017-12-06 | 2020-03-31 | Indium Corporation | Semiconductor device assembly including a thermal interface bond between a semiconductor die and a passive heat exchanger |

| TR201816893A2 (tr) * | 2018-11-09 | 2019-02-21 | Kale Oto Radyatoer Sanayi Ve Ticaret Anonim Sirketi | Çok Sıra Tüplü Otomatik Radyatör Dizme Makinesi |

| US11710677B2 (en) * | 2019-07-08 | 2023-07-25 | Intel Corporation | Ultraviolet (UV)-curable sealant in a microelectronic package |

| US11842944B2 (en) * | 2019-12-26 | 2023-12-12 | Intel Corporation | IC assemblies including die perimeter frames suitable for containing thermal interface materials |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01220852A (ja) * | 1988-02-29 | 1989-09-04 | Hitachi Ltd | 半導体装置 |

| JPH0269962A (ja) * | 1988-09-05 | 1990-03-08 | Sumitomo Electric Ind Ltd | 半導体デバイス製造装置 |

| JPH06112350A (ja) * | 1992-09-30 | 1994-04-22 | Mitsubishi Electric Corp | 半導体装置 |

| JP2005217295A (ja) * | 2004-01-30 | 2005-08-11 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP2006049732A (ja) * | 2004-08-09 | 2006-02-16 | Sony Corp | 半導体パッケージの製造方法および半導体パッケージの製造装置 |

| WO2007084572A2 (en) * | 2006-01-18 | 2007-07-26 | Honeywell International Inc. | Thermal interconnect and interface systems, methods of production and uses thereof |

| JP2008244473A (ja) * | 2007-03-26 | 2008-10-09 | Endicott Interconnect Technologies Inc | スタンドオフ付きフレキシブル電子回路パッケージ、及びその製造方法 |

| JP2008300561A (ja) * | 2007-05-30 | 2008-12-11 | Renesas Technology Corp | 半導体装置の製造方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5900675A (en) * | 1997-04-21 | 1999-05-04 | International Business Machines Corporation | Organic controlled collapse chip connector (C4) ball grid array (BGA) chip carrier with dual thermal expansion rates |

| US6288900B1 (en) * | 1999-12-02 | 2001-09-11 | International Business Machines Corporation | Warpage compensating heat spreader |

| JP3881488B2 (ja) * | 1999-12-13 | 2007-02-14 | 株式会社東芝 | 回路モジュールの冷却装置およびこの冷却装置を有する電子機器 |

| US7061102B2 (en) * | 2001-06-11 | 2006-06-13 | Xilinx, Inc. | High performance flipchip package that incorporates heat removal with minimal thermal mismatch |

| JP3868777B2 (ja) * | 2001-09-11 | 2007-01-17 | 株式会社東芝 | 半導体装置 |

| US6748350B2 (en) * | 2001-09-27 | 2004-06-08 | Intel Corporation | Method to compensate for stress between heat spreader and thermal interface material |

| US6848172B2 (en) * | 2001-12-21 | 2005-02-01 | Intel Corporation | Device and method for package warp compensation in an integrated heat spreader |

| US20050155743A1 (en) * | 2002-06-28 | 2005-07-21 | Getz George Jr. | Composite heat sink with metal base and graphite fins |

| US6930884B2 (en) * | 2003-06-11 | 2005-08-16 | Hewlett-Packard Development Company, L.P. | Land grid array assembly using a compressive liquid |

| US7319591B2 (en) * | 2005-05-26 | 2008-01-15 | International Business Machines Corporation | Optimized thermally conductive plate and attachment method for enhanced thermal performance and reliability of flip chip organic packages |

| US20080157345A1 (en) * | 2006-12-29 | 2008-07-03 | Daoqiang Lu | Curved heat spreader design for electronic assemblies |

| US7737550B2 (en) * | 2007-08-30 | 2010-06-15 | International Business Machines Corporation | Optimization of electronic package geometry for thermal dissipation |

| US7795724B2 (en) * | 2007-08-30 | 2010-09-14 | International Business Machines Corporation | Sandwiched organic LGA structure |

-

2009

- 2009-08-26 JP JP2009195737A patent/JP2011049311A/ja active Pending

-

2010

- 2010-08-23 US US12/861,008 patent/US20110049702A1/en not_active Abandoned

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01220852A (ja) * | 1988-02-29 | 1989-09-04 | Hitachi Ltd | 半導体装置 |

| JPH0269962A (ja) * | 1988-09-05 | 1990-03-08 | Sumitomo Electric Ind Ltd | 半導体デバイス製造装置 |

| JPH06112350A (ja) * | 1992-09-30 | 1994-04-22 | Mitsubishi Electric Corp | 半導体装置 |

| JP2005217295A (ja) * | 2004-01-30 | 2005-08-11 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP2006049732A (ja) * | 2004-08-09 | 2006-02-16 | Sony Corp | 半導体パッケージの製造方法および半導体パッケージの製造装置 |

| WO2007084572A2 (en) * | 2006-01-18 | 2007-07-26 | Honeywell International Inc. | Thermal interconnect and interface systems, methods of production and uses thereof |

| JP2008244473A (ja) * | 2007-03-26 | 2008-10-09 | Endicott Interconnect Technologies Inc | スタンドオフ付きフレキシブル電子回路パッケージ、及びその製造方法 |

| JP2008300561A (ja) * | 2007-05-30 | 2008-12-11 | Renesas Technology Corp | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20110049702A1 (en) | 2011-03-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5635247B2 (ja) | マルチチップモジュール | |

| JP5387685B2 (ja) | 半導体装置の製造方法 | |

| US7563651B2 (en) | Method of fabricating a substrate with a concave surface | |

| US7271480B2 (en) | Constraint stiffener design | |

| TW200411863A (en) | Flip-chip package | |

| US8334174B2 (en) | Chip scale package and fabrication method thereof | |

| US8823164B2 (en) | Heatsink attachment module | |

| TWI228806B (en) | Flip chip package | |

| JP2023175042A (ja) | 電子部品装置の製造方法及び電子部品装置 | |

| JP2013243339A (ja) | 電子部品、電子モジュールおよびこれらの製造方法。 | |

| JP2011049311A (ja) | 半導体パッケージ及び製造方法 | |

| US11658099B2 (en) | Flip chip curved sidewall self-alignment features for substrate and method for manufacturing the self-alignment features | |

| US20170287873A1 (en) | Electronic assembly components with corner adhesive for warpage reduction during thermal processing | |

| TWI255488B (en) | Semiconductor device and multilayer substrate therefor | |

| JP2016162985A (ja) | 半導体装置の製造方法 | |

| US20090057866A1 (en) | Microelectronic Package Having Second Level Interconnects Including Stud Bumps and Method of Forming Same | |

| JP4335263B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US8237275B2 (en) | Tungsten stiffener for flexible substrate assembly | |

| TW200810050A (en) | Package structure and heat sink module thereof | |

| TWI253128B (en) | Method of manufacturing wafer level chip size package | |

| US20040075990A1 (en) | Packaging integrated circuits with adhesive posts | |

| JP2005064118A (ja) | 半導体装置およびその製造方法 | |

| JP2013012570A (ja) | 半導体装置および半導体装置の製造方法 | |

| TWI271839B (en) | Chip package process and heat sink structure thereof | |

| JP2001144215A (ja) | フリップチップ実装体 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120723 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120723 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130109 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130205 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130910 |