JP2010146474A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2010146474A JP2010146474A JP2008325702A JP2008325702A JP2010146474A JP 2010146474 A JP2010146474 A JP 2010146474A JP 2008325702 A JP2008325702 A JP 2008325702A JP 2008325702 A JP2008325702 A JP 2008325702A JP 2010146474 A JP2010146474 A JP 2010146474A

- Authority

- JP

- Japan

- Prior art keywords

- arithmetic processing

- storage

- voltage

- period

- storage device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Abstract

【解決手段】メモリが階層構造となっているシステムにおいて、キャッシュミスが生じた後、メインメモリの先頭アドレスの検出に入った時に、メインメモリの先頭アドレスを検出する命令を検出して演算器を第1の低電力モードに切り替える。また、先頭アドレスが見つかった後、メモリより演算器が備えるキャッシュメモリへの格納と平行して行われる演算器の動作を第2の低電力モードに切り替えて行うものである。

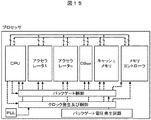

【選択図】図1

Description

リーク電流やしきい値電圧を制御する手段としては、1996年、IEEE, Journal of Solid-State Circuits, VOL.31, No.11、1770頁〜1779(非特許文献1)の"A 0.9-V, 150-MHz, 10-mW, 4 mm2, 2-D Discrete Cosine Transform Core Processor with Variable Threshold-Voltage (VT) Scheme"に記載のように、CMOSトランジスタの基板(ウエル)に電圧を印加し(この文献のFig.2を参照)、することが知られている。また、2005 年、IEEE International Electron Device Meeting Technical Digest Papers pp. 631-634(非特許文献2)や、特開2007-042730号公報(特許文献4)に開示されるように完全空乏(FD)型のSOI構造におけるCMOSトランジスタにおいて、その埋め込み酸化膜(BOX)層が30nm以下と薄いことを特徴としたトランジスタを用い、これにより、このBOX層をゲート絶縁膜と見立てたバックゲートを駆動してしきい値電圧を制御する手段が知られている。また、特開2004-318502にも開示されているように、電源と回路ブロックの間に別のMOSトランジスタを挿入する方法も知られている。

上記のみでも効果は大きいが、メモリより演算器が備えるキャッシュメモリへの格納の転送速度は一般に演算器がキャッシュメモリを用いて行う演算速度よりも一桁以上遅い。よって、第2の手段により、この期間に演算器が第2の低電力モードである低速かつしきい値電圧がキャッシュメモリを用いて行う時よりも高い値とできることにより、本来の全体の動作性能は落さずに、低電力化が可能となるのである。

プロセッサに対してレジスタ−キャッシュ−主記憶−ファイル記憶と構成され、一般にプロセッサに近いほど、スピードは速いが容量は小さい。プロセッサは、図1の演算を行う回路ブロックPUやCPUであり、図1では省略しているが実行中又は次に実行する命令やデータを蓄えておくレジスタを有している。この下にはキャッシュがあり、図1のキャッシュメモリCMなどでありプロセッサが当面の演算を行うのに必要なデータを蓄えておく。このキャッシュはプロセッサの動作速度と同じか近い周波数(1/2や1/4)と高速に動作する。主記憶は、このキャッシュに入りきれない情報を蓄えておくものであり、キャッシュよりも低速であるが大きな記憶容量を備えている。このメモリとキャッシュメモリとのデータのやり取りは、纏まった大きさの単位で行われる。この動作は、先頭のアドレスをアクセスする動作と纏まった単位のデータを連続的に主記憶よりキャッシュへ転送する動作の2つとからなる。このうち、後者の転送する動作はプロセッサの周波数の一桁低い周波数程度であるが、前者の先頭のアドレスをアクセスする動作はこれよりも低速である。これは、バスの衝突を避けるためにプロセッサと主記憶が記憶内容を特定したことを確認する動作や、主記憶を構成するメモリのアクセス時間の制約などによる。これを制御しているのがメモリコントローラである。本発明は、先頭のアドレスをアクセスする動作が半導体装置では起こることを利用し、その間のプロセッサを低速動作又は停止させ、MOSトランジスタのしきい値電圧も高くしてリーク電力を抑え、低電力化を図るものである。この先頭のアドレスをアクセスする動作は通常の動作で起こるため、本発明によって処理性能が低くなることはない。メモリの階層構造としては、更にファイル記憶がある。これは、HDDやフラッシュメモリで構成された巨大な容量のメモリであるが、一般的に速度は遅い。よって、一般的な計算では、これに必要な情報は一旦主記憶に取り込んでから行う。又は、動作中であれば、不要な情報内容となった主記憶の部分に予測してファイル記憶内容を転送するなどこの動作が見えないようにする工夫をする。ファイル記憶にアクセスしている時間は長いため、このときはプロセッサを止めてしまうことは行われてきた。本発明は、主記憶の動作を解析した結果、ここに動作速度を損なわずに電力を削減できる状態を見出し、考案したものである。

図10において、(a)は回路図であり、(b)はバックゲートBGの電圧VBGSを変えた時のドレイン電流IDSのゲート・ソース間電圧VGS依存性である。この(b)から例えばゲート・ソース間電圧VGSが0Vの点の電流、すなわちオフ状態でのリーク電流を値を見ると、BGの電圧VBGSが0Vの時は、ゲート幅1ミクロンメートル当り10のマイナス10乗アンペアであるのに対して、VBGSが1Vの時は、3桁以上大きな電流が流れることが分かる。また、この図は縦軸が対数であるのでわかりにくいが、VGSが1Vの点、すなわちオン電流においても20%程、VBGSが1Vの方が、VBGSが0Vの場合と比較して大きい。このように、同じゲート・ソース間電圧VGSにおいて、バックゲートの電圧VBGを変えることで異なる電流を取ることができる。よって、リーク電流の小さな状態、又はオン電流の大きな状態を作り出すことができるのである。

図12と図13には、プロセッサと同一チップ上に形成されるメモリセルの例を示す。

Claims (8)

- 演算処理装置と、

前記演算処理装置で使用される命令及びデータを含む記憶情報を蓄えた、アクセス速度が前記演算処理装置の動作速度よりも遅い大容量記憶装置と、

前記記憶情報の少なくとも一部を蓄えた、アクセス速度が前記演算処理装置の動作速度よりも遅く、前記大容量記憶装置のアクセス速度よりも速い小規模記憶装置と、

前記大容量記憶装置を制御する記憶制御装置と、を有し、

前記演算処理装置が、ゲート端子とドレイン端子とソース端子と基板端子とを具備してなるCMOSトランジスタで構成され、

前記CMOSトランジスタの基板端子に、前記小規模記憶装置に記憶された記憶情報が前記演算処理装置において実行される第1の期間では第1の電圧が印加され、

前記大容量記憶装置が、前記演算処理装置で必要な記憶情報を前記演算処理装置へ送る準備を行う第2の期間では第2の電圧が印加され、

前記第1の電圧と前記第2の電圧とは異なる電圧であって、前記第1の電圧は前記CMOSトランジスタのしきい値電圧の絶対値を大きくする電圧であることを特徴とする半導体装置。 - 前記第2の期間が、前記演算処理装置が前記小規模記憶装置に必要な記憶情報が無いことを検知し、前記記憶制御装置が前記大容量記憶装置へ前記演算処理装置が必要な記憶情報を求め、その後、前記記憶制御装置が前記大容量記憶装置の記憶情報の中より必要な記憶情報の先頭アドレスを検知し、前記記憶制御装置の制御により前記大容量記憶装置から必要なデータを送り始めるまでの期間であることを特徴とする請求項1記載の半導体装置。

- 前記CMOSトランジスタは、絶縁膜上に構成されたSOI構造を有し、ゲート端子と、ドレイン端子と、ソース端子と、該絶縁膜の下に設けられた半導体領域と、該半導体領域に電圧を印加できるバックゲート端子とを備え、

前記第2の期間において、前記バックゲート端子に、前記CMOSトランジスタのしきい値電圧の絶対値を大きくする電圧であって、前記第1の期間とは異なる電圧が印加されることを特徴とする請求項1記載の半導体装置。 - 前記第2の期間が、前記演算処理装置が前記小規模記憶装置に必要な記憶情報が無いことを検知し、前記記憶制御装置が前記大容量記憶装置へ前記演算処理装置が必要な記憶情報を求め、その後、前記記憶制御装置が前記大容量記憶装置の記憶情報の中より必要な記憶情報の先頭アドレスを検知し、前記記憶制御装置の制御により前記大容量記憶装置から必要なデータを送り始めるまでの期間であることを特徴とする請求項3記載の半導体装置。

- 演算処理装置と、

前記演算処理装置が使用する命令及びデータを含む記憶情報を蓄えた、アクセス速度が前記演算処理装置の動作速度よりも遅い大容量記憶装置と、

前記記憶情報の少なくとも一部を蓄えた、アクセス速度が前記演算処理装置の動作速度よりも遅く、前記大容量記憶装置のアクセス速度よりも速い小規模記憶装置と、

前記大容量記憶装置を制御する記憶制御装置と、を有し、

前記演算処理装置が、ゲート端子とドレイン端子とソース端子と基板端子とを具備してなるCMOSトランジスタで構成され、

前記演算処理装置が前記小規模記憶装置に記憶された記憶情報を用いて演算を実行する第1の期間において、前記CMOSトランジスタの基板端子に第1の電圧が印加され、前記演算処理装置は第1のクロック周波数に同期して動作し、

前記大容量記憶装置が、前記演算処理装置に必要な記憶情報を前記演算処理装置へ送る準備を行う第2の期間において、前記演算処理装置は前記第1のクロック周波数より遅い周波数を有する第2のクロック周波数に同期して動作し、前記基板端子には、前記CMOSトランジスタのしきい値電圧の絶対値を大きくする前記第1の電圧とは異なる第2の電圧が印加されることを特徴とする半導体装置。 - 前記第2の期間が、前記演算処理装置が前記小規模記憶装置に必要な記憶情報が無いことを検知し、前記記憶制御装置が前記大容量記憶装置へ前記演算処理装置が必要な記憶情報を求め、その後、前記記憶制御装置が前記大容量記憶装置の記憶情報の中より必要な記憶情報の先頭アドレスを検知し、前記記憶制御装置の制御により前記大容量記憶装置から必要なデータを送り始めるまでの期間であることを特徴とする請求項5記載の半導体装置。

- 前記CMOSトランジスタは、絶縁膜上に構成されたSOI構造を有し、ゲート端子と、ドレイン端子と、ソース端子と、該絶縁膜の下に設けられた半導体領域と、該半導体領域に電圧を印加できるバックゲート端子とを備え、

前記第2の期間において、前記バックゲート端子に、前記CMOSトランジスタのしきい値電圧の絶対値を大きくする電圧であって、前記第1の期間とは異なる電圧が印加されることを特徴とする請求項5記載の半導体装置。 - 前記第2の期間が、前記演算処理装置が前記小規模記憶装置に必要な記憶情報が無いことを検知し、前記記憶制御装置が前記大容量記憶装置へ前記演算処理装置が必要な記憶情報を求め、その後、前記記憶制御装置が前記大容量記憶装置の記憶情報の中より必要な記憶情報の先頭アドレスを検知し、前記記憶制御装置の制御により前記大容量記憶装置から必要なデータを送り始めるまでの期間であることを特徴とする請求項7記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008325702A JP4966956B2 (ja) | 2008-12-22 | 2008-12-22 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008325702A JP4966956B2 (ja) | 2008-12-22 | 2008-12-22 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010146474A true JP2010146474A (ja) | 2010-07-01 |

| JP4966956B2 JP4966956B2 (ja) | 2012-07-04 |

Family

ID=42566816

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008325702A Expired - Fee Related JP4966956B2 (ja) | 2008-12-22 | 2008-12-22 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4966956B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015148890A (ja) * | 2014-02-05 | 2015-08-20 | 富士通株式会社 | 情報処理装置、情報処理システム、および情報処理システムの制御方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1998022863A1 (fr) * | 1996-11-21 | 1998-05-28 | Hitachi, Ltd. | Processeur a faible consommation d'energie |

| JP2000214967A (ja) * | 1998-11-20 | 2000-08-04 | Hitachi Ltd | 低電力情報処理装置 |

| JP2002006979A (ja) * | 2000-06-19 | 2002-01-11 | Seiko Epson Corp | クロック制御装置、半導体集積回路装置、マイクロコンピュータ及び電子機器 |

| JP2005115769A (ja) * | 2003-10-09 | 2005-04-28 | Nec Corp | 情報処理装置 |

| JP2005196430A (ja) * | 2004-01-07 | 2005-07-21 | Hiroshi Nakamura | 半導体装置および半導体装置の電源電圧/クロック周波数制御方法 |

| JP2007042730A (ja) * | 2005-08-01 | 2007-02-15 | Renesas Technology Corp | 半導体装置およびそれを用いた半導体集積回路 |

| JP2007193433A (ja) * | 2006-01-17 | 2007-08-02 | Matsushita Electric Ind Co Ltd | 情報処理装置 |

-

2008

- 2008-12-22 JP JP2008325702A patent/JP4966956B2/ja not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1998022863A1 (fr) * | 1996-11-21 | 1998-05-28 | Hitachi, Ltd. | Processeur a faible consommation d'energie |

| JP2000214967A (ja) * | 1998-11-20 | 2000-08-04 | Hitachi Ltd | 低電力情報処理装置 |

| JP2002006979A (ja) * | 2000-06-19 | 2002-01-11 | Seiko Epson Corp | クロック制御装置、半導体集積回路装置、マイクロコンピュータ及び電子機器 |

| JP2005115769A (ja) * | 2003-10-09 | 2005-04-28 | Nec Corp | 情報処理装置 |

| JP2005196430A (ja) * | 2004-01-07 | 2005-07-21 | Hiroshi Nakamura | 半導体装置および半導体装置の電源電圧/クロック周波数制御方法 |

| JP2007042730A (ja) * | 2005-08-01 | 2007-02-15 | Renesas Technology Corp | 半導体装置およびそれを用いた半導体集積回路 |

| JP2007193433A (ja) * | 2006-01-17 | 2007-08-02 | Matsushita Electric Ind Co Ltd | 情報処理装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015148890A (ja) * | 2014-02-05 | 2015-08-20 | 富士通株式会社 | 情報処理装置、情報処理システム、および情報処理システムの制御方法 |

| US9710047B2 (en) | 2014-02-05 | 2017-07-18 | Fujitsu Limited | Apparatus, system, and method for varying a clock frequency or voltage during a memory page transfer |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4966956B2 (ja) | 2012-07-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20200089407A1 (en) | Inter zone write for zoned namespaces | |

| KR101249648B1 (ko) | 반도체장치 및 그것을 이용한 반도체집적회로 | |

| US7683669B2 (en) | Semiconductor device, CPU, image processing circuit and electronic device, and driving method of semiconductor device | |

| US9703704B2 (en) | Semiconductor device | |

| JP3884914B2 (ja) | 半導体装置 | |

| JP2020042892A (ja) | 半導体装置、及びダイナミックロジック回路 | |

| US9886997B2 (en) | Semiconductor device for reducing an instantaneous voltage drop | |

| Shuto et al. | Nonvolatile static random access memory based on spin-transistor architecture | |

| JP5364125B2 (ja) | 半導体装置 | |

| JP6420165B2 (ja) | 半導体装置 | |

| WO2009092163A1 (en) | Operational mode control in serial-connected memory based on identifier | |

| TW459230B (en) | Static RAM having word line driving circuitry shared by all the memory cells provided therein | |

| JP2009266339A (ja) | 半導体記憶装置とその半導体記憶装置を用いた電子機器 | |

| JP4966956B2 (ja) | 半導体装置 | |

| Kawahara et al. | Green computing with emerging memory | |

| Shastri et al. | Read write stability with leakage minimization of 4t SRAM cell for nano CMOS technology | |

| JP4972634B2 (ja) | 半導体装置 | |

| US20080024197A1 (en) | Method and architecture for power management of an electronic device | |

| Sakthimurugan et al. | Designing low power magentic flip flop in 45 nm FDSOI technology for large scale cluster based engineering application | |

| WO2023138219A1 (zh) | 一种存储器、时序控制方法及电子设备 | |

| Akashe et al. | Read write stability of Dual-VT 7T SRAM Cell at 45 nm technology | |

| US20230317145A1 (en) | Method and apparatus to implement an integrated circuit to operate based on data access characteristics | |

| US20230315331A1 (en) | Method and apparatus to implement an integrated circuit including both dynamic random-access memory (dram) and static random-access memory (sram) | |

| Srivastava et al. | Effect of technology scale-down on power reduction strategies | |

| Rahman et al. | A new Tunnel-FET based RAM concept for ultra-low power applications |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111031 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111213 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120213 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120306 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120402 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150406 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |