JP2010141933A - 高性能信号発生 - Google Patents

高性能信号発生 Download PDFInfo

- Publication number

- JP2010141933A JP2010141933A JP2010057327A JP2010057327A JP2010141933A JP 2010141933 A JP2010141933 A JP 2010141933A JP 2010057327 A JP2010057327 A JP 2010057327A JP 2010057327 A JP2010057327 A JP 2010057327A JP 2010141933 A JP2010141933 A JP 2010141933A

- Authority

- JP

- Japan

- Prior art keywords

- phase

- signal

- digital

- frequency

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R25/00—Arrangements for measuring phase angle between a voltage and a current or between voltages or currents

- G01R25/04—Arrangements for measuring phase angle between a voltage and a current or between voltages or currents involving adjustment of a phase shifter to produce a predetermined phase difference, e.g. zero difference

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/31708—Analysis of signal quality

- G01R31/31709—Jitter measurements; Jitter generators

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/319—Tester hardware, i.e. output processing circuits

- G01R31/31917—Stimuli generation or application of test patterns to the device under test [DUT]

- G01R31/31922—Timing generation or clock distribution

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03D—DEMODULATION OR TRANSFERENCE OF MODULATION FROM ONE CARRIER TO ANOTHER

- H03D13/00—Circuits for comparing the phase or frequency of two mutually-independent oscillations

- H03D13/003—Circuits for comparing the phase or frequency of two mutually-independent oscillations in which both oscillations are converted by logic means into pulses which are applied to filtering or integrating means

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/091—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector using a sampling device

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/16—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/087—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using at least two phase detectors or a frequency and phase detector in the loop

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Nonlinear Science (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

- Manipulation Of Pulses (AREA)

- Measuring Phase Differences (AREA)

Abstract

【解決手段】位相検出器は、デジタル基準信号とサンプリングされた入力信号の間の位相差を蓄積し、位相誤差の指標を作る。位相検出器は、周波数合成器において用いられ、低位相ノイズおよび正確な位相制御で信号を発生することができる利点がある。さらに、この種類のシンセサイザは、低ジッタのクロックおよび波形を生成するATEシステムおよび他の電子システムにおいて、ビルディングブロックのように用いられる。

【選択図】 図3

Description

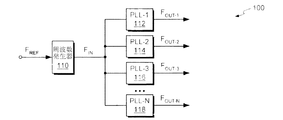

110 周波数発生器

112 位相固定ループ

200 位相固定ループ

210 アナログ位相検出器

212 高利得ループフィルタ

216 周波数デバイダ

218 周波数デバイダ

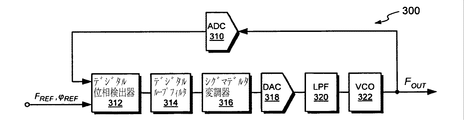

300 周波数合成器

310 変換器

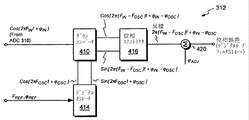

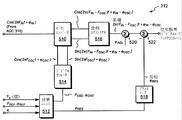

312 デジタル位相検出器

314 デジタルループフィルタ

316 シグマデルタ変調器

320 アナログフィルタ

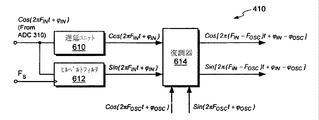

410 ダウンコンバータ

414 デジタルオシレータ

416 位相エクストラクタ

420 加算器

510 ダウンコンバータ

512 計算ユニット

514 デジタルオシレータ

516 位相エクストラクタ

518 アキュムレータ

520 加算器

522 加算器

610 遅延ユニット

612 ヒルベルトフィルタ

614 復調器

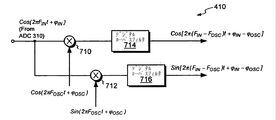

710 マルチプライヤ

712 マルチプライヤ

714 デジタルローパスフィルタ

1010 ホストコンピュータ

1012 自動検査システム

1014 システムクロック

1016a 周波数合成器

1018 パターン発生器

1020 アナログ計器

1022 デジタイザ

1026、1028、1030 デジタルピン

Claims (22)

- 周波数および位相を有するサンプル信号を受け取る入力と、

所定周波数および位相を示す値に対応する基準信号を生成するデジタルオシレータと、

前記入力および前記デジタルオシレータと結合され、前記サンプル信号の前記周波数と前記基準信号の前記周波数の間の差を示す周波数、および前記サンプル信号の前記位相と前記基準信号の前記位相の間の差を示す位相を有する直角位相差信号を生成するダウンコンバータと、

前記直角位相差信号を受け取るために前記ダウンコンバータと結合された第1およびの第2の入力、および前記直角位相差信号の累積位相を示す値を生成する出力を有する位相エクストラクタと、を備えることを特徴とする位相検出器。 - 請求項1に記載の位相検出器であって、前記基準信号が、Cos(2πFOSCt+jOSC)の形を概ね有する第1の構成部分、およびSin(2πFOSCt+jOSC)の形を概ね有する第2の構成部分を含む直角位相基準信号であることを特徴とする位相検出器。

- 請求項2に記載の位相検出器であって、前記サンプル信号がCos(2πFint+jin)の形を概ね有し、前記ダウンコンバータが、

前記位相検出器の前記入力と結合された入力、およびSin(2πFint+jin)の形を概ね有する、前記サンプル信号の位相をシフトしたバージョンを発生する出力を有するヒルベルトフィルタと、

前記位相検出器の前記入力と結合された第1の入力、前記ヒルベルトフィルタの前記出力と結合された第2の入力、前記直角位相基準信号の前記第1および第2の構成部分と個々に結合された第3および第4の入力、および前記直角位相差信号を供給する第1および第2の出力を有する復調器と、を備えることを特徴とする位相検出器。 - 請求項2に記載の位相検出器であって、前記直角位相差信号が第1の構成部分および第2の構成部分を備え、前記ダウンコンバータが、

前記サンプル信号と前記直角位相基準信号の前記第1の構成部分との積を生成する第1のマルチプライヤと、

前記サンプル信号と前記直角位相基準信号の前記第2の構成部分との積を生成する第2のマルチプライヤと、

前記直角位相差信号の前記第1の構成部分を生成するために、前記第1のマルチプライヤの前記積をフィルターにかける第1のデジタルフィルタと、

前記直角位相差信号の前記第2の構成部分を生成するために、前記第2のマルチプライヤの前記積をフィルターにかける第2のデジタルフィルタと、を備えることを特徴とする位相検出器。 - 請求項1に記載の位相検出器であって、前記位相エクストラクタがATAN2関数を実行することを特徴とする位相検出器。

- 請求項1に記載の位相検出器において、さらに、前記位相エクストラクタの前記出力に調整可能な位相値を付加するために、前記位相エクストラクタの前記出力と結合された加算器を備えることを特徴とする位相検出器。

- 請求項1に記載の位相検出器において、さらに、

前記所定周波数および位相を示す前記値を、一次的な構成部分および二次的な構成部分に分割する計算ユニットと、

前記二次的な構成部分を受け取るために前記計算ユニットと結合された入力、および前記二次的な構成部分によって示された位相値を蓄積する出力を有するアキュムレータと、前記位相エクストラクタの前記出力と結合された第1の入力、前記アキュムレータの前記出力と結合された第2の入力、および前記位相エクストラクタの前記出力と前記アキュムレータの前記出力の間の差を発生する出力を有する加算器と、を備え、

前記デジタルオシレータが、前記一次的な構成部分を受け取るために前記計算ユニットと結合されることを特徴とする位相検出器。 - 請求項7に記載の位相検出器であって、

前記デジタルオシレータがFsのクロックレートで動作し、

KおよびLを両方とも整数とした時、FsがLサイクルを完了するのと同じ時間の間に、前記一次的な構成部分によって規定されるデジタル波形がKサイクルを完了することを特徴とする位相検出器。 - 請求項8に記載の位相検出器であって、前記デジタルオシレータが、前記直角位相基準信号の値とFsの連続したサイクルとを関連づける索引テーブルを備えることを特徴とする位相検出器。

- 請求項1に記載の位相検出器であって、前記デジタルオシレータの前記周波数が可調整であることを特徴とする位相検出器。

- 請求項10に記載の位相検出器であって、前記デジタルオシレータの前記位相が可調整であることを特徴とする位相検出器。

- 請求項1に記載の位相検出器であって、前記デジタルオシレータの前記周波数および位相がプログラマブルであることを特徴とする位相検出器。

- 周波数を有するサンプル信号を受け取る入力と、

所定周波数を有する基準信号を生成するデジタルオシレータと、

前記入力および前記デジタルオシレータと結合され、前記サンプル信号の前記周波数と前記基準信号の前記周波数の間の差を示す周波数を有する差信号を生成する手段と、

前記差信号を生成する前記手段と結合され、前記差信号の累積位相を示す値を生成する手段と、を備えることを特徴とする位相検出器。 - 所望の信号の周波数を示す値を受け取る第1の入力、フィードバック信号を受け取る第2の入力、および前記所望の信号と前記フィードバック信号の間の累積的な位相差を示すデジタル信号を供給する出力を有するデジタル位相検出器と、

前記デジタル位相検出器の前記出力と結合された入力、およびアナログ出力信号を供給する出力を有するDAC(DA変換器)と、

前記DACの前記出力と結合された入力、および周期的な出力信号を生成する出力を有するVCO(電圧制御発振器)と、

前記VCOの前記出力と結合された入力、および前記デジタル位相検出器の前記第2の入力と結合され、前記フィードバック信号を供給する出力を有するADC(AD変換器)と、を備えることを特徴とする周波数合成器。 - 請求項14に記載の周波数合成器において、さらに、前記デジタル位相検出器と前記DACの間に直列に結合されたデジタルループフィルタを備えることを特徴とする周波数合成器。

- 請求項15に記載の周波数合成器であって、前記デジタルループフィルタが、偽物の周波数成分を排除するために構成され、配置されることを特徴とする周波数合成器。

- 請求項15に記載の周波数合成器において、さらに、前記デジタルループフィルタと前記DACの間に直列に結合されたシグマデルタ変調器を備えることを特徴とする周波数合成器。

- 請求項14に記載の周波数合成器において、さらに、前記DACの前記出力を平滑化するために、前記DACと前記VCOの間に直列に結合されたアナログフィルタを備えることを特徴とする周波数合成器。

- 請求項14に記載の周波数合成器において、周期的な波形を生成するために自動試験装置と共に用いられることを特徴とする周波数合成器。

- 周期的なサンプル信号とデジタル基準信号の間の位相誤差を決定する方法であって、

所定周波数において前記デジタル基準信号を生成すること、

前記周期的なサンプル信号と前記デジタル基準信号の間の累積位相差を示すデジタル位相誤差を生成すること

を含むことを特徴とする方法。 - 請求項20に記載の方法であって、前記デジタル位相誤差を生成するステップが、

前記サンプリングされた周期信号の前記周波数と前記デジタル基準信号の前記周波数の間の差を示す周波数を有するデジタル差信号を生成すること、

前記デジタル差信号から累積位相信号を引き出すこと

を含むことを特徴とする方法。 - 既知の周波数を有するデジタル基準信号を生成すること、

前記デジタル基準信号の前記周波数とデジタルフィードバック信号の周波数の間の差を示す周波数を有するデジタル差信号を生成すること、

前記デジタル差信号から累積位相信号を引き出すこと、

前記累積位相信号を周期的なアナログ信号に変換すること、

前記デジタルフィードバック信号を発生するために、前記アナログ周期信号をデジタル化することを含むことを特徴とする周期信号を生成する方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/817,780 US7061276B2 (en) | 2004-04-02 | 2004-04-02 | Digital phase detector |

| US10/817780 | 2004-04-02 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005086535A Division JP2005295544A (ja) | 2004-04-02 | 2005-03-24 | 高性能信号発生 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010141933A true JP2010141933A (ja) | 2010-06-24 |

| JP5154594B2 JP5154594B2 (ja) | 2013-02-27 |

Family

ID=34912677

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005086535A Pending JP2005295544A (ja) | 2004-04-02 | 2005-03-24 | 高性能信号発生 |

| JP2010057327A Expired - Lifetime JP5154594B2 (ja) | 2004-04-02 | 2010-03-15 | 高性能信号発生 |

| JP2010057324A Expired - Lifetime JP5165712B2 (ja) | 2004-04-02 | 2010-03-15 | 高性能信号発生 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005086535A Pending JP2005295544A (ja) | 2004-04-02 | 2005-03-24 | 高性能信号発生 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010057324A Expired - Lifetime JP5165712B2 (ja) | 2004-04-02 | 2010-03-15 | 高性能信号発生 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US7061276B2 (ja) |

| EP (1) | EP1584929A3 (ja) |

| JP (3) | JP2005295544A (ja) |

| CN (1) | CN100481711C (ja) |

| TW (1) | TWI292656B (ja) |

Families Citing this family (52)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE10215087B4 (de) * | 2002-04-05 | 2004-08-19 | Infineon Technologies Ag | Verfahren und Vorrichtung zur Phasendetektion |

| DE102004006995B4 (de) * | 2004-02-12 | 2007-05-31 | Infineon Technologies Ag | Digitaler Phasenregelkreis für Sub-µ-Technologien |

| US7340219B2 (en) * | 2004-02-24 | 2008-03-04 | Texas Instruments Incorporated | Method and system for multisite RF transceiver testing |

| DE102004063935A1 (de) * | 2004-07-01 | 2006-03-30 | Krohne Meßtechnik GmbH & Co KG | Frequenzsynthesizer und Verfahren zum Betrieb eines Frequenzsynthesizers |

| US7557623B2 (en) * | 2005-04-18 | 2009-07-07 | Nxp B.V. | Circuit arrangement, in particular phase-locked loop, as well as corresponding method |

| US7711328B1 (en) | 2005-06-29 | 2010-05-04 | Xilinx, Inc. | Method of and circuit for sampling a frequency difference in an integrated circuit |

| US7635997B1 (en) * | 2005-06-29 | 2009-12-22 | Xilinx, Inc. | Circuit for and method of changing a frequency in a circuit |

| US7173462B1 (en) * | 2005-10-27 | 2007-02-06 | Mediatek Inc. | Second order delay-locked loop for data recovery |

| US7847641B2 (en) * | 2005-12-15 | 2010-12-07 | International Business Machines Corporation | Digital phase and frequency detector |

| US7443251B2 (en) * | 2005-12-15 | 2008-10-28 | International Business Machines Corporation | Digital phase and frequency detector |

| US7345549B2 (en) * | 2006-02-28 | 2008-03-18 | Teradyne, Inc. | Phase locking on aliased frequencies |

| US7680227B2 (en) * | 2006-03-02 | 2010-03-16 | Broadcom Corporation | Method and system for filter calibration using fractional-N frequency synthesized signals |

| JP4231532B2 (ja) * | 2006-06-29 | 2009-03-04 | 日本電波工業株式会社 | 周波数シンセサイザ |

| GB0622948D0 (en) | 2006-11-17 | 2006-12-27 | Zarlink Semiconductor Inc | A digital phase locked loop |

| US7586458B2 (en) * | 2007-03-19 | 2009-09-08 | Ahmadreza Rofougaran | Method and system for using a transformer for FM transmit and FM receive functionality |

| DE102007016642B4 (de) * | 2007-04-05 | 2015-12-17 | Austriamicrosystems Ag | Elektromechanisches System und Verfahren zum Betrieb eines elektromechanischen Systems |

| KR101341138B1 (ko) * | 2007-07-23 | 2013-12-13 | 테라다인 인코퍼레이티드 | 에일리어싱된 주파수에 대한 위상 고정 |

| US20090085674A1 (en) * | 2007-09-28 | 2009-04-02 | Ahmadreza Rofougaran | Method and system for signal generation via a pll with digital phase detection |

| US7724096B2 (en) * | 2007-09-28 | 2010-05-25 | Broadcom Corporation | Method and system for signal generation via a PLL with undersampled feedback |

| US20090085678A1 (en) * | 2007-09-28 | 2009-04-02 | Ahmadreza Rofougaran | Method and system for signal generation via a digitally controlled oscillator |

| CN101842987B (zh) * | 2007-11-12 | 2013-11-06 | 松下电器产业株式会社 | Pll电路和使用该pll电路的角速度传感器 |

| US20090243740A1 (en) * | 2008-03-27 | 2009-10-01 | Ahmadreza Rofougaran | Method and system for reduced jitter signal generation |

| US20090243741A1 (en) * | 2008-03-27 | 2009-10-01 | Ahmadreza Rofougaran | Method and system for processing signals via an oscillator load embedded in an integrated circuit (ic) package |

| US8086190B2 (en) * | 2008-03-27 | 2011-12-27 | Broadcom Corporation | Method and system for reconfigurable devices for multi-frequency coexistence |

| PL2149990T3 (pl) * | 2008-07-29 | 2011-10-31 | Siemens Ag | System, zwłaszcza do digitalizacji okresowego sygnału z ciągłym czasem i ciągłą wartością, ze stałą z góry określoną liczbą wartości próbkowania przypadającą na jeden okres |

| TW201230733A (en) * | 2011-01-12 | 2012-07-16 | Tsung-Hsien Lin | Receiver |

| KR20120125096A (ko) * | 2011-05-06 | 2012-11-14 | 삼성전자주식회사 | 디지털 제어 발진기를 포함하는 위상동기루프 회로 |

| US8862648B2 (en) | 2011-05-24 | 2014-10-14 | Taiwan Semiconductor Manufacturing Company, Ltd. | Fast filter calibration apparatus |

| US8513995B2 (en) * | 2011-07-28 | 2013-08-20 | Intel Corporation | System including circuitry providing multiple circuit paths for controlling a characteristic of a period signal |

| JP2013207737A (ja) * | 2012-03-29 | 2013-10-07 | Fujitsu Ltd | 位相検出回路、半導体装置及び位相検出方法 |

| CN103475363A (zh) * | 2013-09-04 | 2013-12-25 | 苏州苏尔达信息科技有限公司 | 一种二元相位比较器数字锁相环电路 |

| JP2015215684A (ja) | 2014-05-08 | 2015-12-03 | 富士ゼロックス株式会社 | 情報処理装置及び情報処理プログラム |

| US9246499B2 (en) * | 2014-05-21 | 2016-01-26 | Robert Bosch Gmbh | Digital phase lock loop circuit including finite impulse response filtering to reduce aliasing of quantization noise |

| JP6382342B2 (ja) * | 2014-12-08 | 2018-08-29 | 古野電気株式会社 | 基準信号発生装置 |

| US10126884B2 (en) * | 2014-12-22 | 2018-11-13 | Synaptics Incorporated | Asynchronous interference detection in a capacitive sensing system |

| US9755766B2 (en) * | 2015-12-07 | 2017-09-05 | Teradyne, Inc. | Front end module for automatic test equipment |

| DE102016115785A1 (de) | 2016-08-25 | 2018-03-01 | Infineon Technologies Ag | Integrierte RF-Schaltung mit Möglichkeit zum Testen von Phasenrauschen |

| JP6862900B2 (ja) * | 2017-02-22 | 2021-04-21 | セイコーエプソン株式会社 | 回路装置、物理量測定装置、電子機器及び移動体 |

| US11095295B2 (en) | 2018-06-26 | 2021-08-17 | Silicon Laboratories Inc. | Spur cancellation for spur measurement |

| CN109324215B (zh) * | 2018-09-21 | 2022-04-19 | 北京无线电计量测试研究所 | 一种基于dds的标准相位产生方法和装置 |

| US10680622B2 (en) * | 2018-09-27 | 2020-06-09 | Silicon Laboratories Inc. | Spur canceller with multiplier-less correlator |

| US10659060B2 (en) | 2018-09-27 | 2020-05-19 | Silicon Laboratories Inc. | Spur cancellation with adaptive frequency tracking |

| US10819353B1 (en) | 2019-10-04 | 2020-10-27 | Silicon Laboratories Inc. | Spur cancellation in a PLL system with an automatically updated target spur frequency |

| US11038521B1 (en) | 2020-02-28 | 2021-06-15 | Silicon Laboratories Inc. | Spur and quantization noise cancellation for PLLS with non-linear phase detection |

| CN111289864B (zh) * | 2020-04-02 | 2023-02-28 | 全球能源互联网研究院有限公司 | 一种局部放电高频电流抗干扰检测系统及方法 |

| US11316522B2 (en) | 2020-06-15 | 2022-04-26 | Silicon Laboratories Inc. | Correction for period error in a reference clock signal |

| CN112710890B (zh) * | 2020-12-15 | 2024-02-27 | 特变电工西安电气科技有限公司 | 一种单相正弦交流相量实时计算方法及装置 |

| CN113406453B (zh) * | 2021-06-30 | 2023-06-23 | 平顶山学院 | 一种基于mcu的prpd/prps图谱数据处理方法及检测装置 |

| US11563444B1 (en) | 2021-09-09 | 2023-01-24 | Textron Systems Corporation | Suppressing spurious signals in direct-digital synthesizers |

| KR102833443B1 (ko) * | 2021-09-13 | 2025-07-10 | 삼성전자주식회사 | 패턴 생성기 및 이를 포함하는 내장 자체 시험 장치 |

| CN114430262B (zh) * | 2022-01-14 | 2023-03-28 | 中星联华科技(北京)有限公司 | 适用于码型发生器的相位调节装置、系统及方法 |

| KR102888889B1 (ko) * | 2023-07-05 | 2025-11-21 | 주식회사 에픽솔루션 | 프로그램어블 위상 변위기를 이용한 주파수 합성기 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1174940A (ja) * | 1997-06-30 | 1999-03-16 | Hyundai Electron Ind Co Ltd | ディジタル復調器 |

| US6252464B1 (en) * | 1999-10-06 | 2001-06-26 | Cubic Defense Systems, Inc. | Numerically-controlled nyquist-boundary hopping frequency synthesizer |

| JP2001522206A (ja) * | 1997-10-31 | 2001-11-13 | トムソン ライセンシング ソシエテ アノニム | 高精細度テレビジョン残留側波帯(vsb)受信機 |

| US20020084856A1 (en) * | 2000-03-14 | 2002-07-04 | Von Dolteren, Jr. George E. | Subsampling digitizer-based frequency synthesizer |

| WO2003067751A2 (en) * | 2002-02-07 | 2003-08-14 | Philips Intellectual Property & Standards Gmbh | Digital phase locked loop |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4090145A (en) * | 1969-03-24 | 1978-05-16 | Webb Joseph A | Digital quadrature demodulator |

| US4156204A (en) * | 1976-06-03 | 1979-05-22 | Motorola, Inc. | Voltage controlled oscillator with frequency and phase control loop |

| US5444420A (en) * | 1994-09-29 | 1995-08-22 | Harris Corporation | Numerically controlled phase lock loop synthesizer/modulator and method |

| JP4980528B2 (ja) * | 1999-07-16 | 2012-07-18 | トムソン ライセンシング | 高精細度テレビジョン受信機内における搬送波捕捉を助けるための選択的利得調節 |

| US6807134B2 (en) * | 1999-12-28 | 2004-10-19 | Matsushita Electric Industrial Co., Ltd. | Asymmetry detection apparatus, jitter detection apparatus, and recording/reproduction apparatus |

-

2004

- 2004-04-02 US US10/817,780 patent/US7061276B2/en not_active Expired - Lifetime

-

2005

- 2005-02-01 EP EP05002023A patent/EP1584929A3/en not_active Withdrawn

- 2005-02-22 TW TW094105194A patent/TWI292656B/zh not_active IP Right Cessation

- 2005-03-24 JP JP2005086535A patent/JP2005295544A/ja active Pending

- 2005-03-29 CN CNB2005100593722A patent/CN100481711C/zh not_active Expired - Lifetime

-

2006

- 2006-05-09 US US11/430,663 patent/US7432751B2/en not_active Expired - Lifetime

-

2010

- 2010-03-15 JP JP2010057327A patent/JP5154594B2/ja not_active Expired - Lifetime

- 2010-03-15 JP JP2010057324A patent/JP5165712B2/ja not_active Expired - Lifetime

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1174940A (ja) * | 1997-06-30 | 1999-03-16 | Hyundai Electron Ind Co Ltd | ディジタル復調器 |

| JP2001522206A (ja) * | 1997-10-31 | 2001-11-13 | トムソン ライセンシング ソシエテ アノニム | 高精細度テレビジョン残留側波帯(vsb)受信機 |

| US6252464B1 (en) * | 1999-10-06 | 2001-06-26 | Cubic Defense Systems, Inc. | Numerically-controlled nyquist-boundary hopping frequency synthesizer |

| US20020084856A1 (en) * | 2000-03-14 | 2002-07-04 | Von Dolteren, Jr. George E. | Subsampling digitizer-based frequency synthesizer |

| WO2003067751A2 (en) * | 2002-02-07 | 2003-08-14 | Philips Intellectual Property & Standards Gmbh | Digital phase locked loop |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1677844A (zh) | 2005-10-05 |

| US7061276B2 (en) | 2006-06-13 |

| TW200534590A (en) | 2005-10-16 |

| JP2010161797A (ja) | 2010-07-22 |

| US20060202733A1 (en) | 2006-09-14 |

| TWI292656B (en) | 2008-01-11 |

| JP5154594B2 (ja) | 2013-02-27 |

| CN100481711C (zh) | 2009-04-22 |

| US7432751B2 (en) | 2008-10-07 |

| EP1584929A3 (en) | 2006-10-04 |

| US20050218997A1 (en) | 2005-10-06 |

| JP5165712B2 (ja) | 2013-03-21 |

| JP2005295544A (ja) | 2005-10-20 |

| EP1584929A2 (en) | 2005-10-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5154594B2 (ja) | 高性能信号発生 | |

| Kumm et al. | An FPGA-based linear all-digital phase-locked loop | |

| Jenq | Digital spectra of nonuniformly sampled signals. II. Digital look-up tunable sinusoidal oscillators | |

| US6396313B1 (en) | Noise-shaped digital frequency synthesis | |

| CN101765974B (zh) | 混叠频率的锁相 | |

| US20210336710A1 (en) | Calibration device, conversion device, calibration method, and computer-readable medium having recorded thereon calibration program | |

| Galaviz-Aguilar et al. | Reliable methodology to FPGA design verification and noise analysis for digital lock-in amplifiers | |

| TWI777418B (zh) | 用以將信號在數位與類比間轉換之電路及方法、測試設備以及電腦程式 | |

| Simrock et al. | Considerations for the choice of the intermediate frequency and sampling rate for digital RF control | |

| CN118646409A (zh) | 一种数字时钟频率监测方法及装置 | |

| JP5113368B2 (ja) | ジッタ測定装置、ジッタ測定方法、試験装置、及び電子デバイス | |

| JP7503100B2 (ja) | 位相ノイズ影響除去用の補正システムとそれを含むアナログ・デジタル変換装置 | |

| US9654124B1 (en) | Coherent signal source | |

| CN101882921B (zh) | 一键测试数字环路滤波器环路带宽的方法 | |

| KR100706217B1 (ko) | 검파 장치, 방법 및 기록 매체 | |

| CN114184099A (zh) | 一种测量引信时延的方法和装置 | |

| JP2005030866A (ja) | ジッタ伝達特性測定装置 | |

| JP6794784B2 (ja) | 周波数シンセサイザー | |

| Jördens | A radio frequency source for the preparation of quantum states | |

| Gui et al. | The effects of flying-adder clocks on digital-to-analog converters | |

| Sharma | Design and implementation of a re-configurable arbitrary signal generator and radio frequency spectrum analyser | |

| Ma et al. | On the Characterization of Phase Noise for the Robust and Resilient PLL-TRNG Design | |

| Mankovskyy et al. | Digital Method of SSB Modulation | |

| D'Arco et al. | Synthesis and generation of critical waveforms by means of AWG | |

| Pogliano | FAST AND PRECISE ALGORITHM FOR TRACKING SINUSOIDAL SIGNALS |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100413 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120120 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120417 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120612 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120924 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20120925 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20121019 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121107 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121205 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151214 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5154594 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |