JP2010141141A - 薄膜トランジスタおよびその製造方法、並びに表示装置 - Google Patents

薄膜トランジスタおよびその製造方法、並びに表示装置 Download PDFInfo

- Publication number

- JP2010141141A JP2010141141A JP2008316255A JP2008316255A JP2010141141A JP 2010141141 A JP2010141141 A JP 2010141141A JP 2008316255 A JP2008316255 A JP 2008316255A JP 2008316255 A JP2008316255 A JP 2008316255A JP 2010141141 A JP2010141141 A JP 2010141141A

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- film transistor

- gate insulating

- insulating film

- active layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Formation Of Insulating Films (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

Abstract

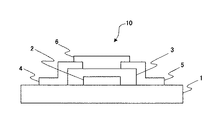

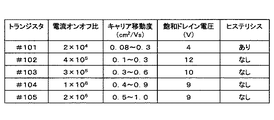

【解決手段】本発明の実施形態による薄膜トランジスタ10は、半導体材料で形成される活性層6;活性層に結合するソース電極4;活性層に結合し、活性層を通してソース電極と導通可能なドレイン電極5;活性層に結合し、複数の有機高分子材料層と複数の無機化合物層とが交互に積層されて構成されるゲート絶縁膜3;および、ゲート絶縁膜に接し、ゲート絶縁膜を介して活性層にチャネル領域を形成できるよう構成されるゲート電極2;を備える。

【選択図】図1

Description

Y. Y. Lin et al., IEEE Electron Device Letters, Vol. 18, 606(1997). S. M. Sze, "Physics of Semiconductor Devices", Wiley, New York, 1981. C. D. Dimitrakopoulos, Science, Vol. 283, 822(1999). W. Y. Chou et al., Appl. Phys. Lett., 89, 112 126 (2006).

添付の全図面中、同一または対応する部材または部品については、同一または対応する参照符号を付し、重複する説明を省略する。また、図面は、部材もしくは部品間または種々の層の厚さの間の相対比を示すことを目的とせず、したがって、具体的な厚さや寸法は、以下の限定的でない実施形態に照らし、当業者により決定されるべきものである。

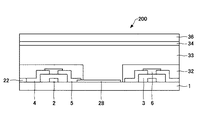

図1は、本発明の第1の実施形態による薄膜トランジスタの断面を模式的に示す図である。図示のとおり、本発明の第1の実施形態による薄膜トランジスタ10は、基板1と、基板1上に形成されたゲート電極2と、基板1上にゲート電極2を覆うように形成されたゲート絶縁膜3と、ゲート絶縁膜3の上面の一部からゲート絶縁膜3の側面に沿って基板1上にまで延在するソース電極4およびドレイン電極5と、ソース電極4およびドレイン電極5のそれぞれの一部とゲート絶縁膜3の上面に接して形成された半導体活性層6とを含む。

まず、ガラス基板を用意し、このガラス基板(基板1)の上にゲート電極2を形成した(図3(a))。具体的には、このゲート電極2は、ガラス基板上に真空蒸着法によりアルミニウム層を形成し、フォトリソグラフィおよびエッチングにより、このアルミニウム層をパターニングして形成した。

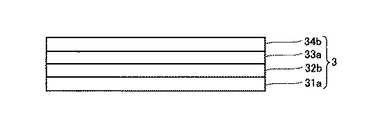

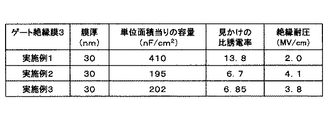

上記のゲート電極2と露出したガラス基板との上に、ゲート絶縁膜3の第1の層31aを形成した。具体的には、まず、強誘電性化合物であるチタン酸バリウムBaTiO3(比誘電率1500)の微粒子(直径約10nm以下、TPL社製、NanOxide HPB−1000)を用意し、この微粒子をSDS界面活性剤を含むメチルアルコール溶媒に混入した。その後、超音波ホモジナイザーを用いて、チタン酸バリウム微粒子を含んだメチルアルコール溶液(SDS界面活性剤を含む)から、均一分散液を作製した。なお、この均一分散液中のチタン酸バリウム微粒子の重量比が約5wt%となるよう調整した。

次いで、ゲート絶縁膜3とガラス基板1の上に真空蒸着法によって金を堆積し、フォトリソグラフィおよびエッチングにより、ソース電極4およびドレイン電極5を形成した(図3(c))。これらの電極4、5の厚さは、約50nmであった。

ソース電極4およびドレイン電極5の形成後、真空蒸着法により、ペンタセンからなる半導体活性層6を形成した。真空蒸着法において、ペンタセンの堆積速度を約0.03〜0.04nm/秒とし、膜厚が約50nmとなるよう堆積時間を調整した。また、真空蒸着の際には、所定の形状の開口部を有するマスクを用いて、半導体活性層6を所定の形状に形成した(図3(d))。

まず、ガラス基板1上にゲート電極2を形成する。この形成方法は、上述の「(1−1)ゲート電極の形成」で説明したとおりである。

上記のゲート電極2と露出したガラス基板との上に、ゲート絶縁膜3の第1の層31aを形成した。具体的には、まず、金属酸化化合物である酸化ジルコニウムZrO2(比誘電率25)の微粒子(直径約10nm以下、NanoTek社製)を用意し、この微粒子をSDS界面活性剤を含むジメチルアセトアミド溶媒に混入した。その後、超音波ホモジナイザーを用いて、酸化ジルコニウム微粒子を含んだジメチルアセトアミド溶液(SDS界面活性剤を含む)から、均一分散液を作製した。なお、この均一分散液中の酸化ジルコニウムの重量比が約2wt%となるよう調整した。

methylated)とを4:1の重量比でPGMEA(Propylene Glycol Methyl Ether Acetate、Aldrich製)溶媒中に溶解させ、ポリビニールフェノール溶液を作製した。次いで、この溶液を第1の層31a上にディップコートし、空気中で約80℃の温度で約30分プリベーキングし、さらに、真空オーブン中で180℃の温度で約1時間ベーキングして、ポリビニールフェノールを含む第2の層32bを得た。このようなベーキング処理により、3次元的な熱架橋反応が促進され、緻密な絶縁膜が得られる。第1の層31aの上の第2の層32bの厚さは、約5nmであった。

まず、上述の「(1−1)ゲート電極の形成」で説明したとおりにガラス基板1上にゲート電極2を形成する。

上記のゲート電極2と露出したガラス基板との上に、ゲート絶縁膜3の第1の層31aを形成した。具体的には、まず、金属酸化化合物である酸化チタンTiO2の微粒子(ルチル構造、比誘電率100、微粒子直径約10nm、NanoTek製)を用意し、この微粒子を分散剤を含むイソプロピルアルコールIPA溶媒に混入した。その後、超音波ホモジナイザーを用いて、酸化チタン微粒子を含んだイソプロピルアルコール溶液(分散剤を含む)から、均一分散液を作製した。なお、この均一分散液中の酸化チタンの重量比が約4wt%となるよう調整した。

図6は、本発明の第2の実施形態によるアクティブマトリックス構造体の模式的な上面図である。図示のとおり、本実施形態のアクティブマトリックス構造体100は、X方向に延びる複数の走査線24と、Y方向に延びる複数の信号線22と、複数の走査線と複数の信号線との各交差点に隣接して配置される薄膜トランジスタ26とを有している。この薄膜トランジスタ26は、本発明の第1の実施形態による薄膜トランジスタ(10、101〜105)であって良い。また、薄膜トランジスタ26のゲート電極2は走査線24と接続し、ソース電極4が信号線22と接続している。

図7は、本発明の第3の実施形態による表示装置の断面図である。図示のとおり、この表示装置200は、第2の実施形態によるアクティブマトリックス構造体100と、アクティブマトリックス構造体100のパッシベーション膜32の上方に設けられる表示素子形成領域33と、表示素子領域33の上に形成される透明電極34と、透明電極34上に設けられる上部基板36と、を含む。上部基板36は、典型的には、ガラス、およびポリエステル、ポリカーボネイト、ポリアリレート、ポリエーテルスルフォンなどのプラスチックにより、形成して良い。

Claims (6)

- 半導体材料で形成される活性層;

前記活性層に結合するソース電極;

前記活性層に結合し、前記活性層を通して前記ソース電極と導通可能なドレイン電極;

前記活性層に結合し、複数の有機高分子材料層と、複数の無機化合物層とが交互に積層されて構成されるゲート絶縁膜;および

前記ゲート絶縁膜に接し、該ゲート絶縁膜を介して前記活性層にチャネル領域を形成できるよう構成されるゲート電極;

を備える薄膜トランジスタ。 - 前記複数の無機化合物層を形成する無機化合物が、金属酸化化合物、強誘電性化合物および希土類金属酸化化合物のうちの少なくとも一つの化合物である、請求項1に記載の薄膜トランジスタ。

- 前記ゲート絶縁膜の厚さが2μm以下である、請求項1又は2に記載の薄膜トランジスタ。

- 前記ゲート絶縁膜が、表面自由エネルギーが50mJ/m2以下となるコーティング薄膜を介して前記活性層と結合する、請求項1から3のいずれか一項に記載の薄膜トランジスタ。

- 請求項1から4のいずれか一項に記載の薄膜トランジスタを製造する製造方法であって、

無機化合物の微粒子を溶媒に混入して分散液を作製し、

該分散液を加熱して前記無機化合物層である第1の膜を形成する第1のステップと、

有機高分子材料を溶媒に溶解し、前記第1の膜上に該溶解液を滴下して加熱し有機高分子材料層である第2の膜を形成する第2のステップと、

前記第1のステップと前記第2のステップを繰り返す、

薄膜トランジスタの製造方法。 - 第1の方向に沿って延びる複数の信号線;

前記第1の方向と交差する第2の方向に延びる複数の走査線;

前記複数の信号線と前記複数の走査線との各交差点に隣接して配置され、ゲート電極が前記走査線と接続し、ソース電極が前記信号線と接続する、請求項1から4のいずれか一項に記載の薄膜トランジスタ;

前記薄膜トランジスタのドレイン電極と結合する表示素子;および

前記表示素子と結合し、前記ドレイン電極とともに前記表示素子へ電力を印加することができるよう設けられた電極;

を含む表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008316255A JP2010141141A (ja) | 2008-12-11 | 2008-12-11 | 薄膜トランジスタおよびその製造方法、並びに表示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008316255A JP2010141141A (ja) | 2008-12-11 | 2008-12-11 | 薄膜トランジスタおよびその製造方法、並びに表示装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010141141A true JP2010141141A (ja) | 2010-06-24 |

Family

ID=42351007

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008316255A Pending JP2010141141A (ja) | 2008-12-11 | 2008-12-11 | 薄膜トランジスタおよびその製造方法、並びに表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010141141A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013069366A1 (ja) * | 2011-11-10 | 2013-05-16 | 富士電機株式会社 | 有機薄膜トランジスタ及びその製造方法 |

| JP2016025246A (ja) * | 2014-07-22 | 2016-02-08 | 株式会社デンソー | 有機トランジスタおよび有機トランジスタの製造方法 |

| JP2016115849A (ja) * | 2014-12-16 | 2016-06-23 | 株式会社デンソー | 有機トランジスタおよびその製造方法 |

| TWI678798B (zh) * | 2018-06-07 | 2019-12-01 | 國立成功大學 | 高感度有機光感測器及其製造方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0262078A (ja) * | 1988-08-26 | 1990-03-01 | Fujitsu Ltd | 薄膜トランジスタ |

| JP2004140123A (ja) * | 2002-10-16 | 2004-05-13 | Semiconductor Energy Lab Co Ltd | 薄膜トランジスタ及びその作製方法 |

| JP2005079560A (ja) * | 2003-09-04 | 2005-03-24 | Hitachi Ltd | 薄膜トランジスタ,表示装置、およびその製造方法 |

| JP2006173532A (ja) * | 2004-12-20 | 2006-06-29 | Nippon Hoso Kyokai <Nhk> | 有機トランジスタおよび有機トランジスタの形成方法 |

| JP2006190923A (ja) * | 2004-12-06 | 2006-07-20 | Toppan Printing Co Ltd | 薄膜トランジスタ |

| JP2008177553A (ja) * | 2006-12-20 | 2008-07-31 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| WO2009044614A1 (ja) * | 2007-10-01 | 2009-04-09 | Rohm Co., Ltd. | 有機半導体装置 |

-

2008

- 2008-12-11 JP JP2008316255A patent/JP2010141141A/ja active Pending

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0262078A (ja) * | 1988-08-26 | 1990-03-01 | Fujitsu Ltd | 薄膜トランジスタ |

| JP2004140123A (ja) * | 2002-10-16 | 2004-05-13 | Semiconductor Energy Lab Co Ltd | 薄膜トランジスタ及びその作製方法 |

| JP2005079560A (ja) * | 2003-09-04 | 2005-03-24 | Hitachi Ltd | 薄膜トランジスタ,表示装置、およびその製造方法 |

| JP2006190923A (ja) * | 2004-12-06 | 2006-07-20 | Toppan Printing Co Ltd | 薄膜トランジスタ |

| JP2006173532A (ja) * | 2004-12-20 | 2006-06-29 | Nippon Hoso Kyokai <Nhk> | 有機トランジスタおよび有機トランジスタの形成方法 |

| JP2008177553A (ja) * | 2006-12-20 | 2008-07-31 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| WO2009044614A1 (ja) * | 2007-10-01 | 2009-04-09 | Rohm Co., Ltd. | 有機半導体装置 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013069366A1 (ja) * | 2011-11-10 | 2013-05-16 | 富士電機株式会社 | 有機薄膜トランジスタ及びその製造方法 |

| JP2016025246A (ja) * | 2014-07-22 | 2016-02-08 | 株式会社デンソー | 有機トランジスタおよび有機トランジスタの製造方法 |

| JP2016115849A (ja) * | 2014-12-16 | 2016-06-23 | 株式会社デンソー | 有機トランジスタおよびその製造方法 |

| TWI678798B (zh) * | 2018-06-07 | 2019-12-01 | 國立成功大學 | 高感度有機光感測器及其製造方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7180108B2 (en) | Transistor, circuit board, display and electronic equipment | |

| KR101943595B1 (ko) | 액티브 매트릭스 감쇄 소스 인에이블형 수직 유기 발광 트랜지스터 | |

| Kim et al. | Organic TFT array on a paper substrate | |

| KR101379616B1 (ko) | 계면특성이 향상된 유기박막트랜지스터 및 그의 제조방법 | |

| US20070278481A1 (en) | Organic electronic device | |

| JP2006191115A (ja) | フッ素系高分子薄膜を含む有機薄膜トランジスタ及びフッ素系高分子薄膜を含む有機薄膜トランジスタの製造方法 | |

| JP2011517075A (ja) | 有機薄膜トランジスタ | |

| US20090101891A1 (en) | Multi-layered bipolar field-effect transistor and method of manufacturing the same | |

| JP2005072569A (ja) | 有機電界効果トランジスタ | |

| KR20160112030A (ko) | 듀얼게이트 박막트랜지스터 | |

| JP2005175386A (ja) | 有機半導体素子 | |

| JP2010141142A (ja) | 薄膜トランジスタおよびその製造方法、並びに表示装置 | |

| KR102073763B1 (ko) | 유기절연막 조성물, 유기절연막의 형성방법, 및 상기 유기절연막을 포함하는 유기박막트랜지스터 | |

| JP2010141141A (ja) | 薄膜トランジスタおよびその製造方法、並びに表示装置 | |

| JP4498961B2 (ja) | 有機電界効果トランジスタ及びそれを具備する平板ディスプレイ装置 | |

| KR101433944B1 (ko) | 전자 장치 및 이를 형성하는 프로세스 | |

| JP2006173532A (ja) | 有機トランジスタおよび有機トランジスタの形成方法 | |

| JP2009295678A (ja) | 半導体装置の製造方法、強誘電体素子の製造方法および電子機器の製造方法 | |

| JP2006024862A (ja) | 有機トランジスタおよび有機トランジスタの製造方法 | |

| JP2005191437A (ja) | 半導体装置、その製造方法、および表示装置 | |

| JP2005251809A (ja) | 薄膜トランジスタの製造方法、薄膜トランジスタ、薄膜トランジスタ回路、電子デバイスおよび電子機器 | |

| US20150295193A1 (en) | Semiconductor device using paper as a substrate and method of manufacturing the same | |

| KR100592266B1 (ko) | 유기 박막 트랜지스터의 제조 방법 | |

| JP2007053147A (ja) | 有機半導体装置及びその製造方法 | |

| KR100794570B1 (ko) | 세로형 유기 박막 트랜지스터 및 이의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110310 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130318 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130326 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130521 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130702 |