JP2010067929A - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP2010067929A JP2010067929A JP2008235514A JP2008235514A JP2010067929A JP 2010067929 A JP2010067929 A JP 2010067929A JP 2008235514 A JP2008235514 A JP 2008235514A JP 2008235514 A JP2008235514 A JP 2008235514A JP 2010067929 A JP2010067929 A JP 2010067929A

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- forming

- substrate

- metallic

- compound layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/751—Insulated-gate field-effect transistors [IGFET] having composition variations in the channel regions

-

- H10P30/204—

-

- H10P30/208—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/691—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator comprising metallic compounds, e.g. metal oxides or metal silicates

-

- H10P14/2905—

-

- H10P14/3402—

-

- H10P14/3411—

-

- H10P30/21—

-

- H10P30/225—

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

- Formation Of Insulating Films (AREA)

- Thin Film Transistor (AREA)

Abstract

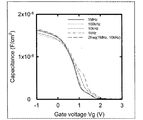

【解決手段】 第一の発明の半導体装置は、基板と、基板表面に形成され、Geを主成分とする半導体領域と、半導体領域上に形成された非金属Ge化合物層と、非金属Ge化合物層上に形成された絶縁膜と、絶縁膜上に形成された電極と、前記電極を挟む前記基板表面に形成されたソース・ドレイン領域とを備えることを特徴とする。非金属Ge化合物層は、例えばSrとGeの化合物、BaとGeの化合物もしくはBaとSiとGeの化合物を有する。

【選択図】 図1

Description

Kamata, Y., Materials Today (2008) 11, 30 Takagi, S., et al., Microelectron. Eng. (2007) 84, 2314 高島 章, 他, 「ゲートスタック研究会 ─材料・プロセス・評価の物理─」第13回 (2008)

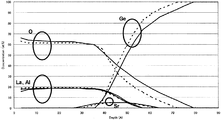

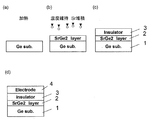

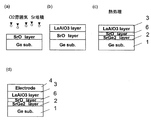

第1の実施形態によるMISFETの概略的な断面を図1に示す。第1の実施形態のMISFETは、図1に示すように、Geを主成分とする半導体基板1上に形成された非金属Ge化合物層2と、非金属Ge化合物層2上に形成された絶縁膜3と、絶縁膜3上に形成されたゲート電極4と、ゲート電極4の両側の半導体基板1に形成されたソース/ドレイン領域5とを備えている。

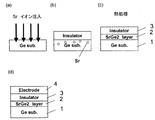

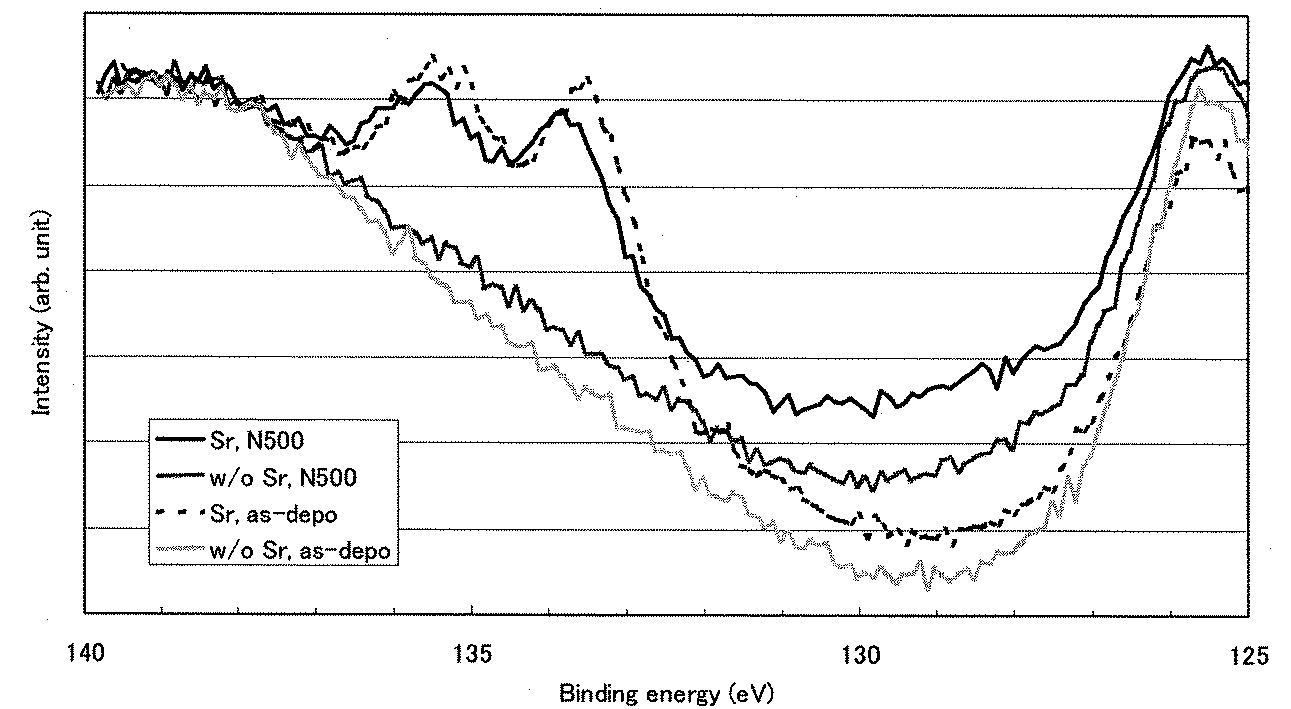

第2の実施形態は、第1の実施形態の半導体装置の製造方法を説明するものであり、Ge基板を昇温し、その温度を維持しつつ、SrもしくはBaを含む金属を堆積することにより、非金属Ge化合物層を形成することを特徴とする。図12に、第2の実施形態の典型的な例を示した。

第3の実施形態は、第1の実施形態の半導体装置の製造方法を説明するものであり、Ge基板にSrもしくはBaを含む金属を堆積した後に、熱処理を施して非金属Ge化合物層を形成することを特徴とする。熱処理は絶縁膜を堆積する前後どちらでもよい。この他は、第2の実施形態と同様である。図13に、第3の実施形態の典型的な例を示した。

第4の実施形態は、半導体基板がSiGe基板であること以外は第3の実施形態と同様である。

第5の実施形態は、第1の実施形態の半導体装置の製造方法を説明するものであり、Ge基板に非金属Ge化合物層を堆積した後に、絶縁膜を形成することを特徴とする。この他は、第2の実施形態と同様である。図14に、第5の実施形態の典型的な例を示した。

第6の実施形態は、第1の実施形態の半導体装置の製造方法を説明するものであり、Ge基板にSrもしくはBaを含む金属酸化膜を堆積した後に絶縁膜を形成し、その後熱処理を施すことにより、金属酸化膜を還元させて非金属Ge化合物層を形成することを特徴とする。この他は、第2の実施形態と同様である。図15に、第6の実施形態の典型的な例を示した。

第7の実施形態は、第1の実施形態の半導体装置の製造方法を説明するものであり、Ge基板にSrもしくはBaを導入した後に、Ge基板上に絶縁膜を形成し、その後、熱処理を施して、前記半導体領域と前記絶縁膜との界面にSrもしくはBaを偏析させて非金属Ge化合物層を形成することを特徴とする。この他は、第2の実施形態と同様である。図16に、第7の実施形態の典型的な例を示した。

2 非金属Ge化合物層

3 絶縁膜

4 電極

5 ソース・ドレイン領域

Claims (11)

- 基板と、

前記基板表面に形成され、Geを主成分とする半導体領域と、

前記半導体領域上に形成された非金属Ge化合物層と、

前記非金属Ge化合物層上に形成された絶縁膜と、

前記絶縁膜上に形成された電極と、

前記電極を挟む前記基板表面に形成されたソース・ドレイン領域とを備えることを特徴とする半導体装置。 - 前記非金属Ge化合物層は、SrとGeの化合物、BaとGeの化合物もしくはBaとSiとGeの化合物を有することを特徴とする請求項1に記載の半導体装置。

- 前記絶縁膜のGibbsの自由エネルギーは、前記非金属Ge化合物層のGibbsの自由エネルギーよりも負に大きいことを特徴とする請求項1または2に記載の半導体装置。

- 前記非金属Ge化合物層と前記絶縁膜との間に、Sr酸化物もしくはBa酸化物が介在していることを特徴とする請求項1乃至3の何れか一項に記載の半導体装置。

- 前記半導体領域のGe濃度が85%以上であることを特徴とする請求項1乃至4の何れか一項に記載の半導体装置。

- 前記絶縁膜は、LaおよびAlを含むことを特徴とする請求項1乃至5の何れか一項に記載の半導体装置。

- Geを主成分とする半導体領域を有する基板を加熱する工程と、

前記基板の温度を維持しつつ、前記半導体領域上にSrもしくはBaを含む金属を堆積し、前記金属と前記半導体領域とを反応させて非金属Ge化合物層を形成する工程と、

前記非金属Ge化合物層上に絶縁膜を形成する工程と、

前記絶縁膜上に電極を形成する工程と、

前記電極を挟む前記基板表面にソース・ドレイン領域を形成する工程と

を備えることを特徴とする半導体装置の製造方法。 - Geを主成分とする半導体領域上に、SrもしくはBaを含む金属層を堆積する工程と、

熱処理を施すことにより、前記金属層と前記半導体領域とを反応させて非金属Ge化合物層を形成する工程と、

前記非金属Ge化合物層上に絶縁膜を形成する工程と、

前記絶縁膜上に電極を形成する工程と、

前記電極を挟む前記基板表面にソース・ドレイン領域を形成する工程と

を備えることを特徴とする半導体装置の製造方法。 - Geを主成分とする半導体領域上に、非金属Ge化合物層を堆積する工程と、

前記非金属Ge化合物層上に、絶縁膜を形成する工程と、

前記絶縁膜上に電極を形成する工程と、

前記電極を挟む前記基板表面にソース・ドレイン領域を形成する工程と

を備えることを特徴とする半導体装置の製造方法。 - Geを主成分とする半導体領域上に、SrもしくはBaを含む金属酸化膜を形成する工程と、

前記金属酸化膜上に絶縁膜を形成する工程と、

その後、熱処理を施して、前記金属酸化膜を還元させるとともに非金属Ge化合物層を形成する工程と、

前記絶縁膜上に電極を形成する工程と、

前記電極を挟む前記基板表面にソース・ドレイン領域を形成する工程と

を備えることを特徴とする半導体装置の製造方法。 - Geを主成分とする半導体領域に、SrもしくはBaを導入する工程と、

前記半導体領域上に、絶縁膜を形成する工程と、

その後、熱処理を施して、前記半導体領域と前記絶縁膜との界面にSrもしくはBaを偏析させて非金属Ge化合物層を形成する工程と、

前記絶縁膜上に電極を形成する工程と、

前記電極を挟む前記基板表面にソース・ドレイン領域を形成する工程と

を備えることを特徴とする半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008235514A JP4768788B2 (ja) | 2008-09-12 | 2008-09-12 | 半導体装置およびその製造方法 |

| US12/482,054 US7986016B2 (en) | 2008-09-12 | 2009-06-10 | Semiconductor device and associated manufacturing methodology for decreasing thermal instability between an insulating layer and a substrate |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008235514A JP4768788B2 (ja) | 2008-09-12 | 2008-09-12 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010067929A true JP2010067929A (ja) | 2010-03-25 |

| JP4768788B2 JP4768788B2 (ja) | 2011-09-07 |

Family

ID=42006426

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008235514A Expired - Fee Related JP4768788B2 (ja) | 2008-09-12 | 2008-09-12 | 半導体装置およびその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7986016B2 (ja) |

| JP (1) | JP4768788B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013073468A1 (ja) * | 2011-11-17 | 2013-05-23 | 独立行政法人産業技術総合研究所 | 素子形成用基板及びその製造方法 |

| JP2014523131A (ja) * | 2011-06-27 | 2014-09-08 | クリー インコーポレイテッド | チャンネル移動度を増加させた半導体デバイスを製造するためのウェット・ケミストリー・プロセス |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102157432A (zh) * | 2011-01-24 | 2011-08-17 | 清华大学 | GeOI结构及其形成方法 |

| US8772873B2 (en) * | 2011-01-24 | 2014-07-08 | Tsinghua University | Ge-on-insulator structure and method for forming the same |

| EP2676213B1 (en) | 2011-02-17 | 2019-07-31 | NIKE Innovate C.V. | Location mapping |

| US8890209B2 (en) * | 2011-03-10 | 2014-11-18 | Tsinghua University | Strained GE-ON-insulator structure and method for forming the same |

| US8704306B2 (en) * | 2011-03-10 | 2014-04-22 | Tsinghua University | Strained Ge-on-insulator structure and method for forming the same |

| WO2012119419A1 (en) * | 2011-03-10 | 2012-09-13 | Tsinghua University | Strained ge-on-insulator structure and method for forming the same |

| US8786017B2 (en) | 2011-03-10 | 2014-07-22 | Tsinghua University | Strained Ge-on-insulator structure and method for forming the same |

| CN105551941B (zh) * | 2016-01-12 | 2019-01-15 | 北京大学 | 一种提高金属锗化物热稳定性的方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005191293A (ja) * | 2003-12-25 | 2005-07-14 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2006210658A (ja) * | 2005-01-28 | 2006-08-10 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2007123895A (ja) * | 2005-10-26 | 2007-05-17 | Internatl Business Mach Corp <Ibm> | 方法および半導体構造(非酸素カルコゲン不活性化ステップを用いて製作されたGe系半導体構造) |

| JP2007273531A (ja) * | 2006-03-30 | 2007-10-18 | Toshiba Corp | 半導体装置およびその製造方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6143072A (en) * | 1999-04-06 | 2000-11-07 | Ut-Battelle, Llc | Generic process for preparing a crystalline oxide upon a group IV semiconductor substrate |

| US6652989B2 (en) * | 1999-04-06 | 2003-11-25 | Ut-Battelle, Llc | Structure and method for controlling band offset and alignment at a crystalline oxide-on-semiconductor interface |

| US6511876B2 (en) * | 2001-06-25 | 2003-01-28 | International Business Machines Corporation | High mobility FETS using A1203 as a gate oxide |

-

2008

- 2008-09-12 JP JP2008235514A patent/JP4768788B2/ja not_active Expired - Fee Related

-

2009

- 2009-06-10 US US12/482,054 patent/US7986016B2/en not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005191293A (ja) * | 2003-12-25 | 2005-07-14 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2006210658A (ja) * | 2005-01-28 | 2006-08-10 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2007123895A (ja) * | 2005-10-26 | 2007-05-17 | Internatl Business Mach Corp <Ibm> | 方法および半導体構造(非酸素カルコゲン不活性化ステップを用いて製作されたGe系半導体構造) |

| JP2007273531A (ja) * | 2006-03-30 | 2007-10-18 | Toshiba Corp | 半導体装置およびその製造方法 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014523131A (ja) * | 2011-06-27 | 2014-09-08 | クリー インコーポレイテッド | チャンネル移動度を増加させた半導体デバイスを製造するためのウェット・ケミストリー・プロセス |

| WO2013073468A1 (ja) * | 2011-11-17 | 2013-05-23 | 独立行政法人産業技術総合研究所 | 素子形成用基板及びその製造方法 |

| JP2013110161A (ja) * | 2011-11-17 | 2013-06-06 | National Institute Of Advanced Industrial & Technology | 素子形成用基板及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4768788B2 (ja) | 2011-09-07 |

| US7986016B2 (en) | 2011-07-26 |

| US20100065886A1 (en) | 2010-03-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4768788B2 (ja) | 半導体装置およびその製造方法 | |

| US7446380B2 (en) | Stabilization of flatband voltages and threshold voltages in hafnium oxide based silicon transistors for CMOS | |

| Schlom et al. | Gate oxides beyond SiO2 | |

| US7824990B2 (en) | Multi-metal-oxide high-K gate dielectrics | |

| CN106663634B (zh) | 半导体器件及半导体器件的制造方法 | |

| Hu et al. | Effect of annealing ambient and temperature on the electrical characteristics of atomic layer deposition Al2O3/In0. 53Ga0. 47As metal-oxide-semiconductor capacitors and MOSFETs | |

| JP2008172227A (ja) | 電子デバイスおよびその製造プロセス | |

| US20110037131A1 (en) | Gate structure for field effect transistor | |

| US9252146B2 (en) | Work function adjustment by carbon implant in semiconductor devices including gate structure | |

| US20140035001A1 (en) | Compound semiconductor structure | |

| CN102044442B (zh) | 一种改善高介电常数栅介质界面特性的方法 | |

| Lee et al. | Improving Interface State Density and Thermal Stability of High-$\kappa $ Gate Stack Through High-Vacuum Annealing on Si 0.5 Ge 0.5 | |

| Jamison et al. | SiO 2 free HfO 2 gate dielectrics by physical vapor deposition | |

| Bethge et al. | Stability of La2O3 and GeO2 passivated Ge surfaces during ALD of ZrO2 high-k dielectric | |

| Nigro et al. | Surface treatments on AlGaN/GaN heterostructures for gate dielectric Al2O3 thin films grown by Atomic Layer Deposition | |

| Singh et al. | CVD-deposited Cu 2 O thin films with a record Hall hole mobility of 263 cm 2 V− 1 s− 1 and field-effect mobility of 0.99 cm 2 V− 1 s− 1 | |

| Zhang et al. | Effects of thermal annealing on the interface between tungsten and CeO2/La2O3 stack gate dielectrics | |

| Song et al. | Post metallization annealing study in La2O3/Ge MOS structure | |

| Bom et al. | Evolution of the Al2O3/Ge (1 0 0) interface for reactively sputter-deposited films submitted to postdeposition anneals | |

| JP2010199294A (ja) | 半導体装置 | |

| Lopes et al. | Electrical and structural properties of ternary rare-earth oxides on Si and higher mobility substrates and their integration as high-k gate dielectrics in MOSFET devices | |

| Zadeh et al. | Low D it high-k/In 0.53 Ga 0.47 As gate stack, with CET down to 0.73 nm and thermally stable silicide contact by suppression of interfacial reaction | |

| KR101070869B1 (ko) | 쇼트키 장벽 트랜지스터 소자의 제조방법 | |

| Kar et al. | Physics and technology of high-k materials 9 | |

| Kim et al. | Atomic layer deposited HfO2/HfSixOyNz stacked gate dielectrics for metal-oxide-semiconductor structures |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101020 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101116 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110117 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110524 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110616 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4768788 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140624 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |