JP2010057133A - 周波数シンセサイザ - Google Patents

周波数シンセサイザ Download PDFInfo

- Publication number

- JP2010057133A JP2010057133A JP2008222722A JP2008222722A JP2010057133A JP 2010057133 A JP2010057133 A JP 2010057133A JP 2008222722 A JP2008222722 A JP 2008222722A JP 2008222722 A JP2008222722 A JP 2008222722A JP 2010057133 A JP2010057133 A JP 2010057133A

- Authority

- JP

- Japan

- Prior art keywords

- frequency

- phase difference

- vector

- detection unit

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Abstract

【解決手段】電圧制御発振部1の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルの位相差を取り出して出力周波数の調節に利用するPLLは、出力周波数調節用の第1の位相差検出部71と、周波数引き込み用の第2の位相差検出部74とを備え、前記第1の位相差検出部71の出力に係る信号をディジタル/アナログ変換した結果が予め定めたしきい値を越えたときに、前記第2の位相差検出部74の出力に係る信号をディジタル/アナログ変換する手段105から切り離すと共に、当該第2の位相差検出部74における消費電力を小さくする。

【選択図】図1

Description

設定周波数に応じて粗刻みに決められた周波数と設定周波数との差分の周波数で回転するベクトルの速度に対応するサンプリング間隔の位相差と、前記第1の位相差検出部にて検出された位相差と、の差分であるベクトル同士の速度差を取り出して積分し、その積分値を第1のディジタル/アナログ変換部を介して制御電圧として電圧制御発振部に供給し、こうしてPLLループが形成された周波数シンセサイザにおいて、

前記逆回転ベクトルにて減速された回転ベクトルを一のサンプリング時間にて得られた位相と次のサンプリング時間にて得られた位相との位相差を求めるディジタル回路からなる第2の位相差検出部と、

この第2の位相差検出部にて得られた位相差を積分した積分値をディジタル/アナログ変換して前記電圧制御発振部に周波数引き込み用の制御電圧として供給するための第2のディジタル/アナログ変換部と、

周波数シンセサイザの立ち上げ時に前記第2の位相差検出部の出力を前記第2のディジタル/アナログ変換部に供給し、前記第1のディジタル/アナログ変換部の出力が予め定めたしきい値を越えたときに、前記前記第2の位相差検出部の出力を前記第2のディジタル/アナログ変換部の入力側から切り離す手段と、

この切り離しが行われたときに、前記前記第2の位相差検出部の消費電力を小さくするための手段と、を備えたことを特徴とする。

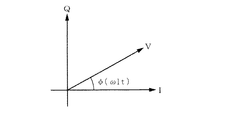

Acos(ω0t+θ)・cos(ω0t)

=1/2・Acosθ+1/2{cos(2ω0t)・cosθ+sin(2ω0t)・sinθ}……(1)

Acos(ω0t+θ)・−sin(ω0t)

=1/2・Asinθ−1/2{sin(2ω0t)・cosθ+cos(2ω0t)・sinθ}……(2)

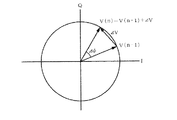

I+jQ={I(n)・I`(n)−Q(n)・Q`(n)}+j{I(n)・Q`(n)+I`(n)・Q(n)} ……(3)

逆ベクトルV`を発生するとは、実際には複素平面上におけるベクトルが逆回転するように当該ベクトルの実数部分及び虚数部分の値つまり逆ベクトルV`の位相をφ`とすると、cosφ`とsinφ`との値を発生させることである。より具体的にはベクトルのcosφ`とsinφ`との組がベクトルの回転方向に沿って順番には配列されたテーブルを例えばパラメータ出力部6内に用意し、そのテーブルのアドレスを、指示された電圧制御発振器1の設定周波数に応じて決定されるインクリメント数またはデクリメント数で読み出すことで実現できる。

Δφ=K・imag[ΔV・conj{V(n)}] ……(4)

ΔV=ΔI+jΔQ ……(5)

conj{V(n)}=I(n)−jQ(n) ……(6)

ただしΔIはI(n)−I(n−1)であり、ΔQはQ(n)−Q(n−1)である。(5)式及び(6)式を(4)式に代入して整理すると、Δφは(7)式で表されることになる。

Δφ=ΔQ・I(n)−ΔI・Q(n) ……(7)

前記第1の位相差検出部71は、このように近似式を用いてΔφを求める機能を備えている。このΔφは、逆ベクトル乗算部5にて減速されたベクトルVの周波数に対応する値である。

SW2 第2のスイッチ

1 VCO(電圧制御発振器)

2 分周手段

3 A/D変換器

4 キャリアリムーブ

5 逆ベクトル乗算部

6 パラメータ出力部

7 減数処理部

71 第1の位相差検出部

73 位相差の累積加算部

74 第2の位相差検出部

8 ループフィルタ

80 第1のD/A変換部

10 切替制御部

101 積分手段

105 第2のD/A変換部

Claims (3)

- 制御電圧に応じて電圧制御発振部から出力される周波数信号を分周し、分周された周波数信号である正弦波信号をディジタル化し、ディジタル化された周波数信号に対して、ディジタル信号である検波用の周波数信号による直交検波を行って、両周波数信号の周波数差に相当する周波数で回転する回転ベクトルを複素表示したときの実数部分及び虚数部分を回転ベクトル取り出し手段にて取り出し、ベクトル取り出し手段にて取り出された回転ベクトルに対して、設定周波数に応じて粗刻みに決められた周波数で逆回転する逆回転ベクトルを乗算して前記ベクトルの速度を減速し、減速されたベクトルについて一のサンプリング時間にて得られた位相と次のサンプリング時間にて得られた位相との位相差を当該ベクトルの速度と擬制して第1の位相差検出部にて検出し、

設定周波数に応じて粗刻みに決められた周波数と設定周波数との差分の周波数で回転するベクトルの速度に対応するサンプリング間隔の位相差と、前記第1の位相差検出部にて検出された位相差と、の差分であるベクトル同士の速度差を取り出して積分し、その積分値を第1のディジタル/アナログ変換部を介して制御電圧として電圧制御発振部に供給し、こうしてPLLループが形成された周波数シンセサイザにおいて、

前記逆回転ベクトルにて減速された回転ベクトルを一のサンプリング時間にて得られた位相と次のサンプリング時間にて得られた位相との位相差を求めるディジタル回路からなる第2の位相差検出部と、

この第2の位相差検出部にて得られた位相差を積分した積分値をディジタル/アナログ変換して前記電圧制御発振部に周波数引き込み用の制御電圧として供給するための第2のディジタル/アナログ変換部と、

周波数シンセサイザの立ち上げ時に前記第2の位相差検出部の出力を前記第2のディジタル/アナログ変換部に供給し、前記第1のディジタル/アナログ変換部の出力が予め定めたしきい値を越えたときに、前記前記第2の位相差検出部の出力を前記第2のディジタル/アナログ変換部の入力側から切り離す手段と、

この切り離しが行われたときに、前記前記第2の位相差検出部の消費電力を小さくするための手段と、を備えたことを特徴とする周波数シンセサイザ。 - 前記消費電力を小さくするための手段は、前記第2の位相差検出部に、減速されたベクトルについての位相を示す信号に替えて、論理「0」の信号を入力することを特徴とする請求項1に記載の周波数シンセサイザ。

- 前記第2の位相差検出部は、クロック信号に同期して動作し、前記消費電力を小さくするための手段は、当該第2の位相差検出部へのクロック信号の入力を停止するものであることを特徴とする請求項1に記載の周波数シンセサイザ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008222722A JP5189436B2 (ja) | 2008-08-29 | 2008-08-29 | 周波数シンセサイザ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008222722A JP5189436B2 (ja) | 2008-08-29 | 2008-08-29 | 周波数シンセサイザ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010057133A true JP2010057133A (ja) | 2010-03-11 |

| JP5189436B2 JP5189436B2 (ja) | 2013-04-24 |

Family

ID=42072524

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008222722A Expired - Fee Related JP5189436B2 (ja) | 2008-08-29 | 2008-08-29 | 周波数シンセサイザ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5189436B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019041169A (ja) * | 2017-08-23 | 2019-03-14 | 横河電機株式会社 | 交流信号発生器 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002223164A (ja) * | 2001-01-25 | 2002-08-09 | Sanyo Electric Co Ltd | Pll回路 |

| JP2007295337A (ja) * | 2006-04-26 | 2007-11-08 | Tamura Seisakusho Co Ltd | 音量調整装置用異常監視装置 |

-

2008

- 2008-08-29 JP JP2008222722A patent/JP5189436B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002223164A (ja) * | 2001-01-25 | 2002-08-09 | Sanyo Electric Co Ltd | Pll回路 |

| JP2007295337A (ja) * | 2006-04-26 | 2007-11-08 | Tamura Seisakusho Co Ltd | 音量調整装置用異常監視装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019041169A (ja) * | 2017-08-23 | 2019-03-14 | 横河電機株式会社 | 交流信号発生器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5189436B2 (ja) | 2013-04-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102291131B (zh) | 频率合成器 | |

| JP5006417B2 (ja) | Pll発振回路 | |

| US8975973B2 (en) | Oscillation frequency adjusting apparatus, oscillation frequency adjusting method, and wireless communication apparatus | |

| JP4679872B2 (ja) | クロック発生装置 | |

| US7642862B2 (en) | Digital phase locked loop | |

| JP5189436B2 (ja) | 周波数シンセサイザ | |

| CN114157294B (zh) | 模拟鉴相器与数字鉴频器合作捕获的低相噪频率合成器 | |

| JP5066466B2 (ja) | 周波数シンセサイザ | |

| JP4397363B2 (ja) | 周波数シンセサイザ | |

| WO2007114523A1 (ja) | ディジタル処理装置 | |

| JP4713525B2 (ja) | 周波数シンセサイザ | |

| JP2010141519A (ja) | 位相同期回路、および通信装置 | |

| WO2007114498A1 (ja) | Pll装置 | |

| JP4651931B2 (ja) | シンセサイザ | |

| JP4459969B2 (ja) | Pllシンセサイザ | |

| JP2008147788A (ja) | 位相同期回路、同期検波回路および放送受信装置 | |

| JP2007295554A (ja) | ディジタル処理装置 | |

| JP4787870B2 (ja) | 周波数シンセサイザ | |

| JPH1022827A (ja) | アナログ/ディジタル変換装置 | |

| JP2002152037A (ja) | 位相同期発振回路 | |

| JP2011139451A (ja) | クロック発生装置 | |

| JP2007295537A5 (ja) | ||

| JP2011188309A (ja) | 周波数シンセサイザ及び周波数シンセサイザの調整方法 | |

| JPS59181726A (ja) | 周波数合成器 | |

| JP2011049963A (ja) | Pll回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110803 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120710 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130115 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130124 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160201 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160201 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |