JP2010044199A - 表示装置、電子装置、電子システム - Google Patents

表示装置、電子装置、電子システム Download PDFInfo

- Publication number

- JP2010044199A JP2010044199A JP2008207895A JP2008207895A JP2010044199A JP 2010044199 A JP2010044199 A JP 2010044199A JP 2008207895 A JP2008207895 A JP 2008207895A JP 2008207895 A JP2008207895 A JP 2008207895A JP 2010044199 A JP2010044199 A JP 2010044199A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- source

- gate

- source bus

- level

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004973 liquid crystal related substance Substances 0.000 description 39

- 239000003990 capacitor Substances 0.000 description 30

- 238000010586 diagram Methods 0.000 description 19

- 239000010408 film Substances 0.000 description 12

- 239000011521 glass Substances 0.000 description 12

- 239000000758 substrate Substances 0.000 description 12

- 230000007704 transition Effects 0.000 description 9

- 238000000034 method Methods 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 2

- 230000010287 polarization Effects 0.000 description 2

- 239000000470 constituent Substances 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000010365 information processing Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3685—Details of drivers for data electrodes

- G09G3/3688—Details of drivers for data electrodes suitable for active matrices only

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3655—Details of drivers for counter electrodes, e.g. common electrodes for pixel capacitors or supplementary storage capacitors

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3696—Generation of voltages supplied to electrode drivers

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/13624—Active matrix addressed cells having more than one switching element per pixel

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Power Engineering (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

- Liquid Crystal Display Device Control (AREA)

Abstract

【解決手段】画素電極とドレインが前記画素電極に、ソースをソースバスに接続し、ゲートに印加されるゲート電圧に応じて前記画素電極印加電圧を制御する画素駆動用トランジスタとを有し、前記画素駆動用トランジスタのゲートに接続し、前記トランジスタのゲートに印加する電圧を保持するキャパシタンスと、ドレインがトランジスタのゲートと前記キャパシタンスとの接続点に接続され、ソースが前記ソースバスに接続され、ゲートがゲートラインに接続され、前記キャパシタンスの印加電圧を制御するゲート駆動電圧制御用トランジスタと、前記キャパシタンス電圧を、隣接するソースバスで、異なる電圧となるように交互に切り換える。

【選択図】図3

Description

第1の高レベル電圧を発生する第1の高電圧源と、

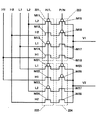

前記第1の高レベル電圧より高いレベルの第2の高レベル電圧を発生する第2の高電圧源と、前記第1及び第2の高レベル電圧より低いレベルの第1の低レベル電圧を発生する第1の低電圧源と、第1の低レベル電圧より低いレベルの第2の低レベル電圧を発生する第2の低電圧源と、前記第1及び第2の高電圧源から前記第1及び第2の高レベル電圧が印加されるとともに、前記第1及び第2の低電圧源から前記第1及び第2の低レベル電圧が印加され、選択信号に基づいて前記第1及び第2の高レベル電圧、前記第1及び第2の低レベル電圧を第1の出力ライン及び第2の出力ラインに選択的に出力する電圧選択回路と、前記キャパシタンスに電圧を保持させるときに、前記第1及び第2の出力ラインの電圧を前記ソースバスに供給し、前記画素駆動用トランジスタのソースにソース電圧を印加するときに、前記デマルチプレクサの出力を前記ソースバスに供給するように切り換える電圧切換回路とを有する構成としてなる。

初期状態においては、図5に示すように、駆動レベル指示信号high/low及びバス指示信号posi/negaはローレベルLL、切換信号gate/sourceはハイレベルHHであり、デマルチプレクサ212の第1のソースバスSB1への出力電圧はVsn、第2のソースバスSB2への出力電圧はVspとなる。

101 インタフェース部、102 コントローラ、103 ゲートライン駆動回路

104 ソースバス駆動回路、105 表示部

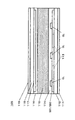

111 偏光板、112 下部ガラス基板、113 画素電極部、GL ゲートライン

SB1 第1のソースバス、SB2 第2のソースバス、114 配向膜、115 液晶

116 配向膜、117 共通電極、118 上部ガラス基板、119 偏光板

211 電圧選択回路 212 デマルチプレクサ、213 電圧切換回路

214 第1の高レベル電圧源、215 第2の高レベル電圧源

216 第1の低レベル電圧源、217 第2の低レベル電圧源

221 第1の電圧レベル選択部、222 第2の電圧レベル選択部

223 第3の電圧レベル選択部、224 第4の電圧レベル選択部

Claims (5)

- 画素電極と、ドレインが前記画素電極に接続され、ソースがソースバスに接続され、ゲートに印加されるゲート電圧に応じて前記画素電極の印加電圧を制御する画素駆動用トランジスタとを有する表示装置であって、

前記画素駆動用トランジスタのゲートに接続され、前記画素駆動用トランジスタのゲートに印加する電圧を保持するキャパシタンスと、

ドレインが前記画素駆動用トランジスタのゲートと前記キャパシタンスとの接続点に接続され、ソースが前記ソースバスに接続され、ゲートがゲートラインに接続され、前記キャパシタンスの印加電圧を制御するゲート駆動電圧制御用トランジスタと、

前記キャパシタンスに電圧を保持する電圧を、隣接するソースバスで、異なる複数のハイレベル電圧、又は、異なる複数のローレベル電圧となるように交互に切り換え、前記ソースを駆動するソースバス駆動回路とを有する表示装置。 - 前記ソース駆動回路は、前記画素電極に印加するソース電圧を前記ソースバスに供給するデマルチプレクサと、

第1の高レベル電圧を発生する第1の高電圧源と、

前記第1の高レベル電圧より高いレベルの第2の高レベル電圧を発生する第2の高電圧源と、

前記第1及び第2の高レベル電圧より低いレベルの第1の低レベル電圧を発生する第1の低電圧源と、

第1の低レベル電圧より低いレベルの第2の低レベル電圧を発生する第2の低電圧源と、

前記第1及び第2の高電圧源から前記第1及び第2の高レベル電圧が印加されるとともに、前記第1及び第2の低電圧源から前記第1及び第2の低レベル電圧が印加され、選択信号に基づいて前記第1及び第2の高レベル電圧、前記第1及び第2の低レベル電圧を第1の出力ライン及び第2の出力ラインに選択的に出力する電圧選択回路と、

前記キャパシタンスに電圧を保持させるときに、前記第1及び第2の出力ラインの電圧を前記ソースバスに供給し、前記画素駆動用トランジスタのソースにソース電圧を印加するときに、前記デマルチプレクサの出力を前記ソースバスに供給するように切り換える電圧切換回路とを有する請求項1記載の表示装置。 - 前記電圧選択回路は、電圧レベル選択信号に応じて前記第1又は第2の高レベル電圧、及び、前記第1又は第2の低レベル電圧を出力する第1電圧選択部と、

電圧レベル選択信号に応じて前記第2又は第1の高レベル電圧、及び、前記第2又は第1の低レベル電圧を出力する第2電圧選択部と、

ソースバス切換信号に応じて前記第1の電圧レベル選択部から出力される前記第1又は第2の高レベル電圧と、前記第1又は第2の低レベル電圧とうちのいずれかを1ソースバスおきに設定された第1のソースバスに出力する第3の電圧選択部と、

ソースバス切換信号に応じて前記第2の電圧レベル選択部から出力される前記第2又は第1の高レベル電圧と、前記第2又は第1の低レベル電圧とのうちのいずれかを前記第1のソースバスに隣接する第2のソースバスに出力する第4の電圧選択部とを有する請求項2記載の表示装置。 - 請求項1乃至3のいずれか一項記載の表示装置を含む電子装置。

- 請求項4記載の電子装置を含む電子システム。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008207895A JP4595008B2 (ja) | 2008-08-12 | 2008-08-12 | 表示装置、電子装置、電子システム |

| TW098126214A TWI409785B (zh) | 2008-08-12 | 2009-08-04 | 顯示裝置 |

| CN2009101603700A CN101751888B (zh) | 2008-08-12 | 2009-08-04 | 显示装置、电子装置、电子系统 |

| US12/539,419 US8264440B2 (en) | 2008-08-12 | 2009-08-11 | Display device, electronic apparatus and electronic system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008207895A JP4595008B2 (ja) | 2008-08-12 | 2008-08-12 | 表示装置、電子装置、電子システム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010044199A true JP2010044199A (ja) | 2010-02-25 |

| JP4595008B2 JP4595008B2 (ja) | 2010-12-08 |

Family

ID=41681032

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008207895A Active JP4595008B2 (ja) | 2008-08-12 | 2008-08-12 | 表示装置、電子装置、電子システム |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8264440B2 (ja) |

| JP (1) | JP4595008B2 (ja) |

| CN (1) | CN101751888B (ja) |

| TW (1) | TWI409785B (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2867753A1 (de) | 2012-06-27 | 2015-05-06 | Johnson Controls Automotive Electronics GmbH | Anzeigeeinheit mit einer tastkontrolleinheit |

| TWI475551B (zh) * | 2013-06-03 | 2015-03-01 | Au Optronics Corp | 顯示面板之驅動方法、顯示面板及閘極驅動電路 |

| KR102269080B1 (ko) * | 2015-01-23 | 2021-06-24 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| CN109461414B (zh) * | 2018-11-09 | 2020-11-06 | 惠科股份有限公司 | 一种显示装置的驱动电路及方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0377915A (ja) * | 1989-08-21 | 1991-04-03 | Sharp Corp | 液晶表示装置 |

| JPH05165431A (ja) * | 1991-12-13 | 1993-07-02 | Kyocera Corp | 液晶表示装置の駆動方法 |

| JP2001059957A (ja) * | 1999-08-23 | 2001-03-06 | Seiko Epson Corp | 液晶装置およびその駆動方法並びに投射型表示装置 |

| JP2003248465A (ja) * | 2002-02-25 | 2003-09-05 | Sharp Corp | 画像表示装置の駆動方法および画像表示装置の駆動装置 |

| JP2007188079A (ja) * | 2006-01-10 | 2007-07-26 | Samsung Electronics Co Ltd | ゲートドライバー、これを備えた薄膜トランジスター基板及び液晶表示装置 |

| JP2007323041A (ja) * | 2006-06-02 | 2007-12-13 | Lg Phillips Lcd Co Ltd | 液晶表示装置及びその駆動方法 |

| JP2008165135A (ja) * | 2007-01-05 | 2008-07-17 | Seiko Epson Corp | 電気光学装置、その駆動方法および電子機器 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI299099B (en) * | 2000-03-30 | 2008-07-21 | Sharp Kk | Active matrix type liquid crystal display apparatus |

| TWI267050B (en) * | 2001-11-26 | 2006-11-21 | Samsung Electronics Co Ltd | Liquid crystal display and driving method thereof |

| TWI293444B (en) * | 2002-04-08 | 2008-02-11 | Samsung Electronics Co Ltd | Liquid crystal display device |

| TWI254899B (en) * | 2002-06-21 | 2006-05-11 | Himax Tech Inc | Method and related apparatus for driving an LCD monitor |

| JP4089546B2 (ja) * | 2003-08-04 | 2008-05-28 | ソニー株式会社 | 表示装置およびその駆動方法 |

| KR100583318B1 (ko) * | 2003-12-17 | 2006-05-25 | 엘지.필립스 엘시디 주식회사 | 액정표시장치의 게이트 구동장치 및 방법 |

| JP4646187B2 (ja) * | 2004-02-12 | 2011-03-09 | 東北パイオニア株式会社 | 発光ディスプレイ装置およびその駆動制御方法 |

| US7332742B2 (en) * | 2004-06-29 | 2008-02-19 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic apparatus |

| TWI429327B (zh) * | 2005-06-30 | 2014-03-01 | Semiconductor Energy Lab | 半導體裝置、顯示裝置、及電子設備 |

| KR101254227B1 (ko) * | 2006-08-29 | 2013-04-19 | 삼성디스플레이 주식회사 | 표시패널 |

| US8035596B2 (en) * | 2007-07-09 | 2011-10-11 | Nec Lcd Technologies, Ltd | Liquid crystal display device |

-

2008

- 2008-08-12 JP JP2008207895A patent/JP4595008B2/ja active Active

-

2009

- 2009-08-04 CN CN2009101603700A patent/CN101751888B/zh active Active

- 2009-08-04 TW TW098126214A patent/TWI409785B/zh not_active IP Right Cessation

- 2009-08-11 US US12/539,419 patent/US8264440B2/en not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0377915A (ja) * | 1989-08-21 | 1991-04-03 | Sharp Corp | 液晶表示装置 |

| JPH05165431A (ja) * | 1991-12-13 | 1993-07-02 | Kyocera Corp | 液晶表示装置の駆動方法 |

| JP2001059957A (ja) * | 1999-08-23 | 2001-03-06 | Seiko Epson Corp | 液晶装置およびその駆動方法並びに投射型表示装置 |

| JP2003248465A (ja) * | 2002-02-25 | 2003-09-05 | Sharp Corp | 画像表示装置の駆動方法および画像表示装置の駆動装置 |

| JP2007188079A (ja) * | 2006-01-10 | 2007-07-26 | Samsung Electronics Co Ltd | ゲートドライバー、これを備えた薄膜トランジスター基板及び液晶表示装置 |

| JP2007323041A (ja) * | 2006-06-02 | 2007-12-13 | Lg Phillips Lcd Co Ltd | 液晶表示装置及びその駆動方法 |

| JP2008165135A (ja) * | 2007-01-05 | 2008-07-17 | Seiko Epson Corp | 電気光学装置、その駆動方法および電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW201007688A (en) | 2010-02-16 |

| JP4595008B2 (ja) | 2010-12-08 |

| CN101751888B (zh) | 2012-11-14 |

| US20100039419A1 (en) | 2010-02-18 |

| CN101751888A (zh) | 2010-06-23 |

| TWI409785B (zh) | 2013-09-21 |

| US8264440B2 (en) | 2012-09-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102169169B1 (ko) | 표시장치와 그 구동방법 | |

| JP4415393B2 (ja) | 駆動回路、液晶装置、電子機器、および液晶装置の駆動方法 | |

| JP4241858B2 (ja) | 液晶装置、および電子機器 | |

| WO2014162791A1 (ja) | 駆動装置及び駆動方法並びに表示装置及び表示方法 | |

| CN110827771B (zh) | 液晶显示装置及其驱动方法 | |

| JP4595008B2 (ja) | 表示装置、電子装置、電子システム | |

| JP2007072062A (ja) | 表示装置 | |

| JP2009168867A (ja) | 表示装置 | |

| WO2012133281A1 (ja) | 表示装置 | |

| US20100265226A1 (en) | Display device | |

| WO2013129239A1 (ja) | 駆動装置および表示装置 | |

| US8264444B2 (en) | Low-flickering display device | |

| JP5244352B2 (ja) | 表示装置及びそのストレージ駆動回路 | |

| KR101785339B1 (ko) | 공통전압 드라이버 및 이를 포함하는 액정표시장치 | |

| KR101456989B1 (ko) | 액정표시장치용 게이트구동부 | |

| JP2006308982A (ja) | 表示装置 | |

| JP5046230B2 (ja) | 液晶装置、および電子機器 | |

| KR20080022801A (ko) | 액정 표시 장치 | |

| JP5224735B2 (ja) | 液晶装置、および電子機器 | |

| JP2009069563A (ja) | 液晶表示装置及びその駆動方法 | |

| JP2008076733A (ja) | 電気光学装置および電子機器 | |

| KR101623594B1 (ko) | 액정표시장치 | |

| KR101151286B1 (ko) | 액정표시장치의 구동방법 | |

| JP2010197485A (ja) | 電気光学装置及び電子機器 | |

| JP2006235267A (ja) | 半導体装置の駆動方法および駆動装置並びに半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100428 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100511 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100809 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100824 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100917 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130924 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4595008 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130924 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130924 Year of fee payment: 3 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130924 Year of fee payment: 3 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130924 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |