JP2010034575A - 半導体レーザ評価装置 - Google Patents

半導体レーザ評価装置 Download PDFInfo

- Publication number

- JP2010034575A JP2010034575A JP2009248375A JP2009248375A JP2010034575A JP 2010034575 A JP2010034575 A JP 2010034575A JP 2009248375 A JP2009248375 A JP 2009248375A JP 2009248375 A JP2009248375 A JP 2009248375A JP 2010034575 A JP2010034575 A JP 2010034575A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor laser

- ground

- conductor plates

- probe

- evaluation apparatus

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Testing Of Individual Semiconductor Devices (AREA)

- Semiconductor Lasers (AREA)

Abstract

【解決手段】半導体レーザ1を接地ステージ2上に載置すると共に、2つの導体プレート3,4を半導体レーザ1の両側から挟み込んだときには、半導体レーザ1の上面と2つの導体プレート3,4の上面とが同一平面上にあるように構成し、半導体レーザ1の信号電極にプローブの信号端子を、導体プレート3又は4の上面にプローブの接地端子を接触させるようにする。

【選択図】図1

Description

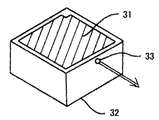

図8は従来の半導体レーザの形状を示す斜視図であり、図において、31は表面に設けられた信号電極、32は裏面にパターニングされた接地電極、33は発光点であり、矢印は発光方向を表している。このような形状を持つ半導体レーザは、信号電極31及び接地電極32が素子の表裏にあるため、両電極間にチップ厚みの分の段差が生じ、高周波でのインピーダンスが取れず、チップ状態では高周波での測定が正確にできない問題があった。

以下、この発明の一実施形態を図について説明する。図1はこの発明の実施の形態1による高周波特性が測定可能な半導体レーザ評価装置を示す斜視図であり、図において、1は半導体レーザ、1aは半導体レーザ1の発光点、1bは半導体レーザ1の表面に設けられた信号電極、2は接地ステージ、3,4は半導体レーザ1と高精度に同じ厚みを持つよう加工された導体プレートである。導体プレート3,4は、半導体レーザ1を両側から挟み込む形で、接地ステージ2上に電気的接触を保って配置され、更に導体プレート3,4は、半導体レーザ1の発光点の位置精度を合わせる目的も兼ねている。

接地ステージ2及び導体プレート3,4は、マイクロ波帯の高周波信号を良好に伝達するため、金などの材質を使用する必要がある。この構造により接地面を導体プレート3,4の上面まで延長することができる。導体プレート3,4は半導体レーザ1と高精度に厚みを同じくしているため、図2に示すように、一般的なGSG(接地―信号−接地)構造やSG構造を持つ高周波プローブによる高周波コンタクトが可能となる。図2において、5は接地―信号−接地構造を持つ高周波プローブである。

図3はこの発明の実施の形態2による高周波特性が測定可能な半導体レーザ評価装置を示す平面図であり、図において、2は接地ステージ、3,4は導体プレート、6は接地ステージ2上の半導体レーザ配置箇所に埋め込んだ、抵抗,容量,インダクタンス等を持つ受動素子成分である。

受動素子成分6は、半導体レーザの持つインピーダンスを考慮に入れて、高周波信号源とのインピーダンス整合を取るように設計する必要があり、半導体レーザのような抵抗性を示す素子については、抵抗成分を埋め込むことで信号源とのインピーダンス整合を図ることが可能となる。

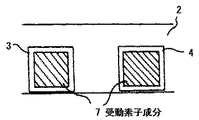

図4はこの発明の実施の形態3による高周波特性が測定可能な半導体レーザ評価装置を示す平面図であり、図において、2は接地ステージ、3,4は導体プレート、7は導体プレート3,4上の高周波プローブコンタクト位置に埋め込んだ、抵抗,容量,インダクタンス等を持つ受動素子成分である。

受動素子成分7は、半導体レーザの持つインピーダンスを考慮に入れて、高周波信号源とのインピーダンス整合を取るように設計する必要があり、半導体レーザのような抵抗性を示す素子については、抵抗成分を埋め込むことで信号源とのインピーダンス整合を図ることが可能となる。

図5はこの発明の実施の形態4による半導体レーザ評価装置にコンタクトを取るための高周波プローブを示す斜視図であり、図において、8は信号源と接続されている高周波ケーブル、9は高周波コネクタ、10はセラミック等からなる誘電体プレート、11,12は接地信号ライン、13は高周波信号ライン、14は信号源と被測定物とのインピーダンス整合を取るための抵抗,容量,インダクタンス等を持つ受動素子成分、15は接地信号ライン11,12及び高周波信号ライン13から被測定物へコンタクトを取るためのプローブ先端部である。

受動素子成分14は、半導体レーザの持つインピーダンスを考慮に入れて、高周波信号源とのインピーダンス整合を取るように設計する必要があり、半導体レーザのような抵抗性を示す素子については、抵抗成分を埋め込むことで、信号源とのインピーダンス整合を図ることが可能となる。

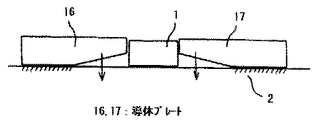

図6はこの発明の実施の形態5による高周波特性が測定可能な半導体レーザ評価装置を示す側面図であり、図において、1は被測定物である半導体レーザ、2は接地ステージ、16,17は下面に切欠きを設けてバネ性を有するようにした導体プレートである。

即ち、導体プレート16,17には、半導体レーザ1の厚みのばらつきを吸収し、接地面と高周波信号面を高精度に同一平面にするための板バネ構造を持つよう加工する。

図7はこの発明の実施の形態6による高周波特性が測定可能な半導体レーザ評価装置を示す斜視図であり、図において、1は被測定物である半導体レーザ、2は接地ステージ、18,19は下面に切り取り部が設けられている導体プレート、20は半導体レーザ1を接着しているサブマウント又はブロック等である。

導体プレート18,19は、サブマウント20の厚み分の切り取り部を設け、図7に示されるような斜線部分にてサブマウント20と接地させるようにする。サブマウント20には、導体プレート18,19の斜線部分において接触可能なように、半導体レーザ1の裏面の接地電極と電気的に接触している構造を取る必要がある。

更に、インピーダンス整合を取るためには、上記形態による構造に加えて、実施の形態2〜実施の形態4に示した構造を採用することにより実現する。

3,4,16,17,18,19 導体プレート、5 プローブ、

6,7,14 受動素子成分、11,12 接地信号ライン、13 高周波信号ライン、20 サブマウント。

Claims (5)

- 接地ステージ上に、同じ高さを有する2つの導体プレートを電気的接触を保って配置するとともに、表面に信号電極かつ裏面に接地電極を設けた所定厚みの半導体レーザを上記2つの導体プレートの間に挟み込むことにより上記半導体レーザの評価を行う半導体レーザ評価装置であって、上記半導体レーザを上記接地ステージ上に載置すると共に上記2つの導体プレートを上記半導体レーザの両側から挟み込んだときには、上記半導体レーザの上面と上記2つの導体プレートの上面とが同一平面上にあるように構成し、上記半導体レーザの信号電極にプローブの信号端子を、上記導体プレートの上面に上記プローブの接地端子を接触させたことを特徴とする半導体レーザ評価装置。

- 接地ステージ上に、同じ高さを有する2つの導体プレートを配置するとともに、表面に信号電極かつ裏面に接地電極を設け更に上記裏面に設けられた上記接地電極にサブマウントを接着した所定厚みの半導体レーザを上記2つの導体プレートの間に挟み込むことにより上記半導体レーザの評価を行う半導体レーザ評価装置であって、上記2つの導体プレートの下面に上記サブマウントの厚み分の切り取り部を設け、上記サブマウントを上記接地ステージ上に載置すると共に上記2つの導体プレートを上記サブマウントとの電気的接触を保ちながら上記半導体レーザの両側から挟み込んだときには、上記半導体レーザの上面と上記2つの導体プレートの上面とが同一平面上にあるように構成し、更に上記半導体レーザの信号電極にプローブの信号端子を、上記導体プレートの上面に上記プローブの接地端子を接触させたことを特徴とする半導体レーザ評価装置。

- 接地ステージ上の半導体レーザ設置個所に受動素子成分を埋め込んだことを特徴とする請求項1又は請求項2に記載の半導体レーザ評価装置。

- 導体プレート上のプローブコンタクト位置に受動素子成分を埋め込んだことを特徴とする請求項1又は請求項2に記載の半導体レーザ評価装置。

- プローブにおける接地信号ライン及び高周波信号ラインとの間に受動素子成分を接続させたことを特徴とする請求項1又は請求項2に記載の半導体レーザ評価装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009248375A JP4515536B2 (ja) | 2009-10-29 | 2009-10-29 | 半導体レーザ評価装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009248375A JP4515536B2 (ja) | 2009-10-29 | 2009-10-29 | 半導体レーザ評価装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP00031399A Division JP4416855B2 (ja) | 1999-01-05 | 1999-01-05 | 半導体レーザ評価装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010034575A true JP2010034575A (ja) | 2010-02-12 |

| JP4515536B2 JP4515536B2 (ja) | 2010-08-04 |

Family

ID=41738616

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009248375A Expired - Fee Related JP4515536B2 (ja) | 2009-10-29 | 2009-10-29 | 半導体レーザ評価装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4515536B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014175014A1 (ja) * | 2013-04-25 | 2014-10-30 | 株式会社村田製作所 | 電子部品の試験装置 |

| CN118336504A (zh) * | 2023-01-10 | 2024-07-12 | 武汉光迅科技股份有限公司 | 一种eml芯片与测试方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02249288A (ja) * | 1989-03-23 | 1990-10-05 | Matsushita Electric Ind Co Ltd | 素子の取り付け治具 |

| JPH10125997A (ja) * | 1996-10-22 | 1998-05-15 | Matsushita Electric Ind Co Ltd | 半導体レーザモジュール |

| JP2000028678A (ja) * | 1998-07-13 | 2000-01-28 | Mitsubishi Electric Corp | 光半導体チップ検査装置及び光半導体チップ検査方法 |

-

2009

- 2009-10-29 JP JP2009248375A patent/JP4515536B2/ja not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02249288A (ja) * | 1989-03-23 | 1990-10-05 | Matsushita Electric Ind Co Ltd | 素子の取り付け治具 |

| JPH10125997A (ja) * | 1996-10-22 | 1998-05-15 | Matsushita Electric Ind Co Ltd | 半導体レーザモジュール |

| JP2000028678A (ja) * | 1998-07-13 | 2000-01-28 | Mitsubishi Electric Corp | 光半導体チップ検査装置及び光半導体チップ検査方法 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014175014A1 (ja) * | 2013-04-25 | 2014-10-30 | 株式会社村田製作所 | 電子部品の試験装置 |

| JP5987977B2 (ja) * | 2013-04-25 | 2016-09-07 | 株式会社村田製作所 | 電子部品の試験装置 |

| US10060970B2 (en) | 2013-04-25 | 2018-08-28 | Murata Manufacturing Co., Ltd. | Electronic component testing device |

| CN118336504A (zh) * | 2023-01-10 | 2024-07-12 | 武汉光迅科技股份有限公司 | 一种eml芯片与测试方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4515536B2 (ja) | 2010-08-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5352170B2 (ja) | 検査用ソケット | |

| KR100864916B1 (ko) | 피시험 디바이스를 테스트하기 위한 프로브 | |

| CN108735678B (zh) | 一种量子裸芯片立体封装结构及其封装方法 | |

| WO2014129278A1 (ja) | インダクタブリッジおよび電子機器 | |

| TW200905204A (en) | Probe assembly for probe card | |

| KR101186915B1 (ko) | 검사용 접촉 구조체 | |

| US7173433B2 (en) | Circuit property measurement method | |

| JP4515536B2 (ja) | 半導体レーザ評価装置 | |

| JP2006337361A (ja) | 信号プローブ及びプローブアセンブリ | |

| JP7206140B2 (ja) | 検査装置 | |

| KR20170010936A (ko) | 무선 주파수 프로브 장치 | |

| JP2016200652A (ja) | 光変調器用の接続治具 | |

| JP4416855B2 (ja) | 半導体レーザ評価装置 | |

| JP2008177602A (ja) | 半導体レーザ評価装置及び半導体レーザ評価方法 | |

| JPWO2010061582A1 (ja) | 回路モジュールの基板及びその製造方法 | |

| JP3732437B2 (ja) | 電気的接続治具及びこれを用いた半導体装置の特性測定装置 | |

| WO2000004394A1 (en) | Socket for device measurement, and method of measuring device | |

| JP2006214943A (ja) | プローブ装置 | |

| JP2572932Y2 (ja) | 高周波測定プローブ | |

| JP3448555B2 (ja) | 光素子パッケージの試験器具 | |

| JP6805923B2 (ja) | 光変調器 | |

| JP2019186729A (ja) | アンテナおよび測定用プローブ | |

| JP2003084010A (ja) | 高周波プローブ | |

| JP2007285980A (ja) | プローブ装置 | |

| JP2010008275A (ja) | 伝送線路基板及び高周波部品の測定装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100427 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100512 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130521 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140521 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |