JP2010033936A - 自発光型素子及びその製造方法 - Google Patents

自発光型素子及びその製造方法 Download PDFInfo

- Publication number

- JP2010033936A JP2010033936A JP2008196050A JP2008196050A JP2010033936A JP 2010033936 A JP2010033936 A JP 2010033936A JP 2008196050 A JP2008196050 A JP 2008196050A JP 2008196050 A JP2008196050 A JP 2008196050A JP 2010033936 A JP2010033936 A JP 2010033936A

- Authority

- JP

- Japan

- Prior art keywords

- bank

- common wiring

- light emitting

- self

- luminous element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Electroluminescent Light Sources (AREA)

Abstract

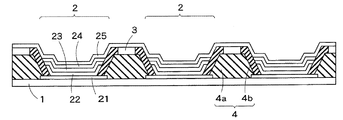

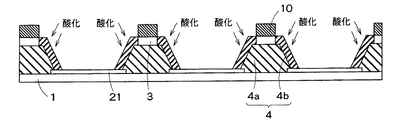

【解決手段】基板1と、前記基板上に所定間隔を空けて形成された複数の第1の電極層21と、前記第1の電極層間の前記基板上に形成されたバンクコア部4aと、前記バンクコア部上に形成された共通配線3と、前記バンクコア部の側面を覆い、前記共通配線を挟むように形成され、上面が前記共通配線の上面と面一になっているバンク側壁部4bと、前記第1の電極層の上方に形成された発光層23と、前記発光層の上方、前記バンク側壁部、及び前記共通配線を覆うように形成された第2の電極層25と、を備える。

【選択図】図3

Description

2 サブピクセル

3 共通配線

21 陽極

22 正孔注入輸送層

23 発光層

24 電子注入輸送層

25 半透過陰極

Claims (9)

- 基板と、

前記基板上に所定間隔を空けて形成された複数の第1の電極層と、

前記第1の電極層間の前記基板上に形成されたバンクコア部と、

前記バンクコア部上に形成された共通配線と、

前記バンクコア部の側面を覆い、前記共通配線を挟むように形成され、上面が前記共通配線の上面と面一になっているバンク側壁部と、

前記第1の電極層の上方に形成された発光層と、

前記発光層の上方、前記バンク側壁部、及び前記共通配線を覆うように形成された第2の電極層と、

を備える自発光型素子。 - 前記バンク側壁部は、前記共通配線に含まれる金属の酸化物を含むことを特徴とする請求項1に記載の自発光型素子。

- 前記共通配線はタンタルを含み、前記バンク側壁部は五酸化タンタルを含むことを特徴とする請求項1又は2に記載の自発光型素子。

- 前記第1の電極層と前記発光層との間に形成された正孔注入輸送層と、

前記発光層と前記第2の電極層との間に形成された電子注入輸送層と、

をさらに有することを特徴とする請求項1乃至3のいずれかに記載の自発光型素子 - 前記第2の電極層は仕事関数が3.4eV以下の金属を含むことを特徴とする請求項4に記載の自発光型素子。

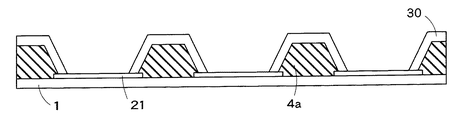

- 基板上に所定間隔を空けて複数の第1の電極層を形成し、

前記第1の電極層間の前記基板上にバンクコア部を形成し、

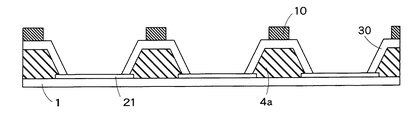

前記バンクコア部の側面及び上面を覆うように金属膜を形成し、

前記金属膜のうち前記バンクコア部の側面を覆っている領域を酸化してバンク側壁部を形成し、

前記第1の電極層の上方に発光層を形成し、

前記発光層の上方、前記バンク側壁部、及び前記バンクコア部の上面を覆う前記金属膜を覆うように第2の電極層を形成する自発光型素子の製造方法。 - 前記金属膜はタンタル又はアルミニウムを含むことを特徴とする請求項6に記載の自発光型素子の製造方法。

- 前記発光層の形成前に前記第1の電極層上に正孔注入輸送層を形成し、

前記第2の電極層の形成前に前記発光層上に電子注入輸送層を形成することを特徴とする請求項6又は7に記載の自発光型素子の製造方法。 - 前記第2の電極層は仕事関数が3.4eV以下の金属を含むことを特徴とする請求項8に記載の自発光型素子の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008196050A JP5002553B2 (ja) | 2008-07-30 | 2008-07-30 | 自発光型素子及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008196050A JP5002553B2 (ja) | 2008-07-30 | 2008-07-30 | 自発光型素子及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010033936A true JP2010033936A (ja) | 2010-02-12 |

| JP5002553B2 JP5002553B2 (ja) | 2012-08-15 |

Family

ID=41738162

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008196050A Expired - Fee Related JP5002553B2 (ja) | 2008-07-30 | 2008-07-30 | 自発光型素子及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5002553B2 (ja) |

Cited By (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011238597A (ja) * | 2010-05-07 | 2011-11-24 | Samsung Mobile Display Co Ltd | 有機発光ディスプレイ装置及びその製造方法 |

| WO2012161005A1 (ja) * | 2011-05-20 | 2012-11-29 | パナソニック株式会社 | 有機エレクトロルミネッセンス素子 |

| WO2012161004A1 (ja) * | 2011-05-20 | 2012-11-29 | パナソニック株式会社 | 有機エレクトロルミネッセンス素子 |

| WO2013108598A1 (ja) * | 2012-01-18 | 2013-07-25 | パナソニック株式会社 | 電子装置およびその製造方法 |

| WO2013118462A1 (ja) * | 2012-02-06 | 2013-08-15 | パナソニック株式会社 | El表示装置およびその製造方法 |

| KR20160139826A (ko) * | 2015-05-28 | 2016-12-07 | 엘지디스플레이 주식회사 | 플렉서블 디스플레이 |

| JP2019133949A (ja) * | 2011-02-25 | 2019-08-08 | 株式会社半導体エネルギー研究所 | 電子機器 |

| WO2022175781A1 (ja) * | 2021-02-19 | 2022-08-25 | 株式会社半導体エネルギー研究所 | 表示装置、表示モジュール、及び電子機器 |

| WO2022180468A1 (ja) * | 2021-02-25 | 2022-09-01 | 株式会社半導体エネルギー研究所 | 表示装置、表示モジュール、電子機器、及び、表示装置の作製方法 |

| WO2022185149A1 (ja) * | 2021-03-05 | 2022-09-09 | 株式会社半導体エネルギー研究所 | 表示装置、表示モジュール、電子機器、及び、表示装置の作製方法 |

| WO2022189908A1 (ja) * | 2021-03-11 | 2022-09-15 | 株式会社半導体エネルギー研究所 | 表示装置 |

| WO2022214904A1 (ja) * | 2021-04-08 | 2022-10-13 | 株式会社半導体エネルギー研究所 | 表示装置 |

| WO2022224080A1 (ja) * | 2021-04-23 | 2022-10-27 | 株式会社半導体エネルギー研究所 | 表示装置、表示モジュール、電子機器、及び、表示装置の作製方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09116161A (ja) * | 1995-10-18 | 1997-05-02 | Seiko Epson Corp | 薄膜半導体装置およびその製造方法 |

| JP2003288994A (ja) * | 2002-01-24 | 2003-10-10 | Semiconductor Energy Lab Co Ltd | 発光装置およびその作製方法 |

| JP2004127933A (ja) * | 2002-09-11 | 2004-04-22 | Semiconductor Energy Lab Co Ltd | 発光装置およびその作製方法 |

| JP2004335389A (ja) * | 2003-05-12 | 2004-11-25 | Sony Corp | 蒸着マスクおよびこれを用いた表示装置の製造方法、ならびに表示装置 |

| JP2005521205A (ja) * | 2002-03-20 | 2005-07-14 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | アクティブマトリクス表示装置及びその製造方法 |

| JP2005521204A (ja) * | 2002-03-20 | 2005-07-14 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | アクティブマトリクスエレクトロルミネッセンス表示装置及びその製造方法 |

| JP2007165215A (ja) * | 2005-12-16 | 2007-06-28 | Seiko Epson Corp | エレクトロルミネッセンス装置の製造方法 |

-

2008

- 2008-07-30 JP JP2008196050A patent/JP5002553B2/ja not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09116161A (ja) * | 1995-10-18 | 1997-05-02 | Seiko Epson Corp | 薄膜半導体装置およびその製造方法 |

| JP2003288994A (ja) * | 2002-01-24 | 2003-10-10 | Semiconductor Energy Lab Co Ltd | 発光装置およびその作製方法 |

| JP2005521205A (ja) * | 2002-03-20 | 2005-07-14 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | アクティブマトリクス表示装置及びその製造方法 |

| JP2005521204A (ja) * | 2002-03-20 | 2005-07-14 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | アクティブマトリクスエレクトロルミネッセンス表示装置及びその製造方法 |

| JP2004127933A (ja) * | 2002-09-11 | 2004-04-22 | Semiconductor Energy Lab Co Ltd | 発光装置およびその作製方法 |

| JP2004335389A (ja) * | 2003-05-12 | 2004-11-25 | Sony Corp | 蒸着マスクおよびこれを用いた表示装置の製造方法、ならびに表示装置 |

| JP2007165215A (ja) * | 2005-12-16 | 2007-06-28 | Seiko Epson Corp | エレクトロルミネッセンス装置の製造方法 |

Cited By (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011238597A (ja) * | 2010-05-07 | 2011-11-24 | Samsung Mobile Display Co Ltd | 有機発光ディスプレイ装置及びその製造方法 |

| US9035330B2 (en) | 2010-05-07 | 2015-05-19 | Samsung Display Co., Ltd. | Organic light-emitting display device and method of manufacturing the organic light emitting display device |

| JP2016048696A (ja) * | 2010-05-07 | 2016-04-07 | 三星ディスプレイ株式會社Samsung Display Co.,Ltd. | 有機発光ディスプレイ装置及びその製造方法 |

| JP2019133949A (ja) * | 2011-02-25 | 2019-08-08 | 株式会社半導体エネルギー研究所 | 電子機器 |

| WO2012161005A1 (ja) * | 2011-05-20 | 2012-11-29 | パナソニック株式会社 | 有機エレクトロルミネッセンス素子 |

| WO2012161004A1 (ja) * | 2011-05-20 | 2012-11-29 | パナソニック株式会社 | 有機エレクトロルミネッセンス素子 |

| CN103250265A (zh) * | 2011-05-20 | 2013-08-14 | 松下电器产业株式会社 | 有机电致发光元件 |

| US8729542B2 (en) | 2011-05-20 | 2014-05-20 | Panasonic Corporation | Organic electroluminescence element |

| JP5520418B2 (ja) * | 2011-05-20 | 2014-06-11 | パナソニック株式会社 | 有機エレクトロルミネッセンス素子 |

| US9356252B2 (en) | 2012-01-18 | 2016-05-31 | Joled Inc. | Electronic device and manufacturing method therefor |

| WO2013108598A1 (ja) * | 2012-01-18 | 2013-07-25 | パナソニック株式会社 | 電子装置およびその製造方法 |

| WO2013118462A1 (ja) * | 2012-02-06 | 2013-08-15 | パナソニック株式会社 | El表示装置およびその製造方法 |

| US9111891B2 (en) | 2012-02-06 | 2015-08-18 | Joled Inc. | EL display apparatus and manufacturing method thereof |

| KR20160139826A (ko) * | 2015-05-28 | 2016-12-07 | 엘지디스플레이 주식회사 | 플렉서블 디스플레이 |

| KR102533387B1 (ko) | 2015-05-28 | 2023-05-17 | 엘지디스플레이 주식회사 | 플렉서블 디스플레이 |

| WO2022175781A1 (ja) * | 2021-02-19 | 2022-08-25 | 株式会社半導体エネルギー研究所 | 表示装置、表示モジュール、及び電子機器 |

| WO2022180468A1 (ja) * | 2021-02-25 | 2022-09-01 | 株式会社半導体エネルギー研究所 | 表示装置、表示モジュール、電子機器、及び、表示装置の作製方法 |

| WO2022185149A1 (ja) * | 2021-03-05 | 2022-09-09 | 株式会社半導体エネルギー研究所 | 表示装置、表示モジュール、電子機器、及び、表示装置の作製方法 |

| WO2022189908A1 (ja) * | 2021-03-11 | 2022-09-15 | 株式会社半導体エネルギー研究所 | 表示装置 |

| WO2022214904A1 (ja) * | 2021-04-08 | 2022-10-13 | 株式会社半導体エネルギー研究所 | 表示装置 |

| WO2022224080A1 (ja) * | 2021-04-23 | 2022-10-27 | 株式会社半導体エネルギー研究所 | 表示装置、表示モジュール、電子機器、及び、表示装置の作製方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5002553B2 (ja) | 2012-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5002553B2 (ja) | 自発光型素子及びその製造方法 | |

| US12035544B2 (en) | Organic light-emitting display apparatus having a conductive layer with an undercut structure and method of manufacturing the same | |

| JP5236060B2 (ja) | 有機エレクトロルミネッセンス表示装置及びその製造方法 | |

| JP4736890B2 (ja) | 有機エレクトロルミネッセンス素子 | |

| US9269753B2 (en) | Organic light emitting device | |

| JP2011040167A (ja) | 表示装置およびその製造方法 | |

| JP5372337B2 (ja) | 有機薄膜トランジスタ基板及びその製造方法、並びに、画像表示パネル及びその製造方法 | |

| US20080237580A1 (en) | Organic Semiconductor Element and Organic El Display Device Using the Same | |

| JP2005327674A (ja) | 有機エレクトロルミネッセント表示素子、それを有する表示装置、及び、その製造方法 | |

| US20170200776A1 (en) | Organic light emitting diode display and manufacturing method thereof | |

| KR20130033259A (ko) | 유기 발광 소자와 그 제조 방법, 유기 표시 패널, 유기 표시 장치 | |

| WO2007043704A1 (ja) | 発光素子及び表示装置 | |

| US7728515B2 (en) | Light-emitting circuit board and light-emitting display device | |

| JP6387547B2 (ja) | 有機el素子とその製造方法、および金属酸化物膜の成膜方法 | |

| US9786726B2 (en) | Organic light-emitting device and organic display device | |

| WO2015166651A1 (ja) | 薄膜トランジスタ装置、及びそれを用いた表示装置 | |

| JP2007109564A (ja) | 発光素子及び表示装置 | |

| JP2006243127A (ja) | シートディスプレイ | |

| JP2010277949A (ja) | 有機el表示装置及びその製造方法 | |

| JP2010009753A (ja) | 有機el表示装置及びその製造方法 | |

| JP6781606B2 (ja) | 有機el素子の製造方法 | |

| WO2015033881A1 (ja) | 有機薄膜トランジスタ | |

| JP4770523B2 (ja) | 発光装置の製造方法 | |

| US20230240122A1 (en) | Method of manufacturing display device | |

| JP6563311B2 (ja) | 表示パネルの製造方法および表示パネル |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110324 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120207 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120208 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120328 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120427 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120521 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150525 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |